### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

#### CAIO GRACO PRATES ALEGRETTI

# Analytical Logical Effort Formulation for Local Sizing

Thesis presented in partial fulfillment of the requirements for the degree of Doctor in Microelectronics.

Prof. Dr. André Inácio Reis Advisor

Prof. Dr. Renato Perez Ribas Co-advisor

Porto Alegre, June 2013.

#### CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Alegretti, Caio Graco Prates

Analytical Logical Effort Formulation for Local Sizing [manuscrito] / Caio Graco Prates Alegretti. – 2013.

84 f.:il.

Advisor: André Inácio Reis; Co-advisor: Renato Perez Ribas.

Tese (doutorado) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica. Porto Alegre, BR – RS, 2013.

1. Subcircuit sizing. 2. Active area minimization. 3. Design constraints. 4. Logical Effort. I. Reis, André Inácio. II. Ribas, Renato Perez. III. Título.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Aldo Bolten Lucion Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb

Coordenador do PGMicro: Gilson Inácio Wirth

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **ACKNOWLEDGMENTS**

There are so many people I am thankful to...

First of all, I would like to express my most sincere gratitude to my advisors, professors André Inácio Reis and Renato Perez Ribas. Their advices, availability, guidance, and patience out of this world were vital for the conclusion of this work. In them, I could find a combination of technical expertise and soft/human skills that is very rare to come upon in the Engineering environment.

Working at LogiCS Labs was a very fruitful experience. I had the opportunity to share the companionship of brilliant, highly motivated, and funny colleagues. It was never ever a boring place. In particular, Vinicius Dal Bem helped a lot in the implementation of the thesis. Here goes a non-exhaustive, lexicographic list of the people I am indebted with: Alessandro Goulart, Digeorgia Natalie Silva, Felipe Marques, Felipe Marranghello, Jody Matos, Leomar Soares Jr., Mayler Martins, Nivea Schuch, Osvaldo Martinello Jr., Paulo Butzen, Rodrigo Mancuso, and Vinicius Callegaro. Either by technical discussions or random conversation, they have all contributed to my work.

Professor Paulo Fernandes, my master's advisor, introduced me to the academic research. I will always be thankful for that, even though my professional trajectory drifted me away from the brave new world of stochastic automata networks.

It is widely known that money makes the world go round. In this sense, I would like to thank the Brazilian funding agency CAPES and the Danish company Nangate A\S for the financial support, as well as my current employer, IFRS. Although there was no institutional stimulus for pursuing a doctorate degree, my colleagues at IFRS were always willing to help.

None of this would have been possible without the support and unconditional love from my family. My parents José Dante and Maria Elizabeth, as well as my brothers Tito Lívio and Francisco José, have taught me the value of reading, studying, and honest, hardworking. My wife Cristiane gave me Alexandre, by very, very far, the greatest happiness in my life. I will always be thankful for her. Just seeing Alexandre smiling, laughing, and playing makes life worth living.

Last, but not least, a perhaps unusual acknowledgment in a doctorate thesis. I would like to register my gratitude to Deolinda, my first teacher in a poor, rotten, public elementary school in a poor fisherman village. With her I learned how to read, to write, and to do basic calculations. Basic education is of foremost importance for the economic, technological, and social development of any nation. Regretfully, this is hardly ever remembered.

## Formulação Analítica Baseada em *Logical Effort* para Dimensionamento Local

#### **RESUMO**

A indústria de microeletrônica tem recorrido cada vez mais à metodologia de projeto baseado em células para fazer frente à crescente complexidade dos projetos de circuitos integrados digitais, uma vez que circuitos baseados em células são projetados mais rápida e economicamente que circuitos full-custom. Entretanto, apesar do progresso ocorrido na área de Electronic Design Automation, circuitos digitais baseados em células apresentam desempenho inferior ao de circuitos full-custom. Assim, torna-se interessante encontrar maneiras de se fazer com que circuitos baseados em células tenham desempenho próximo ao de circuitos full-custom, sem que isso implique elevação significativa nos custos do projeto. Com tal objetivo em vista, esta tese apresenta contribuições para um fluxo automático de otimização local para circuitos digitais baseados em células. Por otimização local se entende a otimização do circuito em pequenas janelas de contexto, onde são feitas otimizações considerando o contexto global. Deste modo, a otimização local pode incluir a detecção e isolamento de regiões críticas do circuito e a geração de redes lógicas e de redes de transistores de diferentes topologias que são dimensionadas de acordo com as restrições de projeto em questão. Como as otimizações locais atuam em um contexto reduzido, várias soluções podem ser obtidas considerando as restrições locais, entre as quais se escolhe a mais adequada para substituir o subcircuito (região crítica) original. A contribuição específica desta tese é o desenvolvimento de um método de dimensionamento de subcircuitos capaz de obter soluções com área ativa mínima, respeitando a capacitância máxima de entrada, a carga a ser acionada, e a restrição de atraso imposta. O método é baseado em uma formulação de logical effort, e a principal contribuição é calcular analiticamente a derivada da área para obter área mínima, ao invés de fazer a derivada do atraso para obter o atraso mínimo, como é feito na formulação tradicional do logical effort. Simulações elétricas mostram que o modelo proposto é muito preciso para uma abordagem de primeira ordem, uma vez que apresenta erros médios de 1,48% para dissipação de potência, 2,28% para atraso de propagação e 6,5% para os tamanhos dos transistores.

**Palavras-Chave:** Dimensionamento de Subcircuitos, Minimização de Área Ativa, Restrições de Projeto, *Logical Effort*.

#### **Analytical Logical Effort Formulation for Local Sizing**

#### **ABSTRACT**

Microelectronics industry has been relying more and more upon cell-based design methodology to face the growing complexity in the design of digital integrated circuits, since cell-based integrated circuits are designed in a faster and cheaper way than fullcustom circuits. Nevertheless, in spite of the advancements in the field of Electronic Design Automation, cell-based digital integrated circuits show inferior performance when compared with full-custom circuits. Therefore, it is desirable to find ways to bring the performance of cell-based circuits closer to that of full-custom circuits without compromising the design costs of the former circuits. Bearing this goal in mind, this thesis presents contributions towards an automatic flow of local optimization for cellbased digital circuits. By local optimization, it is meant circuit optimization within small context windows, in which optimizations are done taking into account the global context. This way, local optimization may include the detection and isolation of critical regions of the circuit and the generation of logic and transistor networks; these networks are sized according to the existing design constraints. Since local optimizations act in a reduced context, several solutions may be obtained considering local constraints, out of which the fittest solution is chosen to replace the original subcircuit (critical region). The specific contribution of this thesis is the development of a subcircuit sizing method capable of obtaining minimum active area solutions, taking into account the maximum input capacitance, the output load to be driven, and the imposed delay constraint. The method is based on the logical effort formulation, and the main contribution is to compute the area derivative to obtain minimum area, instead of making the delay derivative to obtain minimum delay, as it is done in the traditional logical effort formulation. Electrical simulations show that the proposed method is very precise for a first order approach, as it presents average errors of 1.48% in power dissipation, 2.28% in propagation delay, and 6.5% in transistor sizes.

**Keywords:** Subcircuit Sizing, Active Area Minimization, Design Constraints, Logical Effort.

## LIST OF FIGURES

| Figure 2.1 – Different logic and transistor networks for the same logic function       | 16 |

|----------------------------------------------------------------------------------------|----|

| Figure 2.2 – Scale factor of a NOR2 cell                                               | 18 |

| Figure 2.3 – Examples of supercells for NAND2 logic function                           | 19 |

| Figure 2.4 – Current difference in cell sizes                                          |    |

| Figure 2.5 – Cell based design flow                                                    | 22 |

| Figure 2.6 – Local and global design constraints                                       | 23 |

| Figure 2.7 – Subcircuit with several paths $(P_1, P_2,, P_6)$ between input and output | 25 |

| Figure 2.8 – Example of part of SDC file                                               | 26 |

| Figure 2.9 – Example of <i>RC</i> tree                                                 | 29 |

| Figure 2.10 – Logical effort delay model of a logic gate                               | 30 |

| Figure 2.11 – Examples of basic logic gates modeled according to logical effort        | 32 |

| Figure 3.1 – Local optimization                                                        | 39 |

| Figure 3.2 – CSP CMOS logic gate seen as a combination of a pull-up and a pull-dow     | 'n |

| network                                                                                | 41 |

| Figure 3.3 – Series-parallel duality in CSP CMOS logic gate                            | 42 |

| Figure 3.4 – Example of flex cell generation                                           | 49 |

| Figure 4.1 – Laboratory approach for local optimization                                | 51 |

| Figure 4.2 – Example of local remapping                                                | 52 |

| Figure 4.3 – Model of a 2-stage subcircuit with fixed input capacitance                | 53 |

| Figure 4.4 – Model of a 3-stage subcircuit with fixed input capacitance                | 54 |

| Figure 4.5 – Model of a 2-stage subcircuit with variable input capacitance             | 57 |

| Figure 4.6 – Model of a 3-stage subcircuit with variable input capacitance             | 59 |

| Figure 4.7 – Model of a 2-stage branching subcircuit with variable input capacitance.  | 65 |

| Figure 5.1 – Subcircuit to be sized                                                    | 71 |

| Figure 5.2 – Delay vs. sizing of a subcircuit for minimum active area via exhaustive   |    |

| search (electrical simulation)                                                         | 73 |

| Figure 5.3 – Power consumption of the subcircuit under design                          | 74 |

## LIST OF TABLES

| Table 2.1 – Example of a standard cell library                               | 17 | 7 |

|------------------------------------------------------------------------------|----|---|

| Table 5.1 – Sizing results compared with HSPICE reference and Kabbani (2010) | 72 | 2 |

#### LIST OF ABBREVIATIONS

AOI AND-OR-Inverter

ASIC Application Specific Integrated Circuit

AT Arrival Time

CAD Computer Aided Design

CMOS Complementary Metal Oxide Semiconductor

CP Convex Programming

CSP Complementary Series Parallel

DP Dynamic Programming

DSP Digital Signal Processor

EDA Electronic Design Automation

GGP Generalized Geometric Programming

GND Ground

GP Geometric Programming

HDL Hardware Description Language

IC Integrated Circuit

IEEE Institute of Electrical and Electronics Engineers

I/O Input/Output

IP Integer Programming

LE Logical Effort

LP Linear Programming

LSH Locality Sensitive Hashing

LUT Lookup Table

m meter

MFI Maximum FanIn

MINLP Mixed Integer Nonlinear Program

MLE Modified Logical Effort

MOS Metal Oxide Semiconductor

**MOSFET** Metal Oxide Semiconductor Field Effect Transistor

nano  $(10^{-9})$

**NLDM** Nonlinear Delay Model **NLP Nonlinear Programming** *n*-type MOS transistor **NMOS**

**NOCL** NANGATE 45nm Open Cell Library

OAI OR-AND-Inverter **PDN** Pull-Down Network **PMOS** *p*-type MOS transistor

**PUN** Pull-Up Network RCResistor-Capacitor

RTRequired Time

**RTL** Register Transfer Level

**SCMS** Series-Connected MOSFET Structure

**SDC** Synopsys Design Constraints

SOC System on a Chip

STA **Static Timing Analysis** tdhl delay time high to low tdlh delay time low to high **TILOS**

TImed LOgic Synthesizer

**UFRGS** Universidade Federal do Rio Grande do Sul (Federal University of Rio

Grande do Sul)

$V_{DD}$ Supply voltage

$V_t$ threshold voltage of a transistor

$V_{th}$ Logic threshold voltage of a logic gate

## TABLE OF CONTENTS

| RESUM   | O                                                       | 4  |

|---------|---------------------------------------------------------|----|

| ABSTRA  | ACT                                                     | 5  |

| LIST OI | F FIGURES                                               | 6  |

| LIST OF | F TABLES                                                | 7  |

| LIST OI | F ABBREVIATIONS                                         | 8  |

| 1 INTI  | RODUCTION                                               | 12 |

| 2 BAS   | IC CONCEPTS                                             | 14 |

| 2.1 Ge  | eneral Concepts about Digital Integrated Circuit Design | 14 |

| 2.2 De  | esign Constraints                                       | 22 |

| 2.2.1   | Example of design constraint specification format       |    |

| 2.3 De  | elay                                                    | 27 |

| 2.3.1   | Fundamental concepts                                    |    |

| 2.3.2   | Elmore delay model                                      |    |

| 2.3.3   | Logical effort delay model                              |    |

| 2.3.4   | Nonlinear Delay Model – NLDM                            |    |

| 2.3.5   | Delay models comparison                                 | 34 |

| 2.4 Siz | zing                                                    | 34 |

| 2.5 Ma  | athematical Programming                                 | 36 |

| 2.6 Ar  | nalytical Resolution of the Minimization Problem        | 38 |

| 2.6.1   | Minimization of multivariable functions                 | 38 |

| 3 BIBI  | LIOGRAPHICAL REVIEW                                     | 39 |

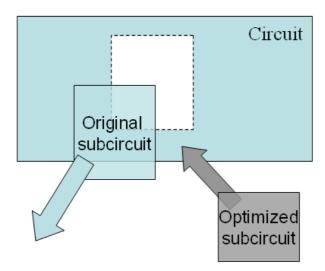

| 3.1 | Local Optimization                                                                  | 39 |

|-----|-------------------------------------------------------------------------------------|----|

| 3.2 | Transistor Networks                                                                 | 40 |

| 3.3 | Delay Models                                                                        | 43 |

| 3.3 | Extension of the logical effort model                                               | 43 |

| 3.3 | 3.2 Modified logical effort model                                                   | 43 |

| 3.3 | 3.3 Logical effort model considering transition time                                | 43 |

| 3.4 | Sizing Algorithms                                                                   | 44 |

| 3.4 | I.1 TILOS: An initial approach in geometric programming                             | 44 |

| 3.4 | A modern approach in geometric programming                                          | 45 |

| 3.4 | 1.3 The logical effort sizing method                                                | 45 |

| 3.4 | 4.4 GS: A well-succeeded discrete sizing algorithm                                  | 46 |

| 3.4 | 1.5 NEW: A recent discrete sizing algorithm                                         | 47 |

| 3.4 | The flex-cell approach for local optimizations                                      | 48 |

|     | ANALYTICAL METHOD FOR MINIMIZING THE ACTIVE A LL SUBCIRCUITS UNDER DELAY CONSTRAINT |    |

| 4.1 | Sizing Method Contextualization                                                     | 51 |

| 4.2 | Contribution of this Thesis                                                         | 52 |

| 4.3 | Fixed Input Capacitance                                                             | 53 |

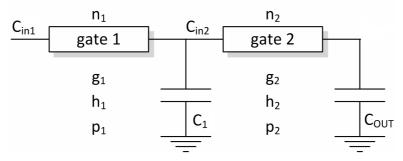

| 4.3 | 3.1 Two-stage subcircuits                                                           | 53 |

| 4.3 | 3.2 Three-stage subcircuits                                                         | 54 |

| 4.4 | Variable Input Capacitance                                                          | 56 |

| 4.4 |                                                                                     |    |

| 4.4 | <del>-</del>                                                                        |    |

| 4.5 | Branching Subcircuits                                                               | 65 |

| 4.6 | Power Delay Product                                                                 | 68 |

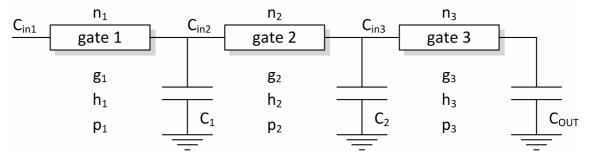

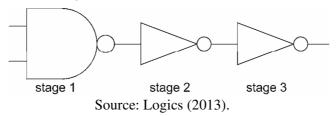

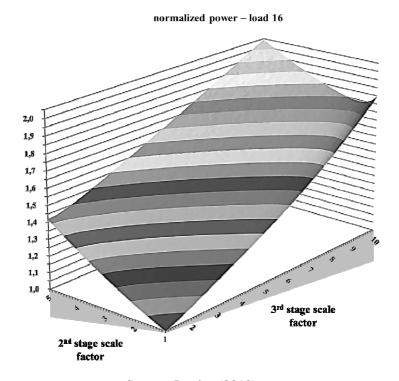

| 5 E | EXPERIMENTAL RESULTS                                                                | 71 |

| 6 ( | CONCLUSION AND FUTURE WORK                                                          | 76 |

| REF | ERENCES                                                                             | 78 |

#### 1 INTRODUCTION

Electronic devices become more and more present on people's daily lives, which makes out of the market of semiconductor devices an important parcel of world economy. A fair chance of good profits has attracted a great number of companies for such market, and so the electronics industry is induced to deliver products every time with higher quality standards and shorter time to market. Therefore, any way to reduce design time of integrated circuits is very appealing for this industry.

Adding to this fact the current stage of miniaturization and integration in microelectronics, which makes the design of an integrated circuit steadily more complex, it is set up scenery for a design methodology capable of dealing with these boundaries efficiently. According to Weste (2006), there are seven design methodologies currently in use:

- Structured design techniques;

- Microprocessor/DSP (Digital Signal Processor);

- Programmable Logic;

- Gate array and Sea of gates design;

- Cell-based design;

- Full-custom design;

- Platform-based design/System on a Chip (SOC).

These design methodologies take advantage of CAD (Computer Aided Design) tools, in a way to allow them to cope with the current scale of miniaturization and integration of semiconductor devices. This is a way to reduce considerably the design time (SHERWANI, 1999).

This research work is related to cell-based design. Cell-based design delivers faster, smaller and less power consuming integrated circuits than those integrated circuits produced by programmable logic or gate array. Nevertheless, cell-based design shows a higher design cost (WESTE, 2006). Compared with full-custom design, cell-based design demands much less man-hours and, therefore, it has a lower cost. Nevertheless, cell-based design generates integrated circuits that may be up to three to seven times more power consuming (CHINNERY, 2005) or three to eight times slower (CHINNERY, 2002) than equivalent integrated circuits designed via full-custom. Even though cell-based design delivers integrated circuits with inferior performance (as compared with full-custom integrated circuits), the market share of this methodology has been steadily increasing.

Full-custom design inherently generates either faster or less power consuming integrated circuits than those generated via cell-based design. This happens because, in the former methodology, a human designer can manually optimize transistor sizing,

placement and routing of devices, even the layout of the circuit. Cell-based design, in its turn, relies on a limited set of options to accomplish the circuit sizing, among other factors that restrain its capacity of generating either faster or less power consuming integrated circuits (HU, 2007).

Cell-based design must deal with discrete sizing of logic gates, since a standard cell library contains a finite number of different sizes for each cell. The problem of choosing, out of a limited number of options, the size of a cell to correspond to a node of a circuit under design is an NP-complete problem (LI, 1993; REZVANI, 2003). Besides, it is likely that the ideally-sized cell to map a given node does not belong to the current standard-cell library.

As a consequence of the factors just mentioned, human intervention in cell-based design became a common practice (ROY, 2005), especially in the nodes that represent a performance bottleneck. This thesis aims specifically at developing a subcircuit sizing method oriented towards on-the-fly cell generation, within the context of local optimization. This sizing method obtains minimum active area solutions, taking into account the maximum input capacitance, the output load to be driven, and the delay constraint. The method is based on the logical effort formulation, and the main contribution is to compute the area derivative to obtain minimum area, instead of making the delay derivative to obtain minimum delay, as it is done in the traditional logical effort formulation.

This thesis is organized as follows. Chapter 2 tackles the fundamental concepts for this research work. In chapter 3, some reference works on digital circuit sizing are shown, as well as concepts intrinsically related to this research. Next, in chapter 4, the subcircuit sizing method is developed. Chapter 5 is devoted to the experimental results obtained with the new sizing method. Finally, chapter 6 brings the conclusion.

#### 2 BASIC CONCEPTS

In this chapter, the basic concepts needed for a better understanding of this thesis will be reviewed. This research work refers to cell-based design methodology, within the broader context of digital integrated circuits. The design of an integrated circuit, from specification to final implementation, is an intricate process that shall be divided into several stages. These stages involve well established concepts and methodologies. Therefore, initially general concepts about digital integrated circuit design will be shown. Based upon these general concepts, cell-based design flow will be tackled, since this methodology came as an answer to the growing complexity of integrated circuit design.

Next section deals with design constraints. When conceiving a digital circuit, there are specifications and design constraints that must be observed in every proposed modification to the circuit. Within design constraints, there are also cost functions that may be associated with a circuit, which are useful for optimization purposes.

After that, the concepts of delay and timing will be seen, since they have foremost importance in digital circuit design. Every digital circuit introduces a delay between its input and output signals. For a digital circuit design to reach its performance goals, these delays must be handled appropriately.

In the same fashion, the concepts regarding sizing of semiconductor devices deserve a section of its own. It is useless to have a very fast circuit that does not respect either area or power consumption limitations, hence the need for adequate sizing.

The final section is devoted to the mathematical tools related to the resolution of the proposed problem. There are different ways to model the digital circuit sizing problem, and for every model there may exist one or more mathematical techniques for its resolution. Grosso modo, these techniques may be divided into mathematical programming and analytical resolution of minimization problems, as reviewed in the end of this chapter.

#### 2.1 General Concepts about Digital Integrated Circuit Design

In this section, concepts referring to integrated circuit design are reviewed. Some of these concepts are consensually defined in the literature, meanwhile others have different definitions according to different authors, and there are even concepts that have not been formally defined in the consulted literature. Therefore, in this section, concepts alluding to integrated circuit design are either reviewed or defined, in a way to conceive a consistent set of definitions to be referred to throughout this work.

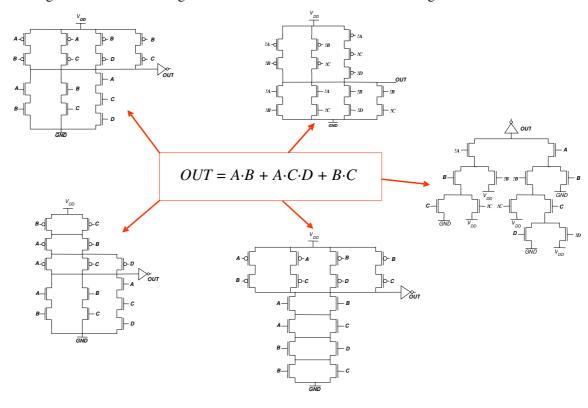

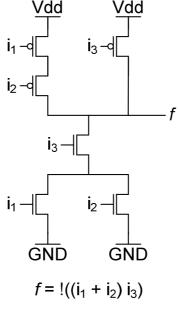

The first concept to be reviewed is that of *logic networks*. Logic gates may be organized into *logic networks*, which are sets of logic gates that implement a non-elementary logic function. A *transistor network* is an array of transistors capable of implementing a logic function, in which these transistors are not necessarily organized into logic gates. For a given logic function, different logic networks and transistor networks may be implemented. Each of these networks may belong to different logic styles (RABAEY, 2003) — also known as circuit families (WESTE, 2006) —, as shown in Figure 2.1. Logic networks and transistor networks differ from each other by logic style and topology. Just to mention two examples, the logic style CSP CMOS — *Complementary Series Parallel* CMOS —is composed of logic gates, meanwhile the *pass transistor* logic style is composed of structures that are not organized as basic logic gates. Therefore, this logic style is based on transistor networks.

This research work deals only with *combinational digital circuits*, i.e., circuits whose outputs are functions exclusively of current inputs. Therefore, these are memoryless circuits.

A concept closely related to logic gate is that of *cell*, although there is a difference between these two concepts: Logic gate refers to the logic function under implementation, its Boolean equation and truth table. In turn, cell alludes to physical aspects of implementation, such as layout, etc. That is, the concept of logic gate is related to logic functionality, meanwhile the concept of cell is related to electrical aspects and physical implementation. For instance, an inverter logic gate may correspond either to a small-sized inverter cell or to an inverter cell capable of driving a large capacitance in its output. In short, according to Gajski-Kuhn's Y diagram (WESTE, 2006), cell belongs to physical domain, and logic gate belongs to structural domain. A cell provides a Boolean logic function (e.g., inverter, AND, NAND, OR, NOR, XOR, XNOR, AOI, OAI, adder, multiplexer) or storage function (latch, flipflop). Therefore, it can be stated that the cell is the basic unit of organization of a digital circuit designed under cell based design.

Cells are conceived by experienced designers, who spend a long time optimizing each cell and taking full advantage of layout properties. Besides, each cell must be verified and characterized individually, which is a time demanding activity. However, once concluded the design, the cell can be reused several times, without need for redesign.

Logic threshold and drive strength are two of the characteristics that define the functioning of a cell. Logic threshold ( $V_{th}$ ), also named input threshold or switching threshold, is the voltage that, when applied to the input of a cell, causes the output voltage  $V_{out}$  to be equal to the input voltage  $V_{in}$  (RABAEY, 2003; WESTE, 2005). Drive strength (or driving strength) is the ability of the cell in charging or discharging a given capacitance in its output. This drive strength is directly related to the size of the transistors in the cell. Logic threshold may be used in the calculation of a cell propagation delay. Drive strength is very important in the sizing of digital integrated circuits, as shown throughout this work.

Usually, cells belong to a *standard cell library* (or cell library). This library is a set of cells with compatible layout template, in which the cells provide different logic functions and storage functions. These cells are used to map a given logic network, according to the cell-based design methodology. Table 2.1 shows an example of a standard cell library.

Figure 2.1 – Different logic and transistor networks for the same logic function

Source: Logics (2013).

Designers find the cell-based design methodology appealing because the power distribution and compatibility among neighbor cells is greatly improved by using a compatible layout template for all cells. This compatible layout template forces the cells to have compatibility with neighbor cells by using power lines ( $V_{DD}$  and GND) at compatible positions, so that placement and routing can be done automatically. Cells are organized in rows, and these rows may be separated one from another by routing channels.

Usually, a standard cell library contains cells with different sizes that implement the same logic function. X1 stands for the minimum sized cell, X2 represents the cell twice as big as X1 cell, and so forth. Larger cells have greater drive strength and therefore are faster, but at the cost of greater power consumption. On the contrary, smaller cells have less drive strength and therefore are slower, but they consume less power.

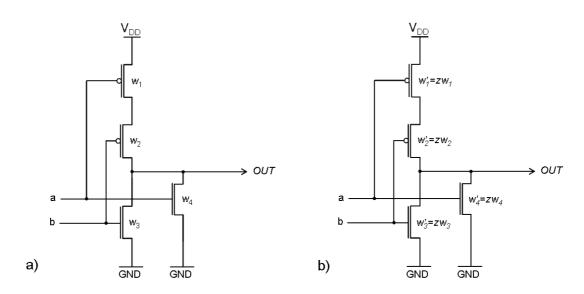

The concepts of template and scale factor are needed for a better understanding of the subject of cell size. The *template* of a cell is the minimum sized version of this cell, which defines the cell topology and the ratio between the sizes of its transistors. Each and every cell obtained from this template has the same topology and the same transistor size ratios. An example of a NOR2 cell template is shown in Figure 2.2a. It is worthy to emphasize that the current concept of template is related to neither layout aspects nor physical implementation aspects. Therefore, the current concept of template shall not be confused with the notion of layout template mentioned in the definition of standard cell library. This latter sort of template refers solely to physical implementation

aspects. Every standard cell in a library has an exclusive layout template, but several cells may have the same template.

Table 2.1 – Example of a standard cell library

| Gate type                         | Variations                                                                                   | Options                                         |

|-----------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------|

| Inverter, buffer, tristate buffer |                                                                                              | 1X, 2X, 4X, 8X, 16X, 32X minimum size inverter  |

| NAND, AND                         | 2-8 inputs                                                                                   | High, normal, low power                         |

| NOR, OR                           | 2-8 inputs                                                                                   | High, normal, low power                         |

| XOR, XNOR                         |                                                                                              | High, normal, low power                         |

| AOI, OAI                          |                                                                                              | High, normal, low power                         |

| Multiplexer                       | Inverting, non inverting                                                                     | High, normal, low power                         |

| Schmitt trigger                   |                                                                                              | High, normal, low power                         |

| Adder, half adder                 |                                                                                              | High, normal, low power                         |

| Latch                             |                                                                                              | High, normal, low power                         |

| Flip-flop                         | D, with and without synch/asynch set and reset, scan                                         | High, normal, low power                         |

| I/O pad                           | Input, output, tristate, bidirectional, boundary scan, slew rate limited, crystal oscillator | Various drive levels (1-16 mA) and logic levels |

Source: Weste (2006, p. 426).

The *scale factor* (BOYD, 2005; HEDLUND, 1987) is the number greater than or equal to 1 that multiplies the widths of the transistors in the template in order to obtain the corresponding cell with the expected drive strength. Figure 2.2 shows two instances of a NOR2 cell: a minimum sized cell (i.e., *template* — Figure 2.2a) and another cell with size z. In this case, the cell depicted in Figure 2.2b has a scale factor equal to z. These two cells have different sizes, but the transistor sizes in each cell keep the same ratio between each other, i.e.,  $w_1: w_2: w_3: w_4$ , where  $w_i$ ,  $i \in \{1, 2, 3, 4\}$ , is the width of every transistor in the template.

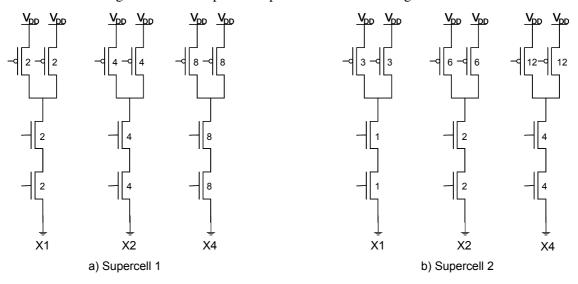

Although the scale factor may in principle assume any value greater than or equal to 1, usually the standard cells in a library have scale factors given by natural numbers. In this work, this set of standard cells in a library, which have the same template and that differ from each other just by their scale factors, is named *supercell*<sup>1</sup>. As examples of supercells, one can mention: a) the supercell constituted by the six inverter cells in the library depicted in Table 2.1; b) the supercell given by the two NOR2 cells in Figure 2.2

<sup>&</sup>lt;sup>1</sup> This definition of supercell is different from the one given by Zhou (2007).

and c) the three supercells depicted in Figure 2.3, each of which is composed by three cells.

Figure 2.2 – Scale factor of a NOR2 cell

Source: Logics (2013).

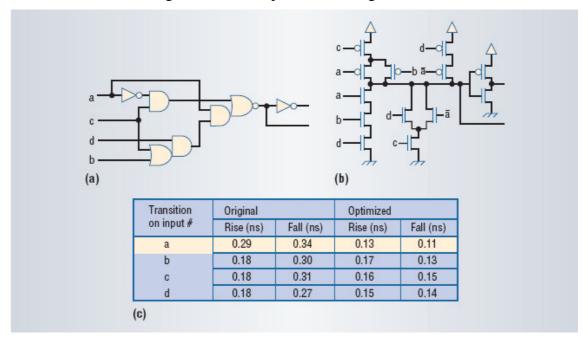

In Figure 2.3, the numbers in each transistor represent the width of the transistor channel (i.e., its size), parameterized with respect to a reference value (e.g., the channel width of the smallest NMOS transistor that can be implemented with the technology). Although the three supercells implement the same logic function, they have different templates. This can be observed in the ratio between PMOS and NMOS transistor sizes in each supercell: in supercell 1, this proportion is equal to 1:1; in supercell 2, it is worth 3:1; and in supercell 3 it is equal to 1:3. This example shows that there may exist standard cells (with the same logic function) that show differences among themselves other than their sizes (drive strengths). In other words, there are standard cell libraries with only one supercell for every logic function implemented, and there are also standard cell libraries with more than one supercell for a given logic function.

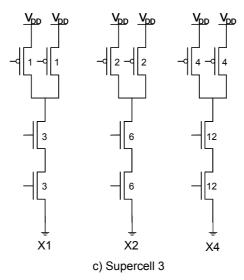

In earlier times, there were a few sizes for every template in a standard cell library. Nowadays, the cell size may vary from X1 to X16. As represented in Figure 2.4, there is a huge difference between an X1 cell and an X16 cell. This difference is reflected in the delay, area, and power consumption of each cell.

With respect to the amount of standard cells, there are libraries ranging from just tens of standard cells (ROSA JUNIOR, 2008) up to thousands of standard cells (SHERWANI, 1999; TRIHY, 2008). Regarding the amount of standard cells in a library, there is a tradeoff that must be respected: the bigger the number of logic functions and the number of different options for every logic function implemented as standard cells, the easier the obtention of a cell with the desired logic function and a close to ideal size for a given node of the circuit under design. However, as more

standard cells are added to the library, the runtime of the cell chooser algorithm increases polynomially and there is also the additional work of designing, verifying, and characterizing extra standard cells. In the literature, there are authors who plead libraries with a few standard cells — e.g., Ricci (2007), Seo (2008) —, and there are also those who defend libraries with many standard cells — e.g., Berkelaar (1988), Correia (2004), Gavrilov (1997), Keutzer (1987), Marques (2007), Scott (1994), Sechen (1996) —, with no consensus whatsoever about this matter.

Figure 2.3 – Examples of supercells for NAND2 logic function

Source: Logics (2013).

All cells in a standard cell library have been previously verified and characterized. Therefore, the designer can take its correct functioning for granted. However, the designer is limited to using in his (her) project only the cells made available by the standard cell library. This is indeed a limiting factor in the cell-based design methodology, which is tackled in this research work.

Technology mapping is the process of expressing a logic network in terms of cells chosen from a standard cell library. Usually, technology mapping aims at the optimized usage of standard cells in order to implement a circuit that obeys given timing constraints, with a minimum area. In its most generic fashion, technology mapping is free to choose both the logic functionality and the size of the standard cells, out of the available sizes in the standard cell library (HU, 2003; KARANDIKAR, 2004). However, in some particular cases, technology mapping just determines the logic functionality of the cells (BERKELAAR, 1988; CORREIA, 2004; MARQUES, 2007) and, in some other cases, technology mapping can choose just the size of the cells (COUDERT, 1997, 2002; HU, 2009).

Figure 2.4 – Current difference in cell sizes

X1

Source: Logics (2013).

The concepts of standard cell, standard cell library, and technology mapping are used in the explanation of cell-based design methodology. Prior to that, however, it is necessary to differentiate the concepts of full-custom circuits, ASIC circuits, and cell-based circuits, since there are in the literature conflicting definitions about this terminology.

There is a strict relationship between the design methodology and the integrated circuit thus produced. By definition, a *full custom circuit* is the one produced via full custom design methodology (also named custom design methodology). A full custom circuit is also named custom circuit. A characteristic of full custom design methodology is to give the designer a wide freedom of action. The designer may conceive each device without interfering in the design of the other devices. If necessary, the designer may act directly into the integrated circuit layout, by manually designing, positioning, and routing the devices. The full custom methodology design is suited for the design of

high performance integrated circuits, such as microprocessors and DSP processors. However, such a high performance is obtained because designers work for a long time in the project, which raises the costs.

The definition of ASIC circuits is somewhat different from the other categories. According to Chinnery (2002), strictly speaking, the expression "Application Specific Integrated Circuit" as well as the acronym ASIC refer to an integrated circuit designed for a particular application. As examples of ASIC circuits, one can cite: an IC for a speaking doll; an IC for military gear; an IC to interface the memory and the microprocessor of a workstation (SMITH, 1997).

There is no consensus in the literature about the utilization and real meaning of the concepts "ASIC circuit", "full custom circuit", and "cell-based circuit". Although the notion of ASIC circuit refers just to the purpose with which a given integrated circuit was conceived – and not to the design methodology used (cell-based design, full custom design etc.) –, most of the times the acronym ASIC refers to an integrated circuit designed via cell-based design methodology (CHINNERY, 2002). This confusion is due to the fact that, according to Sapatnekar (1993-a), cell-based design methodology is the most widely used methodology in the design of ASIC circuits. However, just like there are ASIC circuits conceived via cell-based design methodology, there are also ASIC circuits conceived under full custom methodology. This way, for the sake of coherence, in this research work only cell-based and full custom are referred to henceforth.

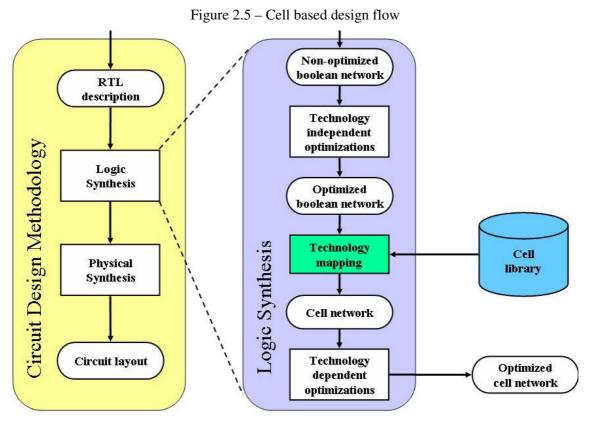

That said, the next topic is the definition of *cell based design methodology*. In this methodology, the circuit under design is mapped to a standard cell library, and the placement and routing are done automatically. Figure 2.5 depicts the cell-based design flow. By *design flow*, it is meant a set of procedures that allow the designer to start from the specification of an integrated circuit and come to the error-free, final implementation of this circuit (WESTE, 2005).

The design starts with its behavioral description in HDL (Hardware Description Language). From this description, logic synthesis generates the circuit netlist, as follows. The RTL (Register Transfer Level) description is interpreted as a Boolean network not necessarily optimized. This network goes through technology-independent optimizations, which use properties of logic functions to generate an optimized Boolean network. Next, technology mapping is done. As result of such mapping, the circuit is now described as a cell network, which goes through technology-dependent optimizations, in order to generate the final, optimized cell network. At this moment, logic synthesis happens: based on the optimized cell network, and on the processes of floorplanning, placement and routing, all the information needed to completely specify the circuit layout is obtained (RABAEY, 2003).

The main objective of cell based design is to reduce implementation costs, by reusing a standard cell library. In this methodology, the cells need to be designed, verified, and characterized only once for a given technology. This is a great advantage of this methodology, because the cells may be reused, thus reducing design cost (RABAEY, 2003). Besides, once the standard cell library is ready to be used, the design time of a new circuit is considerably reduced (as compared with full-custom integrated circuits). The design time is shortened even further, because placement and routing is done automatically in this methodology.

Source: Schneider (2007).

#### 2.2 Design Constraints

Regardless of the design methodology in use, there are design constraints to be taken into account. In terms of engineering design, a *design constraint* refers to a characteristic that the design must possess. According to Design (2008), design constraints are declarations that define the design goals in terms of measurable characteristics of the circuit, such as timing, area, and capacitance. Typically, design constraints state that a circuit must have a delay less than or equal to a given maximum delay, a maximum input pin capacitance (MFI — *Maximum FanIn*), and a given load to be driven by output pin ( $C_{out}$ ).

In this research work, a design constraint is regarded as an objective or characteristic to be attained by the circuit. For instance, if a given circuit path has a delay constraint  $d_1$ , but the circuit is optimized in such a way that this path comes to have a delay  $d_2 < d_1$ , then the delay constraint is updated to  $d_2$ . The same applies to the other design constraints.

Design constraints may also contain directives for the optimization process. These directions point to the costs to be reduced in this process. Usually, some constraints (e.g., maximum input pin capacitance and maximum delay) must be respected, meanwhile some costs (such as area and power consumption) shall be minimized.

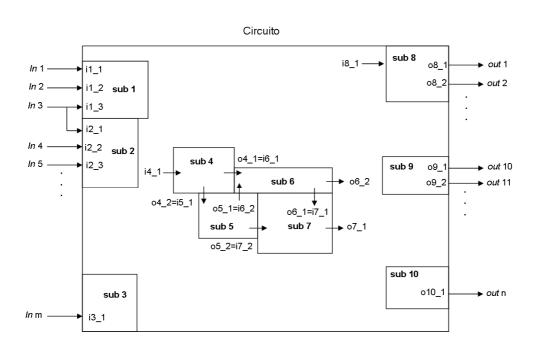

When analyzing or designing a circuit, attention can be focused on a small piece of the global circuit, named subcircuit. Just like the global circuit has global design constraints, each subcircuit has its own local design constraints. In the same fashion as there is a relationship between the subcircuit and the global circuit it belongs to, there is also a relationship between the corresponding global and local design constraints, as depicted in Figure 2.6. The global circuit has m primary inputs  $(in_1, in_2, ..., in_m)$  and n primary outputs  $(out_1, out_2, ..., out_n)$ . Suppose this circuit is divided into subcircuits, out of which ten are emphasized in Figure 2.6. Each subcircuit  $sub_j$  has inputs  $i_{j\_k}$  and outputs  $o_{j\_l}$ , where  $j \in \{1, 2, 3, ..., T\}$ ,  $k, l \in \{1, 2, 3, ..., U\}$ , T is the total number of subcircuits and U is the maximum number of inputs or outputs of the subcircuits.

Figure 2.6 – Local and global design constraints

Source: Logics (2013).

Figure 2.6 shows that there is a strict relationship between the maximum input pin capacitance of the global circuit and the maximum input pin capacitances of the subcircuits in the input of the global circuit. This relationship is expressed in the following set of equations:

$$MFI(in_{1}) = MFI(i_{1_{-1}})$$

(2-1)

$MFI(in_{2}) = MFI(i_{1_{-2}})$

$MFI(in_{3}) = MFI(i_{1_{-3}}) + MFI(i_{2_{-1}})$

$MFI(in_{4}) = MFI(i_{2_{-2}})$

$\vdots$

$MFI(in_{m}) = MFI(i_{3_{-1}})$

The maximum capacitance of the input pin  $in_3$  of the global circuit is given by the sum of the maximum capacitances of two inputs of two subcircuits —  $MFI(i_{1_3})$  and  $MFI(i_{2_1})$  — due to the bifurcation in  $in_3$  that drives these two inputs. The set of

equations (2-1) shows that an alteration in the maximum input capacitance of the global circuit implies the same alteration in the maximum input capacitance of the subcircuit in the input of the global circuit and vice versa. When there is a bifurcation in the input signal, a modification in the corresponding maximum input capacitance of the global circuit may be spread over the maximum input capacitances of one or more subcircuits.

With respect to the load to be driven by the output pins, there is always a biunivocal correspondence between the capacitances of the output pins of the global circuit and the capacitances of the output pins of the subcircuits in the output of the global circuit. Let  $C_x$  be the capacitance of a generic pin x:

$$C_{out1} = C_{o8\_1}$$

(2-2)

$C_{out2} = C_{o8\_2}$

$\vdots$

$C_{out10} = C_{o9\_1}$

$C_{out11} = C_{o9\_2}$

$\vdots$

$C_{out n} = C_{o10\_1}$

The set of equations (2-2) shows that an alteration in the capacitance to be driven by the output pin of the global circuit implies the same alteration in the capacitance to be driven by the output pin of the subcircuit in the output of the global circuit and vice versa.

In its turn, the global design constraint on maximum delay in every path (connecting an input to an output of the global circuit) is equivalent to the sum of the local design constraints on maximum delays of the subcircuits that constitute this global path. An alteration in the global design constraint on maximum delay implies alterations in one or more (or even all) local design constraints on maximum delay. In the same fashion, an alteration in a local design constraint on maximum delay implies the same alteration in the global design constraint on maximum delay. Mathematically speaking, let  $P_x$  be an arbitrary path between an input and an output of the global circuit; let  $d(P_x)$  be the global design constraint on maximum delay of such path. The relationship between the global and local design constraints on maximum delay is given by:

$$d(P_x) = \sum_{i \in P_x} d_i \tag{2-3}$$

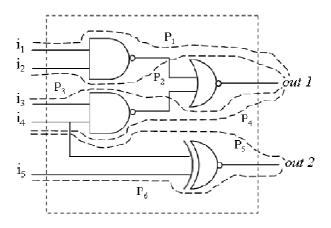

where  $d_i$  denotes the local design constraint on maximum delay of the path within subcircuit i that belongs to global path  $P_x$ . A subcircuit may have several inputs and outputs (as seen in Figure 2.7) and therefore several local design constraints on maximum delay, but for equation (2-3) only the path within subcircuit i that belongs to global path  $P_x$  matters.

Now let us suppose that the global path  $P_x$  has been optimized, its maximum delay has changed from  $d_1(P_x)$  to  $d_2(P_x)$ , where  $d_2(P_x) = d_1(P_x) - \delta$  and  $\delta > 0$ . The outcome of this optimization is a variation  $\delta_i > 0$  on the local design constraint on maximum delay of the subcircuit i that belongs to global path  $P_x$ , so that

$$\sum_{i \in P_x} \delta_i = \delta \tag{2-4}$$

That is, the global path optimization may involve the optimization of one or more subcircuits that belong to such path. In the case of a subcircuit with more than one output, only the path within the subcircuit that belongs to the global path needs to be optimized.

Figure 2.7 – Subcircuit with several paths  $(P_1, P_2, ..., P_6)$  between input and output

Source: Logics (2013).

With respect to power consumption, an alteration in the power consumption of a subcircuit implies the same alteration in the power consumption of the global circuit. As for the area, an alteration in the area of a subcircuit is also reflected in the area of the global circuit, as long as layout aspects of the global circuit do not dim or even nullify this area variation. When the area or power consumption of the global circuit is minimized, this minimization is spread over the subcircuits in a similar way to equation (2-4).

#### 2.2.1 Example of design constraint specification format

The SDC format (Synopsys Design Constraints) is a popular design constraint specification format. Several companies use this format in their EDA (Electronic Design Automation) tools as a means of communicating design intentions (USING).

In SDC format, design constraints are divided in two categories: design rule constraints and optimization constraints (also known as user specified constraints). Design rule constraints are due to the cell-based design methodology. The synthesis tool uses a standard cell library, and for every standard cell in the library there is a set of design rules that must be rigorously obeyed by this synthesis tool. Examples of design rule constraints are:

- Maximum transition time of the cell input signal, also referred to as slew;

- Maximum capacitance: maximum capacitive load that a cell output is capable of driving;

- Cell degradation: some standard cell libraries supply cell degradation tables, which indicate the maximum capacitance that a cell is capable of driving as a function of the transition time of its input signals (SYNOPSYS-b).

Optimization constraints are designer-made specifications that define design intentions such as timing, area, and power consumption. These constraints act as a guide for the synthesis tool to do its task. Examples of optimization constraints are:

- Input and output delays, which restrict the delays of the external paths in the borders of the circuit under design. The input delay specifies the path delay between an external input signal and the first register in the circuit, meanwhile the output delay specifies the delay between the last register in the circuit and its outputs;

- Minimum and maximum path delays, which specify, for every path between an input and an output, its timing constraint;

- Total circuit area (SYNOPSYS-b).

The synthesis tool tries to respect both design rule constraints and optimization constraints, but the former constraints have precedence over the latter ones. That is, some optimization constraints may be sacrificed so that all design rule constraints are met.

Figure 2.8 shows parts of a SDC file for the design of a ripple carry adder (DESIGN COMPILER). In this example, the clock signal has a period of 4 ns, pulse ratio 50/50, uncertainty 0.1 ns, latency 0.2 ns, and transition time 0.1 ns. The commands (attributes) set\_dont\_touch\_network, set\_dont\_touch, and set\_ideal\_network are directives for the design. The command set\_driving\_cell specifies the cells that drive the adder. The command set\_load specifies the load that must be driven by the adder. The commands set\_input\_delay and set\_output\_delay specify the time the input signal takes to arrive at the adder input and the time it takes to pass through the external block until the end of the logic path. The difference between these two delays is the amount of time available for the adder internal logic. Finally, the last design constraint sets the maximum area allowed for the design.

Figure 2.8 – Example of part of SDC file

```

create_clock -name "clk" -period 4 -waveform {0 2} {clk}

set_clock_uncertainty 0.1 clk

set_clock_latency 0.2 clk

set_clock_transition 0.1 clk

set_dont_touch_network clk

set_dont_touch rst_n

set_ideal_network rst_n

set_driving_cell -library umcl18g212t3_tc_180V_25C -lib_cell

HDDFFPB1 -pin Q [get_ports a]

set_driving_cell -library umcl18g212t3_tc_180V_25C -lib_cell

HDINVD1 -pin Z [get_ports b]

set_load [load_of umcl18g212t3_tc_180V_25C/HDDFFPB1/D]

[get ports s]

set_input_delay 0.67 [get_ports b] -clock clk

set_output_delay 0.5 [get_ports s] -clock clk

set_max_area 1000

```

Source: DESIGN COMPILER.

#### 2.3 Delay

In this section, the concepts related to signal propagation delay in digital integrated circuits are seen. Regardless of the logic path implemented as a digital integrated circuit, there is always a delay between the input and output signals, due to the electrical charge propagation through resistive and capacitive components of the circuit. In its current stage of miniaturization, microelectronics industry delivers integrated circuits with transistors whose channel length is equal to 22 nm (e.g., processors Intel Core i5 and i7). Regarded as semiconductor switching devices, these transistors change state very quickly, thanks to their tiny dimensions. Therefore, these devices can deliver a very high maximum operation frequency. However, for an integrated circuit to reach a good effective operation frequency, signal propagation delay in this circuit must be kept under control. The concepts related to delay and timing are seen in this section. Three delay models are also reviewed, namely, Elmore delay model, the gain-based logical effort delay model and the nonlinear delay model (NLDM). Elmore delay is a classic model, still used in recent sizing algorithms — e.g., Hu (2007) —, meanwhile the logical effort delay model was adopted in this research work. The NLDM is mentioned as an example of an empirical model, for the sake of comparison with the former models, which are theoretical delay models.

#### 2.3.1 Fundamental concepts

The first concept worth mentioning is *transition time*, which encompasses the concepts of *fall time* ( $t_f$ ) and *rise time* ( $t_r$ ). In this research work, fall time corresponds to the time a waveform takes to fall from 90% to 10% of its steady value. In its turn, rise time corresponds to the time a waveform takes to rise from 10% to 90% of its steady value.

The second concept is propagation delay  $(t_d)$  — or delay (SAPATNEKAR, 2004), for short —, which is defined in this research work as the maximum time interval which starts when the input signal (whose transition causes a transition in the output) reaches  $V_{DD}/2$  to the time the output signal reaches the same voltage  $V_{DD}/2$ .  $V_{DD}$  is the supply voltage, corresponding to logic level 1.

Since the propagation delay uses to be different for rise and fall transitions of the output signal of the cell, there are two distinct propagation delays: tdlh — *delay time low to high* and tdhl — *delay time high to low*, respectively.

The arrival time (AT) denotes the time a signal takes to propagate from the primary inputs until a given node. In its turn, the required time (RT) represents the time the signal must arrive at a given node, so that the local delay design constraint is satisfied. The slack S is defined as:

$$S = RT - AT \tag{2-5}$$

The *critical path* of a circuit is the logic path between a primary input and a primary output that shows the largest delay.

Timing analysis consists in computing the delay in a path of a digital circuit, in order to verify if the timing constraints imposed by the remaining of the circuit are satisfied (NOWE, 2003). Timing closure represents the timing analysis of an entire circuit (RABAEY, 2003). When a circuit path does not comply with the timing constraints, it is said that a timing violation occurs.

Theoretical delay model denotes the closed form equationing that gives the propagation delay of a logic gate, based on the electrical description of this gate. For instance, there is the Elmore delay model (ELMORE, 1948) and the logical effort delay model (SUTHERLAND, 1999). Besides these theoretical (physical) delay models, there are also empirical delay models, based upon experimental data. Initially, the theoretical delay models are reviewed.

#### 2.3.2 Elmore delay model

The Elmore delay model is a classic method for estimating the delay in circuits, when the circuit is excited by a step function. It is a not very precise model, in which the delay is computed on RC networks, and transistors are modeled as resistances. The propagation delay  $(t_d)$  for the response of the circuit to this step function may be approximated by the first momentum of the response of the circuit to the impulse function:

$$t_d = \int_0^\infty t e'(t) dt \tag{2-6}$$

where: t – time.

e(t) – response of the circuit to the step function.

e'(t) – derivative of the response of the circuit to the step function (i.e., response of the circuit to the impulse function).

This is the formal definition of the Elmore delay. Obtaining the response of a circuit to the impulse function, as defined, may be an arduous task. Nevertheless, when the objective is to evaluate the delay in an *RC* tree, the Elmore delay becomes friendlier. According to Rubinstein (1983) and Sapatnekar (2004), an *RC* tree – depicted in

Figure 2.9 – is a connection of resistors structured as a tree, with two restrictions: a) a capacitance connected to any node in the tree must be grounded; and b) there is no resistor grounded. An RC tree thus defined shows two fundamental characteristics: there are no resistive loops and, if a node other than the ground is the input, then there is only one path from this input node to any other non-ground node in the tree. Besides, if two RC trees with the same ground are connected by a non-ground node, then they form a new RC tree.

The Elmore delay in node  $n_i$  of an RC tree may be obtained as follows. Let  $P_i$  the path between input node  $n_0$  and  $n_i$ , which may be any tree node other than ground and input node. Analogously, let  $P_j$  be the path between  $n_0$  and a node  $n_j$ . Let  $P_{ij} = P_i \cap P_j$  be the part of the path between  $n_0$  and  $n_i$  that is common with the path between  $n_0$  and  $n_j$ . For convenience of notation,  $P_{ij}$  also denotes the set of resistances that belong to the path  $P_{ij}$ . The Elmore delay between the input node  $n_0$  and the node  $n_i$  of the RC tree is given by:

$$T_{D_i} = \sum_{j=0}^{n} C_j \sum_{k \in P_i} R_k \tag{2-7}$$

Figure 2.9 – Example of RC tree

Source: Sapatnekar (2004).

For example, in

Figure 2.9:

$$T_D(n_4) = R_1 C_1 + (R_1 + R_2)C_2 + (R_1 + R_2)C_3 + (R_1 + R_2 + R_4)C_4 + (R_1 + R_2 + R_4)C_5 + R_1 C_6 + R_1 C_7 + R_1 C_8$$

(2-8)

$$T_D(n_8) = R_1 C_1 + R_1 C_2 + R_1 C_3 + R_1 C_4 + R_1 C_5 + (R_1 + R_6) C_6 + (R_1 + R_6 + R_7) C_7 + (R_1 + R_6 + R_7 + R_8) C_8$$

(2-9)

#### 2.3.3 Logical effort delay model

The logical effort (LE) delay model is a gain-based model, which emphasizes the linearity between delay and gain (i.e., the ratio between the input and output capacitances) in a given logic gate. This model has been used in several papers – e.g., Boyd (2005), Hu (2003), Joshi (2008), Karandikar (2004; 2005; 2008), Rezvani (2003), and Zeydel (2006).

The model expresses the delay of a logic gate as a function of four parameters, which are defined and explained along the deduction of the model:

- $-\tau$ : characteristic delay of the given technology;

- g: logical effort of the gate;

- h: electrical effort of the gate;

- p: parasitic (intrinsic) delay of the logic gate.

What matters now is that these four parameters allow the designer to obtain the delay of any logic gate in a quick, straightforward way. Besides, the logical effort differentiates the parasitic delay p (due to the intrinsic parasitic capacitances of the logic gate) from the delay due to the load driven by the logic gate (electrical effort h) and from the delay due to the topological characteristics of the logic gate (logical effort g).

This way, it becomes easy to realize the contribution of each of these factors to the total delay of the logic gate. Next, the logical effort is deducted, which better explains the four parameters previously mentioned. Examples of obtaining the parameters logical effort (g) and parasitic delay (p) for basic logic gates are also given.

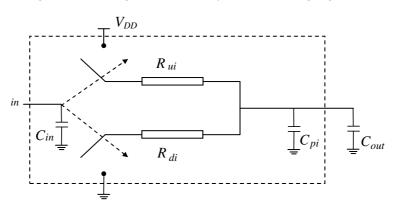

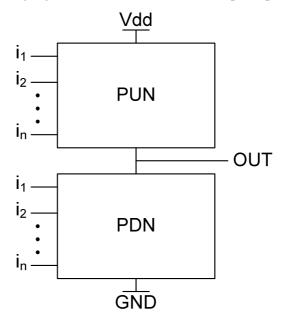

According to Sutherland (1999), a single-input logic gate is modeled according to Figure 2.10.  $C_{in}$  represents the capacitance of each input of the logic gate.  $C_{in}$  is given by the sum of the gate capacitances of the transistors whose gates are connected to such input.  $C_{pi}$  denotes the intrinsic parasitic capacitance of the logic gate.  $C_{pi}$  is given basically by the sum of the drain capacitances of the transistors whose drains are connected to the output of the logic gate. The capacitance to be driven by the logic gate is named  $C_{out}$ .

Figure 2.10 – Logical effort delay model of a logic gate

Source: Sutherland (1999).

When the pull-up key is closed, the pull-up network offers a resistance  $R_{ui}$  to the current between  $V_{DD}$  and the logic gate output. When it is the turn for the pull-down key to be closed, the pull-down network offers a resistance  $R_{di}$  to the current between GND and the logic gate output (The concepts of pull-up and pull-down network are explained in section 3.2). To keep the model simple, it is assumed that  $R_{ui} = R_{di} = R_i$ , so that the logic gate has equal  $t_r$  and  $t_f$ .

In order to assure that  $R_{ui}$  is indeed equal to  $R_{di}$ , it suffices to use the convenient  $\gamma$  parameter for the technology, where  $\gamma$  is the ratio between the channel width of the PMOS transistor  $(w_p)$  and the channel width of the NMOS transistor  $(w_n)$  in a minimum sized inverter:

$$\gamma = w_p / w_n \tag{2-10}$$

The logical effort model uses the parameters  $C_{in}$ ,  $C_{pi}$ ,  $C_{out}$ , and  $R_i$ , along with the concepts of template and scale factor of a logic gate seen in section 2.1, to determine the delay of a generic logic gate, with arbitrary size and topology. In order to obtain the transistor sizes of a generic logic gate, the size of each transistor in the corresponding template is multiplied by a convenient scale factor x. The template of the logic gate in Figure 2.10 has input capacitance  $C_t$ , intrinsic parasitic capacitance  $C_{pt}$  and pull-up/pull-

down resistance  $R_t$ . The logic gate parameters and the corresponding template parameters obey the following relationship:

$$C_{in} = xC_t \tag{2-11}$$

$$C_{pi} = xC_{pt} \tag{2-12}$$

$$R_i = x^{-1} R_t (2-13)$$

According to Sutherland (1999), the absolute delay ( $d_{abs}$ ) of the logic gate depicted in Figure 2.10 is given by:

$$d_{abs} = kR_i (C_{out} + C_{pi}) (2-14)$$

where k is a dimensionless constant, that is specific to the used technology. Let:

$$\tau = kR_{inv}C_{inv} \tag{2-15}$$

$$g = \frac{R_t C_t}{R_{inv} C_{inv}} \tag{2-16}$$

$$h = \frac{C_{out}}{C_{in}}$$

(2-17)

$$p = \frac{R_t C_{pt}}{R_{inv} C_{inv}} \tag{2-18}$$

where:

- $R_{inv}$  is the *pull-up/pull-down* resistance of the minimum-sized inverter (i.e., inverter template);

- $C_{inv}$  is the input capacitance of the minimum-sized inverter;

- $\tau$  is the characteristic delay of the used technology;

- g is the logical effort of the logic gate;

- h is the electrical effort of the logic gate;

- p is the parasitic delay of the logic gate.

Rewriting equation (2-14) as a function of (2-11), (2-12), (2-13), (2-15), (2-16), (2-17), and (2-18), we have:

$$d_{abs} = \tau(gh + p) \tag{2-19}$$

The logical effort g depends solely on the topology of the logic gate; it does not depend on the size of this logic gate. The logical effort expresses how much the logic gate is inferior to the minimum sized inverter of the same technology in delivering output current. By definition, the logical effort of an inverter is equal to 1. The electrical effort gives the ratio between the fanout and the fanin of the logic gate. Therefore, the electrical effort depends on the size of the logic gate and also on the load that it must drive.

The parasitic delay p is so called because it represents the delay due to the intrinsic parasitic capacitance  $C_{pt}$  of the logic gate. In the hypothetical situation of the logic gate driving no load whatsoever (h = 0), the delay is equal to p. The parasitic delay p denotes how much the parasitic delay is greater in a generic logic gate than the parasitic delay of the minimum inverter in the given technology. There is no relationship between the size

of the logic gate and its parasitic delay, since this delay depends only on the topology of the logic gate.

From equation (2-19), one can see that the characteristic delay  $\tau$  may be understood in two different ways: 1)  $\tau$  is the delay of an inverter with no intrinsic parasitic capacitance (p=0) driving an identical inverter; or 2)  $\tau$  is the delay of a loadless inverter whose transistors have gate capacitances equal to the drain capacitances. The absolute delay  $d_{abs}$  may be parameterized as a function of  $\tau$ :

$$d_{abs} = d\tau \tag{2-20}$$

This parameterization is useful for comparing the dimensionless relative delay d of circuits developed in different technologies.

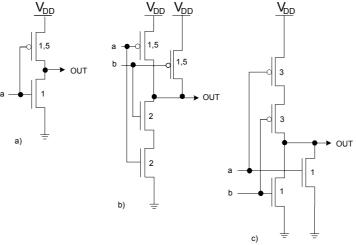

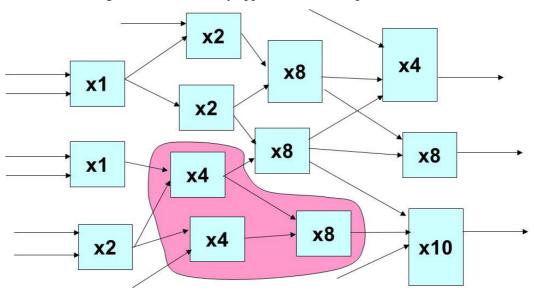

According to Sutherland (1999), there are two rules to determine the logical effort g and the parasitic delay p of a logic gate. The first rule refers to the parameter  $\gamma$ , which is obtained based upon the inverter;  $\gamma$  gives the relative sizes of PMOS and NMOS transistors, and it is valid for all logic gates in a given technology. The second rule refers to series transistors, connected between the output of the logic gate and either  $V_{DD}$  or GND. If there are n series transistors, then each one must be n times bigger than a single transistor, in the same situation. Figure 2.11 exemplifies this procedure for three basic logic gates.

Figure 2.11 – Examples of basic logic gates modeled according to logical effort

Source: Logics (2013).

For the technology used in Figure 2.11, parameter  $\gamma$  is equal to 1.5. Therefore, the inverter (Figure 2.11a) has input capacitance  $C_{in\_INV}$  equal to 2.5. The logical effort g of the inverter is equal to 1. Parasitic delay p is also equal to 1, as long as the transistors have equal gate and drain capacitances.

In the NAND2 logic gate (Figure 2.11b), the PMOS transistors have the same size as the PMOS transistor in the inverter. However, the two NMOS transistors are in series and, therefore, they must have twice the size of the NMOS transistor in the inverter.

Thus, input capacitance  $C_{in\_NAND2}$  is equal to 3.5. The logical effort g is equal to 1.4 ( $g = C_{in\_NAND2}/C_{in\_INV}$ ) and the parasitic delay p is equal to 2 (there are two PMOS transistors and one NMOS transistor connected to the output of the logic gate).

In the NOR2 logic gate (Figure 2.11c), the PMOS transistors are in series and have twice the size of the PMOS transistor in the inverter. The input capacitance  $C_{in\_NOR2}$  is equal to 4, the logical effort g is equal to 1.6 and the parasitic delay is equal to 2.

The logical effort delay model is very simple and easy to use. It is especially well suited for sizing for minimum delay. Nevertheless, its simplicity causes inaccuracy. This model assumes that the gate and drain capacitances of a transistor are equal, but in fact the gate capacitance uses to be greater than drain capacitance. This issue may be solved via model calibration (SUTHERLAND, 1999). Besides, the sizing of series transistors does not take into account the velocity saturation of carriers. This phenomenon is more evident in NMOS transistors, since electrons have a greater mobility than holes. Moreover, series transistors are less prone to showing this phenomenon than single transistors. Therefore, series transistors, especially NMOS transistors, must have a smaller size than that predicted by logical effort. An adequate calibration solves this problem.

Furthermore, the logical effort model computes the delay of a logic gate regardless of the transition time of the input signal. This behavior does not correspond to the real world, since a logic gate shows different delays for different transition times of the input signal. Besides, the logical effort model makes no distinction whatsoever between the transition time in the output of a logic gate and the propagation delay of this logic gate. These problems were solved by Lasbouygues (2006). Other papers also extended the logical effort delay model — e.g., Kabbani (2005) and Keane (2006).

#### 2.3.4 Nonlinear Delay Model – NLDM

The nonlinear delay model (NLDM) is mentioned here as an example of an empirical delay model, in order to show the differences with respect to theoretical (Elmore and logical effort) delay models. This research work is based upon the logical effort delay model, since both mathematical programming techniques and analytical solution of the minimization problem are well suited for solving a problem modeled this way.

The NLDM model, introduced by Synopsys and embodied by the Liberty format (SYNOPSYS-a), consists in a discrete lookup table (LUT) filled by pre-characterization, which gives the delay and the output transition time of a generic cell as a function of both the transition time of the input signal and the output load of this cell. For values of transition time of the input signal and of output load that do not belong in the table, an interpolation is done. A lookup table is empirically constructed for every standard cell in the library.

By construction, the NLDM model is exact in the points of transition time of the input signal and output load in which the table was built. It is an accurate model, but its complexity turns out the simulation of the logic gates to be very slow. The NLDM model demands a high computational effort to simulate the standard cells in order to build the lookup tables, especially during the characterization of these cells (TRIHY, 2008).

There is no consensus in the literature as to which delay model (theoretical or empirical) is the most appropriate one. Even though there is a survey showing that lookup-table based models are more accurate than theoretical models (MARTINEZ apud COUDERT, 1996-b), the interpolation done in the former models may generate inaccurate delay values.

#### 2.3.5 Delay models comparison

Theoretical and empirical delay models have different characteristics and objectives. These differences make each category of delay model more suitable for a specific stage of the industrial design flow, as it is explained next.

Timing analysis is performed twice in an industrial design flow. Initially, an early timing estimation is done. This early timing estimation must be fast enough so that it can be used in the initial sizing of complete circuits, even though it is not sufficiently accurate for timing closure. Theoretical delay models such as Elmore and logical effort delay models are well suited for such early timing estimation.

In a later stage of the industrial design flow, the back-end timing estimation is accomplished. It is too slow for the initial sizing of complete circuits, but its accuracy allows it to be used for timing closure. Empirical delay models are appropriate models for this back-end timing estimation. In fact, the NLDM model is currently the industry standard delay model for timing closure.

#### 2.4 Sizing

Circuit sizing is accomplished in order to determine the size of the components of the circuit, aiming at optimizing a given objective function, and always respecting the design constraints. Within the scope of this research work, the goal is to minimize the active area of the circuit, respecting the maximum delay, maximum input pin capacitance, as well as the load to be driven in each output pin. Depending on the case, the delay constraint may be reduced, and a new sizing is done so that all design constraints are fully respected.

Sizing is of foremost importance in the design flow of digital integrated circuits, since it guarantees that the circuit is conceived within the specifications and required design constraints. More than that, an adequate sizing is capable of delivering an optimized version of the circuit, with more demanding design constraints. In this section, the concept of sizing is introduced. Examples and more details about sizing algorithms and methods are seen in chapter 3.

Transistor sizing is the first type of sizing. In it, each transistor in a logic gate (or in a circuit as a whole) can have its size modified individually, without necessarily provoking modifications in the size of the remaining transistors in the logic gate (or in the circuit). Transistor sizing uses to be employed for sizing standard cells in a library. Based on this sizing, a table of transistor sizes is generated. Then, this table is used for obtaining the template of each standard cell in the library. Transistor sizing was used in Kung (1999), Roy (2007), and Shah (2006).

Once the transistor sizing is done, the next step is cell sizing. This latter sizing aims at determining the size of a cell that is used to map a circuit node. This means to find the scale factor that will be applied to each transistor in the cell template, in order to

obtain the cell with the desired size. In cell sizing, the sizes of all transistors in the cell are multiplied by the found scale factor. For the sake of compatibility with the terminology adopted in the literature, the expressions 'cell sizing' and 'gate sizing' are used indistinctively in this research work.

Sizing may also be classified with respect to its scope, which may be either global or local. In global sizing, the circuit as a whole is sized. This can be done via either transistor sizing or cell sizing. Transistor sizing offers considerable freedom to the designer, since the size of each transistor can be adjusted to the design needs. This is the sizing used in full custom design. However, technological progress fosters the miniaturization and integration in the microelectronics industry, leading to an increase in the number of transistors in a circuit. The complexity of sizing transistors individually grows the same way. Consequently, cell sizing becomes more and more relevant. This kind of sizing handles circuits of high complexity, but this is accomplished at the expense of a lesser sizing granularity: it is impossible to change the size of a single transistor in one cell without changing the size of all the other transistors in the same proportion.

In Joshi (2008), it is proposed a global sizing method that is capable of optimizing a circuit with more than one million logic gates, always finding the global optimum for the circuit. Nevertheless, this huge scale is achieved at the expense of using an inaccurate delay model, which might compromise the optimality of the solution. In order to achieve a high accuracy, local sizing must be used. In local sizing, only a small part (subcircuit) of the circuit is sized. Since there are fewer components to be sized, a more accurate delay model may be used. Global and local sizing may be used in a complementary way. Initially, the entire circuit is globally sized, generating a first version of the circuit. Then, this version of the circuit is optimized, one subcircuit at a time, via local sizing.

Local sizing is advantageous when it is known beforehand that the circuit has just a few specific bottlenecks, in which design constraints are not met. In this case, there is no need to resize globally the entire circuit, it suffices to attack the problematic parts. Local sizing is part of the wider concept of local optimization, which is better explained in the coming chapter.

A third criterion to classify the sizing techniques refers to the way the transistor dimensions can vary. In continuous scale sizing – or just continuous sizing –, the transistor size is free to assume any calculated value. In discrete scale sizing – or discrete sizing, for short –, the transistor sizes cannot assume an arbitrary value, but just one out of a finite set of allowed values.

Discrete sizing is used in cell-based design. In this case, the designer (or CAD tool) is aware, e.g., that the standard cell library contains a given cell with drive strength 1X, 2X, and 4X. Therefore, when sizing a circuit, the designer (CAD tool) is aware that, in a given node, this cell may have drive strength 2X or 4X, but never an intermediate value. Based on this knowledge, the sizing of this node generates a value close enough either to 2X or 4X.