## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

### GUSTAVO GIRAO BARRETO DA SILVA

## **Resource-Aware Clustering Design for NoC-based MPSoCs**

Thesis presented in partial fulfillment of the requirements for the degree of Doctor in Computer Science

Prof. Dr. Flávio Rech Wagner Advisor

Porto Alegre 2014

## CIP – CATALOGAÇÃO NA PUBLICAÇÃO

Silva, Gustavo Girão Barreto da

Resource Aware Clustering Design for NoC-based MPSoCs [manuscrito] / Gustavo Girão Barreto da Silva. – 2014.

146 f.:il.

Orientador: Flávio Rech Wagner.

Tese (doutorado) — Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação. Porto Alegre, BR — RS, 2014.

1.Multiprocessors. 2.Networks-on-chip. 3.Cluster. 4. Resource Management. 5.Parallel Programming. 6.Reliability I. Wagner, Flávio Rech. II. Título.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento

Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb

Coordenador do PPGC: Prof. Luigi Carro

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

### **AGRADECIMENTO**

Agradeço, primeiramente, à minha mãe que sempre me apoiou em tudo que eu fiz e principalmente nos meus estudos. Ela sempre foi meu porto seguro quando precisei e nunca imaginou, por um segundo sequer, que eu não seria capaz de alcançar qualquer objetivo que eu tivesse planejado.

Agradeço a meu irmão e minha cunhada que me deram palavras de encorajamento em momentos que me senti sem ânimo. Também preciso agradecer à minha namorada Patrícia que foi presença constante nos momentos finais (porém fundamentais) do desenvolvimento desta tese .

Agradeço muito ao meu orientador Flávio Rech Wagner que cumpriu com perfeição seu papel. Em alguns momentos deste doutorado estive à deriva e não conseguia achar um direcionamento. Ele foi responsável por me guiar nestas horas e me fazer enxergar novamente meus objetivos. Sei que dei muito trabalho e mesmo assim ele nunca desistiu de mim. Por isso, sou muito grato.

Durante o doutorado é natural que muitas pessoas tenham contribuído, diretamente ou não, para sua realização. Não serei capaz de citar todas as pessoas que me ajudaram neste longo caminho mas quero que saibam que todas foram lembradas na finalização deste trabalho. Sua ajuda foi fundamental para me motivar a concluir esta jornada e para que a mesma não fosse em vão.

Não poderia ter feito este trabalho sem o apoio (científico ou não) de colegas do LSE como Monica Pereira, Ronaldo Ferreira, Daniel Barcelos, Mateus Rutzig, Tomás Moreira, Ulisses Brisolara, Thiago Santini, Leonardo Kunz, Gabriel Nazar, Márcio Oliveira, Marco Wehrmeister, entre outros. Vocês, mais do que outras pessoas, sabem o quanto este caminho é cheio de obstáculos e, por vezes, pouco reconhecido. A minha gratidão pelo companheirismo de vocês é algo ficará para sempre.

Last, but not least, I would like to express my appreciation for all members of the Dutt Research Group (Dr. G!): Abbas, Danny, Hossein, Jan, Trent, Santanu, Soo, Codrut and Prof. Dutt. You all contributed immensely for my work and also made me feel very welcomed inside and outside the campus. It was a great experience because of you. Thank you very much!

Obrigado.

## Projeto de MPSoCs baseados em NoC utilizando Clusterização e Gerenciamento de Recursos

### **RESUMO**

Atualmente, o paradigma multicore é uma tendência fortemente estabelecida também na área de sistemas embarcados. O grau de paralelismo provido por tal arquitetura tem sido a principal causa de avanços de performance na área além de economia de energia e potência. Entretanto, para obter paralelismo eficiente desta arquitetura não é uma tarefa simples. Assim, desenvolvedores propuseram diversos modelos de ambientes de programação tentando prover o máximo de transparência possível. No nível do hardware, este crescente aumento no número de componentes dentro chip cria um problema de gerenciamento a ser tratado. No contexto deste cenário complexo, esta tese propõe o uso de abordagens de gerenciamento de recursos para aumentar a eficiência, levando em consideração tanto performance quanto consumo de energia, de ambientes MPSoC em diferentes níveis. Além disso, estas abordagens tem em comum a noção de clusterização, a qual tenta agregar recursos logicamente de as demandas da aplicação. Primeiramente no processador/aplicação, é proposto um hardware dinamicamente adaptável para suportar modelos de programação paralelos distintos sem nenhum sobrecusto computacional uma vez que todo o processo é completamente transparente para o programador. Ainda neste ambiente, onde aplicações distintas podem ser executadas, é proposto um mecanismo de escalonamento visando gerenciamento de recursos para aumentar a performance chamado Processor Clustering. São propostas quatro diferentes políticas de mapeamento de recursos que tiram vantagem de aspectos distintos da natureza paralela das aplicações e das restrições arquiteturais do sistema. Entretanto, algumas aplicações tem demandas de memória mais altas do que demandas computacionais. Logo, uma abordagem similar pode ser utilizada no nível da hierarquia de memória. Neste caso, o objetivo é redistribuir recursos de memória de acordo com as demandas da aplicação. Redistribuição de memória é explorada tanto em tempo de projeto quanto em tempo de execução. Um mecanismo de mapeamento de distribuição é proposto baseado na quantidade de requisições de acesso à memória externa. Finalmente, é proposto um mecanismo de tolerância à falhas baseado em gerenciamento de recursos para memórias distribuídas dentro do chip em NoCs. É introduzido um modelo de Reliability Clustering que tira proveito da infraestrutura da NoC. Neste caso, os roteadores tem conhecimento dos blocos com falhas e blocos redundantes. Baseado neste conhecimento, o mecanismo é capaz evitar altas latências de acesso à memória.

**Palavras-chave:** Multiprocessadores, Redes-em-Chip, Cluster, Gerenciamento de Recursos, Programação Paralela, Confiabilidade.

## **Resource-Aware Clustering Design for NoC-based MPSoCs**

### **ABSTRACT**

The multicore paradigm is a solid trend nowadays, also in the field of embedded systems. The degree of parallelism provided by such architecture has been the foundation of performance advancements in the field as well as for power and energy savings. However, to obtain efficient parallelism of such architecture is not an easy task. Therefore, developers come up with several proposals of programming environments trying to provide as much transparency as possible. On the hardware side, this increasing number of on-chip components creates a management issue to be handled. In the context of this complex scenario this thesis proposes the use of resource management approaches to improve the efficiency, regarding both performance and energy consumption, of MPSoC environments at different levels. Also, these approaches have in common the notion of clustering, which tries to logically aggregate resources according to application demands. First, at the processor/application level, we propose a dynamically adaptable hardware to support distinct parallel programming models at no computational overhead, since the entire process is completely transparent to the programmer. Also, in this environment, where distinct applications can be executed, we propose a resource-aware scheduling mechanism to improve performance named Processor Clustering. We propose four different resource mapping policies that leverage on distinct aspects of the parallel nature of the applications and on architecture constraints. However, some applications have higher memory demands than computational demands. Therefore, a similar approach can be used at the memory level. In this case, we aim at redistributing memory resources according to application demands. We explore memory redistribution at both design time and runtime and propose a distribution mapping mechanism based on the amount of off-chip memory requests. Finally, we propose a resource-aware fault-tolerance mechanism for distributed on-chip memories in NoCs. We introduce a Reliability Clustering model that leverages on the NoC infrastructure. In this case, the routers have knowledge of faulty blocks and redundancy blocks and, based on that, they are able to avoid higher memory access latency.

**Keywords:** Multiprocessors, Networks-on-Chip, Cluster, Resource Management, Parallel Programming, Reliability.

# **LIST OF FIGURES**

| Figure 1.1 Characteristics of main parallel programming models.               | . 18 |

|-------------------------------------------------------------------------------|------|

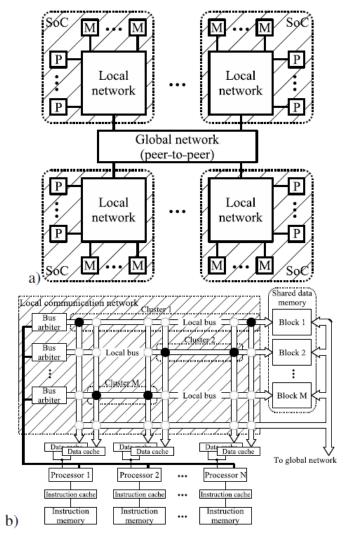

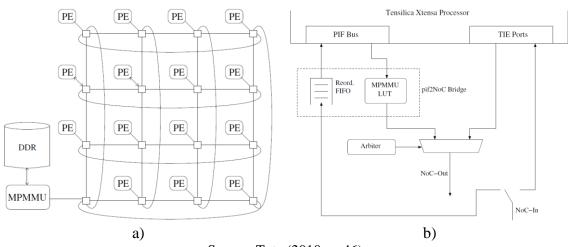

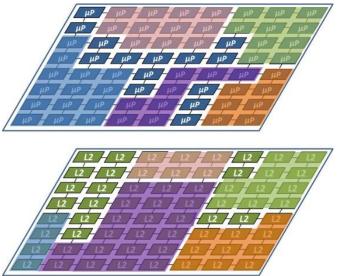

| Figure 2.1. Overall System Architecture and structure of a single SoC         | . 26 |

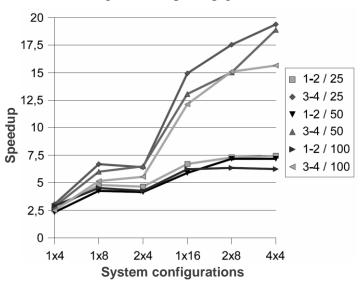

| Figure 2.2. Speedup gains                                                     | . 27 |

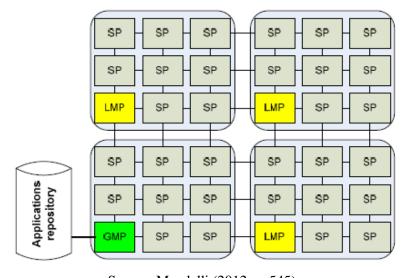

| Figure 2.3. Clustered NoC-based MPSoC.                                        | . 28 |

| Figure 2.4. Cluster-based MPSoC with hybrid interconnection                   | . 31 |

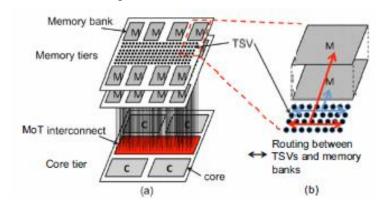

| Figure 2.5. 3D cluster using a Mesh-of-Trees architecture and TSV channels    | . 31 |

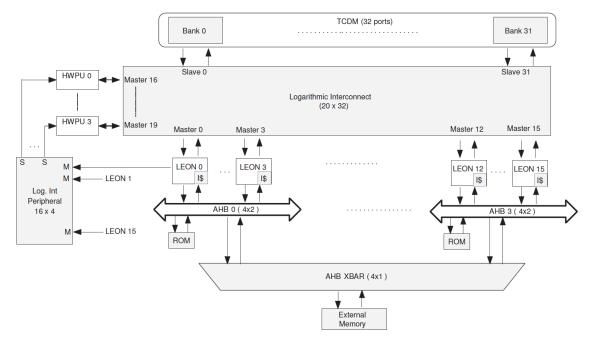

| Figure 2.6. Mega-leon Architecture.                                           | . 32 |

| Figure 2.7. Mesh-of-Trees 2x4 example.                                        | . 32 |

| Figure 2.8. Clustered MPSoC.                                                  | . 33 |

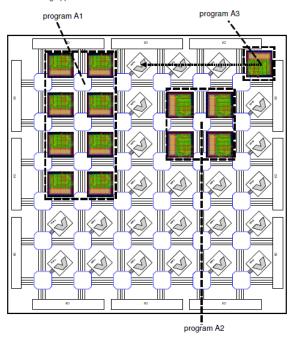

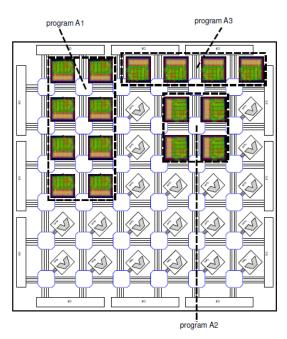

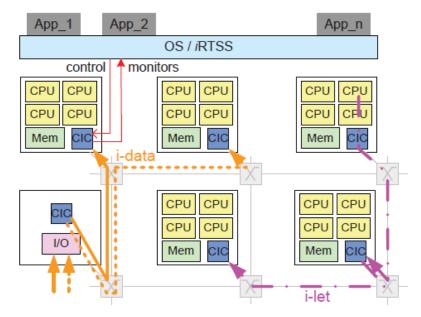

| Figure 2.9. Invasive multi-processor architecture.                            | . 34 |

| Figure 2.10. TCPA scenario before invasion.                                   | . 35 |

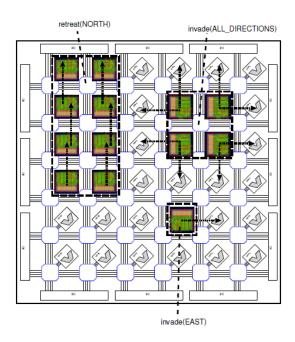

| Figure 2.11. TCPA scenario after invasion.                                    |      |

| Figure 2.12. Uni- and Multi-directional invasions and Retreat operation       |      |

| Figure 2.13. Invasive computing on loosely-coupled MPSoCs.                    |      |

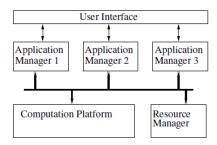

| Figure 2.14. System setup.                                                    |      |

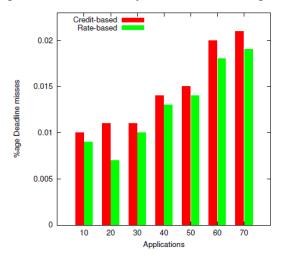

| Figure 2.15. Scalability of resource managers.                                | . 40 |

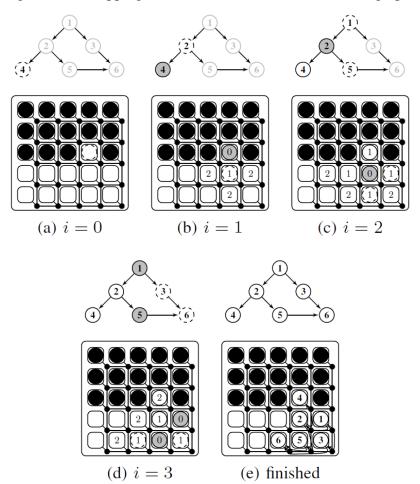

| Figure 2.16. Mapping state after each iteration of the task graph.            |      |

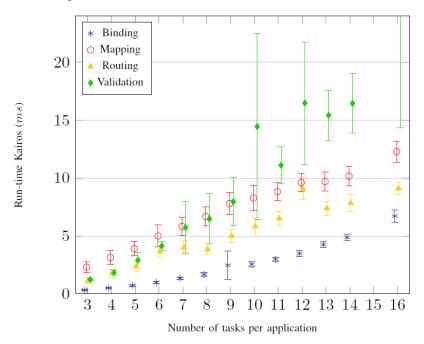

| Figure 2.17. Resource allocation execution time.                              |      |

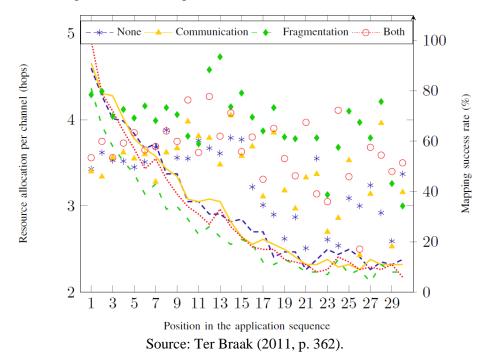

| Figure 2.18. Average communication resources allocated                        |      |

| Figure 2.19. Average resource fragmentation.                                  |      |

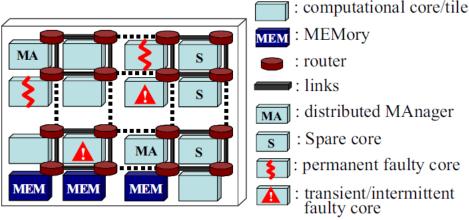

| Figure 2.20. 2-D mesh platform with spare cores.                              |      |

| Figure 2.21. Spare cores distribution schemes.                                |      |

| Figure 2.22. Mapping results using a random placement of spare cores          |      |

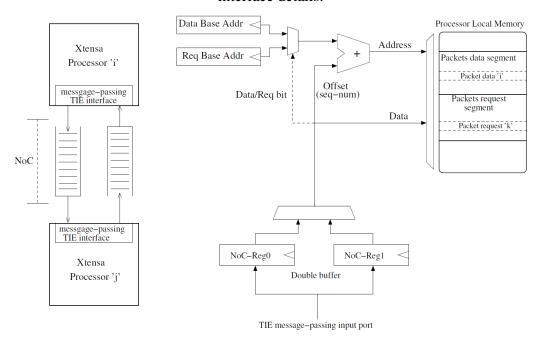

| Figure 2.23. Hardware support for message passing communication and receiving |      |

| interface details.                                                            | . 51 |

| Figure 2.24. MPMMU in a MEDEA architecture and shared memory/message passing  | ıg   |

| interface.                                                                    | _    |

| Figure 3.1. Simple virtual platform.                                          |      |

| Figure 3.2. Adaptable hardware support for different programming models       |      |

| Figure 3.3. Processor allocation and creation of virtual clusters             |      |

| Figure 3.4. Exploration of the <i>NH</i> parameter                            |      |

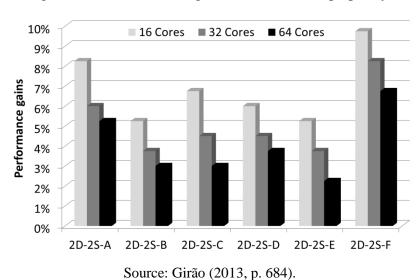

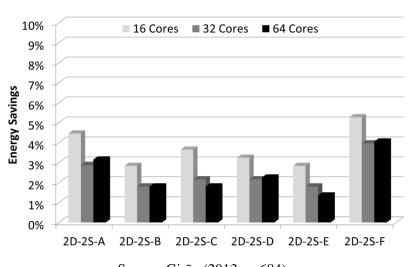

| Figure 3.5. Performance improvements using dynamic clustering.                |      |

| Figure 3.6. Energy savings using dynamic clustering.                          |      |

| Figure 3.7. Cluster Shape Policy.                                             |      |

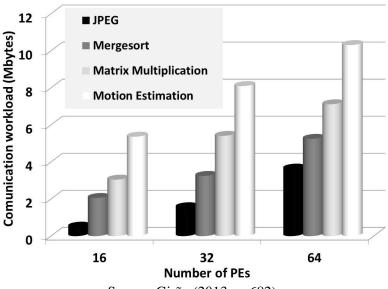

| Figure 3.8. Communication Workload.                                           |      |

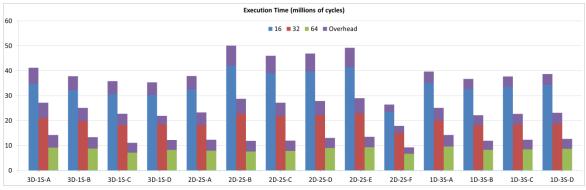

| Figure 3.9. Execution Time results for all combinations.                      |      |

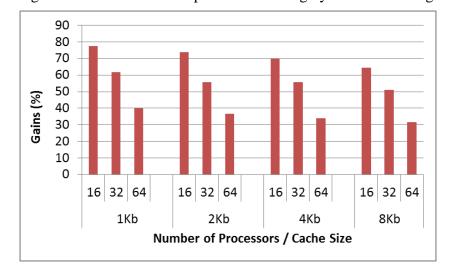

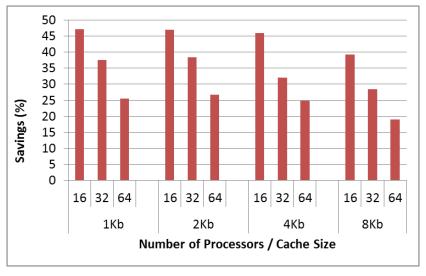

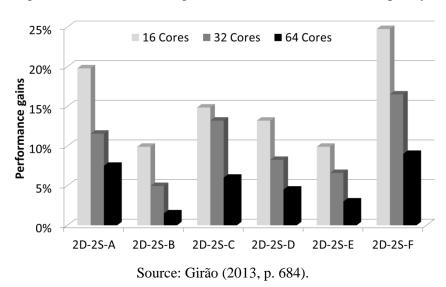

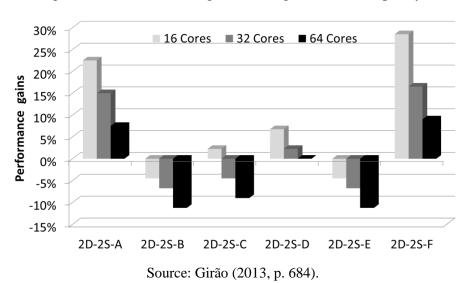

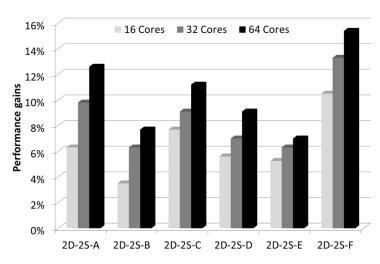

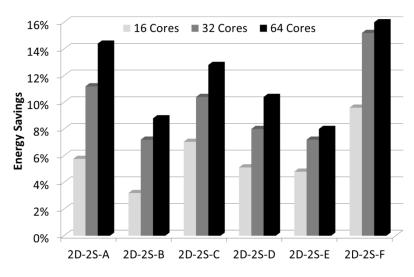

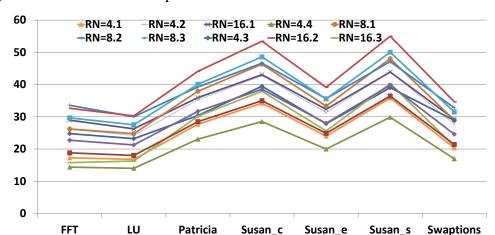

| Figure 3.10. Performance gains for Shared Variables First policy.             |      |

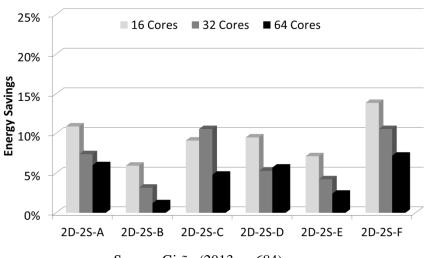

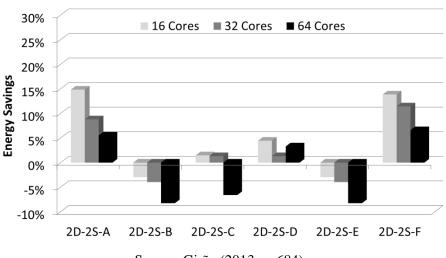

| Figure 3.11. Energy savings for Shared Variables First policy.                |      |

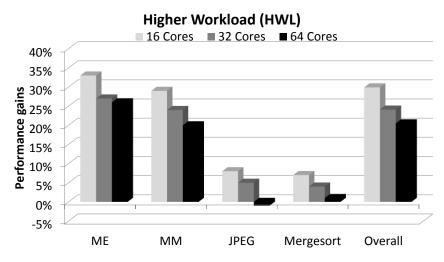

| Figure 3.12. Performance gains for Higher Workload policy.                    |      |

|                                                                               |      |

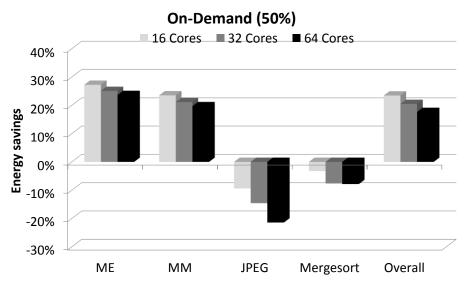

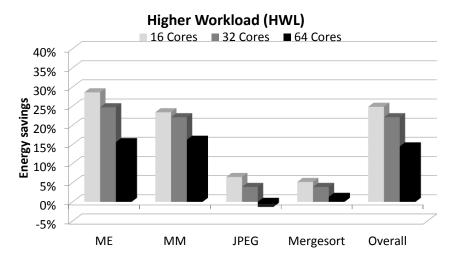

| Figure 3.13. Energy savings for Higher Workload policy.                                   |      |

|-------------------------------------------------------------------------------------------|------|

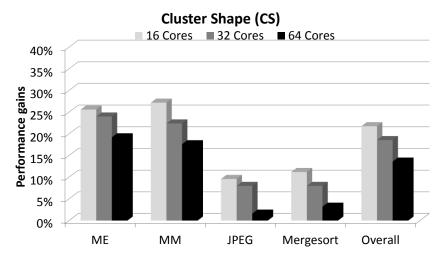

| Figure 3.14. Performance gains for Cluster Shape policy.                                  | . 72 |

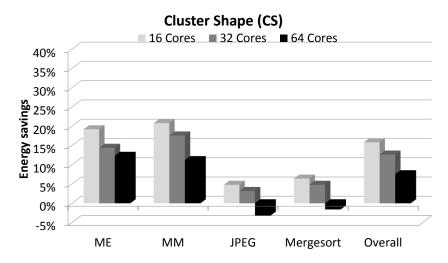

| Figure 3.15. Energy savings for Cluster Shape policy.                                     | . 72 |

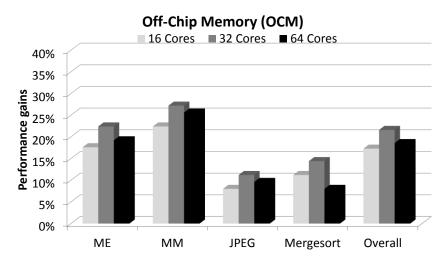

| Figure 3.16. Performance gains for Off-Chip Memory policy                                 |      |

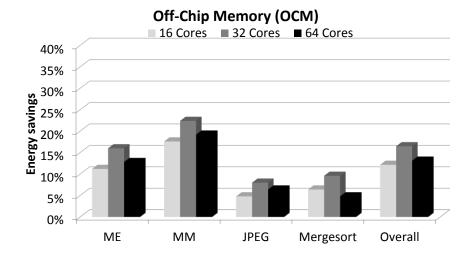

| Figure 3.17. Energy savings for Off-Chip Memory policy                                    | . 73 |

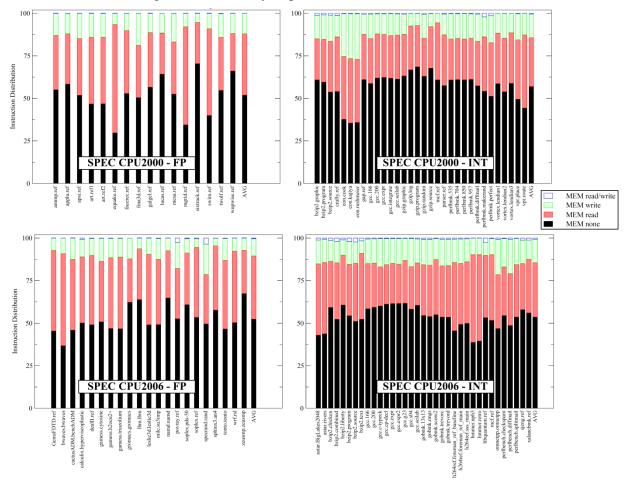

| Figure 4.1. Memory requirements from SPEC.                                                | . 77 |

| Figure 4.2. Memory Clustering                                                             | . 78 |

| Figure 4.3. Homogeneous architecture.                                                     | . 78 |

| Figure 4.4. STA example.                                                                  | . 80 |

| Figure 4.5. PTA example.                                                                  |      |

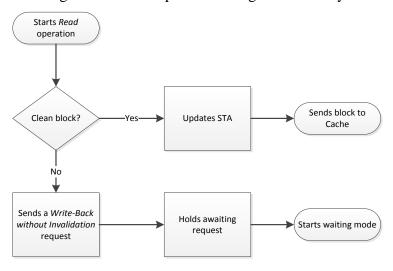

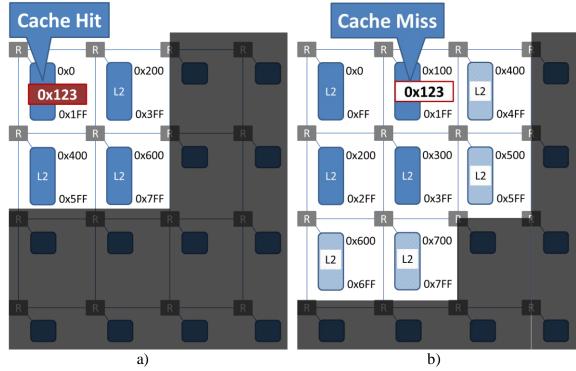

| Figure 4.6. Read operation using the Directory                                            |      |

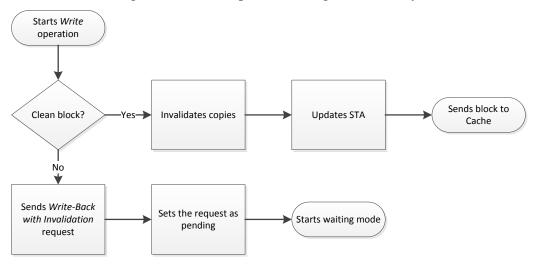

| Figure 4.7. Write operation using the Directory.                                          |      |

| Figure 4.8. Write-Permission operation.                                                   |      |

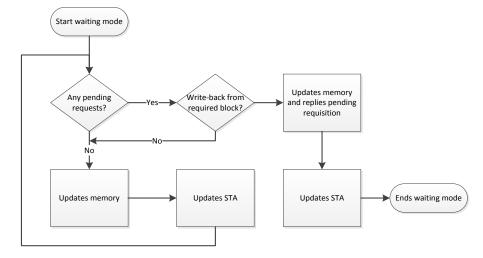

| Figure 4.9. Waiting mode when a Write-Back request is pending.                            |      |

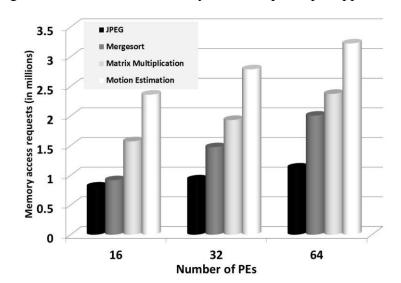

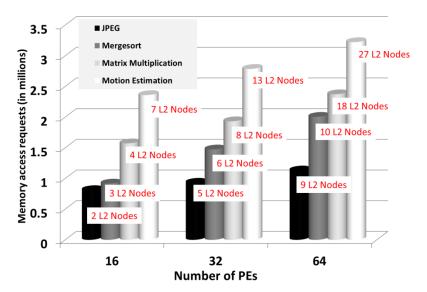

| Figure 4.10. Amount of memory access requests per application                             |      |

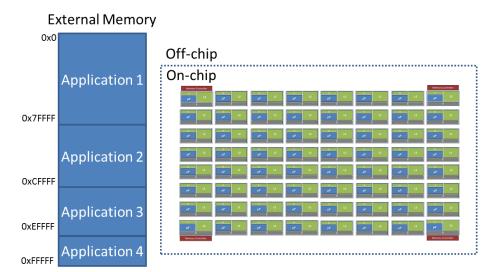

| Figure 4.11. Data space for each application in the external memory                       |      |

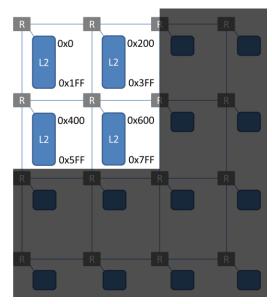

| Figure 4.12. ATA table and MPSoC before resource distribution.                            |      |

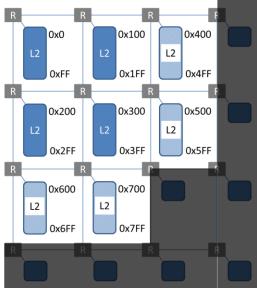

| Figure 4.13. ATA table and MPSoC after resource distribution.                             |      |

| Figure 4.14. Pre-defined distribution.                                                    |      |

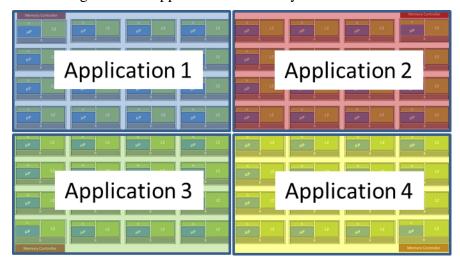

| Figure 4.15. Applications uniformly distributed.                                          |      |

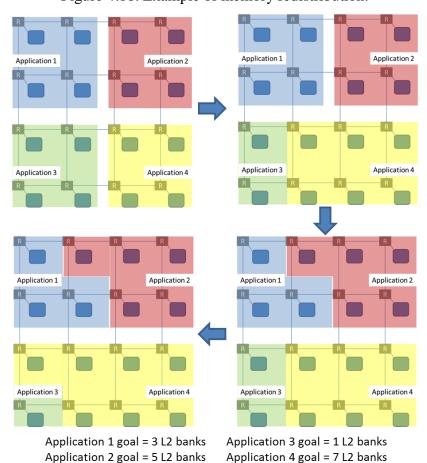

| Figure 4.16. Example of memory redistribution.                                            |      |

| Figure 4.17. Pre-defined Distribution performance and energy results                      |      |

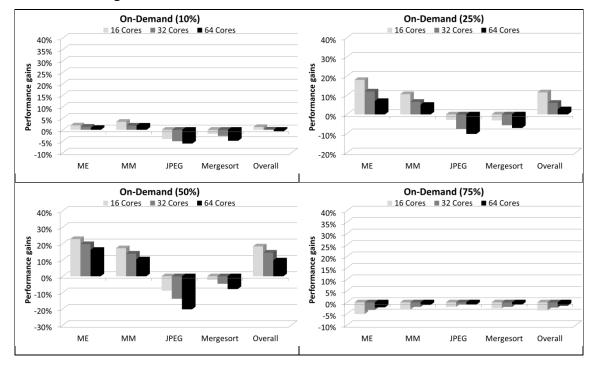

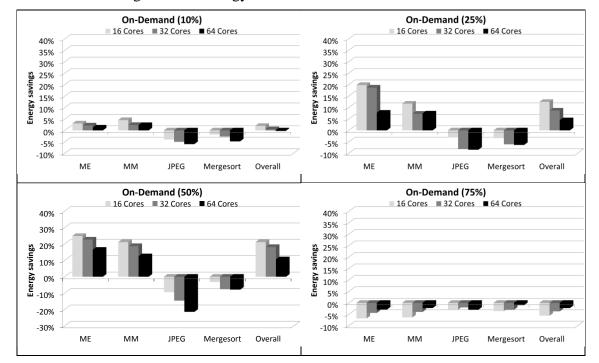

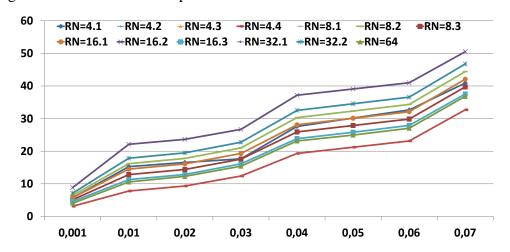

| Figure 4.18. Performance results for <i>On-demand</i> Distribution.                       |      |

| Figure 4.19. Energy results for <i>On-demand</i> Distribution.                            |      |

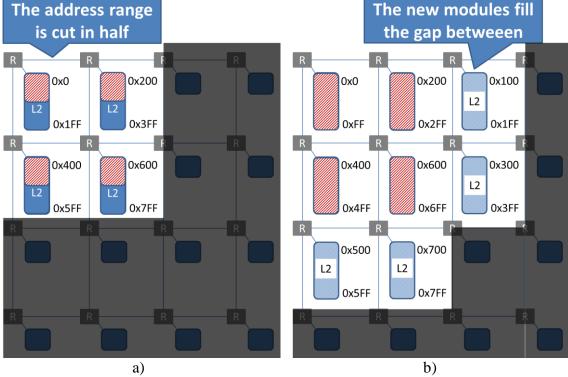

| Figure 4.20. Cold start effect after redistribution.                                      |      |

| Figure 4.21. Sequence of assignments in two steps (current modules, then new modules)     |      |

| Einens 4.22. New assissing algorithms                                                     |      |

| Figure 4.22. New assigning algorithm.                                                     |      |

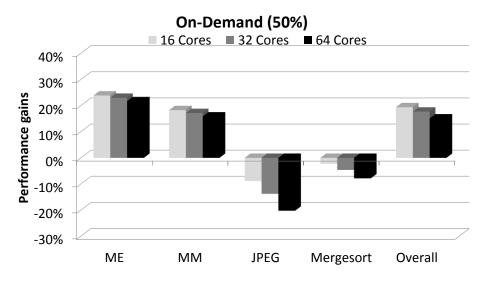

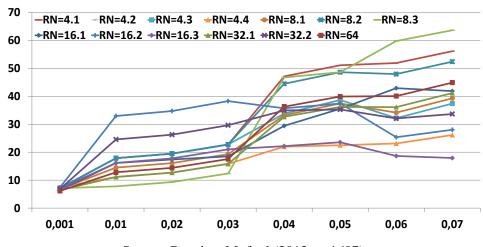

| Figure 4.23. Performance results for <i>On-demand</i> Distribution with a new assignment  |      |

| pattern.                                                                                  |      |

| Figure 4.24. Energy results for <i>On-demand</i> Distribution with a new assignment patte |      |

| Figure 4.25. Performance results for HWL using both Processor and Memory                  | . 90 |

| Clustering                                                                                | 08   |

| Figure 4.26. Energy results for HWL using both Processor and Memory Clustering.           |      |

| Figure 4.27. Performance results for CS using both Processor and Memory Clustering.       |      |

| 1 igure 4.27. I eriormance results for est using both i rocessor and wiemory clustering   | _    |

| Figure 4.28. Energy results for CS using both Processor and Memory Clustering             |      |

| Figure 4.29. Performance results for OCM using both Processor and Memory                  | •    |

| Clustering                                                                                | 100  |

| Figure 4.30. Energy results for OCM using both Processor and Memory Clustering.           |      |

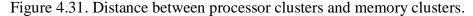

| Figure 4.31. Distance between processor clusters and memory clusters                      |      |

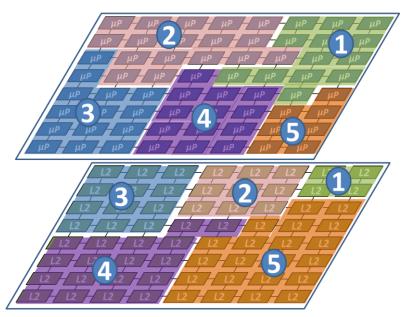

| Figure 4.32. New clustering using Cluster Mirror policy                                   |      |

| Figure 4.33. Cluster Mirror policy.                                                       |      |

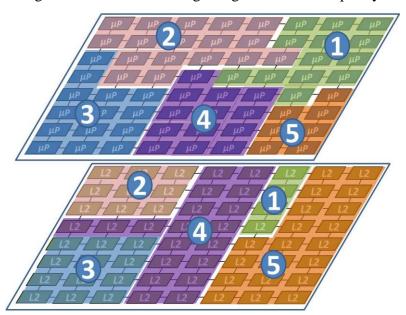

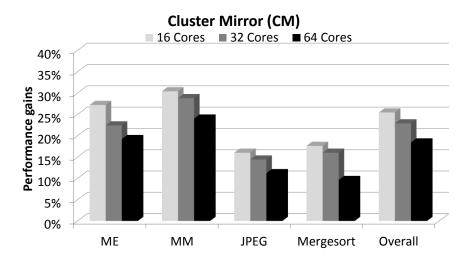

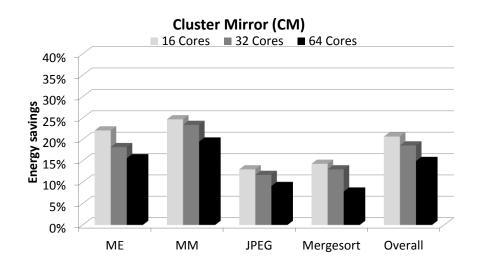

| Figure 4.34. Performance results for CM using both Processor and Memory Clustering        |      |

|                                                                                           | 103  |

| Figure 4.35. Energy results for CM using both Processor and Memory Clustering             | 104  |

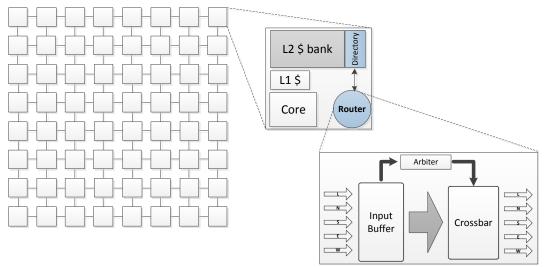

| Figure 5.1. Baseline Architecture.                                                        |      |

| Figure 5.2. SoCIN packet format                                                           | 109  |

|                                                                                           |      |

| Figure 5.3. SoCIN link signals.                                                         | 109  |

|-----------------------------------------------------------------------------------------|------|

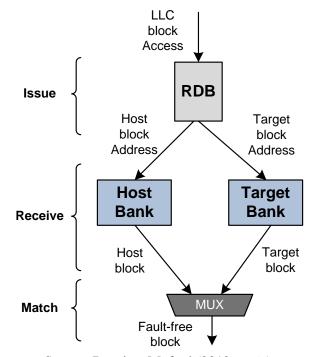

| Figure 5.4. Three phases of a fault-tolerant LLC access                                 | 111  |

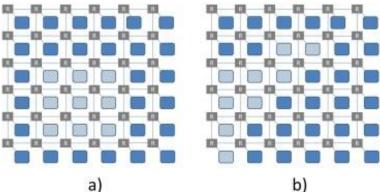

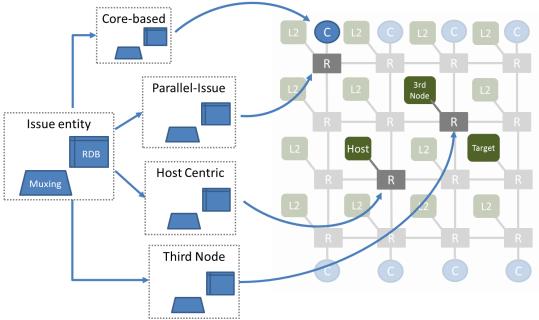

| Figure 5.5. A general view of the NoC with different policies                           | 113  |

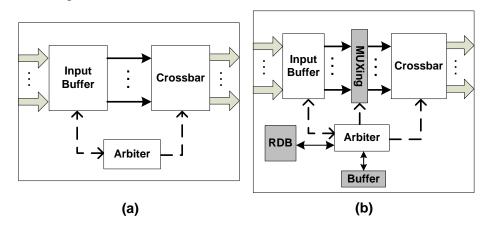

| Figure 5.6. (a) Conventional Router; (b) Fault-aware Router                             |      |

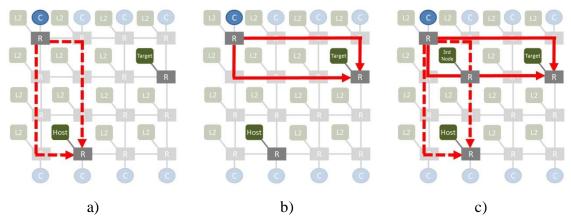

| Figure 5.7. Choosing the intermediary node in the Third Node Policy                     |      |

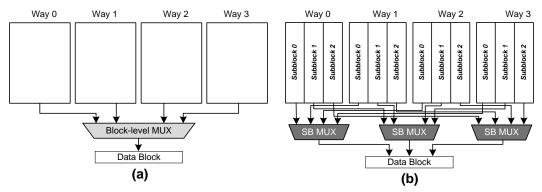

| Figure 5.8. (a) A conventional 4-way set associative cache bank; (b) Modified cache     |      |

| bank with 3 sub-blocks in each way.                                                     | 115  |

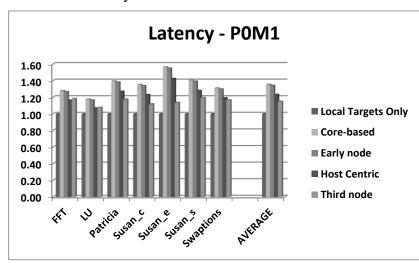

| Figure 5.9. Network latency of the benchmarks normalized to that of Baseline            |      |

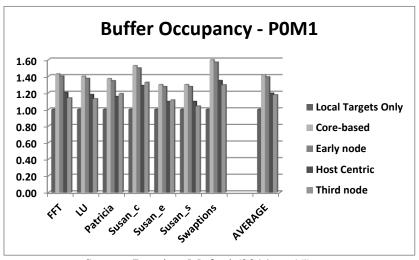

| Figure 5.10. Average Buffer occupancy of different policies normalized to the Basel     | ine. |

|                                                                                         |      |

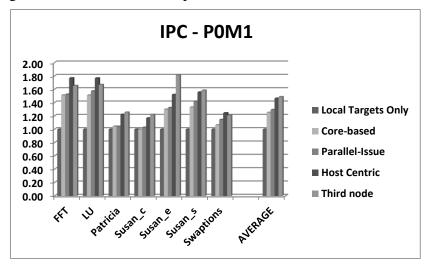

| Figure 5.11. IPC of different policies normalized to the Baseline.                      | 119  |

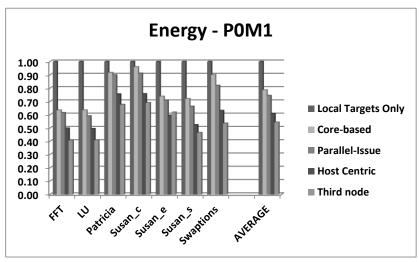

| Figure 5.12. Energy of different policies normalized to the Baseline                    | 119  |

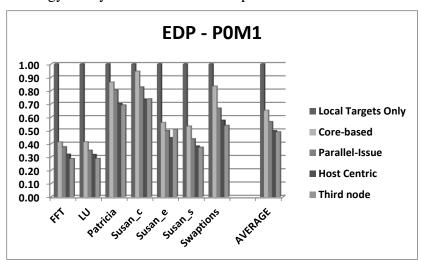

| Figure 5.13. Energy-Delay Product of different polices normalized to the Baseline       | 120  |

| Figure 5.14. Baseline Architecture.                                                     | 121  |

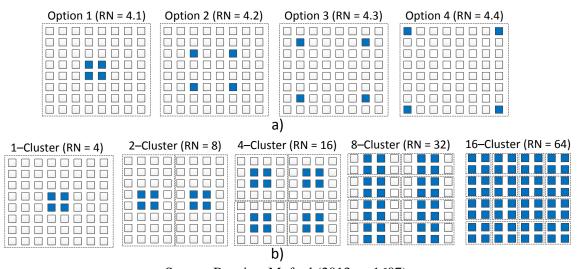

| Figure 5.15. Possible configuration patterns in a) cluster-level, b) system-level, with | four |

| redundancy nodes per cluster                                                            | 123  |

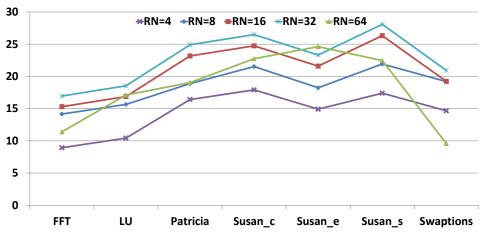

| Figure 5.16. Performance improvement at cluster-level across different benchmarks.      | 124  |

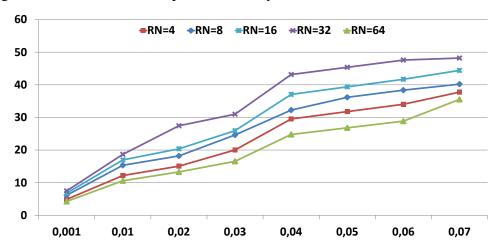

| Figure 5.17. Performance improvement at cluster-level across different fault rates      | 124  |

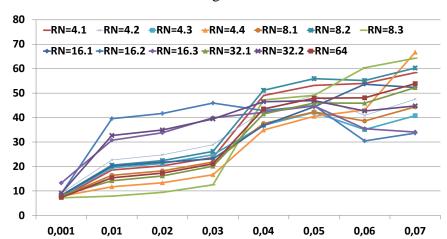

| Figure 5.18. Performance improvement at cluster-level across different amounts of       |      |

| redundancy                                                                              |      |

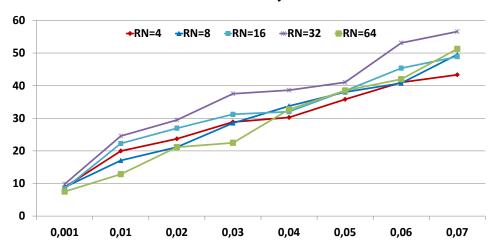

| Figure 5.19. Performance improvement at system-level across different benchmarks.       | .126 |

| Figure 5.20. Performance improvement at system-level across different fault rates       | 126  |

| Figure 5.21. Performance improvement at system-level across different amounts of        |      |

| redundancy                                                                              | 127  |

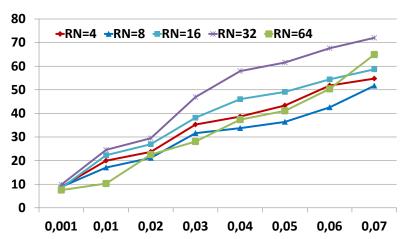

| Figure 5.22. Energy results across different amount of redundancy for the cluster-lev   | /el  |

| configurations.                                                                         | 128  |

| Figure 5.23. Energy results across different amount of redundancy for the system-level  | vel  |

| configurations.                                                                         | 128  |

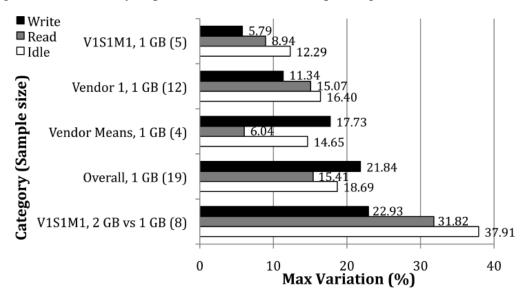

| Figure 6.1. Variability impact on DDR memories depending on models and vendors          |      |

| Figure 6.2. Estimations regarding area, power and frequency scaling                     | 135  |

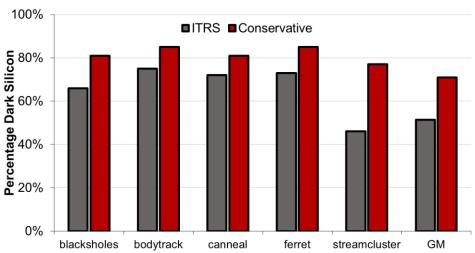

| Figure 6.3. Percentage of Dark Silicon area in a chip.                                  | 135  |

# **LIST OF TABLES**

| Table 2.1. Evaluated scenarios.                                               | 29     |

|-------------------------------------------------------------------------------|--------|

| Table 2.2. Distributed vs. Centralized mapping comparison.                    |        |

| Table 2.3. Processor utilization resulting from different resource managers   | 39     |

| Table 2.4. Performance and energy consumption results                         |        |

| Table 3.1. Resource Occupation Map                                            |        |

| Table 3.2. Cluster Descriptor                                                 |        |

| Table 3.3. Resources required by each application.                            |        |

| Table 3.4. SIMPLE setup.                                                      |        |

| Table 3.5. Combinations of applications according to the parallel programming | model. |

|                                                                               | 68     |

| Table 3.6. Average Performance gains for all combinations.                    | 74     |

| Table 3.7. Average Energy savings for all combinations                        | 74     |

| Table 5.1. Experimental Setup.                                                | 116    |

| Table 5.2. RDB remapping results.                                             |        |

| Table 5.3. Power and Area overhead results.                                   | 121    |

| Table 6.1. List of publications                                               | 136    |

## LIST OF ABBREVIATIONS AND ACRONYMS

ACG Application Control Graph

**AMURHA** Adaptive Multi-grained Hardware Architecture

API **Application Programming Interface**

ATA Address Table BE Best Effort

**BIST**

Built-In-Self-Test

CaCoMa Cache Communication Manager

CIC Core i-let1 Controlers **CMP** Chip Multiprocessor

CM Cluster Mirror CS Cluster Shape

DCT Discrete Cosine Transform

Double Data Rate DDR

DIMM Dual Inline Memory Module

DMA **Direct Memory Access**

**DVFS** Dynamic Voltage and Frequency Scaling

ECC **Error Correction Codes** Earliest Deadline First **EDF EDP Energy Delay Product**

First In First Out **FIFO FMB** Fault Map Block

**FPGA** Field-Programmable Gate Array

FT Fault Tolerant

Global Master Processing element **GMP**

GS Guaranteed Service HWL Higher Workload

ILP Instruction-Level Parallelism IPC Instructions per Cycle

iRTSS Invasive Runtime Support System

ITRS International Technology Roadmap for Semiconductors

JPEG Joint Photographic Experts Group

LLC Last Level Cache

LMP Local Master Processing element

ME Motion Estimation

MIMD Multiple Instruction Multiple Data

MISD Multiple Instruction Single Data

MM Matrix Multiplication

MPEG Moving Picture Experts Group

MPI Message Passing Interface

MPMMU Multiprocessor Memory Management Unit

MPSoC Multiprocessor System-on-Chip

MS Mergesort

NH

Number of Hops

NI

Network Interface

NN

Nearest Neighbor

NoC

Network-on-Chip

NT

Number of Tasks

NUCA Non-Uniform Cache Access

NUMA Non-Uniform Memory Access

OpenMP Open Multi-Processing

OCM Off-Chip Memory

PE Processing Element

8

PREM Predictable Execution Model

PTA Processor Table

QCIF Quarter Common Intermediate Format

RDB Remapping Data Block

RISC Reduced Instruction Set Computing

RM Resource Manager

RTOS Real-Time Operating System SCC Single-chip Cloud Computer

SDF Synchronous Data Flow

SVF Shared Variables First

SIMD Single Instruction Multiple Data

SIMPLE Simple Multiprocessor Platform Environment

SISD Single Instruction Single Data

SMP Symmetric Multiprocessor

SoC System-on-Chip

SoCIN System-on-Chip Interconnection Network

SP Slave Processing element

SPFP Simple Partitioned FIFO Locking Protocol

STA Status Table

TCPA Tightly-Coupled Processor Array

TLP Thread-Level Parallelism

TSV Through-Silicon Via

WPPA Weakly Programmable Processor Arrays

# **TABLE OF CONTENTS**

| 1 II                | NTRODUCTION                          | .16  |

|---------------------|--------------------------------------|------|

| 1.1                 | Parallel Programming on MPSoCs       |      |

| 1.2                 | Resource Management                  |      |

| 1.3                 | Clustering                           |      |

| 1.4                 | Task Mapping and Scheduling          |      |

| 1.5<br>1.6          | Thesis Goals                         |      |

|                     | Text Organization                    |      |

| 2 R                 | ELATED WORK                          | .25  |

| 2.1                 | Cluster-based Multi-cores            | . 25 |

| 2.2                 | Resource Management                  |      |

| 2.3                 | Task Mapping and Migration           |      |

| 2.4                 | Proposed work                        | . 52 |

| 3 P                 | ROCESSOR CLUSTERING                  | .54  |

| 3.1                 | Adaptable Hardware Support           | . 55 |

| 3.2                 | Virtual Dynamic Clustering           | . 57 |

| 3.3                 | Resource Mapping Policies            |      |

| 3.3.1               |                                      |      |

| 3.3.2               | 6                                    |      |

| 3.3.3               | 1 \ /                                |      |

| 3.3.4               |                                      |      |

| 3.4                 | Experimental Setup                   |      |

| 3.4.1               | 11                                   |      |

| 3.5                 | Results                              |      |

| 3.5.1               | 11 7 61                              |      |

| 3.5.2<br><b>3.6</b> | 1                                    |      |

|                     | Final remarks                        |      |

| 4 N                 | IEMORY CLUSTERING                    | .76  |

| 4.1                 | Memory Subsystem and Cache Coherence |      |

| 4.3                 | Redistribution policies              |      |

|                     | Pre-defined distribution             |      |

| 4.3.2               |                                      |      |

| 4.4                 | Distribution Mapping                 |      |

| 4.5                 | Results                              |      |

| 4.5.1               |                                      |      |

| 4.5.2               |                                      |      |

| 4.5.3               | Improving memory redistribution      | . 93 |

| 4.6        | Using Processor Clustering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 97  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.6.1      | Higher Workload (HWL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 4.6.2      | • , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 4.6.3      | 1 ' '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 4.6.4      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 4.7        | Final Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 5 R        | ELIABILITY CLUSTERING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 106 |

| 5.1        | Basic Idea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 107 |

| 5.1.1      | MPSoC and NUCA LLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| 5.1.2      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 5.2        | Base Fault-tolerant Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| 5.2.1      | Proposed NoC Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 5.2.2      | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| 5.2.3      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 5.2.4      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 5.3        | Design Space Exploration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|            | Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 5.4.1      | Network Latency and Traffic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 5.4.2      | Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 5.4.3      | Energy Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 119 |

| 5.4.4      | Overhead Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 120 |

| 5.5        | Reliability Clustering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 121 |

| 5.5.1      | Example NoC Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 121 |