# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

# PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

# QUATERNARY CLB FOR A FAULT TOLERANT QUATERNARY FPGA

Eduardo Luis Rhod

Monografia elaborada para defesa de doutorado sob a orientação do professor Luigi Carro, em preenchimento parcial aos requisitos necessários para a obtenção do grau de Doutor pelo Pograma de Ps-Gaduação em Microeletrônica.

# CIP - Catalogação na Publicação

```

Rhod, Eduardo

QUATERNARY CLB FOR A FAULT TOLERANT QUATERNARY

FPGA / Eduardo Rhod. -- 2012.

90 f.

```

Orientador: Luigi Carro.

Tese (Doutorado) -- Universidade Federal do Rio Grande do Sul, Instituto de Informática, Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR-RS, 2012.

1. Tolerância a Falhas. 2. Lógica Quaternária. 3. FPGA. 4. CLB. I. Carro, Luigi, orient. II. Título.

# **DEDICATÓRIA**

Dedico este trabalho a todos os meus familiares, aos que estão entre nós e também aos que já se foram. Em especial, dedico aos meus pais, que desde cedo me incentivaram e mostraram o valor transformador da educação, pois nunca mediram esforços para me garantir uma educação de qualidade. Principalmente dedico a eles por me educarem através da melhor técnica conhecida pela humanidade, a educação pelo exemplo de bom caráter e valores humanos que sempre demonstraram e continuam demonstrando até hoje.

Dedico também a minha mulher e companheira de todos os momentos, e aos seus familiares que sempre pude considerar como a minha segunda família.

#### **AGRADECIMENTOS**

Ao Programa de Pós-Graduação em Microeletrônica, PGMicro, e a todos os funcionários da secretaria do curso Pós-Graduação em Microeletrônica, pelo profissionalismo e seriedade com que exerceram suas atividades. Agradeço em especial às secretárias do PGMicro, Zíngara Lubaszewski e Gabriela Ouriques. Ao professor Henri Boudinov, pelos ensinamentos relacionados à física de semicondutores. Agradeço também a todos os professores e colegas de turma que contribuíram enormemente na minha formação durante o mestrado, professores Sergio Bampi, Marcelo Lubaszewski, Ricardo Reis e Fernanda Lima Kastensmidt. Em especial, agradeço ao professor e colega de pesquisa Carlos Arthur Lang Lisbôa. Agradeço também e em caráter decisivo para a qualidade da pesquisa desenvolvida ao longo do doutorado e principalmente pelo meu crescimento profissional aos colegas de laboratório Mateus Beck Rutzig, Gabriel Nazar, Ulisses Brisolara Corêa, Antonio C. S. B. Filho, Mônica Magalhães, Ronaldo Ferreira e Fabio Iturriet pelas enormes contribuições e ajudas fornecidas durante os trabalhos de pesquisa. Ao CNPQ e a Capes pela provisão da bolsa de mestrado, sem a qual não teria seguido com os estudos.

Agradeço em especial ao meu orientador Luigi Carro, por acreditar no meu trabalho e por conduzir exemplarmente a minha orientação, guiando-me na busca por um trabalho de qualidade, mas ao mesmo tempo dando espaço para que eu exercesse a minha pesquisa com criatividade e liberdade.

Agradeço a todos os meus familiares e amigos de Lajeado pelo apoio e compreensão da minha ausência nos diversos momentos em que estive dedicado aos meus estudos. Agradeço a minha esposa Alexandra Barcelos Rhod e seus familiares pelo companheirismo e amor. Em especial agradeço aos meus pais Pedro Valentin Rhod e Marta Regina Blasi Rhod pela educação e por todas as oportunidades que me deram sem nunca medir esforços. Agradeço os meus irmãos Guilherme Blasi Rhod e Amanda Rhod Rocha por fazerem parte na minha vida.

#### **RESUMO**

A diminuição no tamanho dos transistores vem aumentando cada vez mais o número de funções que os dispositivos eletrônicos podem realizar. Apesar da diminuição do tamanho mínimo dos transistores, a velocidade máxima dos circuitos não consegue seguir a mesma taxa de aumento. Um dos grandes culpados apontados pelos pesquisadores são as interconexões entre os transistores e também entre os componentes. O aumento no número de interconexões dos circuitos traz consigo um significativo aumento do cosumo de energia, aumento do atraso de propagação dos sinais, além de um aumento da complexidade e custo do projeto dos circuitos integrados. Como uma possível solução a este problema é proposta a utilização de lógica multivalorada, mais especificamente, a lógica quaternária. Os dispositivos FPGAs são caracterizados principalmente pela grande flexibilidade que oferecem aos projetistas de sistemas digitais. Entretanto, com o avanço nas tecnologias de fabricação de circuitos integrados e diminuição das dimensões de fabricação, os problemas relacionados ao grande número de interconexões são uma preocupação para as próximas tecnologias de FPGAs. As tecnologias menores que 90nm possuem um grande aumento na taxa de erros dos circuitos, na lógica combinacional e sequencial. Apesar de algumas potenciais soluções começara a ser investigadas pela comunidade, a busca por circuitos tolerantes a erros induzidos por radiação, sem penalidades no desempenho, área ou potência, ainda é um assunto de pesquisa em aberto. Este trabalho propõe o uso de circuitos quaternários com modificações para tolerar falhas provenientes de eventos transientes. Como principal contribuição deste trabalho destaca-se o desenvolvimento de uma CLB (do inglês Configurable Logic Block) quaternária capaz de suportar eventos transientes e, na possibilidade de um erro, evitá-lo ou corrigi-lo.

Palavras-chaves: Arquiteturas tolerantes a falhas, circuitos quaternários, técnicas de detecção de erros, taxa de *soft error*, *FPGAs*.

#### **ABSTRACT**

The decrease in transistor size is increasing the number of functions that can be performed by the electronic devices. Despite this reduction in the transistors minimum size, the circuit's speed does not follow the same rate. One of the major reasons pointed out by researchers are the interconnections between the transistors and between the components. The increase in the number of circuit interconnections brings a significant increase in energy consumption, propagation delay of signals, and an increase in the complexity and cost of new technologies IC designs. As a possible solution to this problem the use of multivalued logic is being proposed, more specifically, the quaternary logic. FPGA devices are characterized mainly by offering greater flexibility to designers of digital systems. However, with the advance in IC manufacturing technologies and the reduced size of the minimum fabricated dimensions, the problems related to the large number of interconnections are a concern for future technologies of FPGAs. The sub 90nm technologies have a large increase in the error rate of its functions for the combinational and sequential logic. Although potential solutions are being investigated by the community, the search for circuits tolerant to radiation induced errors, without performance, area, or power penalties, is still an open research issue. This work proposes the use of quaternary circuits with modifications to tolerate faults from transient events. The main contribution of this work is the development of a quaternary CLB (Configurable Logic Block) able to withstand transient events and the occurrence of soft errors.

Keywords: Fault tolerant architectures, quaternary circuits, error detection techniques, soft error rate, FPGAs

# **SUMMARY**

| U | NIVERSI | DADE FEDERAL DO RIO GRANDE DO SUL                                                          | 1  |

|---|---------|--------------------------------------------------------------------------------------------|----|

| 1 | Introdu | ction                                                                                      | 14 |

| 2 | Contex  | t of the Research                                                                          | 17 |

|   | 2.1 Qu  | aternary Logic Background                                                                  | 17 |

|   | 2.1.1   | Current-Mode Multivalued-Circuits                                                          | 19 |

|   | 2.1.2   | Voltage-Mode Multivalued Logic Circuits                                                    | 21 |

|   | 2.1.3   | Voltage-Mode Multivalued Logic Circuits Applied to FPGAs                                   | 23 |

|   | 2.2 Qu  | aternary Base Circuits                                                                     | 24 |

|   | 2.3 Fa  | ult Tolerance Background                                                                   | 26 |

|   | 2.3.1   | Radiation Sources and their Effects                                                        | 27 |

|   | 2.3.2   | Effects of SEUs and SETs in Digital Circuits.                                              | 28 |

|   | 2.3.3   | Metrics to Evaluate the Vulnerability of Circuits to Soft Errors                           | 29 |

|   | 2.3.4   | Mitigation Techniques for SEUs and SETs                                                    | 32 |

| 3 | Fault T | olerant Quaternary Circuits                                                                | 38 |

|   |         | ult Tolerant Quaternary Lookup Table (FT-QLUT) and the Error Avoiding Quaternate (EA-QLUT) | -  |

|   | 3.1.1   | QLUT Fragilities                                                                           | 39 |

|   | 3.1.2   | Proposed Architecture                                                                      |    |

|   | 3.1.3   | Fault Injection Experiments                                                                | 42 |

|   | 3.1.4   | FT-QLUT Improvement: The EA-QLUT                                                           | 46 |

|   | 3.2 Th  | e Fault Tolerant Quaternary Latch and Flip-Flop (FT-QL and FT-QFF)                         | 48 |

|   | 3.2.1   | The Fault Tolerant Quaternary Latch (FT-QL)                                                |    |

|   | 3.2.2   | The Fault Tolerant Quaternary Flip-Flop (FT-QFF)                                           | 55 |

|   | 3.3 Va  | riability Impact Analysis                                                                  | 58 |

| 4 | Area, P | erformance and power dissipation overheads                                                 | 60 |

|   | 4.1 FT  | -QLUT and EA-QLUT Overheads                                                                | 60 |

|   | 4.2 FT  | -QL and FT-QFF Area Results, Analysis and Discussion                                       | 65 |

| 5 The Fault Tolerant Quaternary Configurable Logic Block (FT-QCLB) | 68 |

|--------------------------------------------------------------------|----|

| 5.1 Fault Injection Experiments                                    | 70 |

| 5.2 Simulation Results, Overheads and Results Analysis             | 71 |

| 5.3 Area Results                                                   | 74 |

| 6 conclusion and future work                                       | 76 |

| 7 references                                                       | 78 |

| Apendix A: Different bases and its relations                       | 84 |

| Apendix B: Contributions                                           | 88 |

|                                                                    |    |

# LIST OF FIGURES

| Figure 2.1. Quaternary Inverter proposed by YASUDA                                                                                               | 21 |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.2. Standard QLUT schematic circuit with 1 quaternary input                                                                              | 25 |

| Figure 2.3. Quaternary inverter (a) and quaternary inverter truth table (b).                                                                     | 26 |

| Figure 2.4. Boron fission induced by low energy neutron.                                                                                         | 28 |

| Figure 2.5. Sequential circuit.                                                                                                                  | 28 |

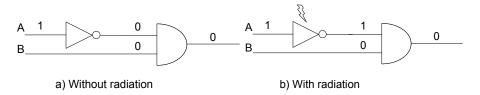

| Figure 2.6. Combinational circuit without radiation (a) and with radiation (b)                                                                   | 29 |

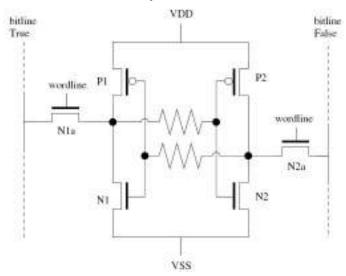

| Figure 2.7. SRAM cell hardened by the inclusion of two feedback resistors                                                                        | 34 |

| Figure 2.8. Combinational circuit (b) by using space (or hardware) redundancy.                                                                   | 35 |

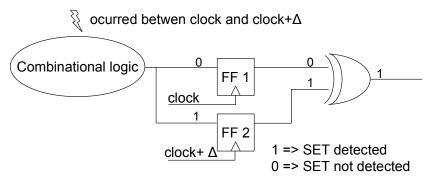

| Figure 2.9. Use of time redundancy to detect an SET in a combinational circuit.                                                                  | 35 |

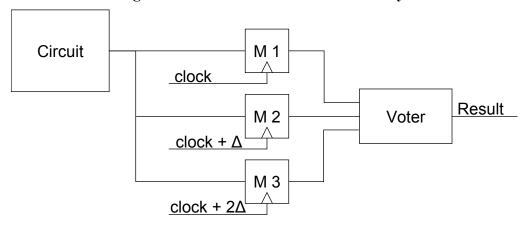

| Figure 2.10. Use of space redundancy to detect an SET in a combinational circuit.                                                                | 36 |

| Figure 2.11. TMR with time redundancy.                                                                                                           | 37 |

| Figure 3.1. Labeled quaternary lookup table with 1 input                                                                                         | 40 |

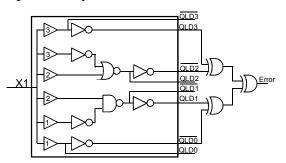

| Figure 3.2. QLD quaternary decoder with its error detection circuit.                                                                             | 41 |

| Figure 3.3. Fault tolerant QLUT circuit                                                                                                          | 42 |

| Figure 3.4. Binary LUT equivalent to the 1 input quaternary LUT                                                                                  | 43 |

| Figure 3.5. Complete binary LUT with the DWC technique equivalent to the FT-QLUT of Figure 3.3.                                                  |    |

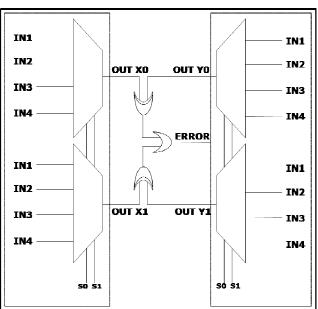

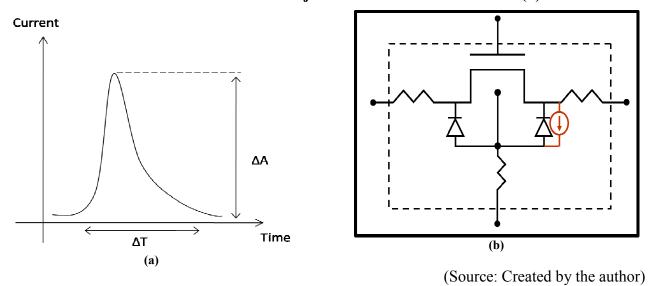

| Figure 3.6. Approximated waveform of the double exponential current source (a) and indication the waveform injections in an NMOS transistor (b). |    |

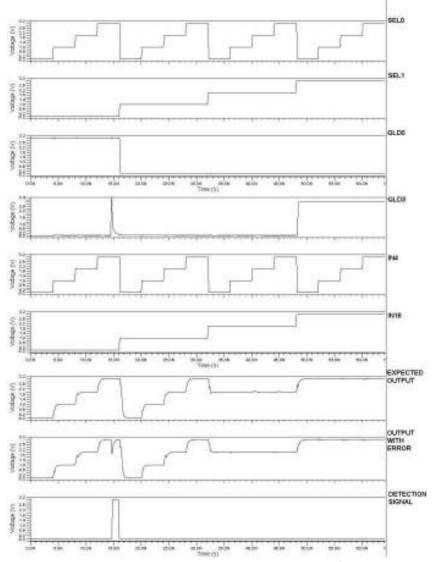

| Figure 3.7. Waveforms of a fault injection simulation at the inverter of the QLD3 signal (Figure 3.2)                                            | 45 |

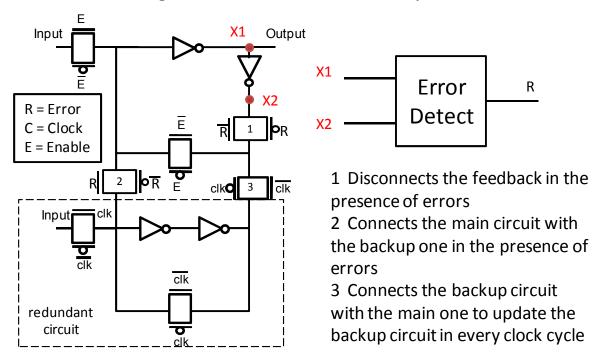

| Figure 3.8. Error Avoiding Quaternary Lookup Table (EA-QLUT)                                                                                     | 46 |

| Figure 3.9. Quaternary latch and quaternary inverter                                                                                             | 48 |

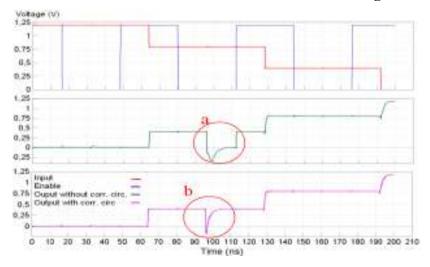

| Figure 3.10. Example of a pulse that did not generate an error (a) and example of a pulse that generated an error (b)                            | 50 |

| Figure 3.11. Fault Tolerant Quaternary Latch.                                                                                                    | 53 |

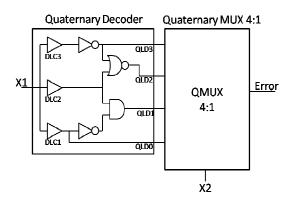

| Figure 3.12. FT-Q-Latch Error detection circuit                                                                                                  | 54 |

| Figure 3.13. Error detection and correction circuit correcting a SET.                                                                            | 54 |

| Figure 3.14. Quaternary master-slave flip-flop.                                                                                                  | 55 |

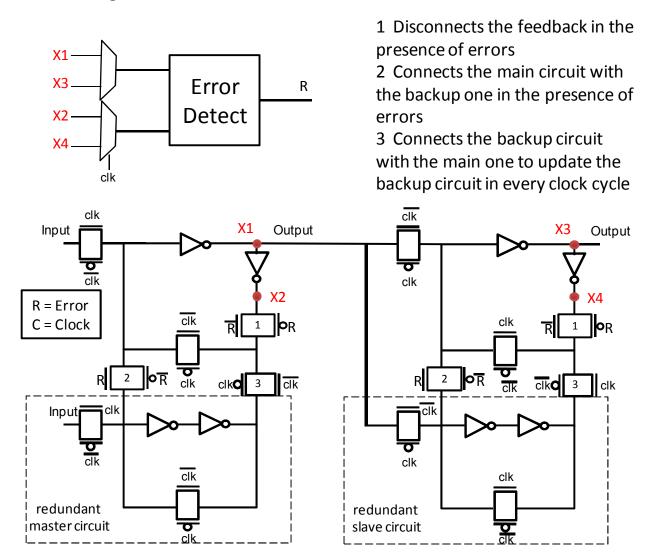

| Figure 3.15. the fault detection and correction of used in the FT-QFF                                                                            | 57 |

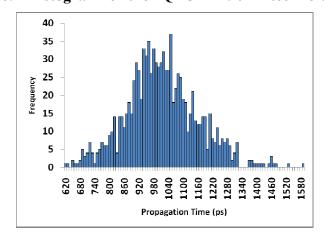

| Figure 3.16. Histogram for the 2QLUT in 90nm technology. | 58 |

|----------------------------------------------------------|----|

| Figure 4.1. 2QLUT: 2 input QLUT                          | 61 |

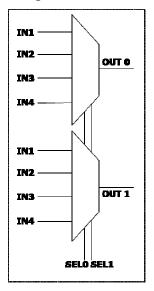

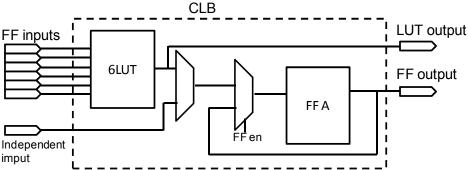

| Figure 5.1. Standard Binary CLB composition              | 68 |

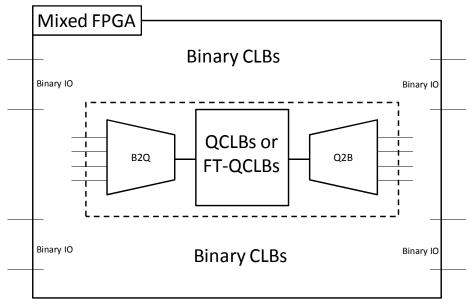

| Figure 5.2. Mixed Binary and Quaternary FPGA             | 69 |

| Figure 5.3. Binary to Quaternary circuit decoder         | 70 |

| Figure 5.4. Quaternary to Binary circuit decoder         | 70 |

# LIST OF TABLES

| Table 2.1. Binary Logic Functions with 2 Inputs                                                                                                 | 18          |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Table 2.2. Threshold Voltage of the Different Transistors                                                                                       | 25          |

| Table 2.3. Truth table of the down literal circuits.                                                                                            | 25          |

| Table 2.4. Architectural-vulnerability-factor (AVF) estimation approaches                                                                       | 31          |

| Table 3.1. QLD Truth Table                                                                                                                      | 41          |

| Table 3.2. Percentage of Errors Observed with Injections in Transistors T1, T2, T4 and                                                          | T651        |

| Table 3.3. Percentage of Errors Observed with Injections at Transistor T3                                                                       | 51          |

| Table 3.4. Percentage of Errors Observed with Injections at Transistor T5                                                                       | 51          |

| Table 3.5. Overall Percentage of Errors Observed in Each Transistor                                                                             | 51          |

| Table 3.6. Quaternary Decoder Truth Table                                                                                                       | 54          |

| Table 4.1. Area results comparing the QLUT with the binary one without the fault detec                                                          |             |

| Table 4.2. Area results comparing the FT-QLUT with the Binary LUT using the DWC to                                                              | echnique.62 |

| Table 4.3. Propagation time for different sizes of the proposed QLUT and its binary corr                                                        | _           |

| Table 4.4. Propagation time (in ps) for different sizes of the proposed QLUT and its bina correspondent obtained by increasing transistor size. | •           |

| Table 4.5. Power Dissipation (in $\mu W$ ) for Different sizes of the FT-QLUT and the Binar Correspondent                                       |             |

| Table 4.6. Area Results of the EA-QLUT and the Two Binary Correspondents                                                                        | 64          |

| Table 4.7. Propagation time (in ps) for different sizes of the proposed EA-QLUT and its correspondent protected with the TMR technique.         |             |

| Table 4.8. Power dissipation (in µW) for different sizes of the proposed EA-QLUT and it correspondent.                                          |             |

| Table 4.9. Area Results in Number of Transistors                                                                                                | 66          |

| Table 4.10. Area Results for the FT-QFF in Number of Transistors                                                                                | 67          |

| Table 5.1. Error Rate for the Quaternary and Binary Circuits with no FT                                                                         | 72          |

| Table 5.2. Error Rate by Component for the Quaternary CLB and the Binary Correspond                                                             |             |

| Table 5.3. Error Rate for the FT-Q-CLB and the Binary Correspondent.                                                                            | 73          |

| Table 5.4. Area of Quaternary and Binary CLBs with no FT Technique.                                                                             | 74          |

| Table 5.5. Area of Quaternary and Binary CLBs with FT Technique.                                                                                | 74          |

Table 5.6. Area Overhead Comparing the Quaternary and the Binary FT Versions ......74

# LIST OF ABREVIATIONS

AVF Architectural Vulnerability Factor

ALU Arithmetic and Logic Unit

BPSG Boron Phospho-Silicate Glass

CLB Configurable Logic Block

CMOS Complementary Metal-Oxide-Semiconductor

DLC Down Literal Circuit

DWC Duplication with Comparison

FIT Failures in Time

IC Integrated Circuit

LET Linear Energy Transfer

LUT Lookup Tables

MOS Metal-Oxide-Semiconductor

MTTF Mean Time to Failure

MVL Multiple-Valued Logic

N-MR Modular Redundancy of order N

SE Soft Error

SER Soft Error Rate

SETs Single Event Transient

SEUs Single Event Upsets

SoC System-on-a-Chip

SOI Silicon-on-Insulator

SRAM Static Random Access Memory

TMR Triple Modular Redundancy

TVF Timing Vulnerability Factor

# 1 INTRODUCTION

In computer engineering and digital systems the subject of the system radix is recurrent. The question of what radix, is optimum for a system, if there is only one possible answer? Is the well known radix-2, pushed forward by the continuous development and ability of microelectronics to provide efficient two-state devices and circuits? Some practical engineering systems would point to the radix-3, for example, a system that has the possible states of forward/stop/reverse. Others would suggest the use the radix-10 as we already do in our 10 fingers based nature or even the biggest radix off all which can be performed by the analog circuits. The decision of the radix of the system is closely related to the pros and cons offered by the radix. In digital systems, the chosen radix reflects at the data length, circuit complexity, interconnection complexity, the total pins of a component, the address bus width, the data bus width, the number of representations, power consumption, the speed of arithmetic operations among others.

Nowadays engineers are facing several problems related to the increase in the number of interconnections and pins of the integrated circuits (IC), increasing the complexity of the designs and all the other related costs, like power consumption and delay. As a possible solution to reduce the number of interconnections, the use of multiple-valued logic (MVL), which means the ability to transport more than 2 logic values in the same wire, may lead to a meaningful reduction in the number of wires required to transport the same information. By reducing the number of wires it is possible to reduce several critical aspects of a circuit, such as the critical path delay, the total area and also the total power and energy demanded. In the MVL field, quaternary logic has been reported as a way to gain area and power when using quaternary circuits instead of binary ones (MAHAPATRA; IONESCU, 2005; SHEIKHOLESLAMI; YOSHIMURA; GULAK, 1998; ZILIC; VRANESIC, 1993). Today, the memory manufacturers are the principal users of multiple-valued circuits, since they are providing drastic improvement of the storage capacity when multiple-valued technology is used (BAUER et al., 1995). Space companies in particular have started the

investigation of the possible adoption of FPGAs (GAC, 2003) based on quaternary logic in the field for space missions without any formal publishing up to this time.

The short time to market provided by FPGAs, plus the vast quantity of tools one can find to assist a design project, together with the great flexibility offered in an FPGA chip make them the first choice of designers to implement the hardware of different systems, targeting low and even medium fabrication volumes. However, with the introduction of advanced technology nodes, interconnection delays are becoming one of the main concerns when it comes to the global circuit delay, together with area and power consumption. In FPGAs the huge amount of interconnections plays an even more important role in the circuit delay (PRAGASAN, 2001), power consumption (FEI et al., 2005) and area (SINGH; PARTHASARATHY; MAREK-SADOWSKA, 2002), as one can have as much as 90% of the chip area devoted for the interconnection of the blocks.

FPGAs allow designers to implement hardware systems together with the possibility to explore any level of parallelism available in the application, with excellent time-to market and reduced non-recurring engineering costs. On the other hand, this flexibility is paid with a huge amount of circuit area, delay and power, taken by all the routing switches and wires. In order to reduce these interconnection related costs, the use of multi-valued logic, more precisely quaternary logic applied to FPGAs is an open subject with almost no meaningful research or results.

Although the appealing aspects offered, the new generation of quaternary-levels technology is resulting more sensitive to process variations due to the reduced transistor dimensions. Furthermore, these technologies will be extremely sensitive to high-energy particle strikes such as neutrons from cosmic rays and alpha particles, which represent a concern not only for spatial applications, but also for general-purpose applications working at low altitude and even at the sea level. In today's circuits, the Soft Error Rate (SER) which represent a measurement of the radiation sensitivity of a given technology or device, is becoming one of the principal aspects in designing integrated circuits, together with performance or power characteristics. Several research works deal with the SER characterization and mitigation for binary circuits, while for multiple-value logic like quaternary logic this remains an open subject that needs to be addressed.

This thesis shows that quaternary logic circuits can have appealing characteristics for space applications, not only because quaternary circuits reduce the interconnection related costs, like for instance, number of interconnections, logic area, power consumption, but also because of some specific characteristics of the quaternary circuits that can be applied to fault tolerant circuits. The quaternary circuits presented in this thesis are a result of the study of the quaternary circuits'

vulnerabilities throughout extensive fault injection experiments taking into account the architectural and timing vulnerability aspects of the proposed circuits. After the evaluation of the quaternary circuits, modifications as well as new topologies of circuits were proposed and evaluated by comparing the proposed quaternary circuits with the binary version protected with the most faire technique, as will be explained in the experimental results analysis.

In this thesis, the reader is conducted to the subject of quaternary circuits applied to the construction of a fault tolerant CLB, which is the main block of an FPGA. At Chapter 2, it is presented the background and basic concepts that are important to the understanding of the contributions of this work, composed by the quaternary logic background and the basic quaternary circuits that have been used as starting point of this work, followed by the fault tolerance subject background. At the Chapter 3, it is presented the first contributions of this thesis trough the process followed to develop the fault tolerant quaternary circuits that are used in the construction of the fault tolerant CLB. Chapter 4 presents the area, power and performance overheads of the circuits presented at Chapter 3 while Chapter 5 presents the Fault Tolerant Quaternary Configurable Logic Block (FT-QCLB), which is the main contribution of this work. Chapter 6 presents the conclusions and open subjects that can be foreseen for the work presented in this thesis.

# 2 CONTEXT OF THE RESEARCH

This chapter presents the context of the research developed during this thesis and is divided in three sections. The first one presents the basis of quaternary logic followed by the quaternary circuits already developed by other researchers. In the second section, the most commonly found sources of radiation and their effects in digital circuits are presented. After that, some of the most used and known techniques applied to detect and mitigate errors in digital circuits are presented and analyzed, together with a brief discussion of the positive and negative aspects of each technique.

# 2.1 Quaternary Logic Background

When working with multiple-valued logic, an important metric to evaluate the logic capacity is the number of possible functions that one can obtain with a given number of inputs. This number can be calculated with the following equation (1):

$$F = B^{B^n} \tag{1}$$

Where 'B' is the radix or the base, and 'n' is the number of variables that compound the function. As a practical example let us consider a binary logic function with 2 inputs. In this case the number of functions that can be obtained can be calculated as follows (equations 2 and 3):

$$F = 2^{2^2} \tag{2}$$

$$F = 16 \tag{3}$$

Bellow one can see in Table 2.1 the 16 possible functions that one can have considering the previous example of binary logic functions with 2 inputs (A and B in table below).

|   |   |    |    |    |    |    |    | -  | _  |    |     |     | _   |     |     |     |     |

|---|---|----|----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|

| Α | В | f1 | f2 | f3 | f4 | f5 | f6 | f7 | f8 | f9 | f10 | f11 | F12 | f13 | f14 | f15 | f16 |

| 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| 0 | 1 | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 0  | 0   | 0   | 0   | 1   | 1   | 1   | 1   |

| 1 | 0 | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 1  | 0  | 0   | 1   | 1   | 0   | 0   | 1   | 1   |

| 1 | 1 | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1   | 0   | 1   | 0   | 1   | 0   | 1   |

**Table 2.1.** Binary Logic Functions with 2 Inputs

Source: Created by the author.

One can easily identify at Table 2.1 the corresponding function implemented by the basic binary logic gates, the 2 inputs NAND gate at the f15 column, as well as the one implemented by the NOR gate, in the f9 column, and the 2 inputs XNOR gate, in the f11 column of the same table. The other functions can be obtained by a combination of the basic binary gates and the inverter gate like the AND function, presented in column f2.

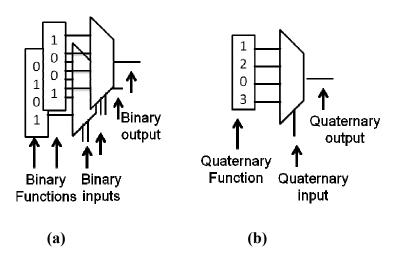

In multiple valued-logic such as quaternary logic, one can have 4 possible logic values (here expressed by the numbers 0, 1, 2 and 3) and therefore, the number of quaternary functions that one can have is exponentially greater than the binary one with the same number of inputs. In order to a binary function have the same capacity as a quaternary one, it is necessary the combination of two binary circuits with the double of the number of inputs as the quaternary one. For instance, if one has a quaternary LUT with 1 quaternary input, one would need the combination of 2 binary LUTs with 2 binary inputs to have the same number of functions. This can be explained mathematically by the reasoning that follows.

Let us consider a binary function called ' $F_B$ ' with 'k' binary inputs and a quaternary function called ' $F_Q$ ' with 'j' quaternary inputs. The binary function equivalent, here called ' $F_Beq$ ', to the quaternary one is given by the following equations:

$$F_B eq = F_O \tag{4}$$

As one needs the combination of any two binary functions to have the same capacity as the quaternary one,

$$F_B.F_B = F_O \tag{5}$$

With equation 1,

$$2^{2^k} \cdot 2^{2^k} = 4^{4^j} \tag{6}$$

$$2^{2^{k+1}} = 2^{2 \cdot 2^{2 \cdot j}} (7)$$

$$2^{2^{k+1}} = 2^{2^{2\cdot j+1}} (8)$$

Which gives us,

$$k = 2.j \tag{9}$$

Which means that the number of binary inputs k must be equal to the double of the number of quaternary inputs j in order to have the same logic capacity as the quaternary circuit. This prove that the use of quaternary logic can reduce the number of interconnections in a circuit, and consequently reduce all the related costs like propagation delay, area and energy consumption of a quaternary integrated circuit (IC) based system. Not only the number of interconnections but also the total number of transistors of an integrated circuit can be reduced when one use multivalued circuits, especially quaternary circuits. This assumption will be proven at Chapter 4. The Appendix A is referred for more information about the binary to quaternary conversion applied to lookup tables.

The next section summarizes the most relevant research related to multivalued circuits and its pros and cons.

#### 2.1.1 Current-Mode Multivalued-Circuits

Multivalued logic (MVL) have been the subject of research of several works in the past, motivated by the objectives of improving the quantity of information to be transmitted in a single wire, improving the capacity of storage devices and also to increase the performance of processing elements. According to Hurst (HURST, S. L., 1984), even before the advent of the semiconductor technology as we know it today, with the well consolidated CMOS technology, some multivalued logic systems were implemented with electromagnetic relay and its derivatives. Despite simple relays were binary in nature (energized or deenergized), there were also available multiple-position devices, such as ten-position uniselectors, three-position polarized relays with a central deenergized state, and other variants.

As the technology evolved to the planar MOS technology, the publishing in the multivalued logic field have also followed this new technology trend. From the late 1950's onwards, with the advent of the solid-state devices, in the form of transistors with more than two stable states, a

certain number of multivalued switching circuits, particularly ternary ones, started to be published (DRUZETA; VRANESIC; SEDRA, 1974; DUNDERDALE, 1970; HURST, STANLEY L., 1978). These first circuits were called current mode circuits because they used different level of current to emulate the different logic levels.

Only in 1983 with (FREITAS, D. A.; CURRENT, 1983a;1983b), after several attempts to develop multivalued circuits, the first large scale circuits started to be produced. By that time, the proposed non binary circuits did not intend to replace completely the binary ones, but only to offer an alternative with better performance in certain domain of applications and still being compatible with the traditional CMOS process. In certain domains of application like for instance, in the arithmetic circuits domain, the use of current-mode multivalued circuits presents excellent results in terms of performance and area (CURRENT, 1990; FRIEDMAN et al., 1977; KAWAHITO et al., 1994).

As it was stated before, these current mode circuits were designed only for specific functions that could be done in a more efficient way than the binary ones. They were intended to be only a part of a mixed, part binary and part multivalued, circuit and therefore needed converter circuits in the frontier with the binary logic. These converter circuits were inspired in the current comparator circuit and can be referred in (FREITAS, D. A.; CURRENT, 1983a;1983b; FREITAS, DAVID A.; CURRENT, 1984). Besides the arithmetic and converters circuits some work also proposed quaternary current-mode latches (CURRENT, 1989; CURRENT; HURLSTON, 1991), quaternary adder with latch (CURRENT, 1990) and current-mode quaternary analog to digital converter (ADC). As these basic current mode MVL circuits started to show up in literature, some other derivative circuits like the full adder with signed digit (GONZALEZ et al., 2000; GONZALEZ; MAZUMDER, 1998), the dual rail differential logic (HANYU; IKE; KAMEYAMA, 1999; HANYU; SAITO; KAMEYAMA, 1998) and the dual rail source coupled and the dynamic source-coupled logic (HANYU; MOCHIZUKI; KAMEYAMA, 2003).

Although these multivalued current mode circuits had some advantages in comparison to the binary ones, especially in the arithmetic domain, these current mode circuits presented a high static power consumption, as they need a constant current flow to hold the different logic levels and keep the circuits working. Despite some of the works previously mentioned proposed the use of lower levels of current to reduce the static consumption, this solution not only did not solve the problem but also leaded to another important problem inherent to the multivalued logic subject, which is the reduction of the margin noise.

In the embedded system era there is no space for static consumption circuits and everything needs to be low power. This is a key reason why we do not see any current mode multivalued logic circuit working in large scale. Current mode circuits need a constant current flow that causes a high static consumption which is the reason why the current mode multivalued circuits were precluded and gave space to the voltage-mode multivalued circuits.

### 2.1.2 Voltage-Mode Multivalued Logic Circuits

In voltage mode multivalued logic circuits, the different logic levels are realized by different levels of voltage. These different levels can be implemented with voltage dividers and also dedicated sources of supply. The first work in the subject of quaternary logic using voltage-mode circuits started to be published in 1986 in (YASUDA et al., 1986). In that work, the authors presented the first version of the quaternary voltage-mode circuits called as "inverter" presented in Figure 2.1, equivalent to "NAND", equivalent to "NOR" and "delta literal" circuits with NMOS technology. In multivalued logic, the name of the logic gates that are used in binary logic, which are "inverter", "AND", "OR" and their variations, lose their meaning. In multivalued logic the logic gates are usually called as "diametrical inverter", instead of "inverter", "MIN" instead of "AND" and "MAX" instead of "OR".

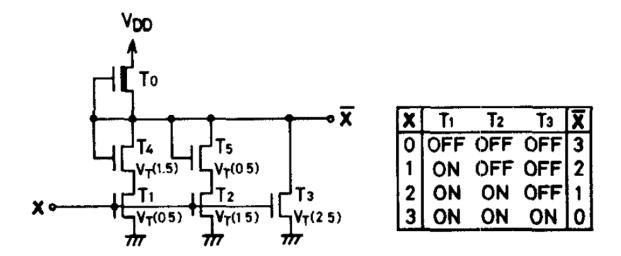

Figure 2.1. Quaternary Inverter proposed by (YASUDA et al., 1986)

(Source: (YASUDA et al., 1986))

One can see from Figure 2.1 that the inverter circuit proposed at (YASUDA et al., 1986) use three different enriched and one depletion transistor. The threshold voltage of each transistor is written in parenthesis. The NMOS based circuits have the drawback of the static consumption of

current. Also in (HEUNG; MOUFTAH, 1985) the authors proposed ternary circuits with lower consumption using both, PMOS and NMOS enriched and depletion transistors, as well as external sources of power supply. Also in the same work, the authors proposed the ternary "AND" and "OR" equivalent circuits.

In (THOIDIS, I. et al., 1998; THOIDIS, I. M. et al., 2001), the authors presented the low power "delta literal" circuits as well as converter circuits from binary to quaternary and vice versa using 2 PMOS and 2 NMOS transistors, both being one of enriched and another of depletion type, using 0.18μm technology with the four voltage levels defined as 0V, 1V, 2V and 3V representing the level 0, level 1, level 2 and level 3 respectively. These circuits were later used in (THOIDIS, IOANNIS M.; SOUDRIS; THANAILAKIS, 2004) to propose the first voltage-mode quaternary full adder presented in literature. Simulation results using the SPICE (NAGEL, 1973) simulator with 0.7 μm technology and presented a critical path delay of 15.9ns.

In (SHIBATA; OHMI, 1993) the authors propose the so called "Neuron MOS" transistors constructed with a double poly-silicon layer. This double poly-silicon layer allows one to set a certain threshold voltage (Vth) deviation in the transistor, which enables the construction of multi Vth transistors that are used in the implementation of the basic circuits used in the construction of the multivalued basic gates. Although this work proposes an alternative process to the traditional ion implantation, this method demands the "programming" of the additional poly-silicon layer of each transistor, with its different VT deviation, which is a big overhead. Using the proposed "Neuron MOS" transistors, the authors in (PARK et al., 2004) presented the quaternary MIN/NMIN, MAX/NMAX and the quaternary adder/subtractor circuits with 0.35μm technology simulated with the SPICE simulator.

In (LEBLEBICI; GURKAYNAK, 1998; OZDEMIR et al., 1996; SCHMID; LEBLEBICI, 2004) the authors proposed multivalued logic circuits equivalent to the inverter, NAND and NOR binary gates using the so called "Capacitive Threshold Logic".

Despite of the big number of publications related to the multivalued logic topic of research, none of the proposed work presented real advantages of using the multivalued version of circuits instead of the traditional binary ones. The current mode attempts, presented good performance results but with the cost of static current consumption, which precluded its usage. When it comes to the publications related to the voltage-mode circuits presented up to the year of 2004, none of the works presented were able to combine low power and high or even compatible performance to the binary circuits.

In (GONÇALVES DA SILVA, R. C.; BOUDINOV, H.; CARRO, L., 2006), the authors proposed a new family of voltage-mode quaternary CMOS circuits composed of a quaternary inverter, NMIN and NMAX circuits, with high performance and low power/energy consumption than any other quaternary voltage mode circuits proposed up to that time. The circuits proposed used three sources of supply, 3V, 2V and 1V, besides the reference 0V that formed the four logic levels of the quaternary circuits and where simulated at the TSMC 0.18 μm technology. To implement the quaternary circuits the authors used 3 PMOS and 3 NMOS with different voltage thresholds. Later on, the same authors proposed in (GONÇALVES DA SILVA, R. C.; BOUDINOV, H. I.; CARRO, L., 2006) a quaternary full adder with 76% reduction in power dissipation, 15% improvement in performance with 20% of area overhead in comparison to the equivalent circuit implemented in binary logic. The authors used the same TSMC 0.18 μm technology, transistors and voltage sources as in the previous work. In (CUNHA; BOUDINOV; CARRO, 2007), the same authors compared quaternary look-up tables with the correspondent binary ones. Simulation results showed that the quaternary LUT with 2 inputs had 49.8% less transistors, 70.3% less power dissipation and 5% better performance than its binary equivalent.

More recently in (VASUNDARA; GURUMURTHY, 2009), the authors presented the same circuits with the same topologies as proposed in (GONÇALVES DA SILVA, R. C. et al., 2006) with the only difference of the technology node used, which was the 90nm MOSIS. As expected the authors obtained faster and lower power circuits in comparison to the previous work. In (DATLA; THORNTON, 2010) the authors present quaternary serial and parallel multipliers with decreased dynamic power dissipation and improved timing performance when compared to binary circuits with equivalent word sizes, especially in the parallel version.

#### 2.1.3 Voltage-Mode Multivalued Logic Circuits Applied to FPGAs

There is not much published work related to multivalued logic applied to FPGAs up to the time that this thesis was written. When it comes to the use of quaternary logic circuits to be used in an FPGA, the work proposed in (RITT et al., 2010) the authors show that when one use quaternary circuits to implement FPGAs one can have a reduction of 27% in the number of transistors and 19% in the number of nets in average. Also in (LAZZARI et al., 2010a;2010b) the authors show that when one use quaternary circuits to reduce the interconnection costs, especially critical in FPGAs, one can have an average gain in area of 33%, less power consumption of 16%, with a small penalty in performance of 11%, comparing to the binary equivalent. The most important result of the previously mentioned paper is that one can have a reduction of more than 50% in wire length and number of switches in average, for the benchmark chosen by the authors.

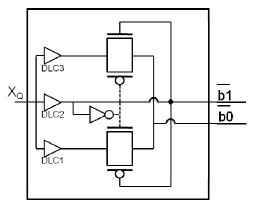

This work proposes a fault tolerant quaternary CLB (FT-Q-CLB) that can be used in the construction of a fault tolerant quaternary FPGA. The FT-Q-CLB of this work is constructed with quaternary logic circuits. Most of the fault tolerant quaternary circuits that are presented here were based on some of the works presented in the previous chapter, but with some hardware improvement and implemented using the 90nm technology with VCC of 1.2V. This way, the four logic values '0', '1', '2' and '3' have the corresponding voltage of '0V', '0.4v', '0.8V' and '1.2V' respectively. The following chapter presents the quaternary circuits used as base for the development of the fault tolerant components used in the construction of the FT-Q-CLB proposed in this work as well as the characterization of the SET phenomena that is considered in this work.

# 2.2 Quaternary Base Circuits

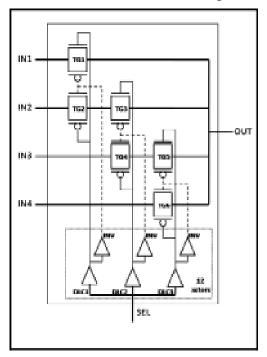

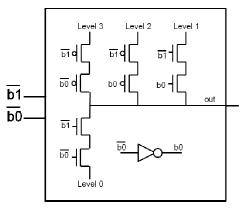

One of the main components of the quaternary CLB is the quaternary Lookup-Table proposed by here referred as QLUT that is illustrated in Figure 2.2. The quaternary lookup table (QLUT) of 0 is based on voltage-mode quaternary logic CMOS circuits. These circuits use several different transistors with different threshold voltages that are presented in Table 2.2, and operates with four voltage levels, corresponding to the logic levels '0', '1', '2' and '3'. The QLUT cell is designed using Down Literal Circuits (DLCs), binary inverters and pass transistor gates. The Down Literal Circuits perform the decoding function shown in Table 2.3. There are three possible Down Literal Circuits in quaternary logic, named DLC1, DLC2 and DLC3. The Down Literal Circuits are designed in CMOS technology with 3 different threshold voltages for PMOS transistors, and 3 different threshold voltages for NMOS transistors.

Figure 2.2. Standard QLUT schematic circuit with 1 quaternary input

(Source: Created by the author)

One can understand the behavior of the QLUT of Figure 2.2 by looking at the DLC truth table at Table 2.3. More details on the QLUT circuit can be found in (CUNHA et al., 2007).

Table 2.2. Threshold Voltage of the Different Transistors

| Name                 | T1   | T2   | T3   | T4   | T5   | T6   |

|----------------------|------|------|------|------|------|------|

| Threshold<br>Voltage | -1.0 | 1.0  | 0.6  | 0.2  | -0.2 | -0.6 |

| Туре                 | PMOS | NMOS | PMOS | NMOS | PMOS | NMOS |

(Source: Created by the author)

Table 2.3. Truth table of the down literal circuits.

| In            | DLC1          | DLC2          | DLC3          |

|---------------|---------------|---------------|---------------|

| (logic level) | (logic level) | (logic level) | (logic level) |

| 0             | 3             | 3             | 3             |

| 1             | 0             | 3             | 3             |

| 2             | 0             | 0             | 3             |

| 3             | 0             | 0             | 0             |

(Source: Created by the author)

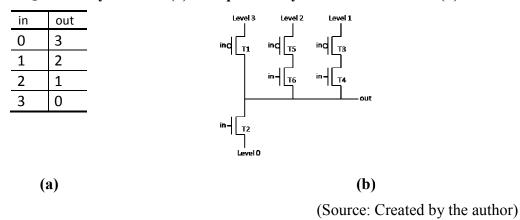

Another important quaternary circuit that is used in the construction of the FT-Q-CLB is the voltage-mode quaternary inverter proposed by (GONÇALVES DA SILVA, R. C. et al., 2006). In quaternary logic, the inverter function has a different meaning as in the binary logic, in which the 2 existent logic values are each other's inversion. In the quaternary logic as there are 4 possible logic

values, the quaternary inverting function must follow a diametrical inversion. Figure 2.3(a) presents the quaternary inverter circuit implemented with the transistors constructed with the threshold voltages presented in Table 2.2. In the same figure one can find the truth table of the quaternary inverter.

Figure 2.3. Quaternary inverter (a) and quaternary inverter truth table (b).

The inverter circuit of Figure 2.3(b) is used to construct a fault tolerant quaternary flip flop that is an important component of the Fault Tolerant Quaternary CLB and will be presented latter on.

In order to have the capacity to tolerate faults, the proposed circuits of this work use variations and also some improvements of some of the well known fault tolerant techniques published so far. The next section introduces the fault tolerance subject starting with the most common sources of radiation, followed by the metrics used in this area and finally the most referenced fault tolerance techniques with a brief discussion of the drawbacks of each technique.

# 2.3 Fault Tolerance Background

This section presents a description of the different types of spatial radiation that can produce or stimulate bit flips in circuits. This section also discusses the most commonly found sources of radiation and their effects in digital circuits. Also, the most used metrics that are applied to measure the vulnerability of the circuits are described followed by some of the most used and known techniques applied to detect and mitigate errors in digital circuits. These different techniques are presented and analyzed, together with a discussion of the positive and negative aspects of each technique.

#### 2.3.1 Radiation Sources and their Effects

There are different types of space radiation that can cause soft errors. In this section the most known and relevant types of radiation sources that can cause SEUs and SETs are presented. Also the effects that SEUs and SETs can cause and the conditions to an error in a certain circuit occur are discussed (HEIJMEN, 2002).

The main sources of radiation catered from space are:

- a) alpha particles;

- b) high energy cosmic neutrons;

- c) boron fission induced by low energy neutrons.

There are other kinds of particles that can cause soft errors, like heavy ions for instance, but they will not be discussed here because they are only relevant for aero-space applications, due to their occurrence only in space or in the highest parts of the earth atmosphere.

#### 2.3.1.1 Alpha Particles

An alpha particle is a doubly ionized helium atom, made of two protons and two neutrons. Alpha particles can be found in circuits packaging materials, solder points of the integrated circuits or in wafers, which are thin slices of semi-conductor material, upon which circuits are constructed. When an alpha particle hits a beta or gamma ray, it loses energy and generates transient current pulses that, depending on their intensity, can cause an SEU (single event upset) which can result in a soft error if it compromises the correct functionality of the circuit.

# 2.3.1.2 High Energy Cosmic Neutrons

This kind of particle is formed by the collision of galactic particles and solar wind particles with the terrestrial atmosphere. Most of cosmic rays are reflected or captured by the geomagnetic field of the earth, and only 1% of the high energy cosmic neutrons hit the earth surface, generating a flux of 25 neutrons/cm<sup>2</sup>.hr (ZIEGLER; LANFORD, 1981) with energy higher than 1 MeV (1 million electron volt) at sea level. Only neutrons with 5 MeV or higher energy are capable of generating soft errors.

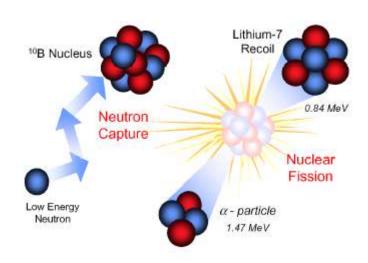

# 2.3.1.3 Boron Fission Induced by Low Energy Neutrons

Another form of radiation can occur when low energy neutrons interact with boron atoms (BAUMANN, R. et al., 1995). As a result, a lithium core and an alpha particle are generated by fission, as depicted in Figure 2.4. Both particles resulting from this reaction are capable of generating SEUs or SETs that can cause the undesired soft errors.

Figure 2.4. Boron fission induced by low energy neutron.

(Source: (BAUMANN, R. C., 2001))

# 2.3.2 Effects of SEUs and SETs in Digital Circuits

A particle hit can affect a combinational as much as a sequential part of a circuit (ALEXANDRESCU; ANGHEL; NICOLAIDIS, 2002). In sequential circuits, like the one shown in Figure 2.5, SEUs can occur only in memory elements (the registers in Figure 2.5). On the other hand, the combinational components can be affected by SETs which, given the right circumstances, can cause an error. The hit of a radiation particle in a memory element does not imply that an SEU will be registered. In order to an SEU occur, it is necessary that this particle has enough charge to create a significant current pulse. In other words, it is necessary that the charge generated by the particle is greater than or equal to the so called critical charge (Q<sub>critical</sub>) of the hit element. The Q<sub>critical</sub> will be explained with more details in following paragraph.

input Combinational logic output

Figure 2.5. Sequential circuit.

(Source: Created by the author)

The occurrence of an SET in combinational logic does not mean that an error will result. In order to an error occur, a combination of events must happen, allowing the SET to be captured or generate and erroneous operation. First, it is necessary that the charge generated by the radiation

source be equal or higher than the  $Q_{critical}$  of the element that was hit. Second, the combinational circuit must be fast enough to propagate the error, and third, the logic of the architecture must allow that the wrong logic value that was generated propagates to some memory element during its latching window or generate an erroneous operation. In Figure 2.6, one can see an example in which the combinational circuit does not allow the SET propagation. The Figure 2.6 shows a small combinational circuit in two different situations. In the first situation (a), the circuit is free of the radiation effects, while in the second (b) the circuit is being affected by a source of radiation. One can see that in booth circuits the result is the same even in the presence of radiation.

Figure 2.6. Combinational circuit without radiation (a) and with radiation (b).

(Source: Created by the author)

#### 2.3.3 Metrics to Evaluate the Vulnerability of Circuits to Soft Errors

The vulnerability of a circuit to soft errors indicates the probability of the circuit to have an error. This probability indicates to the end user how much he can rely on the correct operation of the circuit. With the growing concern about circuit reliability, companies are using some metrics to evaluate their products. In this section, some of the most used metrics proposed by scientists and designers to evaluate the vulnerability of the circuits, which is known as the soft error rate (SER), are presented.

### 2.3.3.1 Failures in Time (FIT)

The fault rate of a circuit can be measured through the number of failures that occur in a certain period of time. This metric is known as *Failures in Time*, or *FIT*. If a circuit has a fault rate of 1 FIT, it means that in a period of 1 billion hours 1 fault will probably occur. Some companies, like IBM, are using this metric as a reference to the design of their products. IBM sets its target for undetected errors caused by SEUs to 114 FIT (BOSSEN, 2002), which means that 1 fault may occur in the time range of about 9 million (8.771.930 to be more precise) hours of device operation. The additive property of FIT makes it convenient for calculation of the fault rate of large systems, because the designer just needs to sum the FIT of all components that are part of the system to have the system FIT.

# 2.3.3.2 *Mean Time to Failure – MTTF*

Another metric that can be applied to measure the fault rate of a system is the mean time to failure. Differently from the FIT, the MTTF is more intuitive, because it indicates the mean time that will elapse before an error occurs. The MTTF has an inverse relation to the FIT, which is expressed by the following equation (10):

$$MTTF (hours) = \frac{10^9}{FIT} \tag{10}$$

### 2.3.3.3 The Soft Error Rate Estimation

The soft error rate (SER) of a system can also be expressed in terms of the nominal soft error rates of individual elements that are part of the system, such as SRAMs, sequential elements such as flip-flops and latches, combinational logic, and factors that depend on the circuit design and the microarchitecture (NGUYEN; YAGIL, 2003; SEIFERT et al., 2001), as follows in equation (11):

$$SER^{design} = \sum_{i} SER_{i}^{no \min al} \times TVF_{i} \times AVF_{i}$$

(11)

where i stands for the i<sup>th</sup> element of the system.

The SER<sup>nominal</sup> for the  $i^{th}$  element is defined as the soft failure rate of a circuit or node under static conditions, assuming that all the inputs and outputs are driven by a constant voltage. The TVF<sub>i</sub>, time vulnerability factor (also known as time derating) stands for the fraction of the time that the element is susceptible to SEUs that will cause an error in the  $i^{th}$  element. The AVF<sub>i</sub>, architectural vulnerability factor (also known as logic derating) represents the probability that and error in the  $i^{th}$  element will cause a system-level error.

The SER<sup>nominal</sup> is defined by the probability of occurrence of an SEU in a specific node of the element. This probability depends on the element type, transistor size, node capacitance and other characteristics of the element. For instance, to estimate the SER<sup>nominal</sup> for a latch, one must know the  $Q_{critical}$ , which identifies the minimum charge necessary to cause the element to fail. This can be done by injecting waveforms of alpha and neutron particle hits on all relevant nodes. Then, it is necessary to evaluate the alpha and neutron flux to which the circuit is submitted. More details can be found in (SEIFERT et al., 2001).

The timing vulnerability factor can be summarized as the fraction of time that the element can fail. For example, the timing vulnerability factor of a latch is equal to the portion of the time that the latch is in its store mode. For combinational logic, the timing vulnerability factor depends

on its type, which can be data path or control path. More details on these and other TVF evaluation aspects can be seen in (NGUYEN; YAGIL, 2003; SEIFERT et al., 2001).

The architectural vulnerability factor of an element can be understood as the probability that a fault in that element causes an error in the system. In Table 2.4 some approaches to estimate the AVF, its major issues, advantages and disadvantages are presented.

Table 2.4. Architectural-vulnerability-factor (AVF) estimation approaches

| Approach              | Description                                                                                                                                                       | Major issues                                                                                                                            | Advantages                                                     | Disadvantages                                                                                                                              |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Fault injection       | Inject error(s) and simulate to see if injected error(s) cause(s) system-level error(s) by comparing the system response with simulated fault-free response       | * Which inputs to simulate;  * How many errors to inject;  * Which signals to inject errors in;  * Which signals to use for comparison. | * Applicable to<br>any design;<br>* Easy<br>automation.        | * Long simulation<br>time (several<br>days or weeks)<br>for statistically<br>significant<br>results;<br>* Dependence on<br>chosen stimuli. |

| Fault-free Simulation | Perform architectural or logic simulation and identify situations that do not contribute to system- level errors, such as unused variables and dead instructions. | * Which inputs to simulate;  * How to identify situations that do not contribute to system-level errors.                                | * Much faster compared to fault injection;  * Easy automation. | * Applicable to very specific designs and not general enough;  * Dependence on chosen stimuli.                                             |

(source: (MITRA et al., 2005))

The AVF value of an element depends on its inputs and also on how important that element is for the circuit considering its functionality. As an example, suppose that the contents of a flip-flop are erroneous. If the flip-flop output drives to an AND gate with another signal whose logic value is 0, the error will have no effect on the output of the AND gate.

The soft error experiments presented in this work are evaluated using an approximation to the methodology explained in this section, which is the soft error rate estimation. More details on the SER experiments will be explained in Chapter 3.

# 2.3.4 Mitigation Techniques for SEUs and SETs

In the first years of spatial exploration, the reliability of the circuits started to become an important concern for designers. At that time, the major technique used to protect circuits was shielding. This shielding technique worked by reducing the particle flow to smaller levels and consequently, reducing the number of errors caused by particle hit to zero. During many years this technique was widely used in aero-spatial applications and guaranteed the correct operation of the circuits. However, with the technology evolution up to nanometer scale, circuits became more susceptible to particle hits, making this shielding technique obsolete for special circuits and even for circuits to be used at sea level.

Trying to reach the level of reliability that once belonged to shielding, scientists have proposed several techniques in the past years, each one with its pros and cons, to mitigate SEUs and SETs. In this section, some of these techniques are presented and their costs, in terms of area and processing time overheads, are discussed.

### 2.3.4.1 Process Modification related techniques

Several process solutions have been proposed to reduce SER sensitivity of circuits, including the usage of well structures, buried layers, deep trench isolation, and implants at the most sensitive nodes. Also wafer thinning has been proposed as a way to reduce SEU sensitivity (DODD et al., 2001). It was shown that the overall SEU threshold LET (linear energy transfer) can be significantly increased if the substrate thickness is reduced to 0.5 µm. In practice, however, several criteria would have to be met to make the thinning of fully processed wafers possible. Another reduction of the SER can be achieved by reducing to almost zero the contribution of errors caused by the particles resulted by the boron fission reaction. This can be done by eliminating BPSG (boron phosphor-silicate glass) from the process flow. If the use of BPSG is necessary, enriched <sup>11</sup>B could be used in the BPSG layers (BAUMANN, R. C., 2001). Silicon-on-insulator (SOI) technologies are relatively insensitive to soft errors. Applying SOI technology instead of the corresponding bulk process improves the SER with a factor in the range of 2 to 8 (HARELAND et al., 2001). However, the cost of materials, especially of the wafers, is higher for SOI. In general, these process modification solutions are expensive and are applied just for a few designs.

### 2.3.4.2 Component Hardening Techniques

There are two basic approaches to improve SER sensitivity at the circuit level. On one hand, the components applied in the design can be modified such that they become less susceptible to soft errors. The main goal of this approach, often named design hardening, is to manufacture SER-reliable circuits using standard CMOS processing without additional masks (VELAZCO et al.,

1994). On the other hand, one can accept that soft errors occur at a certain rate and include extra circuitry to detect and correct them. Error detection and correction techniques are discussed in the next subsection.

Solutions to reduce the SER sensitivity of components can be categorized as techniques to increase the capacitance of the storage node, to reduce the charge collection efficiency, or to compensate for charge loss. The applied design style can have an important effect on SER. For instance, in (SEIFERT et al., 2001) it is demonstrated that level-sensitive latches using transmission gates are more sensitive than edge-triggered static latches, because the former use floating nodes to store information.

Another method to improve SER sensitivity is to enlarge the critical charges by increasing the capacitance of the storage nodes. In fact, if all critical charges are sufficiently large, alpha particles are not able to upset a circuit and neutrons are the only source of soft errors that can affect the circuit. In (KARNIK et al., 2001), an explicit feedback capacitor is added to the node capacitances. In (OOTSUKA et al., 1998), a SER-hardened SRAM cell used stacked cross-coupled interconnects to increase the capacitor area. Enlargement of the node capacitances are not only applied in memory design, but were also shown to be an efficient way to improve the SER sensitivity of sequential or domino nodes in high-performance circuits (KARNIK et al., 2002). The main drawback of increasing the node capacitances is that generally the cell area is increased affecting the memory overall area. The SER sensitivity of SRAM cells and latches can also be improved by adding feedback resistors between the output of one inverter and the input of the other, as shown in Figure 2.7. This SRAM cell topology was proposed in (SEXTON et al., 1991). The transient pulse induced by an ionizing particle is filtered by the two resistors, which slow down the circuit such that it does not have sufficient time to flip state. However, the inclusion of feedback resistors in a memory element has the drawback that the write speed is lowered (VELAZCO et al., 1994).

Figure 2.7. SRAM cell hardened by the inclusion of two feedback resistors

(Source: (SEXTON et al., 1991))

# 2.3.4.3 Circuit Design SEU and SET Hardware Mitigation Techniques

As stated in a previous subsection, process modification solutions are expensive and are used just in few designs with high volume. Also, component hardening techniques involve costs in energy, area and performance that sometimes may not be reasonable for manufacturers. Therefore, the development of techniques not related to the process variation or component modification has been stimulated during the past years, and some design based mitigation techniques have been proposed for the scientific community. In this section, some of the most know and widely used design techniques that have been proposed by researchers worldwide are presented. These techniques are divided into two main groups: error detection techniques and error detection and correction techniques.

# 2.3.4.4 Hardware Error Detection Techniques

This redundancy can be hardware redundancy, also known as space redundancy, or time redundancy. The hardware redundancy approach called duplication with comparison (DWC) is based in the duplication of the module which failing behavior has to be detected, followed by the comparison of the outputs of both modules. If the results do not match, an error signal is activated. This technique can be used to detect either SETs in combinational circuits or SEUs in memory elements. Figure 2.8 illustrates these two situations, time (situation a) and space (situation b) redundancy, to detect SEU and SET, both with one error detected.

Figure 2.8. Combinational circuit (b) by using space (or hardware) redundancy.

(Source: Created by the author)

Time redundancy can be used to detect SETs in combinational logic. This technique detects SETs by capturing the output of the combinational circuit in two different moments in time. The two captured values are compared, and in case of different values, an SET detection is indicated. Figure 2.9 illustrates the use of time redundancy to detect an SET in a combinational circuit.

Figure 2.9. Use of time redundancy to detect an SET in a combinational circuit.

(Source: Created by the author)

The circuit designer must set the " $\Delta$ " time wide enough to allow the SET propagation, but also short enough not to lose the pulse. If a particle hits one of the memory elements used to capture the values, an SEU will be registered and an SET will be erroneously detected. The main drawbacks of detection techniques based on duplication are: the hardware area is more than doubled, and they are only able to detect the events, and not to avoid the occurrence of an error. This way, if the designer wants the circuit to operate correctly, it is necessary that the event detection flag indicates that the operation needs to be repeated and the wrong value must be discarded.

# 2.3.4.5 Hardware Error Detection and Correction Techniques

With the necessity of not only detecting but also correcting the soft errors, researches have proposed some detection and correction techniques based on redundancy of modules. The most

commonly used and known hardware error detection and correction technique is the so called Triple Modular Redundancy, or TMR. The triple modular redundancy (JOHNSON, 1994) first proposed by Von Neumann in 1956, uses the redundancy of modules to guarantee the correct functionality of the circuits in which it is implemented. This technique is based on the triplication of the protected module in a way that, if any of the three modules fails, the other two will guarantee the correct operation of the system. The redundancy used in this technique can be time redundancy or space redundancy. In Figure 2.10, the use of space redundancy of the component that is being protected, together with a voter block, is illustrated. The voter is the module that votes, or chooses, for the majority result from the component blocks to be the circuit result.

Circuit Module 1

Circuit Module 2

Circuit Module 2

Circuit Module 3

Figure 2.10. Use of space redundancy to detect an SET in a combinational circuit.

(Source: Created by the author)

Since all the three modules operate in parallel, this technique corrects any failure in one of the three modules with the performance penalty of the voter delay. On the other hand, the area overhead is more than 200%, due to the triplication of the protected module and the voter. Depending on the size of the module, this area penalty can be a price that the designer cannot afford. In Figure 2.11, the use of TMR with time redundancy to correct a fault in one module is illustrated. The TMR with time redundancy only triplicates the memory elements responsible for capturing the result of the circuit at different moments in time. If we compare the area of both TMRs, the time and the space one, we can say that the time TMR has the lower area overhead if the size of the circuit is smaller than the memory element. On the other hand, the time redundancy TMR will have bigger performance penalty due to the different need to capture the circuit values at three different moments in time. Also, the clock circuit with the two " $\Delta$ " delays adds some extra complexity to the circuit design.

Figure 2.11. TMR with time redundancy.

However, the voter is not free of faults and if a fault hits the voter, the system reliability can be compromised. It is important to mention that the TMR technique is only effective against single faults and in case of a double faults, which means two faults affecting each one a different module, the voter can choose a wrong answer as if it were correct. To guarantee the system reliability against multiple faults, the redundancy has to be increased. This way, N-MR - Modular Redundancy of order N, uses a higher number of modules to guarantee that the majority of the modules operate correctly. In case of double faults, the number of duplicated modules must be five. This way, if two blocks fail, the other three will operate correctly and the voter will be able to choose the right result from the majority. Despite its tolerance to multiple faults, the N-MR has a huge area overhead, which gets to more than 400% for the 5-MR, due to the addition of four copies of the protected module and the voter block. Also, the size of the voter grows geometrically when compared to the TMR version. Since the voter is sensitive to faults, the reliability of the system can be compromised if the size of the voter grows too much.

There are also a lot of software based fault tolerant techniques that can be applied in software based systems. These software based techniques generally have lower area overhead in comparison to the previously mentioned hardware techniques but on the other hand, these techniques end up adding non recurring engineering cost and usually demand considerable extra memory space for the software redundancy. Also there are some errors detecting and correcting codes applied mainly to memory components that are not in the scope of this work and therefore will not be presented here.

# **3 FAULT TOLERANT QUATERNARY CIRCUITS**

This section presents the fault tolerant quaternary circuits that were developed based on the voltage-mode quaternary circuits presented in (CUNHA et al., 2007; GONÇALVES DA SILVA, R. C. et al., 2006). The circuits presented in this section were designed, simulated and analyzed separately to, latter on, be assembled together to form the main result of this work, which is the fault tolerant quaternary configurable logic block (FT-QCLB). In order to evaluate the variability impact of the quaternary circuits, Mote Carlo simulation results are presented for the Quaternary LUT cell with 2 inputs.

The first fault tolerant quaternary circuit developed was the quaternary lookup-table (FT-QLUT), which is presented in the following subsection.

# 3.1 Fault Tolerant Quaternary Lookup Table (FT-QLUT) and the Error Avoiding Quaternary Lookup Table (EA-QLUT)

In this subsection it is presented the FT-QLUT that was designed to detect and tolerate single faults by indicating whenever a single event generates a soft error. In order to become fault tolerant, the Quaternary LUT presented in Figure 2.2 was studied in the search of its fragilities. After finding all the weakness of the QLUT, it was proposed a fault tolerant technique to overcome each of them. The next subsections present first, the evaluation of the weak points of the QLUT of 0 followed by the proposed architecture to overcome its weakness and the fault injection experiments that were taken to evaluate the proposed architecture.

#### 3.1.1 QLUT Fragilities

In order to propose fault tolerant version of the QLUT, it was started a study to raise the fragilities of the QLUT cell first presented in 0 and represented bellow in Figure 3.1 with some important components and connections labeled. As one can see from Figure 3.1, the quaternary input (labeled as "SEL" at the figure) is decoded by the 3 types of DLCs in binary values according to the table already presented (Table 2.3). These decoded binary values, together with its inverted values are used to control the so called transmission gates (TGs) to connect the desired quaternary signal to the circuit output. In a free of faults environment, the correct behavior of the cell is guaranteed, but in the presence of faults caused by an event like a high energy particle strike at a critical component of the QLUT like, for instance, one DLC, could compromise the QLUT functionality. In order to illustrate this scenario, let's consider this example in which the SEL input holds the quaternary level of '0'. In a free of faults environment, this would mean that the value present at the input 'IN1' would be connected to the QLUT output. On the other hand, if a fault event would affect the DLC1 component with enough charge to provoke its incorrect behavior, this would result in an inversion of its output value, which in our example would be from quaternary level '3' to quaternary level '0'. This event would change the selected value to be connected to the QLUT output from the value connected to 'IN1' to the value connected to 'IN2', which would characterize an error at the QLUT. The origin of this error can be understand by looking at the DLC decoding table (Table 2.3) and comparing the decoding of level '0' and level '1'. One can see that only the DLC1 component contributes for the difference between the two decoding values and in case that the DLC1 fails, the 'IN2' connected value can be erroneously selected instead of the 'IN1' one, and vice-versa. The same behavior can be observed in case that the input level is equal to quaternary '1' or '2', in which only the DLC2 component is responsible for the differentiate between the value connected to 'IN2' or 'IN3'. At the same way, the DLC3 component is the only one to differentiate between the quaternary input levels '2' and '3'. The conclusion of this analysis is that the decoding signals generated by the DLCs are not robust enough to tolerate transient faults. Even if one use a circuit to detect errors in the decoding, this circuit would not be able to differentiate between an erroneous code and a valid one as the erroneous one could also be valid as they are equal to valid codes.

Besides the DLCs, there are other sources of vulnerability that can be pointed which are the transmission gates TG1 and TG6 of Figure 3.1. The TG1 and the TG6 are lonely in the connection path between an input 'IN1' and 'IN4' respectively and the output. This way if a faulty event happens to cause the undesired conduction of one of these transistors at the same time that another

input is selected, and if the two paths have different values, this would be characterized as an error in the QLUT circuit.

Figure 3.1. Labeled quaternary lookup table with 1 input

(Source: Created by the author)

After identifying the vulnerable points of the QLUT circuit, it was proposed some modifications in the design of the QLUT cell in order to present a more reliable functionality. The next subsection presents the proposed FT-QLUT architecture.

#### 3.1.2 Proposed Architecture