# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA – FÍSICA – ESCOLA DE ENGENHARIA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA - PGMICRO

## HENRIQUE LUIZ ANDRADE PIMENTEL

# Projeto de um Amplificador de Baixo Ruído em Tecnologia CMOS 130nm para a Banda de 50MHZ a 1GHz

Dissertação apresentada como requisito parcial para a obtenção do grau de Mestre em Microeletrônica.

Prof. Dr. Sergio Bampi Orientador

Porto Alegre, maio de 2012.

# CIP - CATALOGAÇÃO NA PUBLICAÇÃO

#### Pimentel, Henrique Luiz Andrade

Projeto de um Amplificador de Baixo Ruído em tecnologia CMOS 130nm para frequências de 50MHZ a 1GHz / por Henrique Luiz Andrade Pimentel – Porto Alegre: Programa de Pós-Graduação em Microeletrônica da UFRGS, 2012.

98 f.:il.

Orientador: Sergio Bampi

Dissertação (mestrado) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica. Porto Alegre, BR – RS, 2012.

1.LNA. 2.Amplificador de baixo ruído 3.Sistema RF 4.Projeto de Circuitos Integrados. I. Bampi, Sergio. II. Projeto de um Amplificador de Baixo Ruído em tecnologia CMOS 130nm para frequências de 50MHZ a 1GHz.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Aldo Bolten Lucion Diretor do Instituto de Informática: Prof. Luís C. Lamb Coordenador do PGMicro: Prof. Ricardo A. L. Reis

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

## **AGRADECIMENTOS**

Antes de tudo, quero agradecer a Deus, por abençoar todos os dias da minha vida, iluminar o meu caminho e me dar forças para ir sempre em frente.

Aos meus grandes professores e ídolos, aqueles que em momento algum duvidaram da minha (nossa) vitória, meus amados pais Henrique e Elbaniza.

À minha grande irmã, incentivadora e eterna conselheira, Danielle.

Ao meu orientador, Prof. Dr. Sergio Bampi, pela orientação, apoio e principalmente pela confiança depositada em mim.

À UFRGS pela excelente estrutura técnica, organização e grau de excelência de seus docentes e funcionários.

Ao nosso grupo de trabalho do Laboratório da PGMICRO, Dalton, David, Juan, André e Alexandre.

Ao meu grande amigo, Dr. Fernando Cortes, colaborador e incentivador deste trabalho.

Aos meus novos amigos que conheci no Rio Grande do Sul, em especial os da CEITEC-SA, por me proporcionarem todos os dias um grande aprendizado sobre esse fantástico mundo da Microeletrônica.

Ao meu antigo orientador, Prof. Dr. Luiz Carlos Kretly, pela orientação e incentivo a continuar o mestrado, mesmo que fora da UNICAMP.

Aos antigos amigos de Campinas/SP, com os quais tive o prazer de conviver durante anos, seja nas repúblicas, no laboratório de antenas, na UNICAMP, no CI-Brasil ou na Eldorado.

Aos paraenses da Unicamp\_para, que me ensinaram que família não é formada apenas por pessoas do mesmo sangue.

Enfim, a todos que, de uma maneira ou outra, apoiaram o desenvolvimento deste trabalho.

# **SUMÁRIO**

| LIST           | 'A DE ABREVIATURAS E SIGLAS                                 | 6  |

|----------------|-------------------------------------------------------------|----|

| LIST           | 'A DE FIGURAS                                               | 7  |

|                | 'A DE TABELAS                                               |    |

|                | U <b>MO</b>                                                 |    |

|                | TRACT                                                       |    |

|                | NTRODUÇÃO                                                   |    |

|                | CONCEITOS BÁSICOS DE RF (RADIO FREQUÊNCIA)                  |    |

|                |                                                             |    |

| 2.1            | Linearidade  Distorção                                      |    |

| 2.2            | Intermodulação                                              |    |

| 2.4            | Ponto de compressão de 1 dB                                 |    |

| 2.5            | Estágios não lineares em cascata                            |    |

| 2.6            | Ruído                                                       |    |

| 2.6.1          | Ruído referenciado à entrada                                |    |

| 2.6.2          | Figura de ruído                                             | 20 |

| 2.6.3          | Figura de Ruído de estágios em cascata                      | 21 |

| 2.7            | Parâmetros de espalhamento                                  |    |

| 2.7.1          | Definição de parâmetros-S                                   |    |

| 2.8            | Estabilidade                                                |    |

| 2.9            | Sensibilidade e Faixa Dinâmica                              |    |

|                | RANSISTORES MOS EM RF                                       |    |

| 3.1            | Efeitos Não Quase Estáticos (NQS - Non-Quasi-Static models) |    |

| 3.2            | Modelamento em RF                                           |    |

| 3.2.1          | Resistência de Porta (Rg)                                   |    |

| 3.3            | Frequência de Trabalho                                      | 32 |

| 3.4            | Fontes de ruído no transistor MOS                           |    |

| 3.4.1<br>3.4.2 | Ruído no canal                                              |    |

| 3.4.2          | Ruído devido aos componentes resistivos parasitas           |    |

| 3.4.4          | Ruído Shot                                                  |    |

| 3.4.5          | Ruído Flicker ou 1/f                                        |    |

| 4 A            | MPLIFICADOR DE BAIXO RUÍDO - LNA                            |    |

| 4.1            | Características básicas do LNA                              |    |

| 4.1.1          | Especificações                                              |    |

| 4.1.2          | Configurações de LNAs                                       |    |

| 4.1.3          | Funcionamento de uma topologia básica                       |    |

| 5 L            | NA MULTIBANDA                                               |    |

| 5.1            | Tipos de LNA Multibanda                                     |    |

| 5.2            | Diferentes especificações de LNA's Wideband e Multibanda    |    |

| 5.3            | Topologia adotada no projeto do LNA                         | 49 |

| 5.3.1          | Técnica de cancelamento do ruído                            |    |

|                | O Princípio do cancelamento do ruído                        |    |

|                | 2 Cálculo do cancelamento do ruído                          |    |

|                | S Cálculo da figura de ruído                                |    |

| 5.3.1.4        | Análise de linearidade                                      | 54 |

| 56 |

|----|

| 56 |

| 56 |

| 57 |

| 57 |

| 61 |

| 63 |

| 66 |

| 66 |

| 66 |

| 68 |

| 68 |

| 69 |

| 69 |

| 70 |

| 71 |

| 73 |

| 74 |

| 76 |

| 76 |

| 77 |

| 77 |

| 78 |

| 79 |

| 79 |

| 80 |

| 81 |

| 82 |

| 84 |

| 84 |

| 84 |

| 85 |

| 85 |

| 86 |

| 88 |

| 89 |

| 90 |

| 91 |

| 91 |

| 92 |

| 93 |

| 95 |

| 96 |

|    |

# LISTA DE ABREVIATURAS E SIGLAS

EDA Analog Design Environment

CMMB China Multimedia Mobile Broadcasting

CR Cognitive Radio

DVB Digital Video Broadcasting

GSM Global System for Mobile Communications

HD Harmonic distortion factors

HF High Frequency

HIPERLAN High Performance Radio LAN

HSDPA High-Speed Downlink Packet Access

IM Intermodulação

IP3 Ponto de interceptação de 3º ordem ISM Industrial, scientific and medical

LNA Low Noise Amplifier

LTE Long Term Evolution

NF Noise Figure

NQS Non-Quasi-Static models

P1dB Ponto de compressão de 1dB

PDA Assistente pessoal digital

QS Quasi-Static models

RF Radio Frequência

SoC System-on-a-chip

SNR Relação sinal-ruído

UMTS Universal Mobile Telecommunication System

UWB Ultra-wideband

WCDMA Wide-Band Code-Division Multiple Access

WiBro Wireless Broadband

WLAN Wireless Local Area Network

# LISTA DE FIGURAS

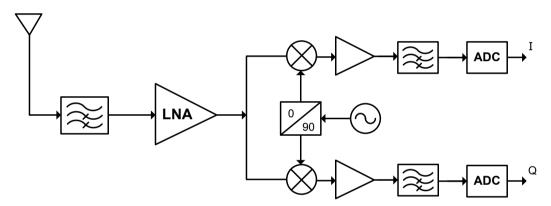

| Figura 2.1: Diagrama de blocos de um sistema de recepção tipo heteródino em quadratura               | 13 |

|------------------------------------------------------------------------------------------------------|----|

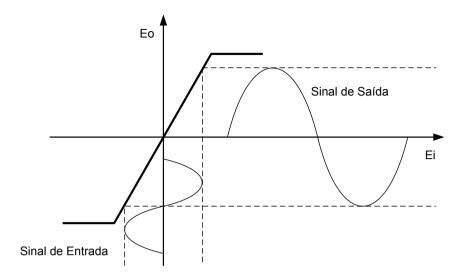

| Figura 2.2: Curva de Transferência de Amplificador com dispositivos ativos.                          |    |

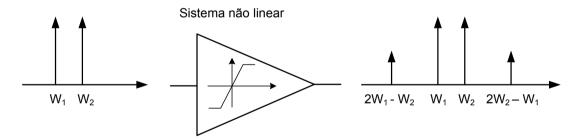

| Figura 2.3: Produtos de Intermodulação em um sistema não linear.                                     | 15 |

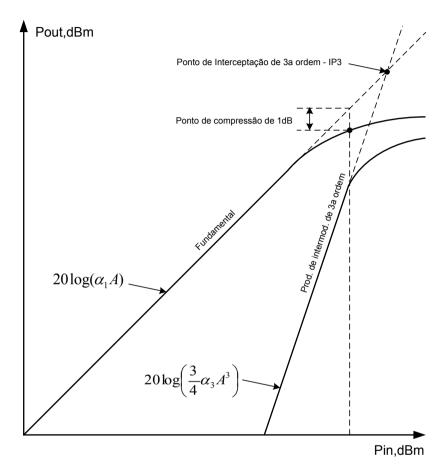

| Figura 2.4: Métricas utilizadas em projetos de RF (Navas, 2005)                                      | 17 |

| Figura 2.5: Ponto de compressão de 1 dB.                                                             |    |

| Figura 2.6: Estágios não lineares em cascata.                                                        |    |

| Figura 2.7: Performance do ruído em um circuito real.                                                | 20 |

| Figura 2.8: Estágios de ruído em cascata.                                                            |    |

| Figura 2.9: (a) Definição dos SP e (b) ondas incidente e refletida em um quadripolo.                 | 22 |

| Figura 3.1: Transistor intrínseco com fontes de polarização DC e fontes de tensão de pequenos sinais |    |

| (Tsividis, 1999).                                                                                    | 27 |

| Figura 3.2: Modelo de pequenos sinais para um transistor completo (Tsividis, 1999).                  |    |

| Figura 3.3: Modelo prático de pequenos sinais para um transistor (Tsividis, 1999).                   |    |

| Figura 3.4: (a) Layout de um transistor simples; (b) aproximação de conjuntos (Tsividis, 1999)       |    |

| Figura 3.5: Transistor com contato da porta em ambos os lados (Tsividis, 1999).                      |    |

| Figura 3.6: Modelo simplificado do transistor.                                                       |    |

| Figura 3.7: Modelo simplificado do transistor MOS em saturação com fonte de ruído no canal           |    |

| Figura 3.8: Modelo do transistor MOS com ruído devido à resistência de porta.                        |    |

| Figura 4.1: Compromisso dos parâmetros no projeto de um LNA.                                         |    |

| Figura 4.2: Arquiteturas de (a) Saída única e (b) Diferencial.                                       |    |

| Figura 4.3: Casamento de impedância: (a) Terminação Resistiva; (b) Terminação 1/gm; (c)              |    |

| Realimentação Série; (d) Degeneração Indutiva.                                                       | 41 |

| Figura 4.4: Configuração degenerada por fonte com transistor MOS: (a) Circuito; (b) Modelo           |    |

| simplificado para o calculo de Zin.                                                                  | 42 |

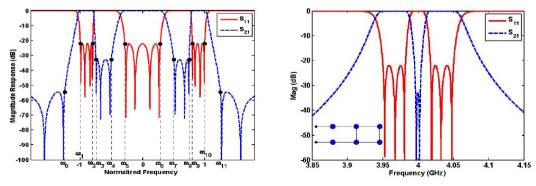

| Figura 5.1: Exemplo conceitual de um receptor multibanda (Wu e Razavi, 1998).                        |    |

| Figura 5.2: Exemplo de solução com conjunto de redes de ajuste usando uma chave: (a) Pseudo LNA      |    |

| três bandas; (b) Rede utilizada para casamento de impedância (Lavasani, Chaudhuri e Kiaei, 2003)     |    |

| Figura 5.3: Exemplo da resposta em frequência de filtros complexos multibanda (Zhang, et al. 2007).  |    |

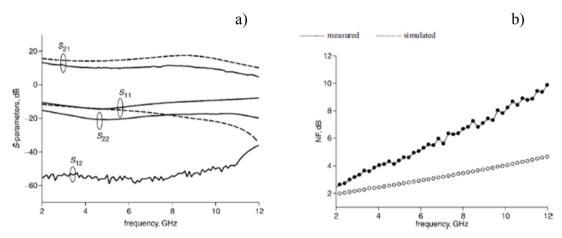

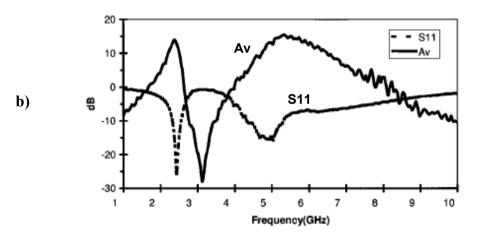

| Figura 5.4: exemplo da resposta em frequência de LNA's Wideband: Medida e simulação de: (a)          |    |

| Parâmetros-S; (b) Figura de Ruído (Kim, Jung e Lee, 2005).                                           | 46 |

| Figura 5.5 Exemplo de (a) LNA's Multi-banda e da sua (b) resposta em frequência (Engberg, 1995).     |    |

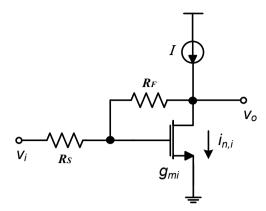

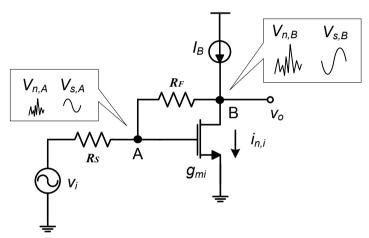

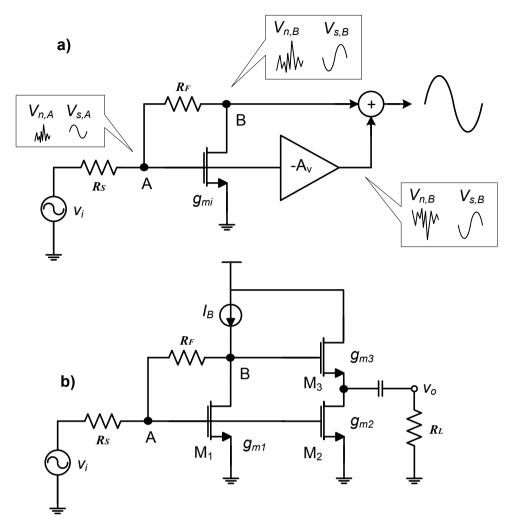

| Figura 5.6: Estrutura de um amplificador com realimentação resistiva.                                |    |

| Figura 5.7: Tensão de (a) Ruído e (b) Sinal gerados no amplificador.                                 |    |

| Figura 5.8: (a) Estrutura de cancelamento do ruído (b) com implementação básica (Bruccoleri,         |    |

| Klumperink e Nauta, 2004).                                                                           | 51 |

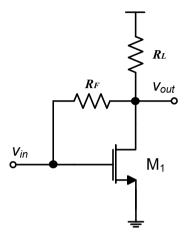

| Figura 6.1: Amplificador fonte-comum com realimentação resistiva.                                    |    |

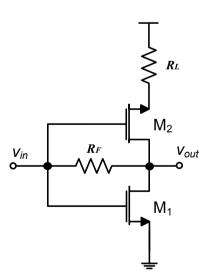

| Figura 6.2: Inversor push-pull com realimentação resistiva.                                          |    |

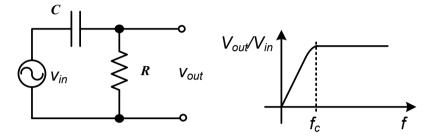

| Figura 6.3: Circuito e resposta de um filtro RC passa-alta.                                          |    |

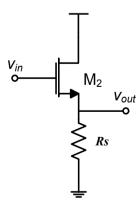

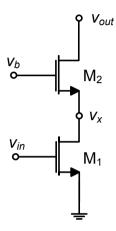

| Figura 6.4: Amplificador seguidor de fonte.                                                          |    |

| Figura 6.5: Amplificador cascode.                                                                    |    |

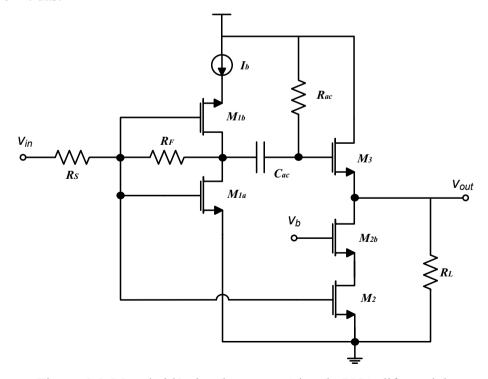

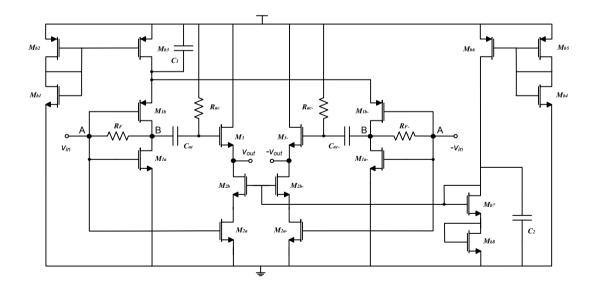

| Figura 6.6: Metade idêntica do esquemático do LNA diferencial.                                       |    |

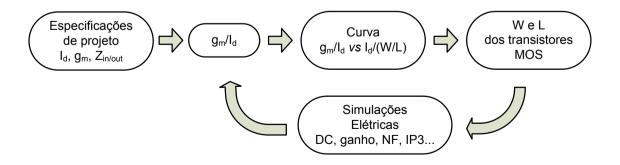

| Figura 6.7: Fluxo de projeto utilizando a metodologia gm/Id.                                         |    |

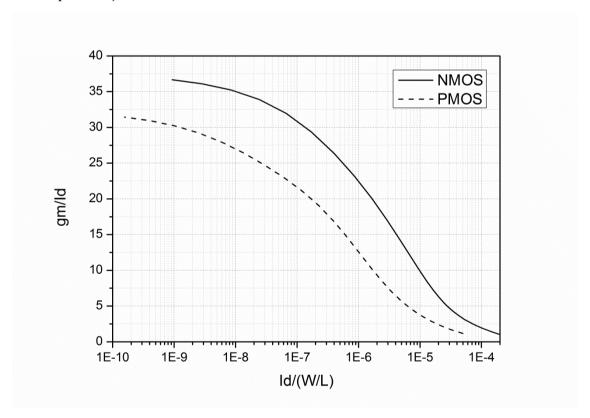

| Figura 6.8: Curva gm/Id simulada dos transistores NMOS e PMOS IBM 130nm                              |    |

| Figura 6.9: Esquemático do LNA banda-larga para frequências de 50MHz-1GHZ                            |    |

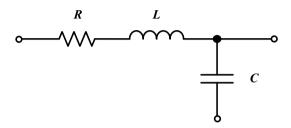

| Figura 6.10: Modelo elétrico básico do wirebond.                                                     |    |

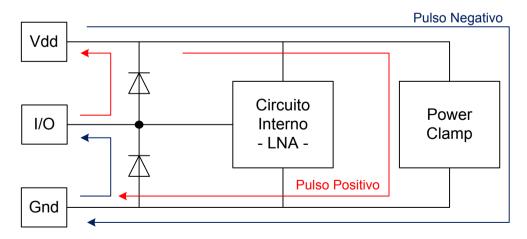

| Figura 6.11: Topologia do circuito de proteção ESD.                                                  |    |

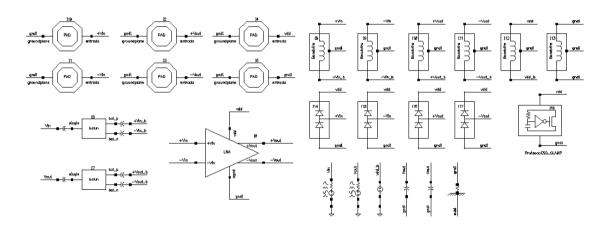

| Figura 6.12: Configuração de testes para simulação.                                                  |    |

| _ , , , , , , , , , , , , , , , , , , ,                                                              |    |

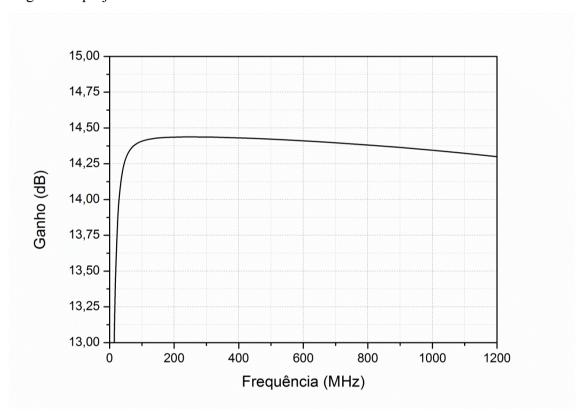

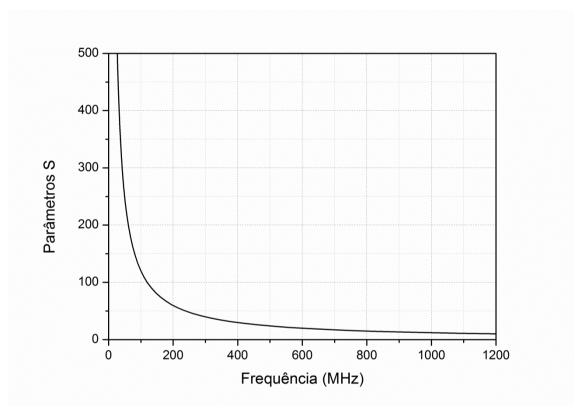

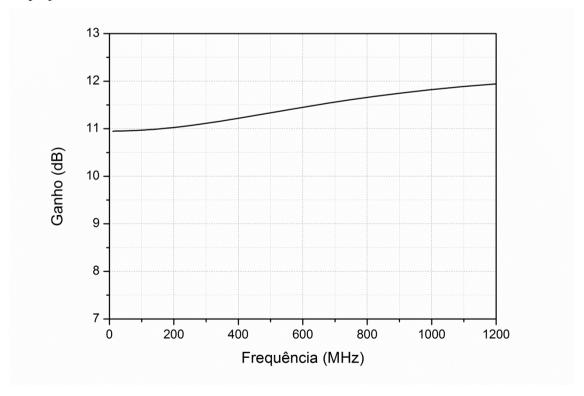

| Figura 6.13: Ganho de tensão do LNA para simulação do esquemático.                       | 69      |

|------------------------------------------------------------------------------------------|---------|

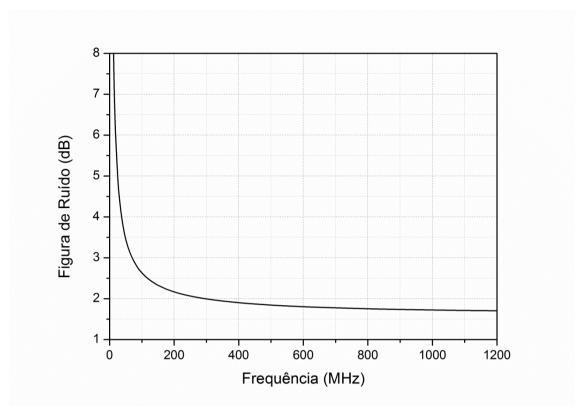

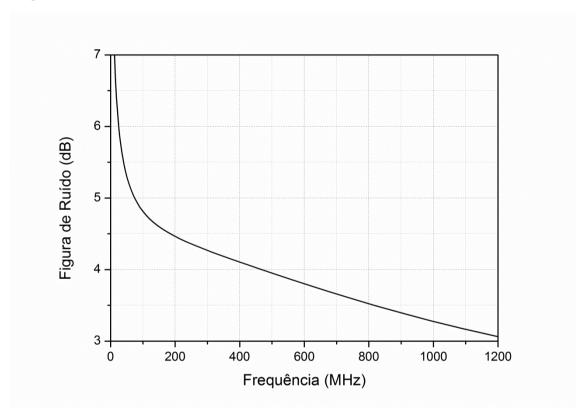

| Figura 6.14: Figura de ruído do LNA para simulação do esquemático.                       |         |

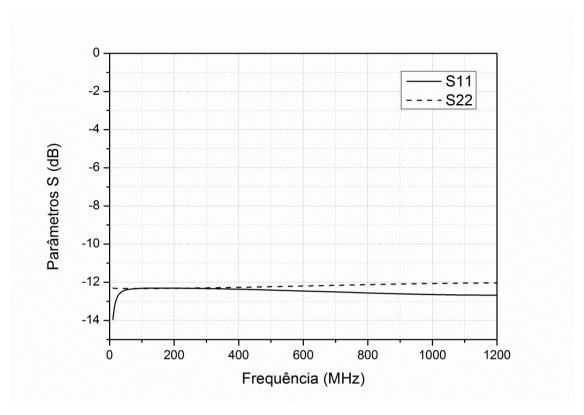

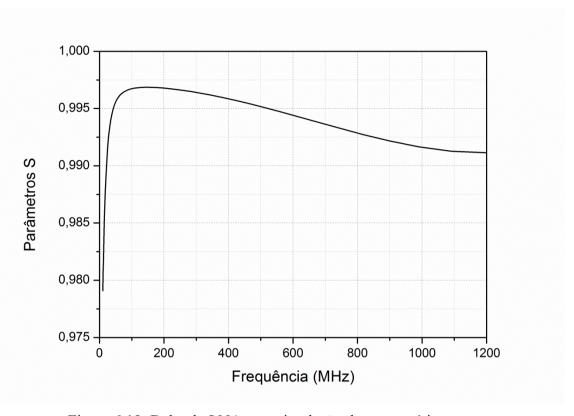

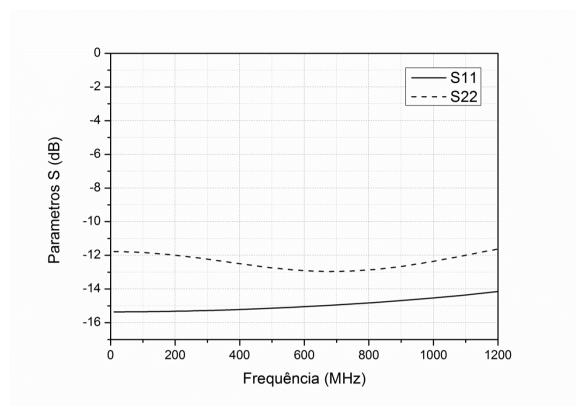

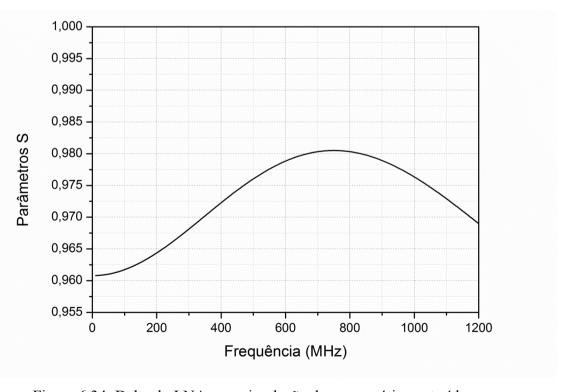

| Figura 6.15: Coeficientes de reflexão do LNA para simulação do esquemático               | 71      |

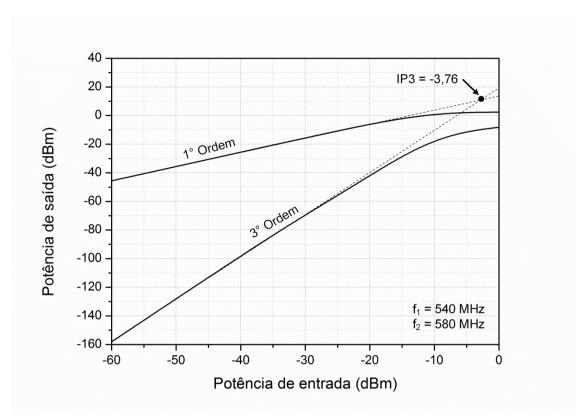

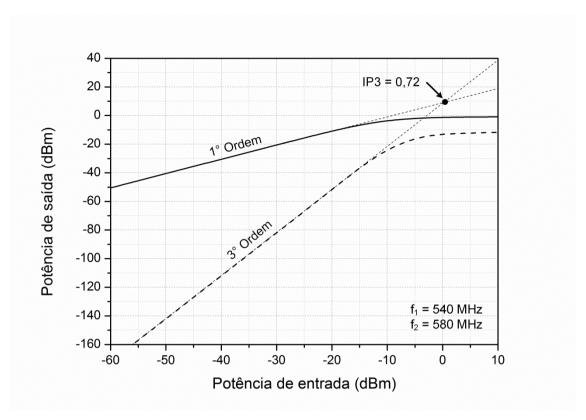

| Figura 6.16: IP3 do LNA para simulação do esquemático.                                   | 72      |

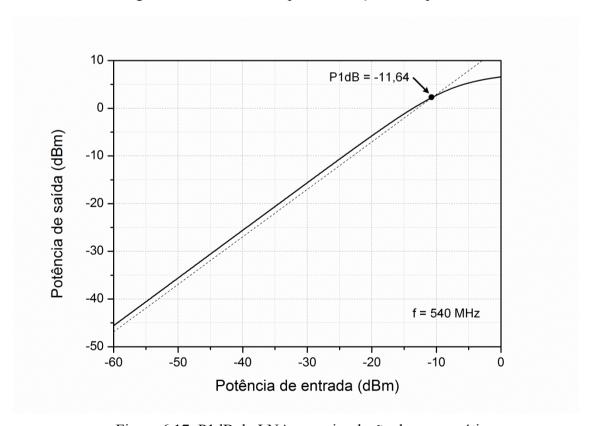

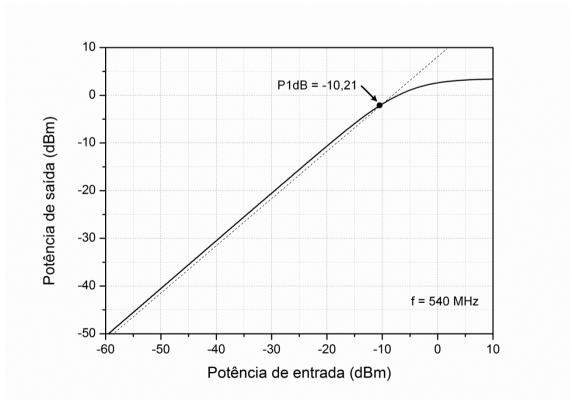

| Figura 6.17: P1dB do LNA para simulação do esquemático                                   | 72      |

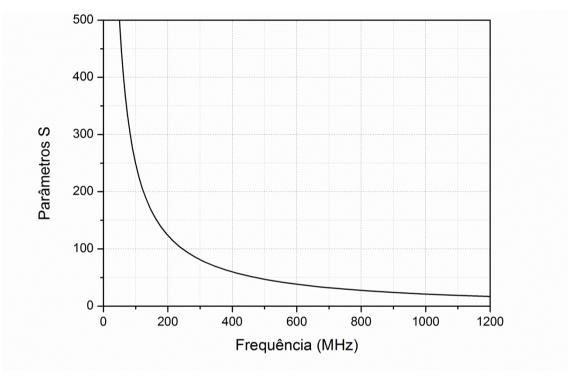

| Figura 6.18: Fator K do LNA para simulação do esquemático.                               | 73      |

| Figura 6.19: Delta do LNA para simulação do esquemático.                                 | 74      |

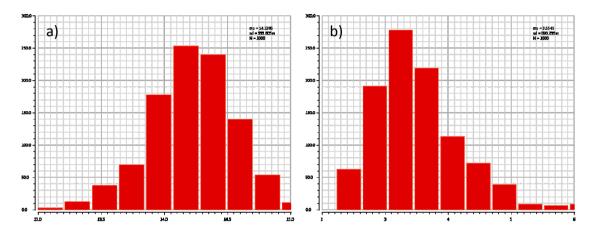

| Figura 6.20: Histograma do ganho (a) e da figura de ruído (b).                           | 76      |

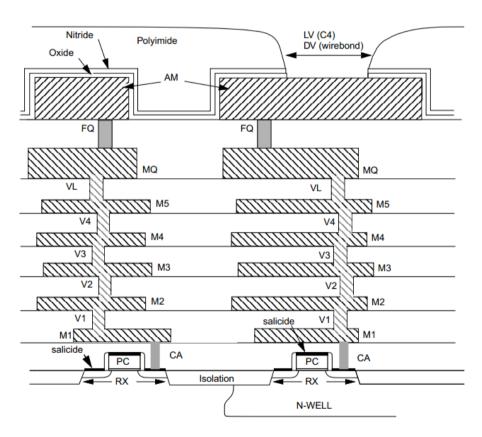

| Figura 6.21: Secção transversal de um modelo de metalização para a tecnologia IBM 8RF-DI | M (IBM, |

| 2010)                                                                                    | 77      |

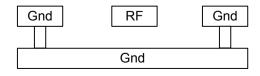

| Figura 6.22: Exemplo da proteção de sinais RF.                                           | 78      |

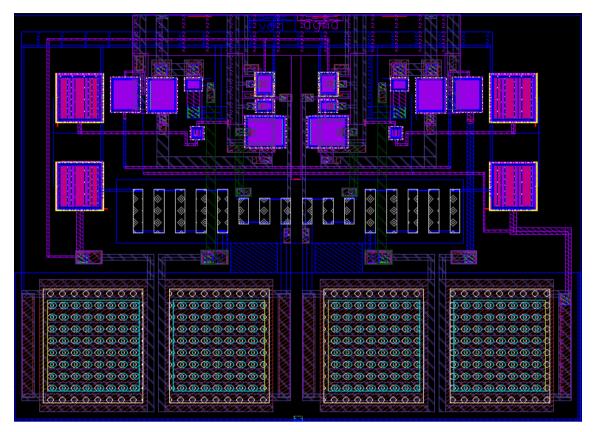

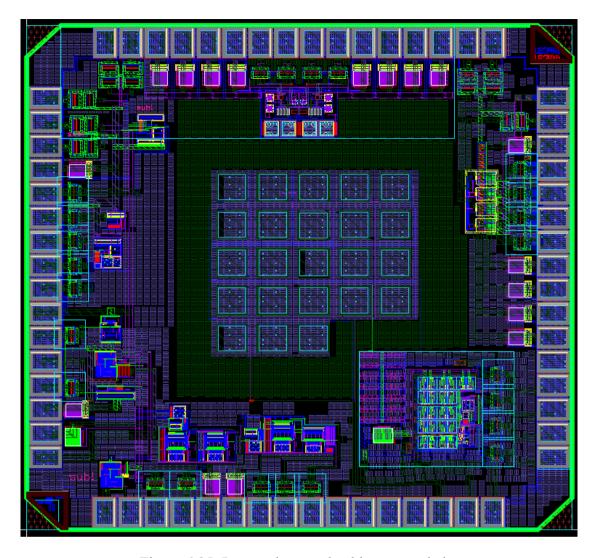

| Figura 6.23: Layout do LNA sem proteção ESD.                                             | 80      |

| Figura 6.24: Layout do LNA com proteção ESD.                                             | 80      |

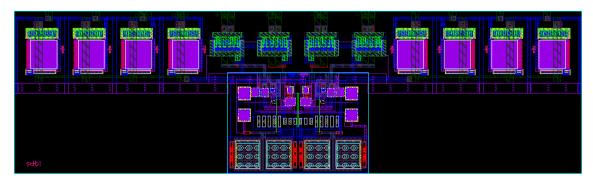

| Figura 6.25: Layout do topo do chip encapsulado                                          | 82      |

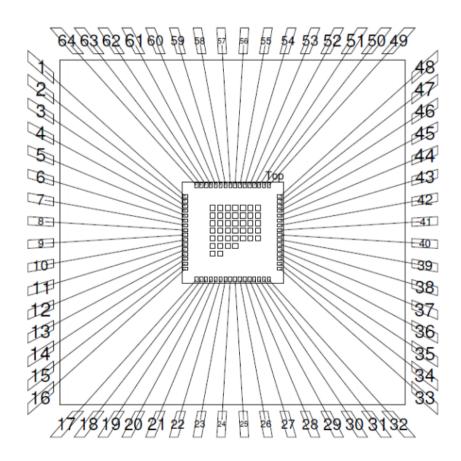

| Figura 6.26: Lista dos pinos do chip encapsulado.                                        | 83      |

| Figura 6.27: Diagrama de bonding do encapsulamento.                                      | 83      |

| Figura 6.28: Ganho de tensão do LNA (S21) obtida por simulação do esquemático extraído   | 84      |

| Figura 6.29: Figura de ruído do LNA para simulação do esquemático extraído.              | 85      |

| Figura 6.30: Coeficientes de reflexão do LNA para simulação do esquemático extraído      | 86      |

| Figura 6.31: IIP3 do LNA para simulação do esquemático extraído                          | 87      |

| Figura 6.32: P1dB do LNA para simulação do esquemático extraído                          | 87      |

| Figura 6.33: Fator K do LNA para simulação do esquemático extraído.                      | 88      |

| Figura 6.34: Delta do LNA para simulação do esquemático extraído.                        | 88      |

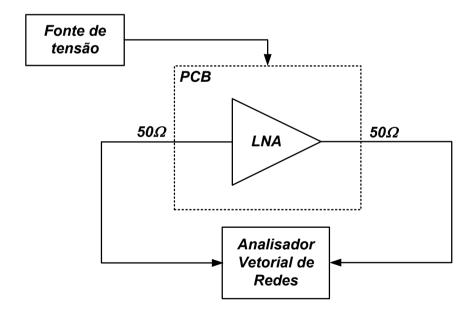

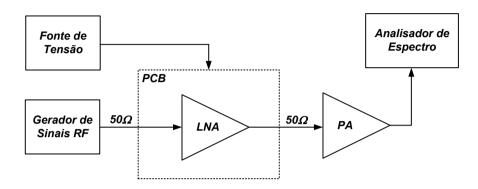

| Figura 6.35: Configuração de teste para parâmetros de espalhamento                       | 91      |

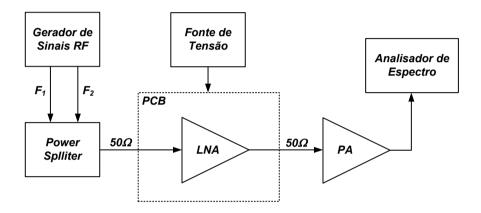

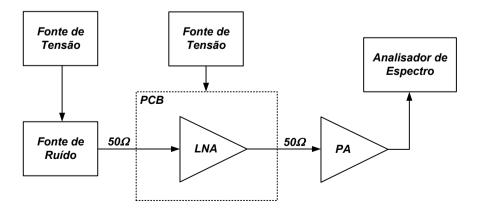

| Figura 6.36: Configuração de teste para IP3.                                             | 92      |

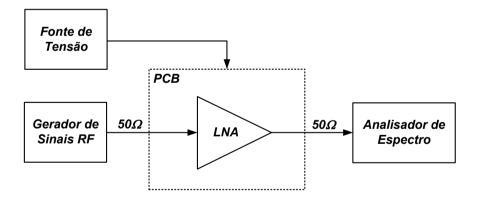

| Figura 6.37: Configuração de teste para P1dB.                                            | 92      |

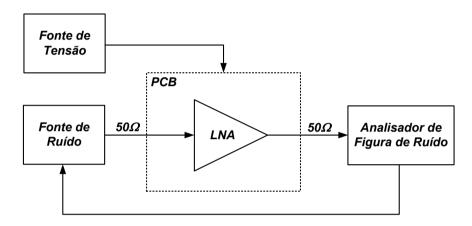

| Figura 6.38: Configuração de teste para NF com analisador de específico                  |         |

| Figura 6.39: Configuração de teste para NF com método fator Y                            | 93      |

| Figura 6.40: Configuração de teste para NF com método do ganho                           |         |

# LISTA DE TABELAS

| Tabela 1: Especificações de LNA's Multibanda presentes na literatura | 48 |

|----------------------------------------------------------------------|----|

| Tabela 2: Especificações do Amplificador de Baixo Ruído              | 57 |

| Tabela 3: Valores calculados e simulados para os transistores MOS    | 64 |

| Tabela 4: Modelos utilizados na simulação                            | 66 |

| Tabela 5: Parâmetros de simulação de corners.                        | 74 |

| Tabela 6: Resultados da simulação de corners do LNA.                 | 75 |

| Tabela 7: Resultados da simulação de Monte Carlo do LNA.             | 75 |

| Tabela 8: Comparação de resultados de artigos sobre LNA banda larga  | 90 |

#### **RESUMO**

O presente trabalho tem por objetivo fornecer o embasamento teórico para o projeto de um amplificador de baixo ruído (LNA – Low Noise Amplifier) em tecnologia CMOS que opere em mais de uma faixa de frequência, de modo a permitir seu uso em receptores multibanda e de banda larga.

A base teórica que este trabalho abrange desde a revisão bibliográfica do assunto em questão, passando pela análise dos modelos de transistores para alta-frequência, pelo estudo das especificações deste bloco e das métricas utilizadas em projetos de circuitos integrados de RF, bem como pela revisão de topologias clássicas existentes.

Com os conhecimentos acima adquiridos, foi possível realizar o projeto de um LNA diferencial de banda larga utilizando tecnologia CMOS IBM 130nm, o qual pode ser aplicado ao padrão IEEE 802.22 para rádios cognitivos (CR). O projeto é baseado na técnica de cancelamento de ruído, sendo validado após apresentar efetiva redução de figura de ruído para banda de frequência desejada, com moderado consumo de potência e utilização moderada de área de silício, devido a solução sem o uso de indutores.

O LNA banda larga opera em frequências de 50Mhz a 1GHz e apresenta uma figura de ruído abaixo de 4dB, em 90% da faixa, um ganho acima de 12dB, e perda de retorno na entrada e na saída maiores que-12dB. O IIP3 e a frequência de ocorrência de compressão a 1dB com a entrada em 580MHz estão acima de 0dBm e -10dBm respectivamente. Possui consumo de 46,5mW para fonte de 1,5V e ocupa uma área ativa de apenas 0,28mm x 0,2mm.

**Palavras-Chave:** LNA, Amplificador de Baixo Ruído, Sistema RF, Projeto de circuitos integrados CMOS, Figura de Ruído.

# A 50MHz-1GHz Wideband Low Noise Amplifier in 130nm CMOS Technology

#### **ABSTRACT**

This work presents the theoretical basis for the design of a low noise amplifier (LNA) in CMOS technology that operates in more than one frequency band, which enables its use in multi-band and wideband receivers.

The theoretical basis that this work will address extends from the literature review on the subject, through the analysis of models of MOS transistors for high frequencies, study of specifications of this block and the metrics used in RF integrated circuit design, as well as the review of existing classical LNA topologies.

Based on the knowledge acquired above, the design of a differential wideband LNA is developed using IBM 130nm RF CMOS process, which can be used in IEEE 802.22 Cognitive Radio (CR) applications. The design is based on the noise-canceling technique, with an indutctorless solution, showing that this technique effectively reduces the noise figure over the desired frequency range with moderate power consumption and a moderate utilization of silicon die area.

The wideband LNA covers the frequency range from 50 MHz to 1 GHz, achieving a noise figure below 4dB in over 90% of the band of interest, a gain of 11dB to 12dB, and an input/output return loss higher than -12 dB. The input IIP3 and input P1dB at 580MHz are above 0dB and -10dB, respectively. It consumes 46.5mW from a 1.5V supply and occupies an active area of only 0.056mm2 (0.28mm x 0.2mm).

# 1 INTRODUÇÃO

Atualmente, dispositivos móveis são amplamente utilizados para uma vasta gama de aplicações, sejam telefones celulares, tablets, assistentes pessoais digitais (PDA's), computadores pessoais, notebooks, console de jogos, televisores, etc. Essa crescente demanda de produtos de aplicação sem fio, exige além de baixo custo, CI's altamente integráveis para transceptores.

Ao acompanhar este crescimento, o número de padrões de comunicação sem fio vem aumentando cada vez mais para suprir estas necessidades tecnológicas, sendo que isto requer transceptores que possam operar em múltiplas bandas de frequência e em variadas aplicações.

Nesse contexto, encontra-se o padrão IEEE 802.22, conhecido como WRAN (*Wireless Regional Area Network*), cujo objetivo é proporcionar, através de rádios cognitivos, uma comunicação de dados através da utilização de canais de frequência ocasionalmente ociosos nas bandas VHF e UHF.

Ainda objeto de estudo, sabe-se que para haver a implantação dos radio cognitivos necessita-se de receptores capazes de trabalhar em mais de uma frequência, seja em frequências separadas (*multi-band*) ou em banda larga (*wideband*). Apesar de o receptor ser tratado como apenas um componente, o mesmo é formado por vários outros blocos, os quais também devem ser capazes de operar nas frequências desejadas, e é neste escopo que este trabalho se enquadra.

Após a antena, o primeiro componente de um receptor de rádio-frequência sem fio é o amplificador de baixo ruído (LNA). Sua principal função é amplificar o sinal para reduzir o ruído de estágios posteriores ao adicionar o mínimo de ruído possível.

Visando a necessidade de maiores estudos sobre LNAs que atendam receptores destinados ao padrão IEEE 802.22, este trabalho teve como objetivo o estudo e a prototipação de um LNA de banda larga, bem como a utilização de uma metodologia alternativa de projeto.

O trabalho apresenta inicialmente o estudo dos conceitos básicos de RF, passando posteriormente pela análise do comportamento dos transistores de tecnologia CMOS em RF. Então é realizada uma revisão na literatura sobre as topologias básicas de LNAs, bem como os mais utilizados em projetos multi-banda e banda larga. Por fim, é apresentado todo o projeto de um LNA banda larga, desde sua especificação até sua prototipação e preparação para medidas experimentais.

# 2 CONCEITOS BÁSICOS DE RF (RADIO FREQUÊNCIA)

A principal função do LNA (Low Noise Amplifier) é proporcionar ganho suficientemente alto para superar o ruído de estágios subsequentes (mixer, etc) de um sistema receptor de RF e adicionar o mínimo de ruído possível. Além disso, ele deve ser linear o suficiente para lidar com fortes interferências, sem introduzir distorção de intermodulação. O intervalo dinâmico de operação do amplificador é, portanto, determinado pelo ruído e não-linearidades do mesmo.

É importante ressaltar que um LNA também deve apresentar uma impedância específica para a fonte de entrada e na carga de saída. E em caso de dispositivos móveis, um parâmetro de projeto importante é o consumo de energia, devido à baixa duração das baterias desses aparelhos. Para correta caracterização e medição, estas e outras métricas de desempenho do LNA são estudadas nesta seção.

Figura 2.1: Diagrama de blocos de um sistema de recepção tipo heteródino em quadratura.

#### 2.1 Linearidade

Um sistema é considerado linear se sua saída pode ser expressada como uma combinação linear (ou superposição) das respostas de entradas distintas (Razavi, RF Microelectronics 1998). Todo sistema que não satisfaz esta condição é considerado não linear. Levando-se em consideração que praticamente nenhum sistema real pode satisfazer esta condição, conclui-se que todo sistema real é não linear.

Baseado nesta afirmação, faz-se necessário o estudo dos principais efeitos não lineares considerados em circuitos analógicos e de RF.

Figura 2.2: Curva de Transferência de Amplificador com dispositivos ativos.

## 2.2 Distorção

Distorção é definida pela alteração de sinais em uma banda desejada por sinais não desejados. Em sistemas não lineares, como dispositivos de RF, se um sinal senoidal é aplicado, geralmente sua saída irá apresentar componentes de frequência que são múltiplos inteiros da frequência de entrada (Razavi, RF Microelectronics 1998). Por exemplo, se a entrada:

$$x(t) = A\cos\omega t$$

(1)

é aplicada a um sistema não linear, a saída y(t) na forma polinomial em  $\cos(\omega t)$  é dada por:

$$y(t) = \alpha_1 A \cos \omega t + \alpha_2 A^2 \cos^2 \omega t + \alpha_3 A^3 \cos^3 \omega t \tag{2}$$

O termo com a frequência de entrada é chamada de fundamental e as de ordem maiores são chamadas de harmônicas.

$$y(t) = \frac{\alpha_2 A^2}{2} + \left(\alpha_1 A + \frac{3\alpha_3 A^3}{4}\right) \cos \omega t + \frac{\alpha_2 A^2}{2} \cos 2\omega t + \frac{\alpha_3 A^3}{4} \cos 3\omega t \tag{3}$$

Fatores de distorção harmônica  $HD_i$  (*Harmonic distortion factors*) fornecem uma medida para a distorção introduzida por cada harmônica para um dado nível de sinal de entrada (utilizando um tom simples para uma dada frequência).  $HD_i$  é definida como a relação dos níveis de sinal de saída da  $i^{th}$  harmônica da fundamental. Assumindo que:

$$\alpha_1 A \gg \frac{3\alpha_3 A^3}{4} \tag{4}$$

A segunda distorção harmônica  $HD_2$ , a terceira distorção harmônica  $HD_3$  e a distorção harmônica total THD são definidas como:

$$HD_2 = \frac{\alpha_2 \cdot A}{2 \cdot \alpha_1} \qquad HD_3 = \frac{\alpha_3 \cdot A^2}{4 \cdot \alpha_1} \tag{5}$$

$$THD = \sqrt{HD_2^2 + HD_3^2 + HD_4^2 + \dots}$$

(6)

Em sistemas totalmente diferenciais, idealmente, harmônicos pares desaparecerão e apenas harmônicos ímpares permanecem. No entanto, em sistemas reais, descasamentos corrompem a simetria produzindo harmônicos finitos de mesma ordem.

## 2.3 Intermodulação

Quando dois sinais com diferentes frequências são aplicados a um sistema não linear, a saída apresenta algumas componentes que não são harmônicas da frequência de entrada. Este fenômeno é chamado de intermodulação, o qual surge da multiplicação de sinais não desejados devido a não linearidades presentes no circuito (Razavi, 1998).

Tradicionalmente, o método mais utilizado para medir a linearidade em função dos produtos de intermodulação é chamado "teste de dois tons". Através da aplicação dois tons de frequências próximas na entrada do sistema não linear, o qual irá apresentar componentes de frequência nas imediações da faixa de passagem desse sistema. Tais componentes são chamadas de produto de intermodulação (IM - intermodulation).

Figura 2.3: Produtos de Intermodulação em um sistema não linear.

Ao aplicar dois tons de frequência na entrada do circuito ( $\omega_1 e \omega_2$ , com  $\omega_2 > \omega_1$ , conforme Figura 2.3), como por exemplo:

$$x(t) = x_1(t) + x_2(t) = A_1 \cos \omega_1 t + A_2 \cos \omega_2 t \tag{7}$$

A saída será:

$$y(t) = \alpha_1 (A_1 \cos \omega_2 t + A_2 \cos \omega_2 t) + \alpha_2 (A_1 \cos \omega_1 t + A_2 \cos \omega_2 t)^2 + \alpha_3 (A_1 \cos \omega_1 t + A_2 \cos \omega_2 t)^3 + \dots$$

(8)

Desprezados os termos de ordem maior que três e a partir de identidades trigonométricas, pode-se encontrar:

As frequências fundamentais:

$$\cos\omega_1 t \left( \alpha_1 A_1 + \frac{3}{4} \alpha_3 A_1^3 + \frac{3}{2} \alpha_3 A_1 A_2^2 \right) \tag{9}$$

$$\cos\omega_2 t \left(\alpha_1 A_2 + \frac{3}{4}\alpha_3 A_2^2 + \frac{3}{2}\alpha_3 A_2 A_1^2\right) \tag{10}$$

• Os termos de segunda ordem:

$$\cos 2\omega_1 t \left(\frac{1}{2}\alpha_2 A_1^2\right); \qquad \cos 2\omega_2 t \left(\frac{1}{2}\alpha_2 A_2^2\right) \tag{11}$$

Um produto de intermodulação de segunda ordem:

$$\alpha_2 A_1 A_2 [\cos(\omega_1 + \omega_2)t + \cos(\omega_1 - \omega_2)t] \tag{12}$$

• Os termos de terceira ordem:

$$\cos 3\omega_1 t \left(\frac{1}{4}\alpha_3 A_1^3\right); \qquad \cos 3\omega_2 t \left(\frac{1}{4}\alpha_3 A_2^2\right) \tag{13}$$

• Produtos de intermodulação de terceira ordem:

$$\frac{3}{4}\alpha_3 A_1^2 A_2 [\cos(2\omega_1 + \omega_2)t + \cos(2\omega_1 - \omega_2)t]$$

(14)

$$\frac{3}{4}\alpha_3 A_1 A_2^2 [\cos(2\omega_2 + \omega_1)t + \cos(2\omega_2 - \omega_1)t]$$

(15)

Através destas equações, pode-se observar que os produtos de intermodulação de 3° ordem (IM3)  $2\omega_2 - \omega_1$  e  $2\omega_1 - \omega_2$  estão situados próximos a  $\omega_1$  e  $\omega_2$ , tornando-se mais próximo quando a diferença entre  $\omega_1$  e  $\omega_2$  for menor.

O efeito dos produtos de intermodulação de 3° ordem, além de muito comum, também é muito crítico em sistemas de RF, de modo que uma métrica de desempenho foi definida para caracterizar esse comportamento, conhecido como ponto de interceptação de terceira ordem (IP3 - *Third-order intercept point*). O IP3 é definido como o ponto em que a potência do sinal de entrada gera um produto de intermodulação de terceira ordem com a mesma potência da componente fundamental, como mostrado na Figura 2.4.

Analisando as equações dos produtos de intermodulação de terceira ordem, eq. (14) e eq. (15), observa-se que as amplitudes destes sinais são proporcionais ao cubo da amplitude do sinal de entrada, ou seja, os termos aumentam três vezes mais rápido que o termo fundamental. A Figura 2.4 apresenta uma analise dos sinais de entrada e saída através de um gráfico logarítmico de Entrada (dBm) versus a Saída (dBm), onde pode

ser visto que ao variar a amplitude do sinal de entrada, haverá diferentes inclinações para a fundamental e para o produto de intermodulação de terceira ordem.

Figura 2.4: Métricas utilizadas em projetos de RF (Navas, 2005).

No teste de dois tons, o ponto de interceptação de terceira ordem de entrada (IIP3) pode ser interpretado como a metade da diferença entre as magnitudes da fundamental e dos produtos de IM3 na saída, mais o nível de entrada correspondente. Esta aproximação fornece uma estimativa de IIP3, cujo valor deve ser obtido através da interseção extrapolada das duas curvas apresentadas na Figura 2.4, contudo, esta interseção não ocorre na prática devido ao efeito compressor dos circuitos.

# 2.4 Ponto de compressão de 1 dB

O ponto de compressão de 1dB (P1dB - *Compression Point*) é definido como o nível de entrada que causa uma redução de 1dB na potência de saída da fundamental em relação ao ganho linear. Sabe-se que o ganho de um sistema linear é constante para qualquer amplitude de entrada, mas o ganho de um sistema real não tem um valor constante e varia segundo a amplitude do sinal de entrada aplicado.

Logo, analisando-se a equação na Figura 2.5, observa-se que, se A for suficientemente pequeno, o valor referente a  $\alpha_3$  pode ser desprezado, porém se A aumentar, o valor referente a  $\alpha_3$  se tornará importante, pois esta é proporcional a  $A_3$ . Logo, o ganho diminui com o aumento da amplitude de sinal na entrada do sistema, caracterizando o ponto de compressão de 1 dB.

Figura 2.5: Ponto de compressão de 1 dB.

O P1dB é um parâmetro que mostra o limite de distorção aceito por um sistema. Para encontrá-lo basta extrapolar a curva fundamental e observar o ponto em que a diferença entre a curva real e a extrapolada for igual a 1dB.

$$V_{1\text{dB}} = \sqrt{0.145 \left| \frac{\alpha_1}{\alpha_3} \right|} \qquad V_{IP3} = \sqrt{\frac{4}{3} \left| \frac{\alpha_1}{\alpha_3} \right|}$$

(16)

$$\frac{V_{IP3}}{V_{1dB}} = \frac{\sqrt{\frac{4}{3} \left| \frac{\alpha_1}{\alpha_3} \right|}}{\sqrt{0.145 \left| \frac{\alpha_1}{\alpha_3} \right|}} = \sqrt{\frac{4}{3 \times 0.145}} = 3.03$$

(17)

$$IP_3 = P_{1dB} + 9.6dB \tag{18}$$

### 2.5 Estágios não lineares em cascata

Em sistemas de RF, sinais são processados através de estágios em cascata, logo, é importante ter conhecimento de como a não linearidade de cada estágio contribui para todo o sistema. Particularmente, é conveniente calcular todos os IIP3 em termos de IP3 e ganho dos estágios individuais.

Figura 2.6: Estágios não lineares em cascata.

Na Figura 2.6, considera-se n estágios não lineares em cascata, sendo o IIP3 global dado por  $A_{IIP3}$  como:

$$\frac{1}{A_{IIP3}^2} = \frac{1}{A_{IIP3,1}^2} + \frac{G1^2}{A_{IIP3,2}^2} + \frac{G1^2 \cdot G2^2}{A_{IIP3,3}^2} + \dots$$

(19)

onde  $A_{IIP3,n}$  e  $G_n$  são IIP3 e ganho do estágio n, respectivamente

#### 2.6 Ruído

O ruído pode ser definido como qualquer interferência aleatória não relacionada com o sinal de interesse. As principais fontes de ruído em circuitos são: o ruído térmico, o qual é gerado por resistores e transistores, o ruído flicker (também conhecido como ruído 1/f), possui origem devido à contaminação e defeitos do cristal, logo, pode ser encontrado em todos os dispositivos ativos, e por último, o ruído shot, o qual está associado às flutuações no número de elétrons remetidos por uma fonte (Razavi, 1998).

Não faz parte do escopo deste trabalho um estudo detalhado especificamente sobre ruído, mas sim o conhecimento das fontes de ruído (Seção 3.4), das técnicas de projeto de circuitos integrados e de medidas das mesmas fontes. A seguir são apresentadas as principais métricas de desempenho utilizadas para caracterizar o comportamento do ruído em sistemas analógicos e de RF.

#### 2.6.1 Ruído referenciado à entrada

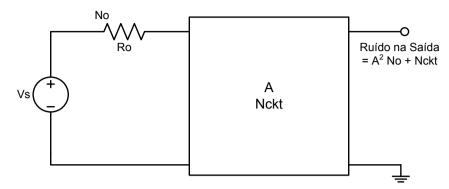

Considerando o circuito real da Figura 2.7, no qual uma fonte ideal é conectada a um amplificador de resistência  $R_o$ , para o qual  $N_{out} = A^2 \cdot N_o + N_{ckt}$  é a densidade

de ruído na saída, No é o ruído da resistência de entrada,  $N_{ckt}$  é a densidade de ruído gerado pelo circuito e A é ganho do circuito amplificador.

Figura 2.7: Performance do ruído em um circuito real.

Logo, o ruído referenciado à entrada é definido como:

$$N_{inp,ref} = \frac{N_{out}}{A^2} = N_o + \frac{N_{ckt}}{A^2} \tag{20}$$

#### 2.6.2 Figura de ruído

Figura de ruído (NF - *Noise Figure*) e Fator de ruído, ambos são utilizados como métricas de desempenho em projetos de circuitos integrados em RF, sendo que a primeira corresponde a segunda expressa em dB. Quando um sinal elétrico passa por um determinado circuito real, sempre haverá a degradação da relação sinal ruído (SNR), e a forma mais utilizada para mensurar esta degradação é a medida da figura de ruído, a qual determina a sensibilidade de um sistema de RF, onde F é o fator.

$$NF = 10 \cdot \log F \tag{21}$$

Através de análises prévias, o fator ruído, que mede todo ruído produzido por um dispositivo RF relacionado com ruído térmico na entrada, pode ser definido como:

$$F = \frac{N_{out}}{N_{in.}} = \frac{N_{out}}{A^2 \cdot N_o} = \frac{A^2 \cdot N_o + N_{ckt}}{A^2 \cdot N_o} = 1 + \frac{N_{ckt}}{A^2 \cdot N_o}$$

(22)

A figura de ruído de um circuito pode ser definida como a relação sinal-ruído (SNR) na porta de entrada dividida pela SNR na porta de saída.

$$F = \frac{SNR_{entrada}}{SNR_{saida}} \tag{23}$$

onde:

F – Fator Ruído;

SNR<sub>entrada</sub> - Relação sinal ruído de entrada;

*SNR*<sub>saída</sub> – Relação sinal ruído de saída.

#### 2.6.3 Figura de Ruído de estágios em cascata

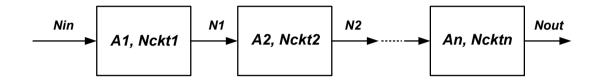

Para estágios em cascata, a figura de ruído total pode ser obtida em termos de figura de ruído e ganhos de cada estágio.

Considerando que *n* figuras de ruído em cascata são apresentados na Figura 2.8, onde *Nin*, *N1*,... *Nout* são os ruídos na entrada, no estágio de saída 1, e na saída, respectivamente.

Figura 2.8: Estágios de ruído em cascata.

Assim, através da eq. (19), o ruído referenciado à entrada devido a N1, N2,...Nn, torna-se:

$$N_{inp,ref} = \frac{N_{out}}{A_1^2 \cdot A_2^2 \dots A_n^2} \tag{24}$$

Logo, através da eq. (20), o fator ruído total pode ser expressa como:

$$F_{total} = F_1 + \frac{F_2 - 1}{A_1^2} + \frac{F_3 - 1}{A_1^2 \cdot A_2^2} + \dots + \frac{F_n - 1}{A_1^2 \cdot A_2^2 \dots A_n^2}$$

(25)

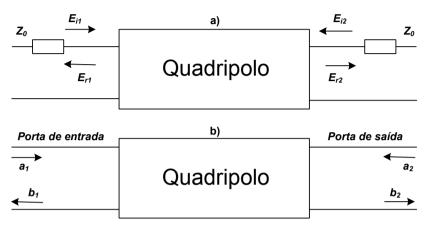

# 2.7 Parâmetros de espalhamento

Em sistemas de RF, parâmetros de espalhamento (ou parâmetros-S) desempenham um importante papel importante devido ao fato de que, para altas frequências, as medidas em circuito aberto e em curto-circuito não são mais aplicáveis, e o modelo de rede para ondas eletromagnéticas se aplica. Em altas frequências, um circuito com saída em curto ( $R_{load} = 0$ ) não se comporta como deveria devido à indutância dos fíos. O mesmo acontece com circuitos abertos, onde se tem um comportamento capacitivo da carga.

Logo, parâmetros-H e parâmetros-Z são difíceis de ser utilizados. Além disso, o objetivo em questão é mensurar a potência incidente e refletida na onda de uma rede de duas portas para blocos de RF, sendo que os parâmetros-S são a melhor maneira de descrever estes parâmetros de redes de duas portas.

#### 2.7.1 Definição de parâmetros-S

Os parâmetros-S (SP) são utilizados para definir a relação de entrada e saída de uma rede em forma de coeficientes de reflexão e transmissão, utiliza-se o fato de que uma linha de transmissão terminada em sua impedância característica (Zo) não tem reflexões e define as variáveis de entrada e saída em termos de ondas de tensão incidente e refletida/espalhada (Lee, 2004).

Figura 2.9: (a) Definição dos SP e (b) ondas incidente e refletida em um quadripolo.

O quadripolo apresentado na Figura 2.9 pode ser descrito como:

$$\begin{bmatrix} b_1 \\ b_2 \end{bmatrix} = \begin{bmatrix} S_{11}S_{12} \\ S_{21}S_{22} \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \end{bmatrix}$$

(26)

Onde:

S<sub>11</sub> - coeficiente de reflexão de entrada;

S<sub>21</sub> - ganho direto;

S<sub>22</sub> - coeficiente de reflexão de saída;

S<sub>12</sub> - ganho reverso.

a<sub>n</sub> - potência da onda de entrada

b<sub>n</sub> - potência da onda de saída

Os valores normalizados são dados por:

$$a_1 = \frac{E_{i_1}}{\sqrt{Z_o}}$$

$a_2 = \frac{E_{i_2}}{\sqrt{Z_o}}$   $a_1 = \frac{E_{i_1}}{\sqrt{Z_o}}$   $b_2 = \frac{E_{r_2}}{\sqrt{Z_o}}$  (27)

Onde Ei e Er são as potências da onda incidente e refletida, respectivamente. A normalização em relação à  $\sqrt{Z_o}$  permite considerar a magnitude dos parâmetros  $a_n$  e  $b_n$  iguais à potência da onda incidente ou refletida.

Para obter os parâmetros  $S_{21}$  e  $S_{11}$ , deve-se aplicar o sinal na entrada do circuito com a saída terminada em Zo, logo, tem-se que  $a_1 = 0$ , e tendo em vista que,  $E_{r2} = 0$ , temos:

$$S_{11} = \frac{b_1}{a_1} = \frac{E_{r1}}{E_{i1}} = \Gamma_1$$

$S_{21} = \frac{b_2}{a_1} = \frac{E_{r2}}{E_{i1}}$  (28)

Onde  $S_{11}$  e  $\Gamma_1$  representam o coeficiente de reflexão do sinal na entrada,  $S_{21}$  representa o ganho direto, pois relaciona a onda de saída em relação à onda de entrada.

Para obter  $S_{12}$  e  $S_{22}$  deve-se aplicar o sinal na saída do circuito com a entrada terminada em Zo, onde temos que:

$$S_{22} = \frac{b_2}{a_2} = \frac{E_{r2}}{E_{i2}} = \Gamma_2$$

$S_{12} = \frac{b_1}{a_2} = \frac{E_{r1}}{E_{i2}}$  (29)

Onde  $S_{22}$  e  $\Gamma_2$  representam o coeficiente de reflexão do sinal na saída,  $S_{12}$  representa o ganho reverso.

Através do ganho direto  $(S_{21})$  é possível obter outra métrica bastante utilizada em amplificadores, o ganho de transdução  $(G_T)$ , que por definição é a razão entre a potência efetivamente entregue à carga e a potência disponível do gerador.

$$G_T = \frac{potência\ entrgue\ na\ carga}{potência\ entrgue\ pela\ fonte} = |S_{21}|^2 \tag{30}$$

#### 2.8 Estabilidade

Estabilidade é uma característica fundamental para o projeto de um amplificador, o qual não deve apresentar nenhuma condição na qual ele possa entrar em oscilação. Oscilações são possíveis quando a entrada ou a saída apresentarem uma resistência negativa (Vizmuller, 1995). Um casamento simultâneo das portas de entrada e saída de um amplificador incondicionalmente estável irá entregar a máxima potência.

Há na literatura diversos fatores que determinam a estabilidade de um circuito, no entanto, não faz parte do escopo deste trabalho um estudo detalhado especificamente sobre esses fatores, mas sim o conhecimento de sua existência e as principais formas de mensurá-los.

A principal forma de verificar a estabilidade é pela determinação do Fator K, o qual é uma medida da estabilidade do amplificador, que deriva das condições de estabilidade básica das potências refletidas de entrada e saída, e que devem ser sempre menores que a potência incidente. Para  $\Delta = S_{11}S_{22} - S_{12}S_{21}$ , o Fator K dado por (Vizmuller, 1995) é:

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |S_{11}S_{22} - S_{12}S_{21}|^2}{2 |S_{12}S_{21}|^2}$$

(31)

Um circuito é incondicionalmente estável para um K > 1 e  $\Delta < 1$ .

#### 2.9 Sensibilidade e Faixa Dinâmica

Define-se a sensibilidade de um receptor como a mínima magnitude de sinal que o sistema consegue detectar com uma aceitável relação sinal-ruído (Razavi, 1998). Abaixo segue o cálculo da sensibilidade.

$$NF = \frac{SNR_{in.}}{SNR_{out}} = \frac{P_{sig}/P_{Rs}}{SNR_{out}} \tag{32}$$

$$P_{sig} = P_{Rs} \cdot NF \cdot SNR_{out} \tag{33}$$

Onde:

$P_{sig}$ - Potência do sinal na entrada;

$P_{Rs}$ - Potência do ruído gerado pela resistência da fonte do sinal.

Pode-se observar que a equação acima prediz a sensibilidade como a potência mínima de sinal de entrada que é necessária para atingir um certo valor para a relação sinal-ruído na saída. Levando-se em consideração que a potência do sinal está distribuída ao longo da banda do canal de comunicação, a potência média pode ser obtida utilizando  $P_{sig} = P_{in,min}$  e  $SNR_{out} = SNR_{min}$  expressas em dB (ou dBm) através da seguinte expressão:

$$P_{in,min} \mid_{dBm} = P_{RS} \mid_{dBm/Hz} + SNR_{min} \mid_{dB} + 10 \log B$$

(34)

Onde:

$P_{in,min}$  - Potência mínima de sinal na entrada necessária para atingir o SNR mínimo; B - Banda em Hz.

Em um sistema com um casamento de impedâncias na entrada,  $P_{Rs}$  pode ser definido como a potência de ruído que a resistência característica da fonte de sinal transfere à impedância de entrada do circuito considerando a banda igual a 1Hz. Logo:

$$P_{RS} = \frac{4KTR_S}{4} \frac{1}{R_{in.}} = KT = -174dBm/Hz$$

(35)

para temperatura ambiente:

$$P_{in,min} = -174dBm/Hz + NF + 10\log B + SNR_{min}$$

(36)

Nota-se que a soma dos três primeiros termos da equação acima é o ruído total do sistema, o qual algumas vezes, é chamado de ruído de fundo (*noise floor*).

Com relação à Faixa Dinâmica (DR - *Dynamic Range*), esta geralmente é definida na literatura como a razão entre a máxima magnitude de sinal de entrada que o circuito consegue tolerar e a mínima magnitude de entrada que o circuito pode detectar, mantendo uma razoável qualidade do sinal na saída (Razavi, 1998). Em sistemas de RF, a magnitude máxima geralmente é determinada através do comportamento dos produtos de intermodulação, e a magnitude mínima é determinada através da sensibilidade. Tal definição é conhecida como faixa dinâmica livre de espúrios (SFDR - *Spurious-free dynamic range*).

Em um teste de dois tons, o limite máximo da faixa dinâmica pode ser definido como a máxima magnitude aplicada à entrada do circuito, na qual os produtos de intermodulação se mantenham abaixo do ruído de fundo. Através da Figura 2.4, sabe-se que:

$$\Delta P = P_{out} - P_{IM,out} \tag{37}$$

considerando que

$$P_{out} - P_{in.} + G = P_{IM.,out} = P_{IM.,in.} + G$$

(38)

onde:

G - Ganho de tensão do circuito;

$P_{IM..in.}$  - Potência dos produtos de intermodulação relacionados à entrada.

Tem-se que:

$$P_{in.} = \frac{2P_{IIP3} + P_{IM.,in.}}{3}$$

(39)

O nível de entrada para que os produtos de intermodulação sejam iguais ao ruído de fundo é dada por:

$$P_{in,max} = \frac{2P_{IIP3} + F}{3} \tag{40}$$

onde

$$F = -174dBm + NF + 10\log B \tag{41}$$

logo, por definição, temos que:

$$SFDR = \frac{2(P_{IIP3} - F)}{3} - SNR_{min} \tag{42}$$

### 3 TRANSISTORES MOS EM RF

Os avanços na fabricação CMOS resultaram em transistores com maiores frequências de transmissão e menores valores de figura de ruído. Projetistas de RF já exploram a tecnologia CMOS em circuitos de RF, cujo avanço no desempenho dos MOSFETs tornou atraente para alta frequência (HF – *High Frequency*) o projeto de circuito no sentido de uma realização SoC (*System-on-a-chip*), onde blocos digitais, de sinal misto de banda base e blocos transceptores em HF seriam integrados em um único chip. Para se ter um ambiente de projeto eficiente, ferramentas CAD com modelos precisos para dispositivos ativos e parasitas são essenciais. Sabe-se que para aplicações analógicas e de RF, a precisão das simulações do circuito é fortemente determinada por estes modelos do dispositivo, tornando-se crucial para predizer o desempenho do circuito.

Na maioria dos simuladores de circuitos disponíveis no mercado, os modelos de transistores MOS tem sido originalmente desenvolvido para projetos de circuitos analógicos de baixa frequência e circuitos CMOS digitais, cujos elementos parasitas podem ser desprezados. No entanto, com o aumento da frequência de operação dentro da faixa gigahertz, a importância dos componentes extrínsecos (que consideram todos os parasitas) torna-se tão importante quanto os intrínsecos (núcleo do dispositivo sem parasitas). Portanto, um modelo de RF com a consideração do comportamento em HF de ambos os tipos de componentes (intrínsecos e extrínsecos) em MOSFETs é extremamente importante para a obtenção de resultados precisos e preditivos na simulação de um circuito projetado.

Até recentemente, os modelos de MOSFET mais compactos não incluíam a resistência de porta (*Rg*). No entanto, o ruído térmico adicionado pela resistência deve ser considerado como transistores MOS próximos a frequências gigahertz, e efeitos resistivos e capacitivos (RC) na porta devem ser bem modelados, uma vez que ambos efeitos são importantes no projeto de circuitos CMOS em RF.

A resistência de porta também irá afetar significativamente a admitância de entrada em RF, logo, um modelo sem Rg não pode prever com precisão as características de um dispositivo em HF, impossibilitando, por exemplo, a utilização desta resistência para o casamento de impedância com o objetivo de se conseguir a máxima transferência de potência. Além disso, o ruído térmico introduzido por Rg aumenta a figura de ruído do transistor e reduz a Fmax (frequência que o ganho de tensão máximo disponível do dispositivo é igual a 1), o qual é um importante parâmetro no projeto de circuitos de Radio Frequência, juntamente com a frequência de transição Ft; a frequência na qual o ganho de corrente do dispositivo é igual a 1.

Outro componente importante que quase todos os modelos compactos implementados em simuladores de circuitos comerciais não levam em conta é a resistência do substrato. Na verdade, os efeitos do acoplamento de substrato através das junções de fonte e dreno e essas componentes de resistência de substrato desempenham um papel importante na contribuição para a admitância de saída, logo, a inclusão dessas componentes de substrato em um modelo RF se faz necessário. Um modelo MOSFET sem os componentes de resistência do substrato não possibilita prever a dependência ou o comportamento em frequência da admitância de saída do dispositivo, portanto, a

simulação com esse modelo irá apresentar resultados de simulação não confiáveis da admitância de saída quando a frequência de operação do dispositivo estiver em um intervalo acima de 1 gigahertz.

# 3.1 Efeitos Não Quase Estáticos (NQS - Non-Quasi-Static models)

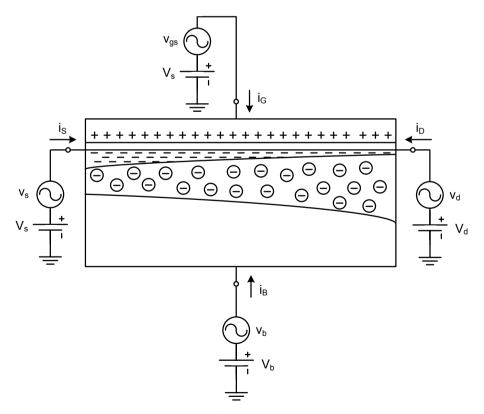

Sabe-se que em altas frequências o modelo quase estático (quasi-static model) do transistor MOS não pode ser utilizado, pois o mesmo não considera o tempo de resposta para a formação ou alteração do canal do transistor após a aplicação de uma polarização. Porém, antes de utilizar o modelo não quase estático (NQS), deve-se conhecer quais as causas e efeitos são considerados em sua formulação.

Para os componentes intrínsecos dos transistores, em geral, assume-se que cada terminal consiste de uma fonte DC e uma componente senoidal, como na Figura 3.1. Pode se supor, inicialmente que apenas uma tensão de pequeno sinal é diferente de zero no tempo. Se *Vs* está variando lentamente, a carga da camada de inversão tem tempo para seguir sem praticamente nenhum atraso, onde tal efeito pode ser modelado conectando um capacitor *Cgs* entre a fonte e a porta do transistor. No entanto, se a variação de *Vs* é muito rápida, a inércia da camada de inversão deixa de ser insignificante, e o efeito (mudança na carga da porta) virá após a causa (mudança na tensão da fonte). Um efeito similar será observado entre o dreno e a porta, bem como entre a fonte e o dreno no substrato.

Figura 3.1: Transistor intrínseco com fontes de polarização DC e fontes de tensão de pequenos sinais (Tsividis, 1999).

Considerando agora uma tensão na porta, se Vg está variando muito rápido, a carga na camada de inversão não tem tempo o suficiente para responder, logo a admitância  $Y_{dg}$ , que modela esta resposta, será pequena. Além disso, o ângulo desta admitância deve ser significante e negativa, por causa do atraso entre a causa (a variação na tensão da porta) e o efeito (a variação na corrente de dreno). E finalmente, observações similares podem ser consideradas para efeitos da tensão de substrato na carga da camada de inversão.

Todos esses efeitos serão observados se a frequência de operação exceder o limite de operação do modelo quase estático. Este limite é proporcional a  $W_0$ , o qual se torna proporcional a  $1/L^2$  na ausência da velocidade de saturação. Um modo de modelar a velocidade de saturação em frequências acima do limite é (a principio) dividir o transistor em seções ao longo do canal, cujo comprimento de cada uma é escolhido de forma que, para ele, o modelo quase estático possa ser usado. A combinação dos modelos de todas as seções será então o modelo válido para todo transistor na frequência de interesse. Como afirmado por (Tsividis, 1999), toda a análise matemática feita neste sentido já está bem estabelecida na literatura, logo, não fará parte do escopo deste trabalho.

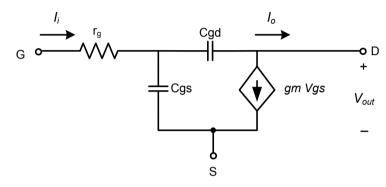

#### 3.2 Modelamento em RF

Normalmente, o modelamento de MOSFETs em RF remete-se a frequências acima da frequência de transição (*cutoff*) do dispositivo. Para essas aplicações, o modelo NQS de pequenos sinais torna-se indispensável para a parte intrínseca. No entanto, a parte extrínseca não deve ser esquecida. Efeitos distribuídos podem ser modelados usando aproximações.

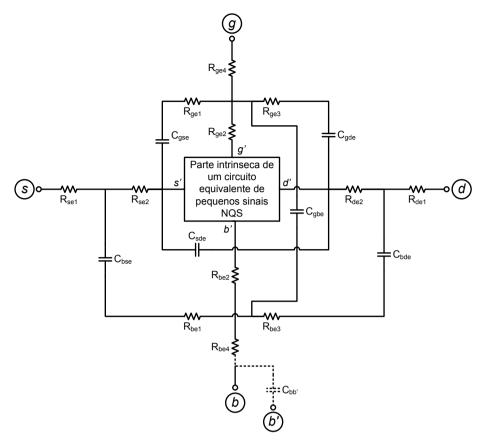

Usualmente, em dispositivos de canal curto e longo que apresentam efeitos não quase estáticos, o modelo NQS é utilizado para a parte intrínseca, cujas resistências são aquelas das regiões de dreno, fonte, porta e substrato, como por exemplo, na Figura 3.2, onde pode ser observado que, cada resistência é dividida em subresistências conectadas a um nó comum, de modo que, as capacitâncias apropriadas sejam conectadas a este nó.

Figura 3.2: Modelo de pequenos sinais para um transistor completo (Tsividis, 1999).

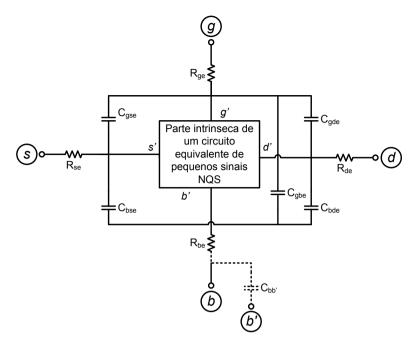

Embora este nível de modelamento seja bastante desejado, na prática é complicado de ser implementado devido a dificuldade de determinar os valores destas subresistências. Isto é particularmente verdade para as subresistências de porta e substrato. Nesses casos, pode-se ter de recorrer ao modelo indicado na Figura 3.3, onde se percebe que algumas vezes, os modelos mais simples são os que devem ser utilizados, seja omitindo alguns efeitos ou até mesmo utilizando um completo modelo quase estático.

Tais modelos altamente simplificados são muito úteis, por exemplo, quando parasitas extrínsecos são dominantes no comportamento do dispositivo, limitando a sua aplicação a frequências mais baixas do que aqueles em que o efeito de componentes intrínsecos faria efeito. Outra utilidade seria com relação a parâmetros de extração, cujos elementos são frequentemente atribuídos qualquer valor que torne o modelo mais próximo das medidas. Estes valores atribuídos não são físicos, porém são utilizados para compensar as insuficiências do modelo, o que pode resultar em predições muito diferentes do real comportamento dos componentes do sistema. Ou seja, o fato de modelos simplificados oferecerem resultados satisfatórios em alguns casos não os torna confiáveis, muito pelo contrário, haverá casos em que estes mesmos modelos serão totalmente falhos para predições de certos fenômenos que são encontrados em modelos completos como o da Figura 3.2.

Figura 3.3: Modelo prático de pequenos sinais para um transistor (Tsividis, 1999).

#### 3.2.1 Resistência de Porta (Rg)

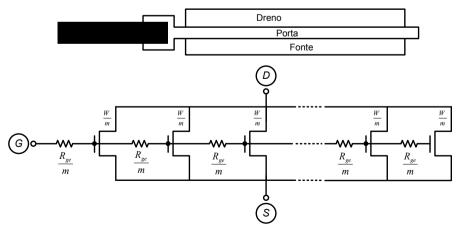

Normalmente em aplicações de RF são utilizados componentes com portas de comprimento longo, gerando valores de largura (W) do canal bastante altos, cujos efeitos da resistência de porta podem ser bem significantes. Através da Figura 3.4b, pode-se observar que a resistência de porta forma uma distribuição de um circuito RC juntamente com a capacitância do canal da porta. Uma forma de entender este efeito é através da divisão do dispositivo em vários subdispositivos, como por exemplo, a Figura 3.4b. Onde Rge representa a resistência de porta total, que na Figura 3.4a é dada por (W/L)  $R_{\square}$ , onde  $R_{\square}$  é a resistência de folha da porta. É claro que a resistência de porta é de pouca importância para os subdispositivos que se encontram à esquerda, mas torna-se cada vez mais importante para os que estão à direita. O sinal da porta dos subdispositivos será significativamente deslocado de fase, devido às resistências e capacitâncias de porta à sua esquerda.

Figura 3.4: (a) Layout de um transistor simples; (b) aproximação de conjuntos (Tsividis, 1999).

Através de equações básicas e considerando m próximo de infinito, (Tsividis, 1999) mostra que o efeito distribuído da resistência de porta pode ser aproximado através de um simples transistor, com a resistência de porta efetiva da eq.( 43 ), cujo valor pode ser usado no lugar de  $R_{ge}$  no modelo de pequenos sinais da Figura 3.4b.

$$R_{ge,eff} = \frac{1}{3} \frac{W}{L} R_{\square} \tag{43}$$

Além de afetar a resposta em frequência, a resistência de porta também irá contribuir com ruído, sendo que para baixas frequências, ele poderá ser modelado utilizando um valor efetivo simples para a resistência de porta, o qual será novamente dado pela equação (43). Dependendo das dimensões da geometria e da resistividade de porta, este ruído pode em alguns casos ser significativamente maior que o produzido pela parte intrínseca do dispositivo. Em altas frequências o ruído da resistência de porta tende a ser filtrado pela capacitância da porta, e o ruído total se aproxima do produzido pela parte intrínseca.

Se a porta está conectada em ambos os lados como na Figura 3.5, o efeito será equivalente a se ter dois dispositivos, cada um com uma porta de *W/2* e a resistência de porta com a metade do valor total em paralelo, sendo que a resistência efetiva será 4 vezes menor, como segue abaixo:

$$R_{ge,eff} = \frac{1}{12} \frac{W}{L} R_{\square} \tag{44}$$

Figura 3.5: Transistor com contato da porta em ambos os lados (Tsividis, 1999).

No projeto de *layouts* de circuitos analógicos/RF, frequentemente utiliza-se vários pequenos transistores funcionando como apenas um. Isto é feito para se obter menor  $R_{ge}$  através das múltiplas portas (*multi-finger*), e também para facilitar o casamento dos transistores com outros dispositivos.

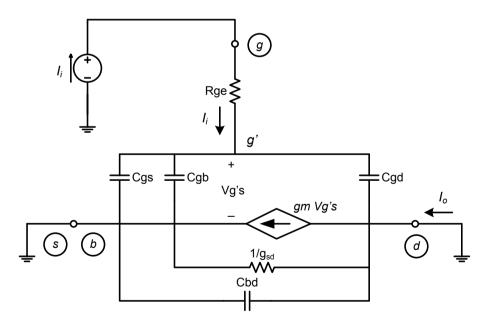

## 3.3 Frequência de Trabalho

Há duas formas amplamente difundidas de se determinar a máxima frequência que um transistor pode operar, a primeira é através da frequência de ganho unitário de corrente  $f_T$  e a segunda é a frequência de ganho unitário de potência  $f_{max}$ . A primeira  $(f_T)$  calcula-se assumindo que o transistor esteja em saturação, que o dreno seja terminado em um curto circuito incremental e que a porta seja alimentada por uma fonte de corrente na entrada. Através da aproximação do modelo na Figura 3.6, desprezando a contribuição de realimentação da corrente de saída e a resistência de porta  $R_g$ , temos que (Lee, 2004):

Figura 3.6: Modelo simplificado do transistor.

$$i_o = -g_m v_{gs} \tag{45}$$

$$v_{gs} \approx \frac{i_i}{j\omega(C_{as} + C_{ad})} \tag{46}$$

$$\left|\frac{\dot{i}_o}{\dot{i}_i}\right| = \frac{g_m}{\omega(C_{as} + C_{ad})}\tag{47}$$

$$\omega = \omega_T \quad quando \quad \left| \frac{\dot{i}_o}{\dot{i}_i} \right| = 1$$

(48)

$$\omega_T = \frac{g_m}{\left(C_{qs} + C_{qd}\right)} \tag{49}$$

$$f_T = \frac{g_m}{2\pi \left(C_{gs} + C_{gd}\right)} \tag{50}$$

Para calcular  $g_m$ , utiliza-se o modelo de primeira ordem e despreza-se  $C_{gd}$ . Pode-se observar que à medida que o comprimento do canal diminui,  $f_T$  aumenta quadraticamente (Tsividis, 1999), e  $f_T$  em 1° ordem pode ser estimado como:

$$f_T = \frac{g_m}{2\pi C_{gs}} = \frac{\mu_n C_{ox}(W/L)(v_{gs} - v_t)}{2\pi (2/3)WLC_{ox}} = \frac{3\mu_n (v_{gs} - v_t)}{4\pi L^2}$$

(51)

Para que haja a máxima transferência de energia, o cálculo da  $f_{max}$  parte da consideração de que deve haver casamento nas terminações do transistor. Logo, as potências na entrada e na carga são dadas por:

$$P_i = \frac{i_i^2 r_g}{2}; \quad P_l = \frac{i_o^2 R_l}{2}$$

(52)

$$r_g = R_{elect} + R_{NQS}; \quad R_{elect} = \frac{R_{\square}W}{kn^2L}$$

(53)

Onde:

$R_g$  - Resistência de porta;

$R_{elect}$  – Resistência do eletrodo de porta;

$R_{NOS}$  – Resistência associada ao efeito não quase estático;

$R_{\square}$  – Resistência de folha do polissilício (ou do filme que compões a porta) por quadrado;

W – Largura do canal;

L – comprimento do canal;

n – número de fingers;

k = 3 ou 12 (dependerá da conexão da porta).

Para calcular a impedância de carga, assume-se que a mesma é igual ao valor da impedância de saída considerando que há casamento de impedância e utilizando uma fonte de teste na saída. Considerando a realimentação da corrente na saída ao se desligar a fonte de corrente de entrada, temos que:

$$R_{l} = \left| \frac{v_{out}}{v_{in}} \right|; \qquad |v_{out}| = \frac{|i_{i}|}{\omega_{T} C_{gd}}$$

(54)

$$R_{l} = \frac{\frac{i_{i}}{C_{gd}}}{\frac{gm i_{i}}{\omega(C_{gs} + C_{gd})}} = \frac{1}{\omega_{T} C_{gd}}$$

(55)

Substituindo as equações, podemos então obter  $f_{max}$ :

$$\frac{P_o}{P_i} = \frac{\left(\frac{\omega_T \, i_i}{2\omega}\right)^2 \cdot \frac{1}{\omega_T \, C_{gd}}}{i_i^2 \, r_g} \tag{56}$$

$$\omega = \omega_{max}$$

quando  $\frac{P_o}{P_i} = 1$  (57)

$$\omega_{max} = \frac{1}{2} \sqrt{\frac{\omega_T}{r_g C_{gd}}} \tag{58}$$

Portanto,

$$f_{max} = \frac{1}{4\pi} \sqrt{\frac{\omega_T}{r_g C_{gd}}}$$

(59)

Na prática, embora a frequência de ganho unitário de corrente seja largamente utilizada, a mesma não inclui os efeitos de vários componentes. Como consequência da terminação curto circuitada e da fonte de corrente,  $f_T$  não considera a capacitância dreno-corpo e a resistência de porta. Para circuitos digitais em baixa frequência, isto pode não ser um problema significativo, porém para circuitos de RF, faz-se necessário utilizar a frequência de ganho unitário de potência ( $f_{max}$ ), a qual faz uso destes dispositivos extrínsecos.

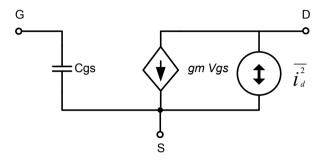

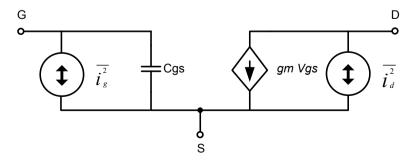

#### 3.4 Fontes de ruído no transistor MOS

Na literatura há diversas publicações que tratam especificamente das fontes de ruído intrínsecas ao transistor MOS em altas frequências, bem como sua influência em blocos de RF como o LNA. Nesta seção serão comentadas as principais fontes de ruído: o ruído shot, o ruído flicker e o ruído térmico, apontado por alguns autores como um fator determinante para se obter bons resultados de figura de ruído (Shaeffer e Lee, 1997).

Basicamente, o ruído térmico é causado pela agitação térmica dos elétrons livres nos semicondutores, esta agitação caracteriza-se como um movimento aleatório traduzido em forma de corrente elétrica. Contudo, as fontes de ruído térmico associadas ao um transistor podem ser divididas em duas classes: intrínsecas e extrínsecas. A primeira classe é composta pelo ruído do canal e pela corrente de ruído induzida na porta. A segunda refere-se ao ruído devido aos componentes resistivos parasitas presentes no transistor, seja no dreno, na fonte, na porta ou no substrato.

#### 3.4.1 Ruído no canal

O ruído térmico gerado pelos portadores no canal também é conhecido como ruído de difusão, por sua origem física. Geralmente este ruído é representado como uma fonte de corrente entre dreno e fonte do transistor (Figura 3.7).

Figura 3.7: Modelo simplificado do transistor MOS em saturação com fonte de ruído no canal.

Na eq. (60) o ruído no canal é representado pelo valor médio quadrático da corrente de ruído.

$$\overline{i_d^2} = 4kT\gamma g_{d0}\Delta f \tag{60}$$

Onde:

k - constante de Boltzmann's.

T - temperatura;

γ - coeficiente de ruído térmico do canal;

$g_{d0}$  - condutância dreno-fonte sem polarização (VDS = 0);

$\Delta f$  - faixa de frequência de medida.

#### 3.4.2 Ruído induzido na porta

Este ruído térmico é induzido pelas flutuações geradas pelo ruído do canal devido seu acoplamento capacitivo do óxido de porta. Observa-se na Figura 3.8 que estes ruídos, de canal e de porta, possuem uma correlação devida sua mesma origem.

Figura 3.8: Modelo do transistor MOS com ruído devido à resistência de porta.

O modelo utilizado é uma fonte de corrente entre a porta e a fonte, a qual pode ser representada pela eq. (61).

$$\overline{i_g^2} = 4kT\delta\gamma g_g|c^2|\Delta f \tag{61}$$

$$g_g = \frac{\omega^2 c_{gs}^2}{5g_{d0}} \tag{62}$$

Onde:

$\delta$  - coeficiente de ruído térmico na porta;

c – fator de correlação (≈ j0,395);

$C_{qs}$  – capacitância porta-fonte;

$C_{gs}$  – capacitância porta-fonte.

#### 3.4.3 Ruído devido aos componentes resistivos parasitas

O ruído causado pelas resistências parasitas pode ser estimado utilizando a equação tradicional de resistências em equilíbrio térmico.

$$\overline{i_{n,R_p}^2} = \frac{4kT}{R_n} \Delta f \tag{63}$$

O modelo utilizado é uma fonte de corrente em paralelo com a resistência parasita  $(R_p)$ , de forma que  $R_p$  pode representar a resistência parasita do dreno, da fonte, da porta ou do substrato.

#### 3.4.4 Ruído Shot

Este ruído é causado pela flutuação de corrente que cruza uma barreira de potencial, ocasionando uma corrente de fuga no canal. A fonte de ruído equivalente é representada pela eq. (64) (Razavi, 2000).

$$\overline{i_{ns}^2} = 2qI_{DC}\Delta f \tag{64}$$

Onde:

$\overline{i_{ns}^2}$  – valor RMS da corrente de ruído;

q – carga do elétron (1,6x10<sup>-19</sup> *Coulombs*);

$I_{DC}$  – corrente DC em *amperes*.

Geralmente a contribuição deste ruído é relativamente pequena, sendo considerada apenas quando a impedância ligada a fonte do transistor possuir um valor elevado.

### 3.4.5 Ruído Flicker ou 1/f

Este ruído é originado principalmente por contaminação e imperfeições do óxido, as quais causadas por portadores aleatórios no canal. Como sua variação é inversamente proporcional à frequência, este ruído também é conhecido como ruído 1/f. Sua representação é dada pela eq. (65) (Lee, 2004).

$$\overline{i_n^2} = \frac{k}{f} \frac{g_m^2}{WLC_{ox}^2} \Delta f \tag{65}$$

Onde:

k – constante dependente do processo;

$C_{ox}$  – capacitância do óxido;

$g_m$  – transcondutância do transistor.

A influência deste ruído diminui para transistores MOS com canais mais largos, onde há maior capacitância e menor variação. No entanto, este ruído também pode ser minimizado através de processos de fabricação com altos padrões de pureza, o que reduz a constante k, a qual é diretamente proporcional à fonte de ruído. Deve-se também considerar que esta constante é 50 vezes maior em transistores NMOS se comparada a constante em transistores PMOS (Lee, 2004).

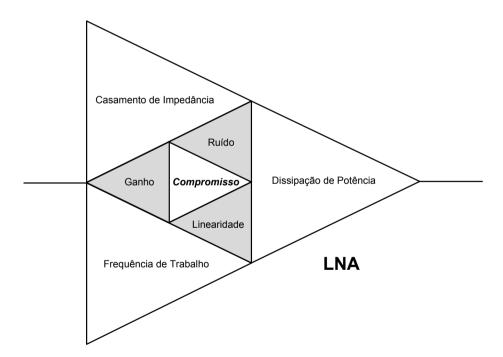

# 4 AMPLIFICADOR DE BAIXO RUÍDO - LNA

## 4.1 Características básicas do LNA

Em um sistema de recepção sem fio, o fraco sinal recebido pela antena deve ser amplificado de forma que haja uma detecção adequada com posterior processamento. Além disso, em sistemas deste tipo, há uma série de dispositivos em cascata que contribuem com um ruído adicional, o qual é potencialmente amplificado ao longo do caminho. Nesse contexto, o LNA é o bloco que tem a função de fornecer ganho suficiente aos baixos níveis de potência que chegam à antena, sem degradar a relação sinal-ruído (SNR) e sendo capaz de sustentar grandes sinais com baixa distorção e baixo consumo de potência quando necessário.

$$F_{tot} = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \frac{F_4 - 1}{G_1 G_2 G_3} + \dots$$

(66)

De acordo com a fórmula de Friis's acima, o Fator ruído total de um sistema com estágios em cascata é dominado pelo Fator Ruído  $(F_I)$  e pelo ganho  $(G_I)$  do primeiro estágio. Logo, pode ser especificado, de forma básica, que a função do amplificador de baixo ruído é ser a fonte de ganho de sinal suficiente para superar o ruído das fases seguintes, e paralelamente, produzir o mínimo de ruído possível.

### 4.1.1 Especificações

Ao se projetar um LNA, a primeira providencia é modular o canal de entrada do sinal para a aplicação de recepção desejada, de forma a definir suas especificações. Isso é feito em termos de uma série de parâmetros e pode variar bastante de acordo com o tipo de projeto. O baixo número de componentes existentes no projeto de um LNA pode aparentar uma falsa simplicidade do projeto, no entanto, a grande dificuldade está no alto compromisso existente entre os distintos parâmetros das especificações do projeto.

Normalmente, em um sistema de recepção (Figura 2.1), o LNA é o bloco posterior ao da antena (ou do filtro), o que significa a necessidade de casar a impedância de entrada com um valor específico (geralmente 50 ohms) que garanta a máxima transferência de potência e um bom isolamento do sinal reverso. Além disso, por ser um circuito de natureza não linear, que após receber excitações fracas na entrada, pode vir a gerar diferentes efeitos não desejados, o LNA também deve considerar a linearidade como um importante fator de projeto. Logo, este é um bloco que não apenas amplifica sinais fracos adicionando o mínimo de ruído, ele deve também manter-se linear ao receber sinais fracos na presença de sinais fortes, evitando componentes indesejáveis para o sistema de RF.

Em resumo, as principais metas a serem obtidas no projeto de um LNA são:

- Máximo ganho;

- Mínima figura de ruído;

- Alta linearidade;

- Casamento na entrada e na saída;

- Isolamento do sinal reverso e;

- Baixo consumo de potência quando necessário.

Entretanto, de modo que o compromisso entre estas especificações seja satisfatório, deve haver uma boa caracterização dos dispositivos analógicos, que infelizmente ainda deixa a desejar em tecnologias CMOS padrão.

Tal caracterização está relacionada com a precisão dos modelos dos dispositivos, que por sua vez está relacionada com a boa caracterização física dos efeitos que dominam os dispositivos em RF. Estes modelos devem considerar o comportamento AC e DC, de linearidade, extração de parâmetros, variações de temperatura, fontes de ruído, bem como as tolerâncias do processo (Razavi, 1998) (Cheng, et al, 1998) (Tsividis, 1999) (Tsividis e Suyama, 1994).

Figura 4.1: Compromisso dos parâmetros no projeto de um LNA.

## 4.1.2 Configurações de LNAs

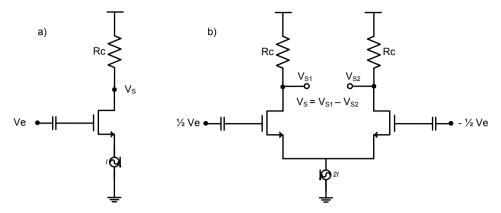

Basicamente, há dois tipos de arquitetura para LNA's em tecnologia CMOS, uma com apenas uma saída e outra com saída diferencial. A Figura 4.2 exemplifica estas arquiteturas de modo simplificado.

Figura 4.2: Arquiteturas de (a) Saída única e (b) Diferencial.

No caso de circuitos com uma única saída (Figura 4.2a), o ganho de tensão é dado por:

$$A_{Vs} = \frac{e_o}{e_i} \approx g_m R_L \tag{67}$$

Em inversão forte, a transcondutância tem uma relação quadrática com a corrente  $I_d$ :

$$g_m = \sqrt{2\mu_n C_{ox} \frac{W}{L} I_d} \tag{68}$$

onde:

$g_m$  – transcondutância do transistor MOS, em inversão forte;

W - largura do canal:

L - comprimento do canal;

$\mu_n$  – mobilidade de elétrons no canal;

$C_{ox}$  - capacitância por unidade de área do capacitor de placas paralelas formado pelo eletrodo da porta e canal;

$I_d$  - corrente pelo dispositivo.

Para circuitos diferenciais (Figura 4.2b), a polarização do amplificador diferencial deve ter o dobro de corrente do que a utilizada por um circuito de saída simples, de modo a se obter o mesmo ganho com transistores de mesmas dimensões. Isto caracteriza uma grande desvantagem com relação a consumo de potência, no entanto, faz-se necessário no sentido de que cada parte do circuito diferencial possua a mesma corrente do circuito de saída simples.

Há casos em que a necessidade de um sinal diferencial adiciona outra desvantagem a este tipo de arquitetura, pois um novo elemento deve ser adicionado ao sistema, nesse caso o *balun*, o qual dará a defasagem do sinal proveniente do estágio anterior (filtro ou antena). Este elemento causa perdas adicionais no sistema, contribuindo assim com a figura de ruído total do mesmo.

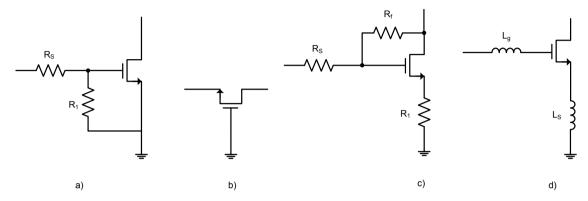

Para alcançar a máxima transferência de potência do sinal é necessário que se faça o casamento de impedância, o qual pode ser interno ou externo. A dificuldade em realizar este casamento é devido à capacitância intrínseca de entrada dos transistores MOS. Encontra-se na Figura 4.3 as principais configurações de LNA para casamento de impedância que podem ser usadas com saída simples ou diferencial. Estas topologias são conhecidas como: Terminação Resistiva, Terminação 1/gm, Realimentação Resistiva e Degeneração Indutiva.

Figura 4.3: Casamento de impedância: (a) Terminação Resistiva; (b) Terminação 1/gm; (c) Realimentação Série; (d) Degeneração Indutiva.

A primeira topologia (Figura 4.3a), utilizada em (Sheng, et al, 1996), fornece um bom casamento de entrada para faixas largas, porém há uma grande degradação no ganho e na figura de ruído do LNA devido a utilização de uma terminação resistiva, que através de seu próprio ruído térmico aumenta a figura de ruído do circuito e atenua o sinal. Uma aproximação do fator ruído F, desprezando o ruído induzido na porta e usando o modelo simples de baixa frequência mostrado na Figura 3.7, pode ser expresso como (Ge e Mayaram, 1998):

$$F \ge 2 + \frac{4\gamma g_{d0}}{g_m^2 R_s} \tag{69}$$

Observa-se na segunda topologia (Figura 4.3b), utilizada em (Houston e Read, 1969), a utilização da fonte de um transistor MOS porta comum como terminação de entrada, onde através da seleção apropriada de suas dimensões e da corrente de polarização, pode-se obter a impedância necessária para o casamento. Para bandas estreitas é gerado um bom casamento, onde a impedância vista pela fonte é 1/gm. No entanto, analisando as equações abaixo, é visto que a figura de ruído é inversamente proporcional ao comprimento do canal do transistor, onde teoricamente, a figura de ruído já possui um valor mínimo antes mesmo de qualquer tentativa de se realizar alterações de valores dos componentes. Para dispositivos de canal longo a figura de ruído mínima é 2.2dB ( $\gamma = 2/3$  e  $\alpha = 1$ ) e para dispositivos de canal curto é 4.8dB ( $\gamma/\alpha = 2$ ).

Considerando que a tendência na evolução da microeletrônica é a contínua diminuição do tamanho do canal, esta topologia se torna menos atrativa em projetos que faz necessário o uso de tecnologias menores. Outro fator importante é a linearidade, que é bastante pobre para esta topologia.

$$NF = 1 + \frac{\gamma}{\alpha} \qquad \alpha = \frac{g_m}{g_{d0}} \tag{70}$$

onde:

NF - limite inferior da figura de ruído para o transistor;

$g_m$  - transcondutância do dispositivo;

O Fator ruído desta topologia pode ser expresso como:

$$F \ge 1 + \gamma g_{d0} R_s \tag{71}$$

A terceira topologia (Figura 4.3c), utilizada em (Benton, 1992) e (N. Sheng, 1991), faz uso da técnica de amplificação com realimentação resistiva, a qual resulta em um projeto bastante linear e com relativa insensibilidade a elementos parasitas da rede de casamento de entrada. Entretanto, necessita-se de uma alta transcondutância para se obter ganho, o que ocasiona um maior consumo de potência, não sendo possível remediar com técnicas de sintonia LC (para tentar minimizar a potência) por se tratar de um projeto típico de banda larga, além de aumentar a figura de ruído devido o uso de resistores. Normalmente esta técnica é utilizada em circuitos de banda larga que necessitam de um bom casamento de impedância, onde consumo de potência não seja um fator determinante. O fator ruído para esta topologia, assumindo o casamento de impedância, pode ser expresso como:

$$F \ge 1 + \frac{G_s + G_f}{g_m - G_f}^2 \gamma g_{d0} R_s + \frac{G_s + G_f}{g_m - G_f}^2 R_s G_f$$

(72)

onde  $G_s$  e  $G_f$  são as condutâncias associadas aos resistores  $R_s$  e  $R_f$ .

A última topologia, chamada de degeneração indutiva (Figura 4.3d), utiliza indutores conectados à fonte do transistor de amplificação para gerar a parte real desejada na impedância de entrada. O amplificador fonte comum necessita de uma sintonia de dreno, tornando esta configuração tipicamente estreita. Sua maior vantagem é a possibilidade de poder controlar o valor da parte real da impedância, o que pode ser feito através da escolha de indutores adequados a cada projeto.

Figura 4.4: Configuração degenerada por fonte com transistor MOS: (a) Circuito; (b) Modelo simplificado para o calculo de Zin.

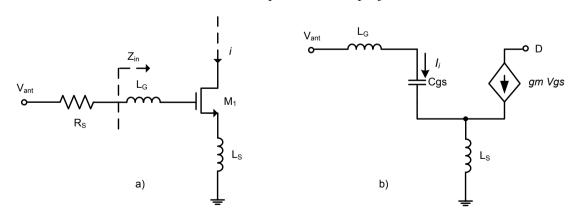

### 4.1.3 Funcionamento de uma topologia básica

Dentre as quatro soluções básicas encontradas na literatura, a topologia com degeneração indutiva é a que apresenta melhor desempenho para LNA's de banda única com relação a ruído, isto devido à ausência de resistores geradores do mesmo. Uma simples análise da impedância de entrada usando transistor MOS (Figura 4.4a/b), mostra que:

$$i_i = v_{gs} \cdot sC_{gs}$$

para  $s = j\omega$  (73)

$$v_{ant} = i_i \cdot sL_g + \frac{i_i}{sC_{gs}} + sL_s i_i + \frac{g_m \cdot i_i}{sC_{gs}}$$

(74)

$$v_{ant} = i_i \frac{g_m \cdot L_s}{cgs} + s(L_g + L_s) + \frac{1}{sc_{gs}}$$

(75)

onde:

v<sub>ant</sub> – é tensão de saída da antena e vista na entrada do LNA ;

Ls, Lg e Cgs – são calculados para estar em ressonância na frequência  $\omega = \omega_0$ ;

Logo,

$$s(L_g + L_s) + \frac{1}{sC_{gs}} = 0$$

(76)

E a impedância de entrada pode ser escrita como:

$$Z_{in.} = \frac{g_m}{C_{gs}} \cdot L_s \qquad Z_{in.} \approx \omega_T \cdot L_s \qquad (77)$$

Onde  $\omega_T$  é a frequencia de ganho unitário de corrente.

É importante ressaltar que o cálculo acima foi realizado desprezando os valores das resistências associadas aos indutores (as quais possuem valores consideráveis em indutores *on-chip*) e a resistência de folha da porta. Para o modelo da Figura 4.4b, o fator ruído para esta topologia é dado por (Shaeffer e Lee, 1997):

$$F \ge 1 + \frac{\omega_0^2}{\omega_T^2} \gamma g_{d0} R_s \tag{78}$$

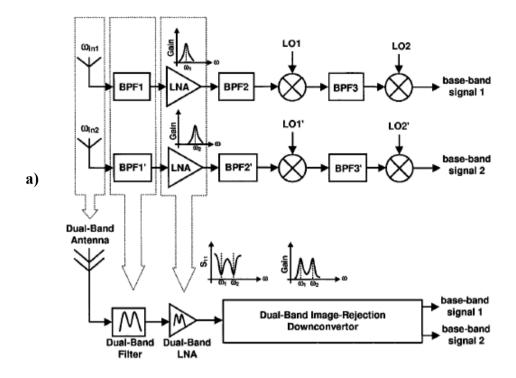

## **5** LNA MULTIBANDA

Nos últimos anos, tem havido um crescente mercado para transceptores que atuam em vários padrões sem fio. A maioria deles tenta maximizar a partilha de hardware para salvar a área do chip, custo e consumo de energia. Atualmente, há algumas soluções *wideband* e multibanda existentes, sendo que cada uma possui uma técnica específica para solucionar um certo tipo de problema para um determinado projeto. Como na maioria dos problemas de engenharia, uma experiência baseada em habilidades e intuições é útil para um projeto bem sucedido. Contudo, faz-se necessário a busca de técnicas utilizadas anteriormente para que se possa obter tal base de conhecimento necessário. Dentre as soluções encontradas na literatura, segue na próxima seção as mais utilizadas atualmente.

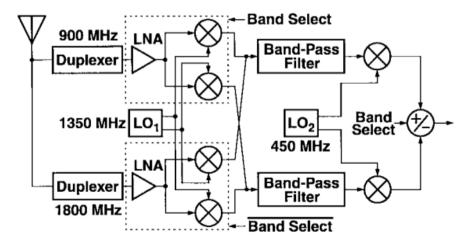

# 5.1 Tipos de LNA Multibanda

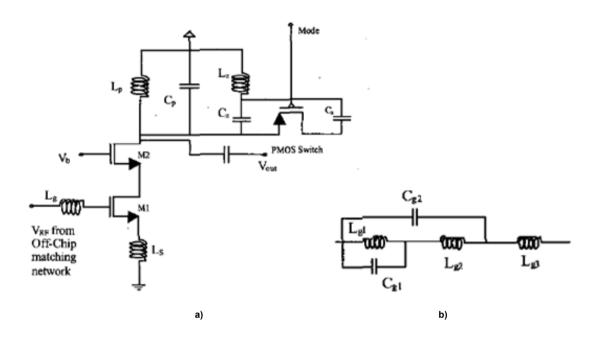

No início principalmente, para se atingir uma implementação *dual-band* (duas bandas de frequência distintas), utilizava-se duas cadeias de recepção, onde era utilizada uma chave para selecionar uma das frequências (Wu e Razavi, 1998). Essa abordagem geralmente degrada a figura de ruído (NF) devido à perda de inserção ocasionada pela chave. A eficiência desta solução é degradada pelo fato de que apenas uma banda pode ser selecionada por vez. Um exemplo desta solução é mostrado na Figura 5.1.

Figura 5.1: Exemplo conceitual de um receptor multibanda (Wu e Razavi, 1998).