# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

#### JAIR FAJARDO JUNIOR

# Sistema de Tradução Binária de Dois Níveis para Execução Multi-ISA

Dissertação apresentada como requisito parcial para a obtenção do grau de Mestre em Microeletrônica

Prof. Dr. Luigi Carro Orientador Prof. Dr. Antonio Carlos S. Beck Filho Co-orientador

Porto Alegre, agosto de 2011.

# CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Fajardo Jr, Jair

Sistema de Tradução Binária de Dois Níveis para Execução Multi-ISA / Jair Fajardo Junior — Porto Alegre: Programa de Pós-Graduação em Microeletrônica, 2011.

76 p.:il.

Dissertação (mestrado) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica. Porto Alegre, BR – RS, 2011. Orientador: Luigi Carro.

1.Tradução Binária 2.Arquiteturas Reconfiguráveis 3.Sistemas Embarcados I. Carro, Luigi. II. Beck Filho, Antonio C. S. III. Título.

# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitora de Pós-Graduação: Prof. Aldo Bolten Lucion Diretor do Instituto de Informática: Prof. Flávio Rech Wagner

Coordenador do PGMicro: Prof. Ricardo Reis

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

# **SUMÁRIO**

| LIST  | TA DE ABREVIATURAS E SIGLAS                             | 5  |

|-------|---------------------------------------------------------|----|

| LIST  | 「A DE FIGURAS                                           | 6  |

| LIST  | TA DE TABELAS                                           | 8  |

| RES   | SUMO                                                    | 9  |

|       | STRACT                                                  |    |

|       | NTRODUÇÃO                                               |    |

|       | -                                                       |    |

|       | Soluções Existentes                                     |    |

|       | Motivação                                               |    |

|       | Contribuições deste trabalho Organização deste trabalho |    |

|       | <i>,</i>                                                |    |

| 2 S   | SISTEMAS DE TRADUÇÃO BINÁRIA                            | 19 |

| 2.1   | Conceitos Básicos                                       | 20 |

| 2.1.1 | Modos de execução                                       | 20 |

| 2.1.2 |                                                         |    |

| 2.1.3 |                                                         |    |

| 2.1.4 | 3 8                                                     |    |

|       | Trabalhos Correlatos                                    |    |

| 2.2.1 |                                                         |    |

| 2.2.2 |                                                         |    |

| 2.2.3 | •                                                       |    |

| 2.2.4 |                                                         |    |

| 2.2.5 | J                                                       |    |

| 2.2.6 |                                                         |    |

|       | Considerações finais                                    |    |

| 3 A   | ARQUITETURAS RECONFIGURÁVEIS                            | 38 |

| 3.1   | Conceitos Básicos                                       | 39 |

| 3.1.1 | Granularidade                                           | 39 |

| 3.1.2 | Acoplamento                                             | 41 |

| 3.1.3 | Modos de Reconfiguração                                 | 41 |

| 3.2   | Trabalhos Correlatos                                    | 42 |

| 4 T   | RADUÇÃO BINÁRIA DE DOIS NÍVEIS                          | 44 |

| 4.1   | Funcionamento do Sistema Proposto                       | 45 |

| 4.2   | Tradução de Código x86 para MIPS (Primeiro Nível)       | 46 |

| 4.2.1 |                                                         |    |

| 4.2.2 | Unidade de Montagem                                     | 49 |

| 4.2.3 | Unidade de PC                                           | 49 |

| 4.2.4 | Unidade de Controle                                          | 49 |

|-------|--------------------------------------------------------------|----|

| 4.3 I | Processador MIPS (Estendido)                                 | 49 |

| 4.3.1 | Processador MIPS                                             |    |

| 4.3.2 | Processador x86                                              |    |

| 4.3.3 | Extensão do conjunto de instruções                           |    |

| 4.4 I | DIM (Dynamic Instruction Merging)                            |    |

| 4.4.1 | Organização da Unidade Reconfigurável                        | 54 |

| 4.4.2 | Tradutor Binário (Segundo Nível)                             |    |

| 4.4.3 | Cache de Tradução (TCache)                                   | 56 |

| 5 M   | ETODOLOGIA E RESULTADOS                                      | 58 |

| 5.1.1 | Simuladores (Software)                                       | 58 |

| 5.1.2 | Ferramentas e Configuração de Simulação                      |    |

| 5.2   | Resultados                                                   |    |

| 5.2.1 | Desempenho                                                   |    |

| 5.2.2 | Potência e Energia                                           | 64 |

| 5.2.3 | Área                                                         | 66 |

| 6 AI  | NÁLISE CRÍTICA                                               | 67 |

| 6.1   | Custos de implementação de todo o conjunto de instruções x86 | 67 |

| 6.2   | Suporte para outros conjuntos de instruções                  | 67 |

| 6.3 I | Estendendo o segundo nível de tradução                       | 68 |

| 6.4 I | Desempenho de outros sistemas de tradução binária            | 69 |

| 7 C   | ONCLUSÕES E TRABALHOS FUTUROS                                | 71 |

| 7.1   | Frabalhos Futuros                                            | 72 |

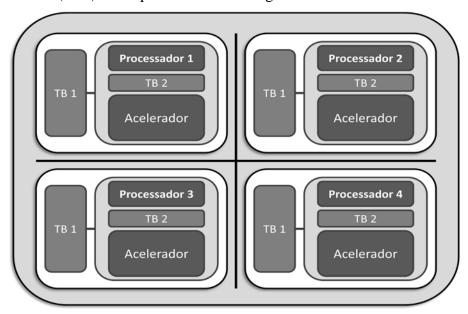

| 7.1.1 | Processador Multi ISA                                        | 72 |

| 7.1.2 | Estudo do sistema utilizando multi-processadores             | 73 |

| REFE  | ERÊNCIAS                                                     | 74 |

# LISTA DE ABREVIATURAS E SIGLAS

ASIP Application Specific Instruction Set Processor

DSP Digital Signal Processor

MP3 Moving Picture Experts Group

GPS Global Positioning System

JPEG Joint Pictures Expert Group

UFR Unidade Funcional Reconfigurável

PPG Processador de Propósito Geral

RISC Reduced Instruction Set Computer

CISC Complex Instruction Set Computer

VHDL VHSIC hardware description language

VLIW Very Long Instruction Word

TB Tradutor Binário

LDH Linguagem de Descrição de Hardware

ISA Instruction Set Architecture

NOC Network On-Chip

SOC System On-Chip

ULA Unidade Lógica Aritmética

ILP Instruction Level Parallelism

TLP Thread Level Parallelism

PC Program Counter

ROM Read Only Memory

SRAM Static Random Access Memory

# **LISTA DE FIGURAS**

| Figura 1.1: Declínio da lei de Moore em termos de desempenho (KIM, AUSTIN, et a 2003).  |     |

|-----------------------------------------------------------------------------------------|-----|

| Figura 1.2: Gráfico de desempenho em relação às diferentes arquiteturas (BECK, 201      | 0). |

| Figura 1.3: Diferentes cenários para a execução de código compilado                     |     |

| Figura 1.4: Sistema de processamento com dois níveis de tradução binária                |     |

| Figura 1.5: Visão geral do trabalho proposto.                                           |     |

| Figura 2.1: Camadas onde o tradutor binário pode ser implementado                       |     |

| Figura 2.2: Camada ocupada pelo tradutor binário em software                            |     |

| Figura 2.3: Tradução binária de x86 para Alpha.                                         |     |

| Figura 2.4: Diagrama de funcionamento do FX!32                                          |     |

| Figura 2.5: Demonstrativo do funcionamento do sistema Dynamo (BALA, 1999)               |     |

| Figura 2.6: Camada ocupada pelo sistema de tradução binária CMS.                        |     |

| Figura 2.7: Comparativo de temperatura entre um Crusoé (b) e um Pentium III             |     |

| Coppermine (a) (KLAIBER, 2000)                                                          | 31  |

| Figura 2.8: Camadas da arquitetura DAISY                                                | 32  |

| Figura 2.9: Tradutor binário situado na camada de interface                             |     |

| Figura 2.10: Resultado do processo de tradução binária de instruções x86 para MIPS.     |     |

| Figura 2.11: Desempenho do sistema ao executar diferentes aplicativos                   |     |

| Figura 3.1: Arquitetura reconfigurável incluída em uma plataforma de processamento      |     |

|                                                                                         |     |

| Figura 3.2: ARs de granularidade fina (a) e granularidade grossa (b e c)                |     |

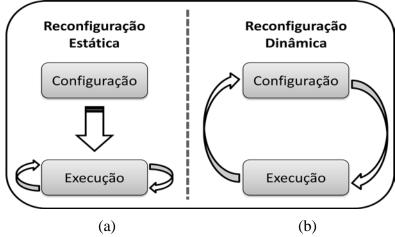

| Figura 3.3: Princípios da reconfiguração estática (a) e dinâmica (b)                    |     |

| Figura 4.1: Mecanismo proposto para este trabalho                                       |     |

| Figura 4.2: Visão geral do trabalho proposto.                                           |     |

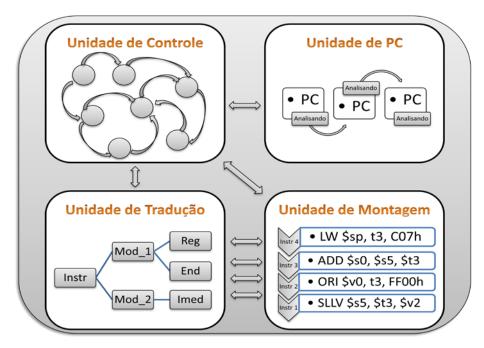

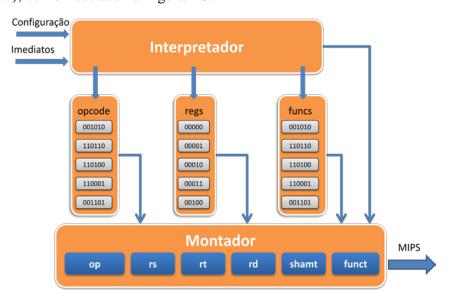

| Figura 4.3: Unidades que compõem o mecanismo de tradução binária                        |     |

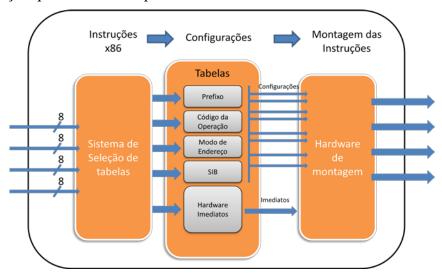

| Figura 4.4: Geração dos bits de configuração correspondente a instrução x86 da entra    |     |

|                                                                                         |     |

| Figura 4.5: Bits de configuração chegando na unidade de interpretação                   |     |

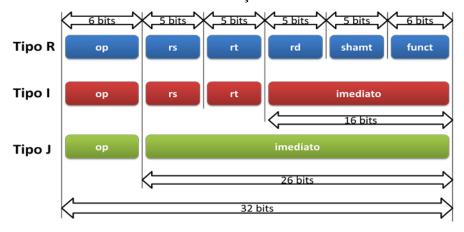

| Figura 4.6: Os três formatos de instruções MIPS.                                        |     |

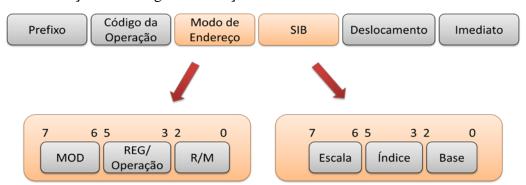

| Figura 4.7: Possibilidades de composição de uma instrução x86                           |     |

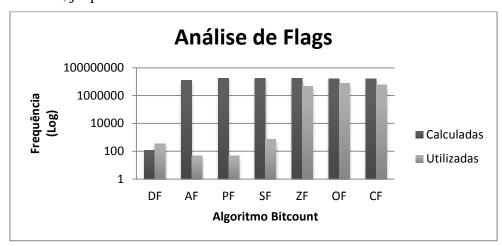

| Figura 4.8: Comparativo entre o número de vezes em que cada <i>flag</i> é calculada e o |     |

| número de vezes em que são utilizadas                                                   | 53  |

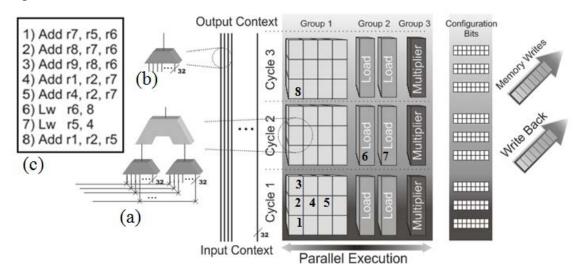

| Figura 4.9: Exemplo de uma configuração da Unidade Reconfigurável a partir de uma       | a   |

| sequência definida de instruções (BECK, RUTZIG, et al., 2008).                          | 55  |

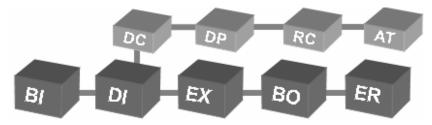

| Figura 4.10: Estágios do Tradutor Binário anexados ao pipeline do processador           | 56  |

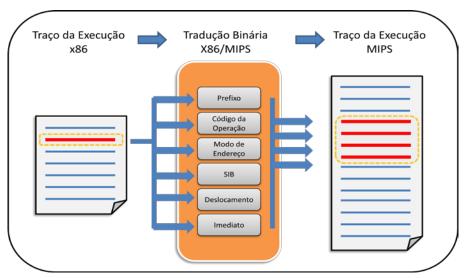

| Figura 5.1: Tradução binária realizada pelo simulador.                                  |     |

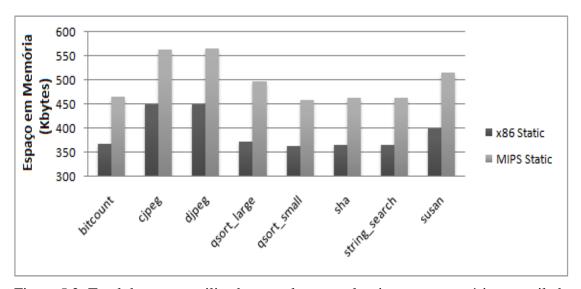

| Figura 5.2: Total de espaço utilizado para alocar os algoritmos na memória, compilad    | los |

| pelo GCC com "-static"                                                                  | 61  |

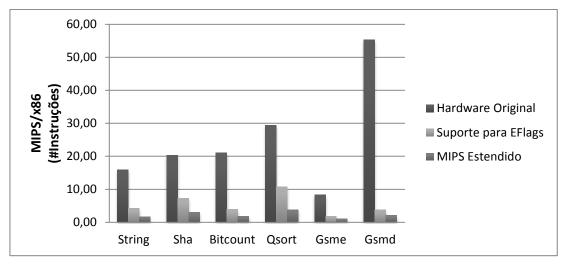

| Figura 5.3: Comparativo entre o número médio de instruções MIPS geradas a cada  |       |

|---------------------------------------------------------------------------------|-------|

| instrução x86                                                                   | 62    |

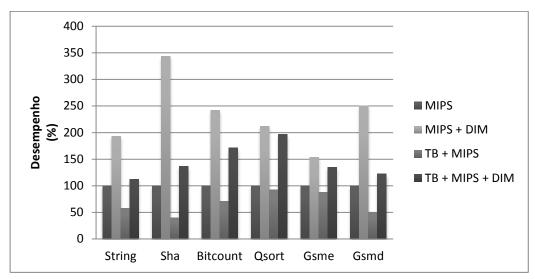

| Figura 5.4: Gráfico de desempenho para quatro diferentes configurações          |       |

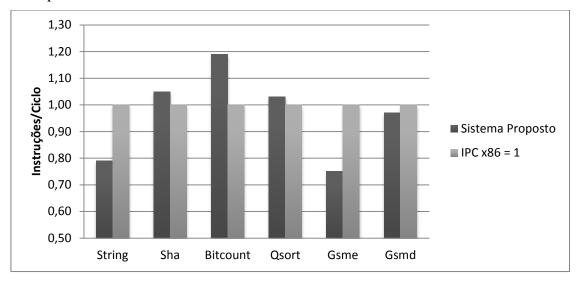

| Figura 5.5: Comparativo do sistema proposto com um processador nativo da arquit | etura |

| x86 com IPC = 1                                                                 | 64    |

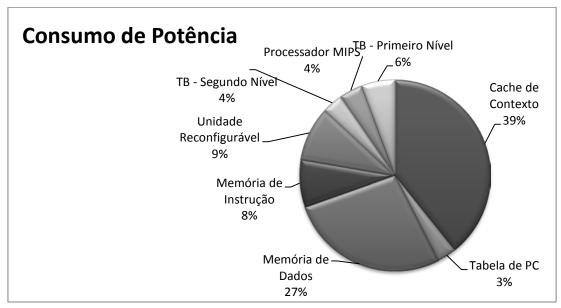

| Figura 5.6: Gráfico demonstrativo do consumo de potência relativo em cada       |       |

| componente do sistema                                                           | 65    |

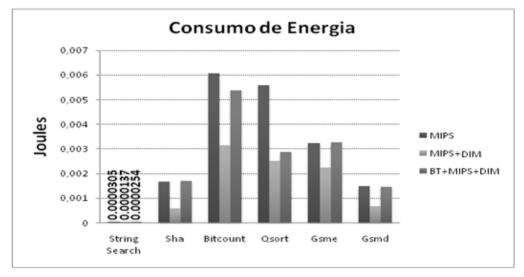

| Figura 5.7: Consumo de energia em três sistemas diferentes                      | 66    |

| Figura 7.1: Processador capaz de executar diversos conjuntos de instruções      | 72    |

| Figura 7.2: Utilização de diversos núcleos em um sistema de processamento       | 73    |

# LISTA DE TABELAS

| Tabela 1: Características da implementação de um TB                        | 22 |

|----------------------------------------------------------------------------|----|

| Tabela 2: Sistemas reconfiguráveis e suas características (BECK, 2010)     | 43 |

| Tabela 3: Um exemplo de tradução de instruções x86 para MIPS               | 52 |

| Tabela 4: Operações realizada por uma instrução complexa                   | 53 |

| Tabela 5: Número de instruções executadas nos dois conjuntos de instruções | 61 |

| Tabela 6: Configurações utilizadas para as simulações de desempenho        | 62 |

| Tabela 7: Custo de área de cada componente do sistema                      | 66 |

# **RESUMO**

Atualmente, a adição de uma nova função implementada em hardware em um processador não deve impor nenhuma mudança no conjunto de instruções (ISA -Instruction Set Architecture) suportado para atingir melhorias em seu desempenho. O objetivo é manter a compatibilidade retroativa e futura de programas já compilados. Todavia, este fato se torna, muitas vezes, um fator impeditivo para o aprimoramento ou desenvolvimento de uma nova arquitetura. Desta maneira, a utilização de mecanismos de Tradução Binária abre novas oportunidades aos projetistas, já que estes mecanismos permitem a execução de programas já compilados em arquiteturas que suportam conjuntos de instruções diferentes do previsto inicialmente. Assim, para eliminar o custo adicional apresentado por estes sistemas de tradução, será proposto um novo mecanismo de tradução binária dinâmico de dois níveis. Enquanto o primeiro nível é responsável pela tradução de facto das instruções do conjunto nativo para instruções de uma linguagem de máquina intermediária, o segundo nível otimiza estas instruções já traduzidas para serem executadas na arquitetura alvo. O sistema é totalmente flexível, pois pode suportar a tradução de conjuntos de instruções completamente diferentes; assim como a utilização de arquiteturas de hardware com as mais diversas características. Este trabalho apresenta o primeiro esforço nesta direção: um estudo de caso onde ocorre a tradução de código x86 para MIPS (linguagem intermediária), que será otimizado para ser executado em uma arquitetura que realiza reconfiguração dinâmica. Resta demonstrado que é possível manter a compatibilidade binária, com melhoria no desempenho em torno de 45% em média e consumo de energia semelhante ao da execução nativa.

Palavras-Chave: tradução binária, sistemas embarcados, arquiteturas reconfiguráveis.

# **Tow-Level Binary Translation System for Multiple-ISA Execution**

# **ABSTRACT**

In these days, every new added hardware feature must not change the underlying instruction set architecture (ISA), in order to avoid adaptation or recompilation of existing code. Therefore, Binary Translation (BT) opens new possibilities for designers, previously tied to a specific ISA and all its legacy hardware issues, since it allows the execution of already compiled applications on different architectures. To overcome the BT inherent performance penalty, we propose a new mechanism based on a dynamic two-level binary translation system. While the first level is responsible for the BT de facto to an intermediate machine language, the second level optimizes the already translated instructions to be executed on the target architecture. The system is totally flexible, supporting the porting of radically different ISAs and the employment of different target architectures. This work presents the first effort towards this direction: it translates code implemented in the x86 ISA to MIPS assembly (the intermediate language), which will be optimized by the target architecture: a dynamically reconfigurable architecture. In this work is showed that is possible to maintain binary compatibility with performance improvements on average 45% and similar energy consumption when compared to native execution.

**Keywords:** binary translation, embedded systems, reconfigurable architectures.

# 1 INTRODUÇÃO

Nos últimos anos, houve um grande salto de crescimento no mercado de sistemas embarcados (VASSILIADIS, 2006) enquanto o consumidor final tem exigido cada vez mais poder de processamento. A tendência é a unificação de diversas funcionalidades em um mesmo dispositivo, com a mesma ou superior qualidade dos dispositivos anteriormente individualizados. Esta união de diferentes funcionalidades podem ser visualizadas em aparelhos como os *smartphones*, onde em apenas um celular foram integrados funcionalidades de áudio e vídeo, jogos, editor de texto, navegação na internet, GPS (*Global Positioning System*) e etc.

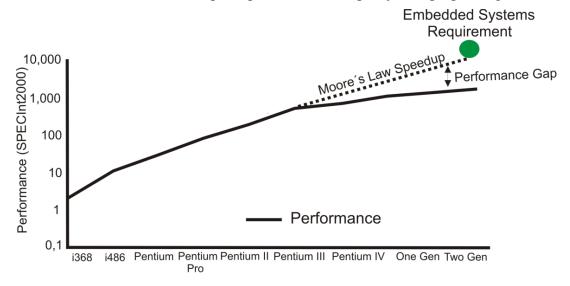

Com a Lei de Moore entrando em declínio e os processadores chegando ao seu limite de dissipação térmica (FLYNN e HUNG, 2005) (SIMA, 2004) houve uma busca maior de alternativas na área de tecnologia de sistemas computacionais. Esta realidade revela a grande necessidade das empresas na procura de novas soluções que atendam os requisitos orçamentários mínimos (alto poder de processamento e baixo consumo de energia) estipulados pelo mercado de embarcados. A Figura 1.1 demonstra que ao passar dos anos, os processadores não tem conseguido manter a linearidade de desempenho, prevista pela lei de Moore.

Um ponto muito significativo para o desenvolvimento de novas arquiteturas computacionais é a questão da compatibilidade binária entre os códigos de aplicativos já existentes e os que irão surgir. Para os desenvolvedores de hardware, existe uma grande dificuldade de lançar no mercado novos modelos de processadores, pelo fato de que existe a necessidade do reaproveitamento de ferramentas e códigos já desenvolvidos e compilados.

Outra questão importante é que no ponto de vista de uma empresa desenvolvedora de software se torna muito custoso o treinamento de funcionários para codificação em novos conjuntos de instruções. Seria muito mais simples se a informação a respeito do hardware que compõe o sistema pudesse ser abstraída, assumindo-se, desta forma, que o mesmo aplicativo poderia ser executado em componentes de hardware diferentes. Já para os usuários, os aplicativos desenvolvidos apenas em uma linguagem perdem em flexibilidade, sendo reduzida a possibilidade de utilizar o mesmo código compilado em diferentes processadores, tornando-os assim, totalmente dependentes da arquitetura utilizada.

Existem famílias de processadores muito bem difundidas e solidificadas no mercado, juntamente com uma série de aplicativos já desenvolvidos e compilados com seu conjunto de instruções proprietários. Assim, pode-se concluir que disponibilidade de

serviços para o usuário está diretamente ligada ao modelo de processador escolhida. Podem ser citados como exemplos os processadores ARM (ARM, 2011) no mercado de sistemas embarcados e os processadores x86 (INTEL, 2011), que estão no mercado há mais de 30 anos e são utilizados principalmente na computação de propósito geral.

Figura 1.1: Declínio da lei de Moore em termos de desempenho (KIM, AUSTIN, *et al.*, 2003).

## 1.1 Soluções Existentes

Algumas técnicas (tanto em hardware como software) foram propostas como solução para este problema. Dentre elas está a interpretação por software. Esta solução permite a execução de código previamente compilado em diferentes conjuntos de instruções em apenas um único processador. Cada código executado pelo aplicativo é analisado em tempo real pelo interpretador, e em seguida, realizada uma conversão entre os conjuntos de instruções nativa do aplicativo e o novo conjunto do processador.

A utilização desta técnica traz como principal benefício a execução de um mesmo código binário em diferentes arquiteturas. Porém, existem significativas desvantagens, podendo ser citado o sistema de interpretação por software que necessita de uma camada extra de software entre o aplicativo e o processador e, sendo assim, a sua execução em muitos casos é mais lenta quando comparado com a execução do código nativo. Também pode ser mencionado a necessidade de haver um interpretador implementado no mesmo conjunto de instruções do processador alvo.

Outra solução proposta é o emulador por microcódigo (HENNESSY e PATTERSON, 2007) que realiza um processo semelhante ao interpretador de software. Todavia, este é implementado em hardware, dispensando um custo alto de processamento. Esta arquitetura é responsável pela decodificação do código do aplicativo para o novo conjunto de instruções. O mecanismo interno de funcionamento é basicamente formado por uma memória ROM (*Read Only Memory*) de alta velocidade para armazenamento do microcódigo e uma máquina de estados para realizar o controle interno do sistema. Entretanto, este sistema não é flexível pois é totalmente dependente do processador para o qual o sistema foi programado.

Geralmente a escrita do microcódigo é feita pelos engenheiros de projeto da arquitetura. Existem alguns emuladores que permitem a adição de microcódigo através

de uma memória flash ou SRAM (*Static Random Access Memory*), porém normalmente este nível é transparente para o programador comum. Uma utilidade prática desta técnica é permitir que instruções CISC (*Complex Instruction Set Computer*) sejam executadas em processadores mais simples do tipo RISC (*Reduced Instruction Set Computer*), apenas adicionando uma camada extra de hardware e mantendo assim a compatibilidade binária. Esta solução já é utilizada há muito tempo nos processadores da Intel que transformam instruções CISC x86 (complexas) em instruções RISC para serem executadas internamente (HINTON, SAGER, *et al.*, 2001).

Existe também uma terceira solução, conhecida como tradução binária. A tradução binária possui o mesmo objetivo das técnicas anteriores, ou seja, manter a portabilidade de aplicativos em diferentes conjuntos de instruções com ou sem a intervenção do usuário final. A principal diferença entre um Tradutor Binário (TB) e as técnicas citadas anteriormente é que, além de guardar as traduções para uma reutilização futura, ele pode ser implementado de diversas maneiras: pode ser dinâmico ou estático; e pode ainda ser implementado como uma camada de software ou hardware. Este tópico é o foco principal deste trabalho e será discutido com mais riqueza de detalhes nos próximos capítulos.

# 1.2 Motivação

Conforme o comentado na seção anterior, usuários de sistemas embarcados, como telefones celulares do tipo *smartphone*, querem abstrair qual processador está sendo utilizado em um determinado produto ou ainda qual a frequência em que o processador está computando dados. Entretanto, maior importância é dada para questões como a quantidade e a disponibilidade de software para o seu produto, a forma satisfatória de execução dos aplicativos no equipamento, e ainda se estes mesmos aplicativos poderão ser executados em novas versões do produto.

Analisando as soluções existentes citadas na seção anterior, com a tradução binária é possível, em muitos casos, atingir ganhos de desempenho quando comparada com a interpretação de software e o emulador de microcódigo. Isto ocorre porque os dois modelos anteriores não se preocupam com as otimizações do código em tempo de execução para eliminar a queda no desempenho do sistema. No primeiro caso, o tempo de computação sempre é maior devido à concorrência no processamento entre a execução do interpretador e a execução do aplicativo.

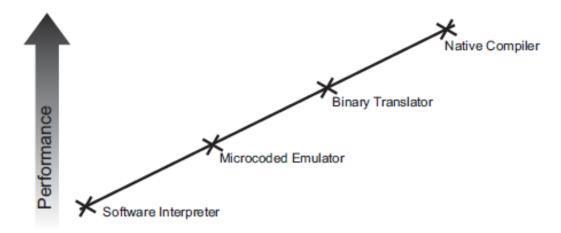

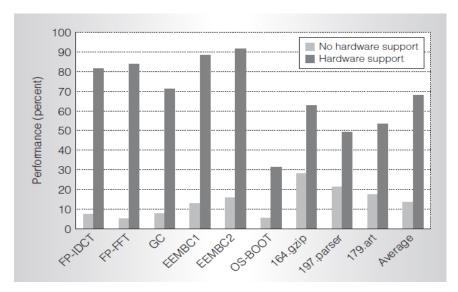

A Figura 1.2 ilustra um gráfico de desempenho, demonstrando a superioridade dos programas traduzidos em relação aos códigos interpretados ou se utilizando a solução por microcódigo. Porém, a tradução possui um desempenho menor quando comparada a execução nativa com otimizações em tempo de compilação.

Figura 1.2: Gráfico de desempenho em relação às diferentes arquiteturas (BECK, 2010).

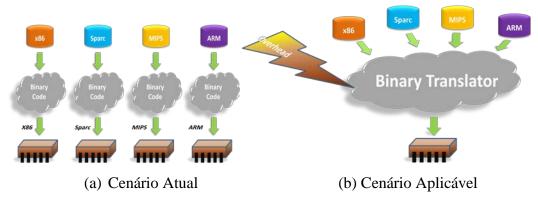

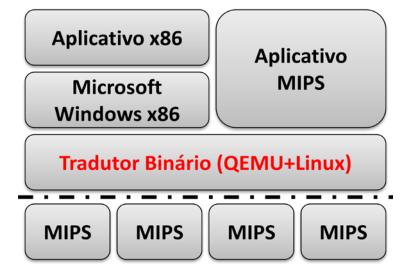

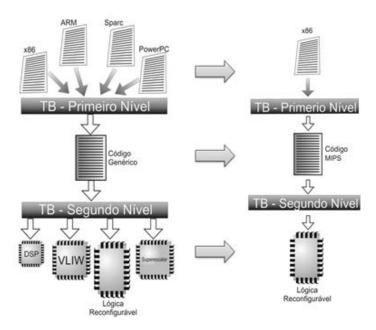

Para melhor visualização da problemática e baseando-se na solução da utilização de sistemas de tradução binária, existem hoje três diferentes cenários:

- Cenário atual: cada aplicativo compilado em um determinado conjunto de instruções deverá ser executado no seu correspondente processador. Neste cenário existe uma forte dependência entre o software e o hardware. Por exemplo, um código compilado no conjunto de instruções X86 somente poderá ser executado em um processador AMD, Intel, etc. Este cenário pode ser melhor ilustrado através da Figura 1.3 (a).

- Cenário ideal: de forma independente do conjunto de instruções em que o aplicativo foi compilado, esse código seria executado em um processador genérico de forma eficiente, ou seja, com desempenho igual ou melhor que o processador nativo. Por exemplo, dois códigos compilados para conjuntos de instruções diferentes (ARM e PowerPC) poderiam ser executados no mesmo processador de forma eficiente.

- Cenário aplicável: o aplicativo que foi desenvolvido e compilado visando a execução em um determinado processador, poderá ser executado em um processador genérico através da inserção de uma camada de tradução binária entre o caminho crítico do hardware e o software. No entanto, este cenário (exibido na Figura 1.3 (b)) impossibilita que o aplicativo seja executado com o mesmo desempenho quando se for comparado com a execução nativa.

Apesar da ideia de um tradutor binário ser simples, na prática, a complexidade deste sistema é muito alta, pois existem diversas variáveis (formato da instrução, manipulação de dados, modo de endereçamentos, *flags* de estado) a serem analisadas e que precisam ter seu comportamento emulado perfeitamente.

Figura 1.3: Diferentes cenários para a execução de código compilado.

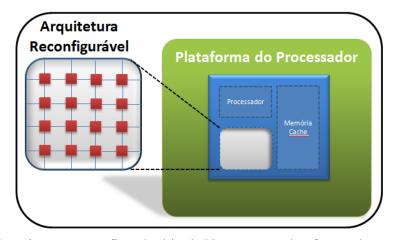

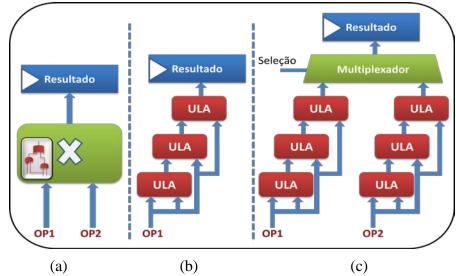

Para eliminar o impacto causado pelo tradutor binário e fazer com que o processador genérico idealizado tenha uma execução satisfatória, é necessário que este sistema (tradutor binário e processador) possibilite uma execução de código compartilhada com aceleradores em hardware. Estes aceleradores são sistemas especializados na execução de trechos específicos de código, aproveitando-se características como a exploração de paralelismo e/ou hardware otimizado. Entre os aceleradores podem ser citados: processadores VLIW (*Very Long Instruction Word*) que exploram paralelismo; processadores DSP (*Digital Signal Processor*) que, por exemplo, possuem o hardware otimizado para operações do tipo "multiplica e acumula"; e arquiteturas reconfiguráveis que permitem que o hardware se adapte de acordo com a necessidade do código.

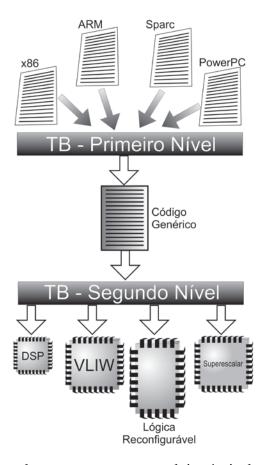

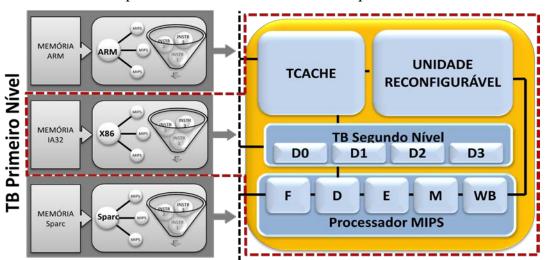

Com a adição de um hardware acelerador, outro impasse é criado. Os aceleradores também possuem um conjunto de instruções proprietário, impossibilitando o seu uso na execução direta do código traduzido pelo primeiro nível de tradução binária. Neste caso, a ideia foi inserir um segundo nível de tradução binária, que realiza a tradução do código genérico para o código do acelerador, gerando assim um sistema de tradução binária de dois níveis. As possibilidades deste sistema podem ser melhores visualizadas na Figura 1.4, onde a primeira camada de tradução binária é responsável pela transformação do código de um determinado conjunto de instruções para um código pertencente a um conjunto de instruções genérico, enquanto a segunda camada otimiza este código para ser executado em *hardware* otimizado. Como há uma interface bem definida entre as duas camadas, o sistema é, ao mesmo tempo, flexível (o conjunto de instruções a ser traduzido pode ser modificado, assim como o *hardware* alvo, sem que hajam alterações na camada oposta) e eficiente, pois ambas as camadas são implementadas em *hardware*.

Devido as propriedades de um código compilado, onde a maior parte do tempo de computação de um aplicativo se concentra em uma pequena porção do código escrito, ou seja, na execução de laços (for e while) e rotinas, é possível melhorar o desempenho de um aplicativo se estas partes específicas do código forem executadas de forma mais eficiente. De tal modo, a queda no desempenho de execução causada pelos dois níveis de tradução poderá ser compensada com a execução rápida de partes chave do código. Esta possibilidade é a temática do trabalho e será fortemente discutida e avaliada nos próximos capítulos.

Figura 1.4: Sistema de processamento com dois níveis de tradução binária.

## 1.3 Contribuições deste trabalho

Este trabalho é baseado na ideia do uso de dois níveis de tradução binária para a execução satisfatória de código não nativo. A finalidade do trabalho é implementar um estudo de caso da proposta supracitada: um sistema completo que executa código compilado para o conjunto de instruções X86 em uma arquitetura reconfigurável de forma eficiente, onde este sistema é capaz de executar os dois conjuntos de instruções.

Para o primeiro nível de tradução binária, foi desenvolvido um novo mecanismo dinâmico implementado em hardware que funciona como interface entre o processador e a memória de instruções. Este primeiro nível tem a função de manter a compatibilidade binária entre dois diferentes conjuntos de instruções. Para o segundo nível de tradução binária foi utilizada uma arquitetura reconfigurável (revisão bibliográfica no Capítulo 2) já existente chamada DIM (*Dynamic Instruction Merge*) funcionando assim como acelerador de execução de código e amortizando os custos do primeiro nível.

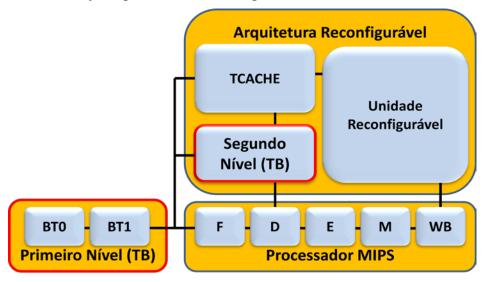

Como já mencionado, o trabalho visa o estudo de caso, onde o primeiro nível é responsável pela tradução do código nativo x86 para MIPS (neste caso, o código genérico da Figura 1.4), enquanto o segundo nível otimiza partes do código traduzido em tempo de execução para que futuramente sejam executadas na arquitetura reconfigurável. A Figura 1.5 exibe uma visão geral do sistema de tradução com dois níveis.

O tradutor binário de primeiro nível foi desenvolvido tanto em hardware como em software (simulador) para extrair resultados mais rápidos e seguros. Com o hardware foi possível extrair dados como área, potência e energia. Já com o simulador em software, foi possível analisar o comportamento do código compilado, número e tipo de instruções, avaliar as possibilidades de melhorias no hardware, tempo de computação entre outras informações que serão discutidas posteriormente.

Figura 1.5: Visão geral do trabalho proposto.

As principais contribuições deste trabalho, em resumo, são:

- Implementação de uma ferramenta de simulação em linguagem C que realiza a tradução de código X86 para MIPS;

- Avaliação do comportamento do código compilado em termos de número e tipo de instruções, tempo de computação e uso de EFlags;

- Determinação das melhorias a serem feitas no hardware para otimização da execução;

- Utilização em série do simulador em software desenvolvido neste trabalho, com o simulador já desenvolvido da arquitetura reconfigurável;

- Desenvolvimento de um protótipo de hardware de tradução binária em VHDL:

- Extração dos custos de área, desempenho e energia utilizando as ferramentas da Synopsys;

- Validação do funcionamento do sistema.

## 1.4 Organização deste trabalho

Neste trabalho os capítulos estão organizados de forma a seguir uma sequência lógica e auto suficiente para o entendimento do sistema de tradução binária de dois níveis. Após esta introdução, onde foram discutidas as soluções existentes, foi descrita a motivação que levou a implementação do trabalho e na sequência suas contribuições. No Capítulo 2, através de uma revisão bibliográfica, serão vistos os sistemas de tradução binária mais utilizados na atualidade. Neste mesmo capítulo serão apresentados conceitos básicos a respeito de tradução binária, nomenclaturas, definições, formas de implementação e características gerais. É necessária também uma

breve explanação a respeito de cada um dos principais sistemas de tradução binária, suas funcionalidades e peculiaridades.

O capítulo 3 traz uma revisão bibliográfica a respeito de arquiteturas reconfiguráveis, o conceito de granularidade e acoplamento, além das formas de reconfiguração. Esta revisão é necessária para que o leitor se situe melhor na funcionalidade do segundo nível de tradução. Da mesma forma, o Capítulo 2 terá uma amostra sobre arquiteturas reconfiguráveis existentes, porém de forma mais sucinta, já que este tema não faz parte da discussão principal e nem foi fruto do desenvolvimento deste trabalho.

No capítulo 4 o tema deste trabalho será apresentado de forma mais aprofundada. Detalhes sobre o funcionamento de seu hardware, composição, diferenças arquiteturais e na semântica dos conjuntos de instruções x86 e MIPS, bem como as características funcionais do sistema como um todo serão exibidos.

O capítulo 5, apresenta a metodologia permitindo a repetibilidade dos experimentos e os resultados obtidos durante a fase de validação do sistema. Além disso, este capítulo irá apresentar os resultados e juntamente uma discussão a respeito dos dados apresentados.

Uma visão crítica realizada no capítulo 6, comentando a respeito dos resultados atingidos por outros trabalhos correlacionados. Neste capítulo também será discutido as possibilidades de se substituir o segundo nível de tradução binária por outro sistema equivalente.

Finalmente, no capítulo 7 serão apresentadas as devidas conclusões do trabalho, juntamente com os trabalhos futuros, mostrando as possibilidades para dar continuidade e expansão desta dissertação.

# 2 SISTEMAS DE TRADUÇÃO BINÁRIA

Nos últimos anos, a dependência software/hardware vem se tornando cada vez mais presente no mercado de processadores e, também, mais significativa, ao passo em que novas plataformas são desenvolvidas e tecnologias incompatíveis entre si são criadas. O mercado de processadores para sistemas embarcados é relativamente novo e existem diversas empresas tentando fixar o seu produto. Esta diversidade arquitetural torna cada vez mais comum o surgimento de aplicativos exclusivos (dependentes do conjunto de instruções). Empresas e pesquisadores há muito tempo visualizaram esta problemática. No decorrer de aproximadamente 10 anos, se estuda e se desenvolve sistemas de tradução binária como uma possível solução arquitetural para problemas de compatibilidade binária entre processadores.

Basicamente, o método de tradução binária consiste em converter um código já compilado para um determinado conjunto de instruções apontado pelo processador, no qual o código será executado de fato. Como resultado desta tradução, surge a possibilidade de executar um aplicativo que anteriormente era dependente de um hardware proprietário em outro sistema que utiliza um conjunto de instruções diferente. Para o usuário do sistema, esta tradução é abstraída e o aplicativo é executado da mesma forma como se o programa estivesse sendo utilizado no processador nativo. No entanto, poderá existir uma diferença em termos de tempo de computação e consumo de energia. Neste caso, o usuário poderia perceber, por exemplo, que seus aplicativos são executados de forma mais lenta ou ainda que o tempo de vida da sua bateria foi reduzido.

O aumento no tempo de computação causado pela execução de um tradutor binário não é desprezível. O sistema está sujeito a uma perda de desempenho em relação à execução de código em um processador nativo. Esta queda no desempenho deve-se a inserção de uma camada adicional entre o hardware e o software (i.e. tradutor binário). Esta limitação poderia tornar esta técnica impraticável, principalmente considerando o mercado de sistemas embarcados, onde qualquer custo adicional tem grande impacto ao usuário.

Além do mais, espera-se que a tradução binária, no futuro, possa trazer outros benefícios, como a possibilidade de que um código uma vez escrito possa ser executado em qualquer modelo de processador (*write once, run everywhere*) e ainda tirando proveito de toda a tecnologia que determinado hardware possa oferecer para a aceleração do software.

#### 2.1 Conceitos Básicos

As arquiteturas de processadores apresentam muitas diferenças. Por exemplo, os processadores têm diferentes quantidades de registradores (propósito geral ou não), utilização de *flags* de estado, número de unidades funcionais, interrupções, tipos de instruções (CISC ou RISC) e até mesmo a forma como exploram o paralelismo (superescalar ou VLIW).

Entretanto, segundo (ALTMAN, KAELI e SHEFFER, 2000), partindo do princípio que todos processadores são baseados em uma máquina de Turing, apesar de suas diferenças, todos podem ser emulados de um para o outro. Porém, à medida que cresce a complexidade dos processadores, aumentam-se também as dificuldades de realizar o processo de tradução binária.

Devido à complexidade dos sistemas de tradução binária, frequentemente se emprega uma nomenclatura própria, assim, torna-se importante um breve resumo explicativo a este respeito. Algumas das principais são citadas abaixo:

- Arquitetura nativa: conjunto de instruções para o qual o código foi originalmente compilado;

- **Arquitetura alvo**: código o qual um tradutor binário gerou após analisar e traduzir as instruções de uma arquitetura nativa;

- Cache de tradução (TCache): memória utilizada para alocar o resultado do processo de tradução binária de um trecho de código a fim de ser reaproveitado futuramente;

- Máquina virtual de monitoramento: conhecida também como VMM (Virtual Machine Monitor): realiza o controle da execução do tradutor binário e o momento correto em que um código otimizado deverá ser executado.

Nos próximos tópicos serão apresentados mais alguns conceitos que definem a semântica de um mecanismo de tradução binária, contemplando as camadas de execução de um TB e suas características. Além disso, outras estratégias possuem particularidades em relação aos benefícios e problemas que um sistema pode enfrentar. Estas características são totalmente dependentes da forma de implementação, seja ela software/hardware e dinâmico/estático ou ainda, a relação dos mecanismos de TB com os processos de otimização de código.

#### 2.1.1 Modos de execução

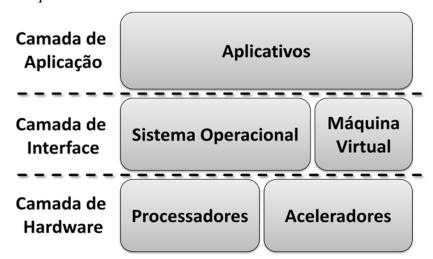

Talvez uma das primeiras decisões de implementação ou característica a ser observada em um tradutor binário é o seu modo de execução. Tradutores binários podem ser executados em diferentes camadas dentro de uma arquitetura computacional. Alguns sistemas ocupam um espaço adicional no hardware, outros são executados em uma camada abaixo do sistema operacional e existem ainda arquiteturas que são executadas de forma similar a um aplicativo podendo, inclusive, ser visíveis ao usuário. Desta forma, o modo de execução refere-se à camada onde o TB será implementado e que será o foco de sua tradução. Basicamente existem três camadas de abstração (ilustradas na Figura 2.1) possíveis, onde as duas primeiras são camadas de software:

Camada de Aplicação: a sua implementação é feita da mesma forma que um aplicativo comum. É dependente do sistema operacional e utiliza seus recursos (por exemplo, bibliotecas) no momento da sua execução. Geralmente, neste caso, o tradutor binário é executado somente quando o aplicativo compilado na arquitetura nativa é chamado. Tanto o tradutor binário quanto o sistema operacional já estão compilados e preparados para a arquitetura alvo.

- Camada de Interface: nesta camada o tradutor binário está situado abaixo da camada do sistema operacional. Todo o software (SO e aplicativos), com exceção do TB, está compilado para uma determinada arquitetura nativa. Para o SO, o tradutor binário pode ser equiparado a uma máquina virtual, no qual somente após a tradução do código fornece acesso ao hardware de fato. Desta forma, o usuário não percebe diretamente a execução do tradutor, sendo este o primeiro a rodar na inicialização do sistema. Para tornar a sua execução menos custosa, o mecanismo de TB é desenvolvido e compilado para a arquitetura no qual o código nativo será executado de fato (arquitetura alvo).

- Camada de Hardware: neste caso, o tradutor passa a ter um controle interno dedicado implementado em hardware. Desta maneira, não é gasto poder de processamento da unidade central de processamento para realizar a tradução. Geralmente, neste caso, a tradução é feita com alto desempenho, onde diversos recursos que são necessários para a tradução são executados em paralelo. Entretanto, esta camada faz com que o sistema se torne pouco flexível (já que é difícil de modificar o hardware) e impactante em termos de área e potência consumida pelo processador.

A camada ocupada pelo tradutor está diretamente ligada com a forma no qual este TB irá interagir com o sistema. Por exemplo, caso o TB tenha incluído a funcionalidade de otimização de código (este tema será abortado na seção 2.1.4) e estiver na camada de aplicação, somente a execução do aplicativo será otimizada. Já nas camadas de interface e hardware, qualquer parte do software poderá ser beneficiada pelo processo de otimização que o TB provê, inclusive o sistema operacional. Entretanto, esta característica não revela qual é a camada ideal para execução, dependendo muito do objetivo para o qual este mecanismo será utilizado.

Figura 2.1: Camadas onde o tradutor binário pode ser implementado.

#### 2.1.2 Software/hardware

A composição software/hardware de um sistema de tradução binária tem impacto significativo no funcionamento da arquitetura. Algumas características inerentes à

forma de implementação devem ser analisadas e consideradas como as vantagens e desvantagens devem ser consideradas em um tradutor binário. Na Tabela 1 podemos visualizar melhor as características de ambas.

| Características                                                                                             | Hardware | Software                                                                                                                                                                                    | Observações                                                                                                                                                                   |  |  |

|-------------------------------------------------------------------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Flexibilidade                                                                                               | Não      | Sim                                                                                                                                                                                         | Utilizando um tradutor binário em software, é possível utilizá-lo em outras arquiteturas apenas recompilando o código, já em hardware qualquer modificação é impossibilitada. |  |  |

| Desempenho                                                                                                  | Alto     | Baixo                                                                                                                                                                                       | Em hardware a tendência do sistema é ser mais simples e seu controle é dedicado, já em software o próprio tradutor binário possui execução concorrente com o aplicativo.      |  |  |

| Análise de<br>Código                                                                                        | Baixa    | Alta                                                                                                                                                                                        | As ferramentas disponíveis em hardware são limitadas. Em software as possibilidades de análise do código em termos de complexidade são muito maiores.                         |  |  |

| Recursos de Hardware  Alto  Baixo  hardware, que resume-se memória e processamento implementado em hardware |          | O software tem pouco consumo de recursos do hardware, que resume-se em alocação na memória e processamento. Quando o TB é implementado em hardware, há os custos óbvios de área e potência. |                                                                                                                                                                               |  |  |

Tabela 1: Características da implementação de um TB.

Além da forma de implementação do tradutor, é possível avaliá-lo também conforme o momento em que será realizada a tradução do código. Esta análise de código pode ocorrer de forma dinâmica (em tempo de execução) ou estática (em tempo de computação).

#### 2.1.3 Dinâmico/estático

A forma com que é feita a análise de código é definida por (ALTMAN, KAELI e SHEFFER, 2000) que classificou a arquitetura do TB em três diferentes tipos:

- **Tradutor Estático:** realiza a tradução off-line, ou seja, em tempo de compilação. Desta forma é possível que as otimizações do código sejam feitas de forma mais eficiente que o tradutor dinâmico. Este tipo de tradução também pode utilizar informações extraídas em tempo de execução do aplicativo, através de ferramentas auxiliares, para aumentar a eficiência da otimização.

- Emulador: realiza a interpretação do código em tempo de execução. Todavia, depois de terminada a análise por parte do tradutor binário, geralmente nenhuma tradução é salva em memória para uma futura reutilização. Geralmente sua estrutura é mais simples e baseada em acessos a tabelas que contêm as possíveis configurações da arquitetura para qual a instrução será traduzida.

- **Tradutor Dinâmico:** realiza a tradução e otimização de código em tempo de execução, com a possibilidade de guardar, em uma memória reservada, partes do código que poderão ser utilizadas novamente no futuro. Desta forma, é

possível obter um ganho de desempenho otimizando trechos do código que são executados com maior frequência (laços e rotinas), amortizando o aumento no tempo de computação do sistema. Um exemplo muito conhecido é o Java JIT (*Just-in-Time*), que converte bytecodes JAVA (arquitetura nativa) para o conjunto de instruções da arquitetura alvo de forma dinâmica (YANG, MOON, *et al.*, 1999).

Utilizando a técnica de tradução binária estática, é necessário o uso de uma ferramenta padrão, para que o sistema torna-se visível ao usuário comum possibilitando a intervenção manual no seu processo. Esta intervenção manual pode ser proveitosa caso o usuário tenha um conhecimento mais aprofundado do hardware, já que poderão ser alterados parâmetros que podem ser melhor aproveitados segundo as características da arquitetura alvo e que tornarão o processo mais eficiente.

O emulador e o tradutor dinâmicos realizam análise somente durante a execução do programa e geralmente são transparentes tanto para o usuário final quanto para o programador, ou seja, o código pode ser executado em um processador "A" da mesma forma que seria executado no processador "B". Esta questão é de extrema importância ao ponto que evita a necessidade do usuário final ou o programador comum de conhecer a arquitetura em que o código está sendo executado.

As três formas de implementação revelam a complexidade de um sistema de tradução e que qualquer decisão a respeito do formato ou comportamento do sistema poderá resultar em custos para o usuário, seja ele em termos de potência, queda no desempenho ou ainda transparência. Entretanto, atualmente existe uma forte tendência na utilização de TBs dinâmicos, pelo fato de que dispensam o usuário final ou o programador de um conhecimento mais profundo da arquitetura.

#### 2.1.4 Otimização de código

O conceito de otimização de código está fortemente ligado com a técnica de Tradução Binária. Frequentemente, tradutores binários são executados em paralelo com aceleradores ou ainda possuem este mecanismo incorporado à sua implementação, otimizando o código da melhor forma possível, eliminando dependências, desenrolando laços (do tipo *for* ou *while*), montando instruções que irão tirar melhor proveito do hardware, dentre outras otimizações possíveis.

Apesar da técnica de tradução binária permitir a portabilidade de uma arquitetura à outra, é necessário também que a sua execução seja competitiva com os códigos gerados de forma nativa. Para tanto, a maioria dos sistemas de tradução também realizam análise do código em tempo real, visando otimização e redução do custo trazido pelo mecanismo de tradução. Segundo (CHERNOFF, HERDEG, *et al.*, 1998), arquiteturas de tradução binária podem se comportar como um compilador tradicional de alto desempenho. Todavia, ao contrário dos tradutores binários que têm como entrada o código objeto, os compiladores comuns iniciam a sua análise através do código de alto nível (por exemplo, na linguagem C). Desta forma, são capazes de interpretar melhor o comportamento do programa antes de realizar a otimização e a compilação de fato.

A falta de uma linguagem de alto nível (código fonte C/C++, Java, Pascal) para realizar uma análise mais profunda do seu real funcionamento, faz com que um dos maiores desafios para os sistemas de tradução seja a geração de um código correto e eficiente a partir das informações disponíveis em baixo nível. Algumas destas informações da linguagem de alto nível são perdidas no momento em que o código é

compilado. Desta maneira, muitas das otimizações de código feitas por um compilador ficam impossibilitadas.

Pode-se utilizar como exemplo um processador lançado há 2 anos e que possui a sua arquitetura baseada no conjunto de instruções x86. Um código desenvolvido, compilado e executado para este modelo de processador não terá nenhum tipo de problema de compatibilidade. Mas, se levarmos em conta que nesta família um novo processador é desenvolvido com recursos em hardware que permita também a execução de instruções multimídia (e.g. MMX, SIMD) (INTEL, 2011), o código anteriormente compilado não terá problemas de compatibilidade binária. No entanto, também não será beneficiado com a tecnologia disponibilizada pelo novo processador devido ao seu conjunto de instruções antigo.

Com o uso de um tradutor binário, surge a possibilidade de otimizar o código anteriormente escrito, atualizando partes do código que utilizavam um conjunto de instruções antigo e menos eficiente para as novas tecnologias desenvolvidas, fazendo com que um código anteriormente compilado para um modelo antigo de processador seja readequado para um novo conjunto de instruções, a fim de que tire proveito de todos os artifícios que um novo processador possa oferecer em termos de aceleração.

## 2.1.4.1 Profiling

Segundo (ALTMAN, EBCIOGLU, et al., 2001), em diversas arquiteturas a tradução binária e a otimização de código estão incluídas no mesmo sistema. Porém, técnicas de análise de execução em tempo real como o Profiling, são realizadas separadamente do processo de tradução estática. Esta técnica realiza análise do programa em tempo de execução, extraindo informações que poderão ser utilizadas posteriormente como um guia de otimização. Durante o processamento de um aplicativo, o Profiling é executado em paralelo, verificando quais partes do código são as mais requisitadas (como o número de iterações que ocorre dentro de um laço) e instruções que podem ser executados em paralelo visando aceleração por ILP (*Instruction Level Parallelism*).

Após o Profiling gerar diversos arquivos com uma variedade de otimizações que podem ser feitas no código, o sistema de tradução analisa e associa estes arquivos em um único *profile* (ALTMAN, EBCIOGLU, *et al.*, 2001). Posteriormente o código pode ser novamente analisado, caso o sistema de Profiling altere o padrão de otimização do código. Geralmente estas informações são alocadas em um espaço reservado na memória.

#### 2.1.4.2 Otimização dinâmica

O processo de otimização dinâmica funciona de forma concorrente à tradução binária e pode estar ligada também ao processo de profiling. Estas análises e mudanças no código em tempo de execução permitem que as melhorias para otimizar o processamento sejam sempre atualizadas caso exista mudanças no padrão de execução. Um ponto muito interessante é que dependendo da técnica utilizada, existe a possibilidade do programador comum não ter acesso ao processo de otimização. Muitas vezes, o programador não fica ciente da sua existência, devido ao fato de que o tradutor binário é executado de forma transparente.

Os compiladores realizam a tradução de código estaticamente. Já com tradutores dinâmicos surge a possibilidade de adquirir informações importantes a respeito do comportamento do programa durante sua execução como, por exemplo, com qual frequência que determinada parte do código é executada ou ainda em qual sequência

determinadas instruções podem ser executadas pra aumentar a eficiência de processamento. Estas informações permitem que se façam otimizações que são apenas possíveis por causa da análise dinâmica do programa sendo executado.

Por outro lado, existem alguns problemas enfrentados pela otimização dinâmica, como a necessidade de amortização do custo adicional de processamento. O acréscimo de mais uma camada entre o software e o hardware faz com que o conjunto perca em velocidade de execução para um compilador nativo, devido ao tempo gasto em tradução e otimização. Este atraso pode ser originado dos diversos estágios da tradução binária e até mesmo do tempo de acesso à memória.

Devido a grande geração de dados oriundos das análises realizadas pelo sistema de otimização, se faz necessária a alocação de um espaço dedicado para a arquitetura na memória principal ou a adição de uma memória física, conhecida como Cache de Tradução (TCache).

Dependendo do formato com que os dados são armazenados, pode existir um aumento no tempo de computação devido à alta quantidade de acessos à memória. Se um trecho de código otimizado possuir uma taxa alta de execução, logo serão realizados vários acessos à memória de tradução (TCache), assim o tempo de acesso a este dado na memória torna-se significante para o sistema. Uma das possíveis soluções propostas para minimizar esta perda é criar memórias menores e de rápido acesso permitindo que sequências de código mais executadas sejam alocadas neste espaço de endereçamento (BANAKAR, 2002).

Contudo, segundo (SRIDHAR, SHAPIRO e BUNGALE, 2007), a redução da sobrecarga causada pelo tradutor binário pode estar na simplificação da arquitetura, visando à utilização de algoritmos mais simples para otimização e tradução de código.

#### 2.2 Trabalhos Correlatos

#### 2.2.1 Rosetta

A empresa Apple, que se encontrava em um momento de transição de arquitetura de processador (substituindo PowerPCs por processadores Intel), solicitou à empresa Transitive Corporation o desenvolvimento de um software capaz de permitir que aplicativos, originalmente desenvolvidos para processadores PowerPC, fossem executados na nova família de computadores Macintosh baseados na arquitetura de processamento da Intel.

A Transitive Corporation então, desenvolveu o tradutor binário chamado Rosseta (APPLE, 2011). Apesar de portar ferramentas de otimização, Rosseta não consegue fazer com que o código traduzido seja executado com a mesma eficiência de um código nativo, devido à queda de desempenho causada pelo mecanismo de tradução. Além do mais, por problemas de compatibilidade, nem todos os aplicativos podem ser executados após a tradução. Esta compatibilidade depende do tipo de aplicação e as instruções que são utilizadas pelo programa candidato à tradução.

O Rosetta traduz instruções das versões G3, G4, e AltiVec do PowerPC. No entanto, não é compatível com instruções G5. Desta forma, aplicativos que utilizam instruções G5 devem ser modificados pelos seus desenvolvedores para serem compatíveis com os computadores Macs baseados em processadores Intel. Programas com baixa necessidade de processamento e alta interação com o usuário geralmente têm execução satisfatória após a tradução. Em contrapartida, programas com alta necessidade de

processamento, como a disponibilidade de dados em tempo real (aplicativos multimídia) e computação complexa de modelos 3-D, geralmente tornam a execução do aplicativo bastante lenta.

Durante a tradução binária, o código convertido e otimizado é alocado em uma memória de tradução (TCache), de forma transparente ao usuário final. Esta tradução, após sua devida alocação na memória, poderá ser reutilizada em execuções posteriores, permitido que o aplicativo seja acelerado devido a não necessidade de nova tradução e evitando perdas decorrentes do custo desta atividade. Desta forma, a etapa de tradução binária é desnecessária durante uma grande parte do tempo. Na Figura 2.2 é ilustrada a camada que se esta situado o sistema de tradução.

Figura 2.2: Camada ocupada pelo tradutor binário em software.

No instante em que um programa portador de um código binário não nativo é executado, o Sistema Operacional detecta esta incompatibilidade e executa o aplicativo por meio da interface Rosetta. Para o usuário que está utilizando uma máquina baseada na arquitetura Intel, é imperceptível visualmente a execução e a tradução binária dinâmica do Rosetta, devido à inexistência de qualquer tipo de interface gráfica ou ainda indicativo visual demonstrando que a aplicação está sendo traduzida. Entretanto, o usuário poderá perceber uma queda no desempenho durante a inicialização e execução do aplicativo.

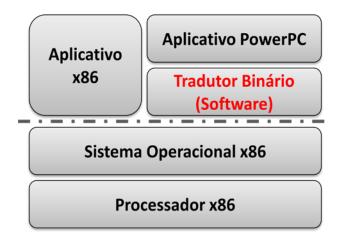

#### 2.2.2 FX!32

O sistema FX!32 (HOOKWAY, 1997) (CHERNOFF, HERDEG, et al., 1998), tinha como premissa a portabilidade de código, possibilitando que qualquer programa originalmente implementado em código Intel x86, possa ser executado em microprocessadores Alpha. O Digital FX!32, é uma camada de software que combina emulador com o sistema de tradução binária do código nativo Intel x86, para o processador alvo Alpha. O emulador realiza conversão do código x86 para Alpha (que também fornece informações de profiling) e um sistema de tradução binária. A partir das informações do profiling, que é gerado em tempo de execução, o tradutor binário gera imagens otimizadas da aplicação por meio de intensivos algoritmos computacionais, com o objetivo de executar o código de forma mais eficiente. Segundo o autor, o FX!32 é o primeiro sistema a explorar esta combinação de emulação e tradução binária.

A camada de software é totalmente transparente ao usuário e permite que programas 32-bit sejam instalados e executados em uma arquitetura x86, executando o sistema operacional Windows NT 4.0, possam também ser instalados e executados em sistemas Alpha executando a mesma versão do SO (desenvolvida implementando o conjunto de instruções nativo do Alpha). As camadas deste sistema estão ilustradas na Figura 2.3.

Figura 2.3: Tradução binária de x86 para Alpha.

Executando aplicativos compilados de forma nativa para a arquitetura Alpha, é dispensado o uso do emulador e do sistema de tradução binária. No momento em que o usuário comum deseja executar um aplicativo compilado para a arquitetura x86, o emulador inicia o processo de geração de código do Alpha a partir das instruções nativas x86 em tempo de execução juntamente com o processo de profiling. Devido ao fato do sistema estar sendo executado na camada de interface, a sua execução é concorrente com a execução do software ocasionando uma queda na velocidade de processamento. Para minimizar o problema de perda de desempenho, foi implementado um sistema de tradução binária em software que realiza otimização do código a partir das informações geradas pelo profiling após a sua execução, impedindo-se que esse processo consuma recursos de processamento juntamente com o aplicativo. Assim, o emulador irá executar o código x86 traduzido e otimizado somente quando for detectado uma pré tradução já existente.

As imagens e as informações de *profiling* são alocadas em um banco de dados para serem utilizadas no momento em que o usuário executar um aplicativo. O servidor coordena as otimizações, tanto em tempo de execução, como as realizadas após a execução, podendo atuar de forma padrão ou de acordo com os parâmetros especificados manualmente pelo usuário. Existe também a possibilidade do usuário controlar os recursos utilizados pelo FX!32 através de um sistema de gerenciamento.

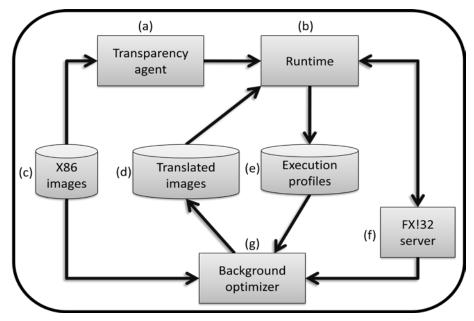

O FX!32 é composto por diversos componentes em software conforme demonstrado na Figura 2.4 :

Figura 2.4: Diagrama de funcionamento do FX!32.

Transparency agent – agente (Figura 2.4a) que garante que o sistema seja invisível durante a sua execução, permitindo que os aplicativos x86 sejam executados sem a distinção de ser ou não código nativo, ou seja, de forma transparente e sem a necessidade de intervenção do usuário comum;

Runtime – carrega as imagens x86 e permite que sejam executadas em tempo real, além disso permite que o código x86 faça chamada de rotinas da API do Windows NT (Alpha) através de pequenos fragmentos de código chamados de "Jackets" (Figura 2.4b). Esta execução ocorre passando pelo emulador no qual disponibiliza análises da execução (Figura 2.4e) e faz uso do código já traduzido (Figura 2.4d) e otimizado (quando disponível);

*Backgroud optimizer* – deste bloco (Figura 2.4g) faz parte o sistema de tradução binária que realiza a otimização do código e gera imagens do código x86 (Figura 2.4d);

*FX!32 Server* – este servidor (Figura 2.4f) provê o serviço de alocar os dados de profiling fornecido pelo emulador e controla o momento em que o tradutor binário deve iniciar a sua execução.

Após a finalização de um determinado aplicativo x86, o servidor realiza uma comparação dos dados de um novo *profiling* com o *profiling* já existente, ambas geradas pelo emulador. Caso as informações estiverem diferentes, significa que o *profiling* atual possui informações incompletas ou desatualizadas, necessitando então, de atualização. Este processo é repetido todas as vezes que o aplicativo for executado.

#### 2.2.3 Dynamo

O Dynamo (BALA, DUESTERWALD e BANERJIA, 2000) é um sistema baseado inteiramente em software, escrito em linguagem C e algumas partes em assembly. Este sistema foi criado por pesquisadores da Hewlett-Pachard (HP) para realizar otimização dinâmica de código. Originalmente o sistema foi implementado para PA-RISC, uma plataforma baseada no PA-8000 executando o sistema operacional HPUX. Esta arquitetura não realiza tradução binária, somente otimização em tempo de execução.

Segundo (BALA, DUESTERWALD e BANERJIA, 2000), pelo fato do Dynamo ser totalmente transparente para o usuário final, este sistema pode ser visto como um processador virtual, onde as otimizações dinâmicas do componente são implementadas na camada de software enquanto o processador é implementado em hardware. Suas otimizações são realizadas baseadas no escopo do código do programa à medida que ele é executado, ou seja, não há nenhum tipo de acesso aos arquivos executáveis.

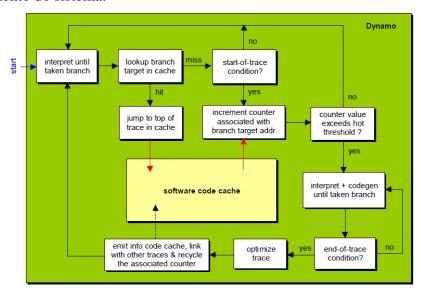

Inicialmente, o Dynamo começa a analisar um determinado trecho de código e verifica se existe uma alta taxa de execução deste grupo de instruções. Depois de satisfeita esta condição, o sistema entra em modo de otimização de código.

As informações referentes aos trechos de instruções mais executados (*hot regions*) são armazenados em um buffer. O otimizador gera uma versão otimizada do conjunto, chamada de fragmento. Este fragmento é então alocado em uma memória reservada (*fragment cache memory*), onde estes fragmentos podem ser integrados dinamicamente através de procedimentos de chamadas. Na Figura 2.5 é apresentado um esquemático de funcionamento do sistema.

Figura 2.5: Demonstrativo do funcionamento do sistema Dynamo (BALA, 1999).

Dentre as técnicas de otimização de código estão incluídas a remoção de redundâncias no código, propagação de constantes, diminuição de instruções de leitura e *loop unrolling*, que é basicamente a reordenação das instruções contidas em um laço e para transformá-las em uma sequência contínua de código, a fim de diminuir o número de instruções de controle (BALA, 2000).

### 2.2.4 Transmeta Crusoé

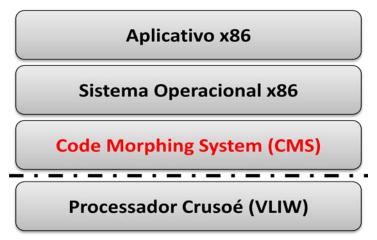

O Crusoé fez parte de um projeto da empresa Transmeta, que visou o desenvolvimento de um microprocessador totalmente compatível com o conjunto de instruções x86, porém que apresentasse alguns fatores diferenciais dos processadores já existentes, em termos de poder de processamento e baixo consumo de energia. Internamente a sua arquitetura é compromissada a um processador do tipo VLIW (*Very Large Instruction Word*) nativo, o qual é dependente de uma camada de software chamada *Code Morphing Software* (CMS).

Cada palavra (nesta arquitetura é chamada de molécula) pode armazenar duas ou quatro instruções do tipo RISC, chamados de átomos. Estes átomos podem ser

executados por cinco unidades funcionais em paralelo: duas ULAs (unidade lógica aritmética), uma unidade de ponto flutuante, uma unidade de memória e uma unidade para tratamento de salto. Além disso, 64 registradores de propósito geral e 32 registradores de ponto flutuante.

O uso deste modelo de processador torna o sistema passível de diversos tipos de otimizações, principalmente em termos de ILP. Desta maneira, aumentam-se as chances de ocupação de todas as unidades funcionais disponíveis do processador, executando o maior número de instruções em paralelo. A família de processadores TM5000 está fortemente ligada à família TM3000. A diferença da nova geração é que a mesma obteve mudanças pela adição de átomos para melhorar a execução das instruções x86

Em software, o sistema Crusoé possui uma camada situada logo abaixo do SO, realizando a interface entre o hardware e o aplicativo CMS, como demonstrado na Figura 2.6. O CMS é a implementação de um sistema de tradução binária em software, que de forma dinâmica realiza a análise de código, otimização e tradução binária.

Figura 2.6: Camada ocupada pelo sistema de tradução binária CMS. Segundo (DEHNERT, GRANT, *et al.*, 2003), os desafios naturais do CMS são:

- O tradutor binário deve implementar completamente a arquitetura x86, incluindo: mapeamento de memória das entradas e saídas, implementação de todo o conjunto de instruções, manutenção do comportamento das interrupções e suporte aos registradores da arquitetura.

- Devido ao CMS ser uma camada de sistema e não de aplicação, o software não pode interferir nas tomadas de decisões do sistema operacional, ou seja, deve ser transparente no ponto de vista de tradução e até mesmo executar instruções da BIOS, tornando-o não dependente de nenhum tipo de informação ou assistência das camadas superiores. Desta forma, o CMS não tem acesso a nenhum tipo de arquivo ou código estático, todas as instruções chegam em tempo de execução para a tradução.

- Com base na grande quantidade de diferentes tipos de aplicativos a serem executados como: jogos, processamento de áudio e vídeo, servidores e sistemas operacionais, o CMS deve prover ao sistema um bom desempenho de tradução e otimização para que seja amortizado o custo desta camada, e ainda tenha um ganho de desempenho na execução das aplicações melhorando o processamento.

Quando o computador é ligado, o Code Morphing é o primeiro programa a ser inicializado. O código do CMS é escrito no formato das instruções do Crusoé. Seu funcionamento ocorre de forma semelhante a outros tradutores: inicialmente um interpretador decodifica e executa as instruções x86 sequencialmente. Quando o número de instruções ultrapassarem uma quantidade mínima, este conjunto é otimizado e guardado com uma indexação através do PC em uma TCache em formato de instruções VLIW. Posteriormente as instruções serão executadas pelo processador quando o mesmo PC for encontrado.

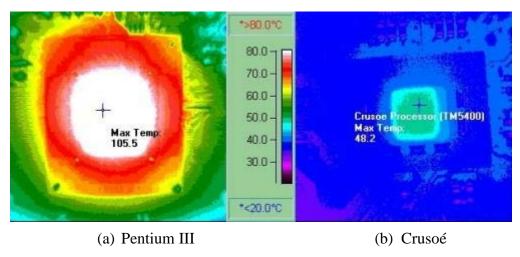

A Figura 2.7a ilustra o mesmo aplicativo sendo executado no Pentium III e ao lado na Figura 2.7b a execução ocorrendo no processador Crusoé. A execução em um processador VLIW permite a combinação da aceleração por ILP juntamente com a diminuição da complexidade do hardware. Como estes fatores são significativos na redução de consumo de potência com alto poder de processamento, pode-se observar que reduzindo a frequência de operação do processador e mantendo o mesmo desempenho, os custos no consumo de potência são reduzidos de forma significante. Tornando-se a otimização do software e hardware necessários e fundamentais para que um sistema funcione de forma eficiente.

Figura 2.7: Comparativo de temperatura entre um Crusoé (b) e um Pentium III Coppermine (a) (KLAIBER, 2000).

# **2.2.5 Daisy**

O sistema DAISY (*Dynamically Architected Instruction Set from Yorktown*) (EBCIOGLU e ALTMAN, 1997) é muito semelhante ao Crusoé, no entanto possui propósitos diferentes quando se refere ao conjunto de instruções e algumas outras particularidades. O objetivo deste projeto é executar o conjunto de instruções do PowerPC em um processador VLIW, possibilitando um ganho de desempenho de processamento, juntamente com uma queda na frequência de operação. Assim, é possível reduzir os custos de energia, quando comparado ao processador original.

Este sistema é composto por três grandes camadas: camada de aplicação, onde está situado o sistema operacional e aplicativos; camada da máquina virtual (DAISY VMM), que realiza a interface entre o hardware e software aplicativo; e camada de hardware, formado pelo processador DAISY VLIW (as camadas estão ilustradas na Figura 2.8). Existem também diferentes tipos de memórias: a TCache que aloca os dados vindos da tradução e otimização de código; a memória do PowerPC, que aloca as instruções no

formato da arquitetura original; e memória de boot que guarda as instruções referentes à inicialização da máquina virtual (DAISY VMM).

Figura 2.8: Camadas da arquitetura DAISY.

A microarquitetura do processador DAISY VLIW é composta por 4 conjuntos, conhecidos como clusters, onde cada cluster possui 4 unidades funcionais e uma ou duas unidades de *load/store*. Para a alocação dos dados resultantes das operações, o processador DAISY VLIW possui 64 registradores de números inteiros, 64 registradores de ponto flutuante e 16 registradores de condição. Este processador também possui suporte a especulação durante a execução.

O processo de tradução binária ocorre de forma totalmente transparente, ou seja, para o usuário final, o processador DAISY VLIW se comporta como se fosse um processador PowerPC. Esta tradução binária é realizada pela camada de software DAISY VMM. Esta camada de software é inicializada juntamente com o boot do sistema. De forma similar ao PowerPC nativo, o endereço da ROM de boot é o mesmo (0xfff00100). O código de boot será interpretado, traduzido e executado sob o controle da máquina virtual.

Quando o DAISY VMM encontra o primeiro fragmento de código nativo PowerPC, ele realiza a interpretação. Durante esta interpretação é realizada uma análise dos dados coletados, para que futuramente sejam utilizados na otimização deste trecho. Estas primitivas são alocadas em uma área de memória que é invisível pelo usuário.

A sequência traduzida é utilizada em chamadas do tradutor binário, para evitar que um código já presente na TCache seja novamente recompilado. Desta forma, o processador DAISY VLIW executa imediatamente a sequência de código otimizada, amortizando o tempo adicional da compilação dinâmica e elevando o grau de paralelismo na execução no nível das instruções (ILP). Cada grupo de código traduzido é vinculado ao endereço PC. Assim, quando um PC já existente for localizado na TCache, entende-se que não existe necessidade de uma nova análise.

A aceleração por ILP e a paralelização na execução do código são os principais focos da arquitetura DAISY, o que permite alcançar um alto desempenho através da adaptabilidade dinâmica de código. Esta otimizações permitem o DAISY a atingir a execução de quase 2,5 instruções por ciclo, mesmo com o custo adicional de sistema.

#### 2.2.6 Godson-3 GS464

O processador Godson-3 (FAN, YANG, et al., 2009) (HU, WANG, et al., 2009) é a terceira geração de processadores Godson. O primeiro multi-core da família surgiu no final do ano de 2008, na China. A grande aposta desta arquitetura está na possibilidade da execução de código x86 em processadores MIPS, através de um sistema de tradução binária em software. No entanto, esta tradução de instruções x86 para MIPS não é realizada de forma simples. Diferenças importantes tanto na arquitetura como na organização dos processadores que executam estes conjuntos de instruções precisam ser consideradas, como por exemplo, flags de estado, modos de endereçamento, movimentação de dados, etc. Devido a estas diferenças, muitas vezes a tradução de uma instrução x86 requer dezenas de instruções MIPS. Para reduzir estes custos de tradução, foram desenvolvidas soluções tanto em software como em hardware, visando tornar este processo o mais eficiente possível. Na Figura 2.10 é possível visualizar exemplos de tradução do código x86 (Figura 2.10a) para MIPS (Figura 2.10b) onde se pode visualizar que cada instrução x86 é transformada em várias instruções MIPS formando um grupo equivalente.

### 2.2.6.1 Sistema (Hardware)

O sistema é formado por processadores superescalares MIPS R10000 modificados (64 bits) com suporte a execução fora de ordem. A comunicação entre eles é feita através de uma mescla entre redes em chip (NOC) e um sistema Crossbar, possibilitando desta forma que até 64 processadores MIPS possam ser instanciados. O modelo descrito (GS464) (HU, WANG, et al., 2009) é composto por quatro processadores, onde cada processador possui duas ULAs de ponto fixo. Ambas executam operações de subtração, lógicas, deslocamento e comparação. Porém, a primeira unidade (ALU1) também executa instruções de chamadas de sistema UNIX (trap), movimentação condicional de dados e instruções de salto. A segunda unidade (ALU2), em contrapartida, executa operações de multiplicação e divisão. Além disso, existem mais duas unidades de ponto flutuante (FALU1 e FALU2), onde a primeira pode executar todas as instruções de ponto flutuante, e a segunda unidade executa instruções de adição, subtração e multiplicação. A memória de sistema suporta 64 bits de endereçamento virtual e 48 bits para endereçamento real. É possível acessar 128 bits (quad word) de dados em apenas um ciclo. Possui dois níveis de memória cache: L1 (instruções e dados) com 64 kbytes (four-way associative) e cache L2 de 512 kbyte.

A tradução de código x86 (CISC) para MIPS (RISC) não é eficiente por causa das diferentes características na semântica de cada conjunto de instruções. Pode ser citado como exemplo o uso de EFlags de estado, que são sinalizadores em hardware que fornecem informações a respeito do resultado de uma determinada operação (negativo, igual a zero, paridade, etc). No caso de instruções X86, a maioria das operações de ponto fixo calculam sinais de estado de acordo com o resultado da operação na ULA. Desta forma, a microarquitetura do Godson-3 foi estendida para auxiliar que a tradução de uma instrução x86 ocorra de forma mais eficiente. Podem ser citadas, além do suporte a *flags* de estado: suporte ao acesso a dados de ponto flutuante, suporte a instruções multimídia (MMX, SSE e SSE2), alterações no modo de endereçamento e mudanças no banco de registradores permitindo inserção e extração de bytes ao invés de apenas palavras.

#### 2.2.6.2 Tradutor binário (Software)

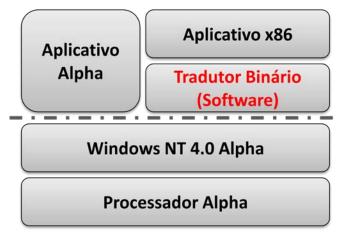

O sistema de tradução binária do Godson-3 foi desenvolvido sobre um sistema operacional Linux, compilado no conjunto de instruções do Godson, ou seja, implementado com as instruções MIPS estendidas. O tradutor binário pode ser considerado intrínseco ao SO, já que provê diretamente as instruções x86 traduzidas para o processador. Desta forma, a camada do mecanismo de TB pode ser visualizada na Figura 2.9.

Figura 2.9: Tradutor binário situado na camada de interface.

O mecanismo de tradução é uma melhoria da máquina virtual QEMU (BELLARD, 2005) com melhorias que permitem tradução binária e otimização no código em tempo de execução. Inicialmente, a VMM interpreta as instruções x86 e as transforma em inúmeras instruções MIPS, continuamente analisando o comportamento da execução. No momento em que um trecho com alta frequência de execução é encontrado, além da tradução, são feitas também otimizações no código para a exploração de paralelismo entre instruções.

Apesar das otimizações serem muito eficazes, a utilização de um tradutor binário em software faz com que o BT seja executado de forma concorrente com o aplicativo, com tempo de computação superior à execução do mesmo código compilado para arquitetura nativa MIPS.

| instructio                                   | of<br>ns   |                                       | Ins                                  | truction                    |                        | Comment                                                             |

|----------------------------------------------|------------|---------------------------------------|--------------------------------------|-----------------------------|------------------------|---------------------------------------------------------------------|

| 0<br>1                                       |            | SUB<br>JE                             | ECX<br>X86_target                    | EDX                         |                        |                                                                     |

| (a)                                          |            |                                       |                                      |                             |                        |                                                                     |

| 0.00<br>0.01<br>0.02<br>0.03<br>0.04<br>0.05 |            | SUBU<br>SRL<br>BEQ<br>ADD<br>B<br>NOP | Result<br>Rsf<br>Result<br>Rzf<br>L2 | Recx<br>Result<br>R0<br>R0  | Redx<br>31<br>L1<br>R0 | /*SF=Result[31]*/<br>/*ZF=0*/                                       |

| 0.06                                         | L1:        | ADDI                                  | Rzf                                  | R0                          | 1                      | /*ZF=1*/                                                            |

| :                                            |            | :                                     |                                      | :                           | :                      |                                                                     |