## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

GUILHERME AUGUSTO FLACH

# **Clock Mesh Optimization**

Thesis presented in partial fulfillment of the requirements for the degree of Master on Microelectronics

Marcelo de Oliveira Johann Advisor

Ricardo Augusto da Luz Reis Coadvisor

Porto Alegre, May 2010

Flach, Guilherme Augusto

Clock Mesh Optimization / Guilherme Augusto Flach. – Porto Alegre: PGMICRO da UFRGS, 2010.

75 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2010. Advisor: Marcelo de Oliveira Johann; Coadvisor: Ricardo Augusto da Luz Reis.

1. Clock. 2. Clock mesh. 3. Skew. 4. Performance. 5. Microprocessor. 6. Variability. 7. Microelectronic. I. Johann, Marcelo de Oliveira. II. Reis, Ricardo Augusto da Luz. III. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Carlos Alexandre Netto Vice-Reitor: Prof. Rui Vicente Oppermann Pró-Reitor de Pós-Graduação: Prof. Aldo Bolten Lucion Diretor do Instituto de Informática: Prof. Flávio Rech Wagner Coordenador do PGMICRO: Prof. Ricardo Augusto da Luz Reis Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

To the beauty of this world, despite its ugliness.

# ACKNOWLEDGMENTS

To my mom and my stepfather for their endless support... To my father who taught me my first computer lessons... And also special thanks to Gustavo Wilke for his unmeasurable contribution to this work.

# CONTENTS

| LIST                                         | OF ABBREVIATIONS AND ACRONYMS           | 11 |  |

|----------------------------------------------|-----------------------------------------|----|--|

| LIST                                         | OF SYMBOLS                              | 13 |  |

| LIST                                         | OF FIGURES                              | 15 |  |

| LIST                                         | OF TABLES                               | 17 |  |

| ABST                                         | RACT                                    | 19 |  |

| RESL                                         | ΙΜΟ                                     | 21 |  |

| 1 IN                                         |                                         | 23 |  |

| 1.1                                          | Clock Signal                            | 23 |  |

| 1.2                                          | Clock Network                           | 23 |  |

| 1.2.1                                        | Signal Regeneration                     | 24 |  |

| 1.3                                          | Clock Mesh                              | 25 |  |

| 1.4                                          | Motivation                              | 26 |  |

| 1.5                                          | Contributions                           | 26 |  |

| 2 TIMING CONSTRAINTS IN SYNCHRONOUS CIRCUITS |                                         |    |  |

| 2.2                                          | Sequential Components: FlipFlops        | 29 |  |

| 2.3                                          | Combinational Paths                     | 30 |  |

| 2.4                                          | Clock Signal Uncertainty                | 30 |  |

| 2.4.1                                        | Clock Skew                              | 30 |  |

| 2.4.2                                        | Clock Jitter                            | 30 |  |

| 2.5                                          | Clock Period Definition                 | 31 |  |

| 2.5.1                                        | Ideal Scenario: Neither Skew nor Jitter | 31 |  |

| 2.5.2                                        | Introducing Clock Skew                  | 31 |  |

| 2.5.3                                        | Introducing Clock Jitter                | 32 |  |

| 2.5.4                                        | Putting All Together                    | 32 |  |

| <b>3</b> SOURCES OF SKEW AND JITTER          |                                         |    |  |

| 3.1                                          | Summary of Skew and Jitter Sources      | 36 |  |

|                | A BRIEF REVIEW ON COMMON CLOCK DISTRIBUTION ARCHI-                | 20       |

|----------------|-------------------------------------------------------------------|----------|

| 4.1            | TECTURES       Single-Path Networks       Single-Path Networks    | 39<br>39 |

| <b>4.1.1</b>   | 8                                                                 | 39<br>39 |

| 4.1.2          |                                                                   | 40       |

| 4.1.3          |                                                                   | 40       |

| 4.2            | Multiple-Path Networks                                            | 41       |

| 4.2.1          | •                                                                 | 41       |

| 4.2.2          |                                                                   | 41       |

| 4.3            | Tree + Local Mesh (TLM)                                           | 42       |

| 5              | RELATED WORKS                                                     | 45       |

| 5.1            | Combinatorial Algorithms for Fast Clock Mesh Optimization         | 45       |

| 5.1.1          | Simultaneous Mesh Buffer Placement and Sizing                     | 45       |

| 5.1.2          | 2 Mesh Reduction                                                  | 46       |

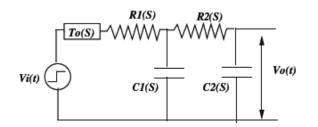

| 5.1.3          | Buffer Model                                                      | 46       |

| 5.2            | MeshWorks: An Efficient Framework for Planning, Synthesis and Op- |          |

|                | timization of Clock Mesh Networks                                 | 47       |

| 5.2.1          |                                                                   | 47       |

| 5.2.2          |                                                                   | 47       |

| 5.2.3          | .8.                                                               | 47       |

| 5.2.4          | Buffer Model                                                      | 48       |

| 6              | MESH SIZE SELECTION                                               | 49       |

| 6.1            | Definitions                                                       | 49       |

| 6.2            | Motivation                                                        | 50       |

| 6.3            | Average Stub Length                                               | 50       |

| 6.4            | Mesh Size for Minimum Wirelength                                  | 51       |

| 6.5            | Mesh Size for Minimum Capacitance                                 | 52       |

| 6.6            | Optimum Mesh Bin Density                                          | 52       |

| 6.7            | Experiments                                                       | 52       |

| 6.7.1          | 1                                                                 | 53       |

| 6.7.2          | 1 1                                                               | 53       |

| 6.7.3          | 5                                                                 | 53       |

| 6.8            | Conclusions                                                       | 54       |

|                | SKEW REDUCTION BY MESH BUFFER DISPLACEMENT                        | 57       |

| 7.1            | Elmore Delay                                                      | 57       |

| 7.1.1          |                                                                   | 57       |

| 7.2            | Single-dimension displacement optimization                        | 58       |

| 7.2.1          |                                                                   | 59       |

| 7.2.2          |                                                                   | 59       |

| 7.2.3          | 1 2 1                                                             | 60       |

| 7.2.4          | 5                                                                 | 60       |

| 7.2.5<br>7.2.6 | 5 8                                                               | 60<br>61 |

| 7.2.0<br>7.3   | 8                                                                 | 61<br>62 |

| 7.3<br>7.4     | Two-dimensional displacement optimizationExperiments              | 62<br>62 |

| /.4            |                                                                   | 02       |

| 7.4.1 | 1                                             | 62 |  |  |  |  |

|-------|-----------------------------------------------|----|--|--|--|--|

| 7.4.2 | Results                                       | 63 |  |  |  |  |

| 7.5   | Conclusion                                    | 64 |  |  |  |  |

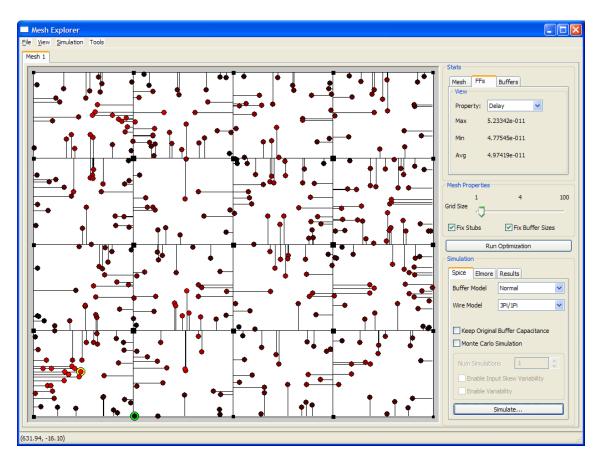

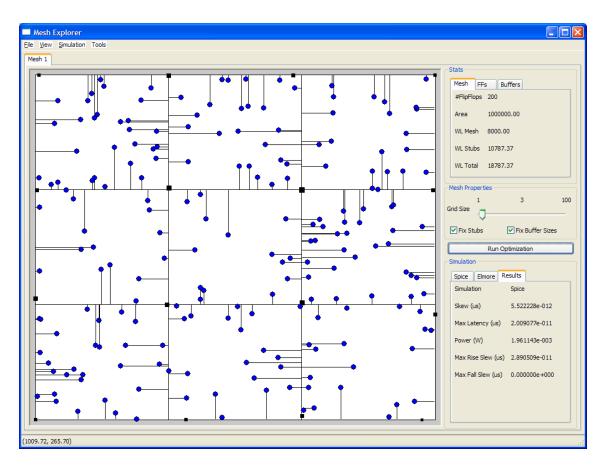

| 8 M   | IESH EXPLORER: A CLOCK MESH TOOL              | 65 |  |  |  |  |

| 8.1   | Programming Language and External Libraries   | 65 |  |  |  |  |

| 8.2   | Key Features                                  | 65 |  |  |  |  |

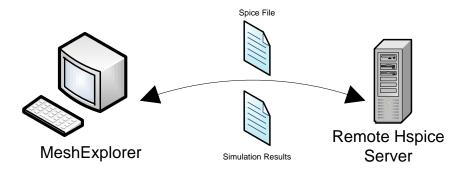

| 8.2.1 | Spice Simulation                              | 65 |  |  |  |  |

| 8.2.2 | Elmore Simulation                             | 66 |  |  |  |  |

| 8.2.3 | Sink Properties Visualization                 | 66 |  |  |  |  |

| 8.2.4 | Changing Buffer and Sink Properties           | 68 |  |  |  |  |

| 8.2.5 | Dragging Buffers                              | 68 |  |  |  |  |

| 8.2.6 | Mesh Optimization Through Buffer Displacement | 68 |  |  |  |  |

| 9 C   | ONCLUSIONS                                    | 71 |  |  |  |  |

| 9.1   |                                               | 71 |  |  |  |  |

| REFE  | REFERENCES                                    |    |  |  |  |  |

# LIST OF ABBREVIATIONS AND ACRONYMS

- GUI Graphical User Interface

- FF Flip-Flop

- FO Fanout Of

- ASIC Application Specific Integrated Circuit

- TLM Tree + Local Meshes

# LIST OF SYMBOLS

- f Femto

- $\mu$  Micron/Mean

- m Milli

- n Nano

- $\Omega$  Ohms

- p Pico

- $\sum$  Summation

- $\sigma$  Standard deviation

# LIST OF FIGURES

| The clock signal - a periodic signal that synchronizes the circuit com- |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ponents                                                                 | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Clock signal spanned over all circuit area                              | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Clock mesh is a grid wire to where clock sinks connect to               | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Timing diagram for a positive edge-triggered flipflop (JAN M. RABAEY    | ANAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| THA P. CHANDRAKASAN, 2002)                                              | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| A combinational path.                                                   | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Positive Clock Skew                                                     | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Negative Clock Skew                                                     | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Clock Jitter                                                            | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Clock sinks with different delays due to different RC                   | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Sources of skew and jitter (JAN M. RABAEY ANANTHA P. CHAN-              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DRAKASAN, 2002)                                                         | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

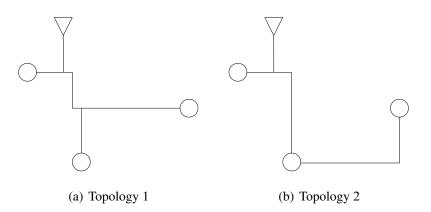

| Example of different topologies for a same set of sinks                 | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| H-Tree                                                                  | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Fishbone                                                                | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Spine Tree                                                              | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

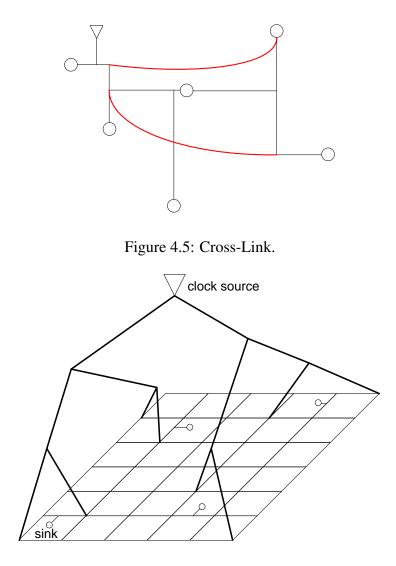

| Cross-Link                                                              | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Clock Mesh.                                                             | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

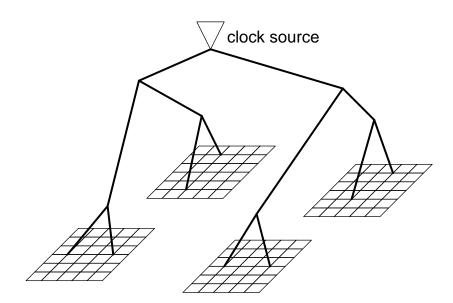

| Tree + Local Mesh (TLM)                                                 | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

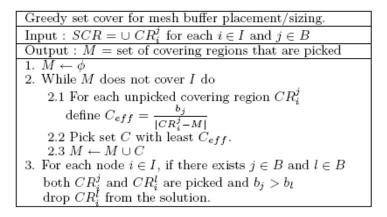

| Greedy set cover for mesh buffer placement and sizing (VENKATARA-       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MAN et al., 2006)                                                       | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

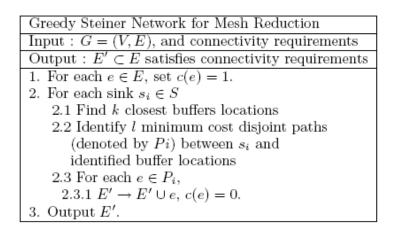

| Mesh reduction algorithm (VENKATARAMAN et al., 2006)                    | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

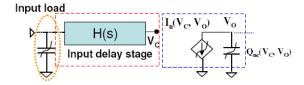

| Driver model used in (VENKATARAMAN et al., 2006)                        | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

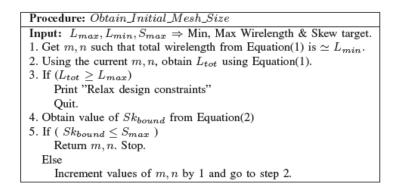

| Algorithm to find a good initial mesh size (RAJARAM; PAN, 2008).        | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Buffer model used in (RAJARAM; PAN, 2008)                               | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

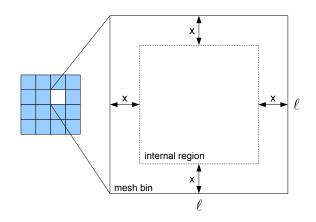

| A $4 \times 4$ Clock Mesh                                               | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

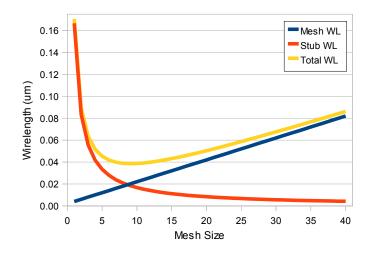

| Mesh wirelength as a function of the mesh size                          | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

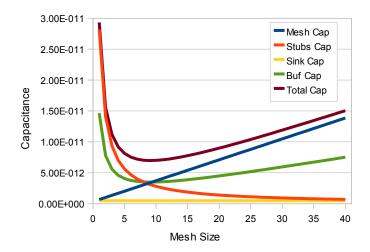

| Mesh capacitance as a function of the mesh size                         | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| An internal bin region where stubs have the same length $x$             | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| The coverage region of a buffer.                                        | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

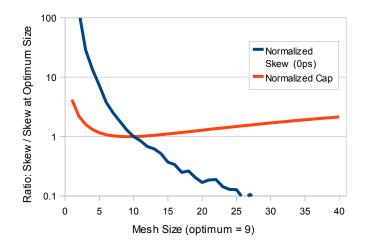

| Skew and capacitance trade-off for no input skew                        | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

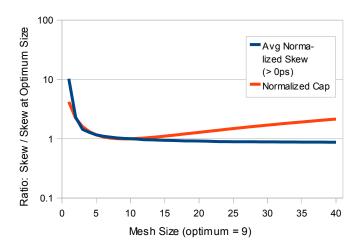

| Skew and capacitance trade-off when input skew is applied               | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                         | ponents.Clock signal spanned over all circuit area.Clock mesh is a grid wire to where clock sinks connect to.Timing diagram for a positive edge-triggered flipflop (JAN M. RABAEYTHA P. CHANDRAKASAN, 2002)A combinational path.Positive Clock SkewNegative Clock SkewClock JitterClock sinks with different delays due to different RC.Sources of skew and jitter (JAN M. RABAEY ANANTHA P. CHANDRAKASAN, 2002).Example of different topologies for a same set of sinks.H-Tree.Fishbone.Spine Tree.Clock Mesh.Clock Mesh.Tree + Local Mesh (TLM).Greedy set cover for mesh buffer placement and sizing (VENKATARA-MAN et al., 2006).Driver model used in (VENKATARAMAN et al., 2006).Algorithm to find a good initial mesh size (RAJARAM; PAN, 2008).Buffer model used in (RAJARAM; PAN, 2008).A 4 × 4 Clock MeshMesh virelength as a function of the mesh size.An internal bin region where stubs have the same length $x$ .The coverage region of a buffer.Skew and capacitance trade-off for no input skew. |

| Figure 7.1:                | A Simple RC Ciruit                                                                       | 58       |

|----------------------------|------------------------------------------------------------------------------------------|----------|

| Figure 7.2:                | Multi-step optimization algorithm.                                                       | 59       |

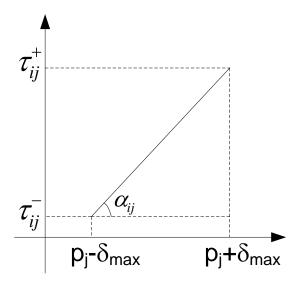

| Figure 7.3:                | The delay of sink $i$ w.r.t the buffer $j$                                               | 60       |

| Figure 7.4:                | Computation of sensitivity, $\alpha_{ij}$ , of a sink <i>i</i> w.r.t the buffer <i>j</i> | 61       |

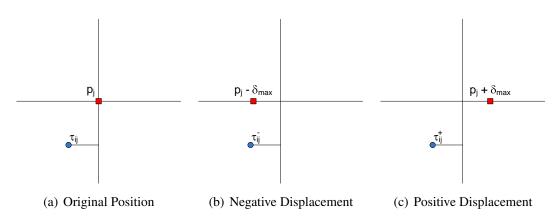

| Figure 7.5:                | Displacement direction computation.                                                      | 62       |

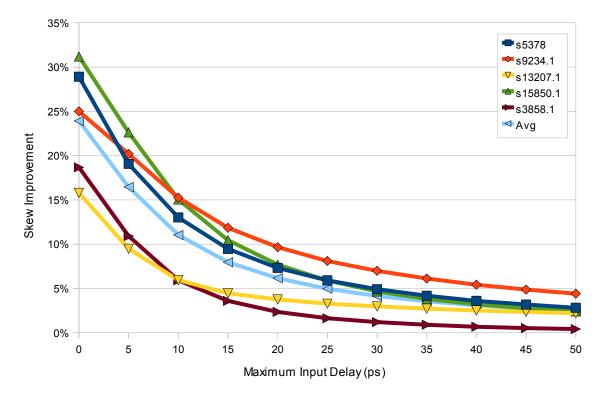

| Figure 7.6:                | ISCAS Optimization Results                                                               | 64       |

|                            |                                                                                          |          |

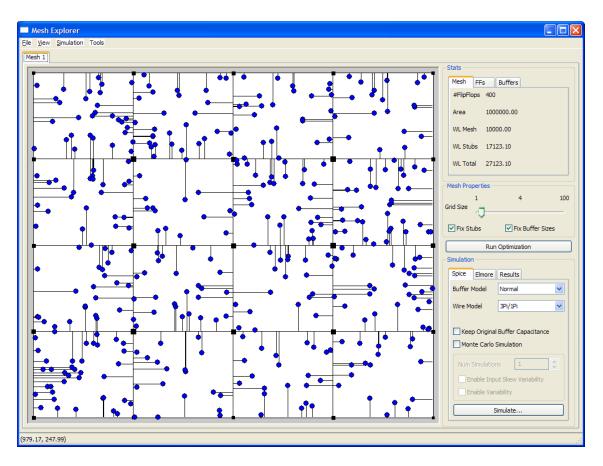

| Figure 8.1:                | Mesh Explorer Tool.                                                                      | 66       |

| Figure 8.1:<br>Figure 8.2: | Mesh Explorer Tool                                                                       | 66       |

| U                          | -                                                                                        | 66<br>67 |

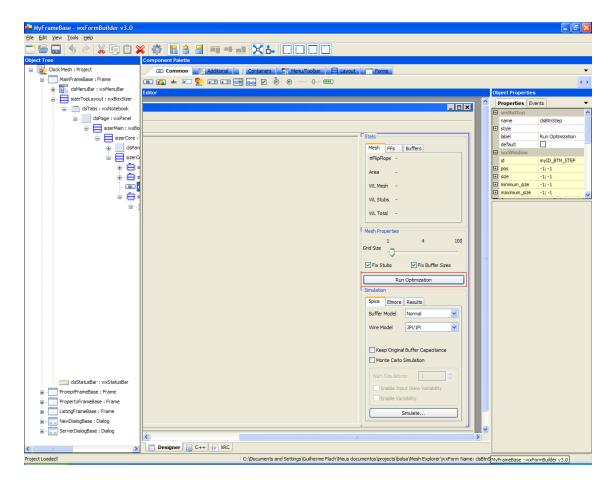

| U                          | Main Window of Mesh Explorer Being Designed Using wxForm-                                |          |

| Figure 8.2:                | Main Window of Mesh Explorer Being Designed Using wxForm-<br>Builder                     | 67       |

# LIST OF TABLES

| Table 3.1: | Sources of skew and jitter.       | 37 |

|------------|-----------------------------------|----|

|            | ISCAS Benchmarks                  |    |

|            | Buffer ProprietiesSink Properties |    |

# ABSTRACT

Clock meshes are a suitable clock network architecture for reliably distributing the clock signal under process and environmental variations. This property becomes very important in the deep sub-micron technology where variations play a main role.

The clock mesh reliability is due to redundant paths connecting clock buffers to clock sinks, so that variations affecting one path can be compensated by other paths. This comes at cost of more power consumption and wiring resources. Therefore it is clear the tradeoff between reliably distributing the clock signal (more redundancy) and the power and resource consumption.

The *clock skew* is defined as the difference in the arrival time of clock signal at clock sinks. The higher is the clock skew, the slower is the circuit. Besides slowing down the circuit operation, a high clock skew increases the probability of circuit malfunction due to variations.

In this work we focus on the clock skew problem. We first extract some useful information on how the clock wirelength and capacitance change as the mesh size changes. We present analytical formulas to find the optimum mesh size for both goals and study how the clock skew varies as we move further away from the optimum mesh size.

We also present a method for reducing the clock mesh skew by sliding buffers from the position where they are traditionally placed. This improvement comes at no increasing cost of power consumption since the buffer size and the mesh capacitance are not changed.

**Keywords:** Clock, Clock mesh, Skew, Performance, Microprocessor, Variability, Microelectronic.

## RESUMO

Malhas de relógio são arquiteturas de rede de relógio adequadas para distribuir confiavelmente o sinal de relógio na presença de variações de processo e ambientais. Tal propriedade se torna muito importante nas tecnologias submicrônicas onde variações têm um papel importante.

A confiabilidade da malha de relógio é devido aos caminhos redundantes conectando o sinal de relógio até os receptores de forma que variações afetando um caminho possam ser compensadas pelos outros caminhos. A confiabilidade vem ao custo de mais consumo de potência e fiação. Desta forma fica claro o balanceamento necessário entre distribuir confiavelmente o sinal de relógio (mais redundância) e o consumo de potência e aumento de fiação.

O *clock skew* é definido como a diferença entre os tempos de chegada do sinal de clock nos seus receptores. Quanto maior é o clock skew, mais lento o circuito precisa operar. Além de diminuir a velocidade do circuito, um valor alto de clock skew aumenta a probabilidade de o circuito não funcionar devido às variações.

Neste trabalho, nos focamos no problema de clock skew. Inicialmente extraímos informações úteis de como o comprimento da fiação e a capacitância variam a medida que o tamanho da malha varia. São apresentadas fórmulas analíticas que encontram o tamanho ótimo para ambos objetivos e é apresentado um estudo de como o clock skew varia a medida que nos afastamos do tamanho ótimo da malha de relógio.

Um método para a redução de clock skew através do deslocamento dos buffers também é apresentado. Tal melhoria no clock skew não afeta o consumo de potência já que o tamanho dos buffers e a malha não são alterados.

**Palavras-chave:** Relógio, Malha de Relógio, Skew, Performance, Microprocessador, Variabilidade, Microeletrônica.

# 1 INTRODUCTION

Imagine some stage of a milk industry where two independent robots cooperate. Their operation is synchronized by a common signal, which can be either on or off. When the signal is on, the first robot fills the bottle with fresh milk and the second one waits. When the signal is off, the first one stops filling and the second one closes the bottle. Now imagine that for some reason the second robot receives the synchronization signal earlier than the first one. In this case, the bottle is closed before the milk is completely disposed causing the system to fail.

As in our milk industry example, synchronous circuits are composed of several components, where many of them must operate synchronously so that the circuit works properly. Discrepancies in the time the synchronization signal arrives at each synchronous component may cause the circuit malfunction.

### 1.1 Clock Signal

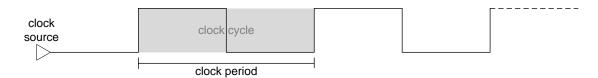

In synchronous circuits, the synchronization is performed via a periodic clock signal, as shown in Figure 1.1, which controls the operation of all synchronous components. Synchronous components are the ones that store the information processed by the circuit. The clock signal defines the moment at which data is read from and written to such components - hereafter, for short, called clock sinks or just sinks.

Figure 1.1: The clock signal - a periodic signal that synchronizes the circuit components.

The clock period - the time a clock cycle requires to be completed - defines the velocity of the circuit. The shorter the clock period is, the faster is the circuit operation. The clock period can be reduced (or the clock frequency can be increased) until some bounds are not crossed. These bounds and how they are affected by the clock signal arrival time discrepancy are discussed in the Chapter 2.

## **1.2** Clock Network

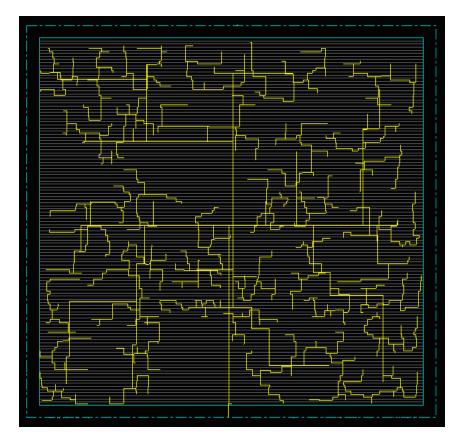

The clock signal is carried to the clock sinks throughout a clock network, which commonly spans over all the circuit area. An example of a clock network is shown in Figure 1.2. Such a huge network is more prone to fabrication process and environmental variations and it is one of the most important sources of power consumption of a digital circuit (WARNOCK et al., 2002). Tolerance to variations and power consumption are the two main issues that must be addressed in the clock network design.

Figure 1.2: Clock signal spanned over all circuit area.

Fabrication process and environmental variations affect the circuit components by changing their electrical parameters in a non-deterministic fashion. In the case of a clock network some paths may become faster and others may become slower disturbing any design-time attempt to balance the arrival times at each clock sink. The clock network must be designed so that even under variations the arrival time discrepancy is confined inside a tolerance limit. Since the variation problems worsen as the technology node shrinks, variation tolerance becomes more and more relevant in the circuit design.

Beside the problems caused by variations, the clock network is commonly the main source of power consumption in a synchronous circuit. At each clock cycle, the clock network and its sinks must be charged and discharged. Since the clock network frequently spans over all circuit area and must drive several components, no wonder it is one of the main sources of power consumption. For instance, the total clock capacitance of the Alpha microprocessor correspond to 40% of the total effective switching capacitance of the circuit (JAN M. RABAEY ANANTHA P. CHANDRAKASAN, 2002) (WARNOCK et al., 2002).

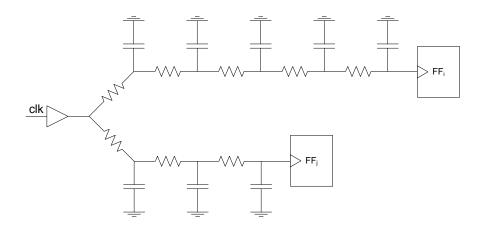

#### **1.2.1** Signal Regeneration

Any electrical signal becomes weaker as it transverses a wire. For smaller connections, the signal attenuation may be neglected. However, for a huge network like the clock network, regeneration elements must be inserted.

Although the regeneration elements - also called *buffers* - allow the signal to travel longer distances, they insert new sources of arrival time discrepancy and power consumption.

## 1.3 Clock Mesh

Some clock network architectures were developed and studied in the literature. They can be divided into two main categories w.r.t the connectivity between clock signal and clock sinks: (1) single path and (2) multiple paths.

In the first category there is only one path connecting each clock sink to the clock source while in the second one multiple paths (or redundant paths) may connect a clock sink to the clock source. Redundant paths allow variations affecting one path to be compensated by other ones. On the other hand, single path architecture consume less circuit resources. Single and multiple path architectures are described in Chapter 4.

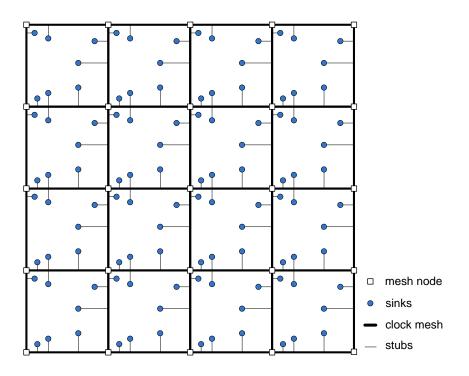

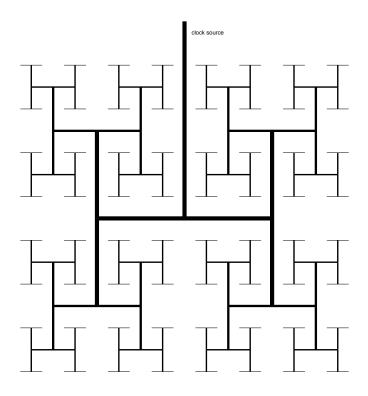

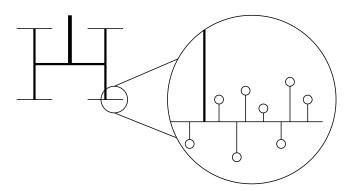

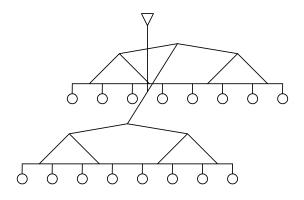

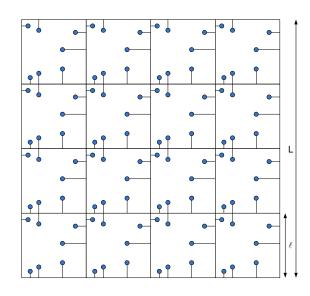

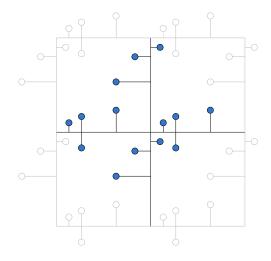

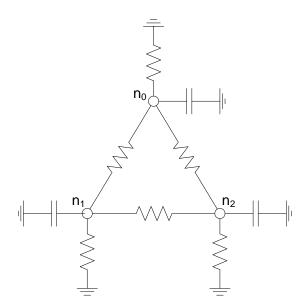

Among the redundant path architectures, *clock meshes* emerge as a feasible multiplepath solution to the variability problem for sub-micron technologies. Clock meshes are  $m + 1 \times m + 1$  wire grids formed by m + 1 horizontal and m + 1 vertical wires as shown in Figure 1.3. An  $m + 1 \times m + 1$  mesh is referred in this work as having size m.

Clock sinks connect to the clock mesh through wires called *stubs*. The clock signal is connected at multiple points of the clock mesh through a high-level clock network architecture. These points are commonly the *mesh nodes* - the intersection of a horizontal and a vertical wire.

Figure 1.3: Clock mesh is a grid wire to where clock sinks connect to.

Due to the high degree of redundancy, clock meshes have a very high tolerance to variations, which can be increased by increasing the mesh size. The tolerance to variations comes at cost of more wire and thus power consumption.

In Chapter 6 the trade-off between power consumption and variation tolerance is discussed. In Chapter 7 a method for reducing the arrival time discrepancy without increasing the power consumption is presented.

### **1.4 Motivation**

Clock meshes impose a great usage of wiring resources and power consumption, which restricted its use to products like microprocessors where the demand for performance further narrows the tolerance to variations. Several microprocessors have used clock meshes to distribute the clock signal:

- Itanium 1st Generation 2000 (TAM et al., 2000)

- 1.2GHz Alpha Microprocessor 2001 (XANTHOPOULOS et al., 2001)

- Power4 2002 (WARNOCK et al., 2002) (RESTLE et al., 2002)

- Power5 2004 (KALLA; SINHAROY; TENDLER, 2004) (CLABES et al., 2004)

- Dual-Core SPARC V9 2005 (HART et al., 2006)

- First Cell Processor 2005 (PHAM et al., 2006) (PHAM et al., 2005) (PHAM et al., 2005)

- Power6 2007 (FRIEDRICH et al., 2007) (THOMSON; RESTLE; JAMES, 2006)

In all of those circuits, clock meshes are not used as the sole solution for clock distribution. As already pointed out, the clock mesh itself relies on a high-level clock network architecture, which brings the clock signal to multiple points at mesh. And, in many cases, the sinks of the clock mesh are not directly the synchronous elements of the circuit, but the inputs of a lower-level clock network architecture. Therefore, we must consider that clock meshes do not replace other clock architecture, but they are applied together to make the circuits more robust to process and environmental variations.

However, as the variations still and will increase as the technology advances, even non-microprocessors may consider the use of clock meshes. Since, for non-microprocessor, the design life-cycle is much shorter than for microprocessors, there is a new demand for methods and algorithms, which allow the automatic clock mesh synthesis addressing the time-to-market requirements (RAJARAM; PAN, 2008). The clock mesh architecture has been gaining increasing attention in the literature in the recent years (VENKATARAMAN et al., 2006) (RAJARAM; PAN, 2008) (REDDY; WILKE; MURGAI, 2006) (CHEN et al., 2005) (YEH et al., 2006).

Gustavo Wilke's thesis (WILKE, 2008) analyzed and presented optimization methods for mesh architectures including a sliding window technique for optimizing electric simulation and a new buffer model for decreasing the mesh power consumption. To some extent, this work is an extension of Wilke's work as the analysis and methods presented herein expands the results of that work.

### **1.5** Contributions

The contributions of this work can be summarized as follow:

- A tool for aiding the development of new algorithms for mesh optimization and teaching clock meshes (Chapter 8);

- An analytical formula for finding the mesh size, which minimize the total mesh capacitance (Chapter 6);

- A study on how to define a good mesh size, which provides insights in the right mesh size for trading-off variation tolerance and power consumption (Chapter 6);

- A method for improving the tolerance to variations of clock meshes (Chapter 7) without increasing the total mesh capacitance through linear programming.

# **2 TIMING CONSTRAINTS IN SYNCHRONOUS CIRCUITS**

In this chapter, the parts that compose a synchronous circuit and its implications on the clock period, T, are presented.

## 2.1 Clock Signal

Considering a single-phase positive edge-triggered clocking style, the rising edge of the clock signal defines the end of the current clock cycle and the beginning of the next one. At a rising edge, positive edge-triggered flipflops store data currently held in their inputs. Hereafter, throughout this work, flipflop refers to a positive edge-triggered flipflop and a clock edge to a rising clock edge as well.

### 2.2 Sequential Components: FlipFlops

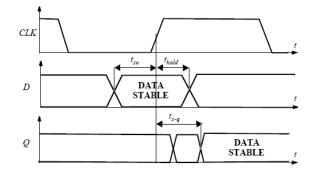

The time required for a flipflop to change its output after an occurrence of a clock edge is called *propagation time*  $(t_{pFF})$ . To be correctly stored, data at the input of a flipflop must be stable during a certain amount of time before and after a clock edge arrives. The time required before is defined as the *setup time*  $(t_{setup})$  and the time required after is defined as the *hold time*  $(t_{hold})$ . The time parameters of a flipflop are presented in the time diagram shown in Figure 2.1.

Figure 2.1: Timing diagram for a positive edge-triggered flipflop (JAN M. RABAEY ANANTHA P. CHANDRAKASAN, 2002)

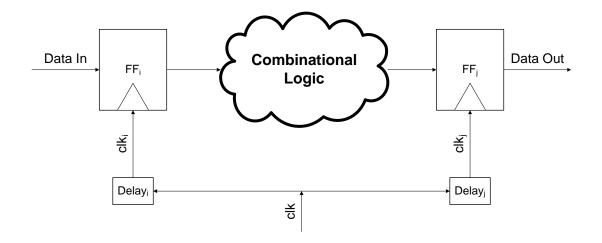

Figure 2.2: A combinational path.

### **2.3** Combinational Paths

A combinational path is composed of one input flipflop i and one output flipflop j connected through a combinational logic as shown in Figure 2.2. This is the basic structure found in synchronous circuits. A combinational path may present different delays depending on its input and output values. For timing analysis, we are interested in the minimum  $(t_{comb-min})$  and maximum  $(t_{comb-max})$  delays of the combinational path. The clock arrival time for flipflop i and j are given by  $t_{clk_i}$  and  $t_{clk_j}$  respectively.

### 2.4 Clock Signal Uncertainty

The clock signal may arrive at different times at each clock sink even though it is being generated from a common source. The first reason is that different paths with different lengths and widths present different delays. However, even when the paths are designed with the same electric characteristics, process and environmental variations tend to mismatch the paths delays.

Arrival discrepancies can be classified as static and dynamic. Statics variations are caused mainly by the circuit design and by process variations while dynamic variations are commonly effect of environmental variations. The sources of static and dynamic variations are discussed in Chapter 3.

#### 2.4.1 Clock Skew

Static variations cause the clock signal to arrive in different times at each clock sinks. The time mismatch between two clock sinks is called *clock skew*. Since clock skew is a static characteristics of the circuit, by definition, it does not change cycle-to-cycle. For two clock sink i and j, clock skew is given by Equation 2.1.

$$\delta\left(i,j\right) = t_{clk_i} - t_{clk_j} \tag{2.1}$$

#### 2.4.2 Clock Jitter

Dynamic variations may change the delay of a given node cycle-by-cycle. This discrepancy on the clock signal delay is called *clock jitter*. For a clock sink *i*, the clock jitter

for two subsequent clock cycles is given by Equation 2.2.

$$t_{jitter_i} = t_{clk_{1_i}} - t_{clk_{2_i}} \tag{2.2}$$

## 2.5 Clock Period Definition

In this section we walk through the equations that must hold if the circuit is expected to work properly. When designing a circuit, the designer must be aware of two basic timing constraints. Both define a lower bound constraint for the clock period and for the delay of the fastest combinational path.

The first lower bound states that clock period must be sufficiently large so that every combinational path processes and stores correctly its information before the next clock cycle begins. The second one states that the delay of the fastest combinational path inside a combinational path must be sufficiently large to avoid race conditions. A race condition occurs when the current data held in the combinational path is overwritten by the next one.

First we suppose an ideal scenario where neither skew nor jitter acts on the circuit. Next the clock skew and clock jitter implications on the ideal scenario are outlined. And, finally, we put all together and present the timing constraints when skew and jitter apply.

#### 2.5.1 Ideal Scenario: Neither Skew nor Jitter

Initially, suppose neither skew nor jitter affects the circuit. In this ideal case, Equation 2.3 and 2.4 must hold such that the circuit works properly.

$$T > t_{pFF} + t_{comb-max} + t_{setup} \tag{2.3}$$

$$t_{comb-min} > t_{hold} - t_{pFF} \tag{2.4}$$

#### 2.5.2 Introducing Clock Skew

In the presence of clock skew the ideal timing constraint equations should be adapted to account to the skew. The new clock period lower bound is presented in Equation 2.5 and the new minimum combinational path delay is presented in Equation 2.6.

$$T > t_{pFF} + t_{comb-max} + t_{setup} - \delta \tag{2.5}$$

$$t_{comb-min} > t_{hold} - t_{pFF} + \delta \tag{2.6}$$

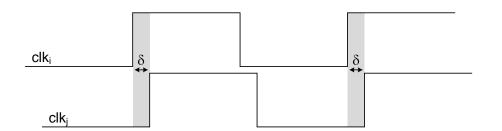

As clock skew can be positive or negative there are two possible scenarios: (1) positive clock skew ( $t_{clk_i} > t_{clk_j}$ ) and (2) negative clock skew ( $t_{clk_i} < t_{clk_j}$ ).

#### 2.5.2.1 Positive Clock Skew

A positive clock skew occurs when the clock signal arrives later at flipflop j than at flipflop i as shown in Figure 2.3. In this case, clock period can be reduced by  $\delta$  improving the circuit performance as can be noticed in Equation 2.5. On the other hand, the delay of the fastest combinational path must be slowed down by  $\delta$  as can be seen in Equation 2.6.

Figure 2.3: Positive Clock Skew

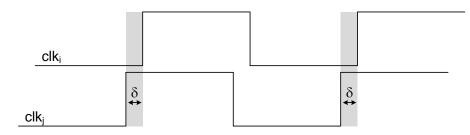

#### 2.5.2.2 Negative Clock Skew

A negative clock skew occurs when the clock signal arrives earlier at flipflop j than at flipflop i as shown in Figure 2.4. In this case, clock period must be increased by  $\delta$ harming the circuit performance as can be noticed in Equation 2.5. On the other hand, the delay of the fastest combinational can be even faster than in the ideal scenario as can be seen in Equation 2.6.

Figure 2.4: Negative Clock Skew

#### 2.5.3 Introducing Clock Jitter

In the presence of jitter in the circuit the ideal timing constraint equations should be adapted to account to the jitter. Figure 2.5 shows how the clock jitter affects the clock signal arrival time. The new clock period lower bound is presented in Equation 2.7 and the new minimum combinational path delay is presented in Equation 2.8. Notice that, differently from the clock skew, clock jitter always harms the circuit performance.

Figure 2.5: Clock Jitter

$$T > t_{pFF} + t_{comb-max} + t_{setup} + 2t_{jitter}$$

$$(2.7)$$

$$t_{comb-min} > t_{hold} - t_{pFF} + 2t_{jitter} \tag{2.8}$$

#### 2.5.4 Putting All Together

As previously presented, when defining the circuit timing constraints the designer must take into account both clock skew and clock jitter. Combining the timing constraints for clock skew and clock jitter effects, we have the final timing constraints as defined by Equation 2.9 and Equation 2.10.

$$T \ge t_{pFF} + t_{comb-max} + t_{setup} - \delta + 2t_{jitter}$$

(2.9)

$$t_{comb-min} > t_{hold} - t_{pFF} - \delta + 2t_{jitter}$$

$$(2.10)$$

As already pointed out, both skew and jitter may harm the circuit operation velocity. Although, Equation 2.9 states that a positive clock skew improve the circuit velocity, it is almost impracticable to design a circuit with only either positive clock skew. In general, we can assume that in real designs both positive and negative clock skews are present.

Also it is important to keep in mind that a high discrepancy in the clock signal arrival times, not only harms the circuit velocity, but increases the probability of failures. Therefore circuits must be designed so that the clock skew and clock jitter are small.

# **3 SOURCES OF SKEW AND JITTER**

Clock skew is intrinsic to all circuit designs. Although, in practice, it cannot be avoided, it can and should be minimized. Many reasons contribute to the different arrival times observed at clock sinks.

The most direct reason is the fact that the clock network is an RC network and such nodes with different RC present different delays. Figure 3.1 shows a simple example of clock skew due to RC. In theory, this source of skew can be eliminated by building a clock tree network in which every node presents the same RC w.r.t the driver node. However, when the network is inserted inside the circuit, the coupling capacitance may be different for each line unbalancing again the RC.

Many skew sources cannot be predicted exactly during design time. These sources are due to process and environmental variability. Process variability is the main source of clock skew, as it affects wire and transistor dimensions changing their electrical characteristics.

- Process Variability

- Wire Dimension. The balancing of the RC clock networks is performed using the nominal characteristics of the wires. However, due to process variability, wire dimensions and consequently wire resistance and capacitance differs from the expected values. This acts by unbalancing the RC clock network and potentially increasing the clock skew.

- Transistor Width. Variations in transistor width may harm the clock skew by changing the drive strength and the load capacitance of clock buffers. For

Figure 3.1: Clock sinks with different delays due to different RC.

instance, if the transistor width of a buffer is increased, it loads faster its sinks. On the other hand, if the transistor width of a sink is increased, it takes more time to be loaded.

- Transistor Length. Similar to the transistor width variation, the variation of the transistor length may increase skew as the threshold voltage of buffers is changed as well as the capacitance of sinks.

- Environmental Variability

- **Temperature.** The temperature changes the transistor and wire properties acting as a source of skew.

## 3.1 Summary of Skew and Jitter Sources

This section summarizes the sources of clock skew and clock jitter based on the definitions from Rabaey's book. (JAN M. RABAEY ANANTHA P. CHANDRAKASAN, 2002).

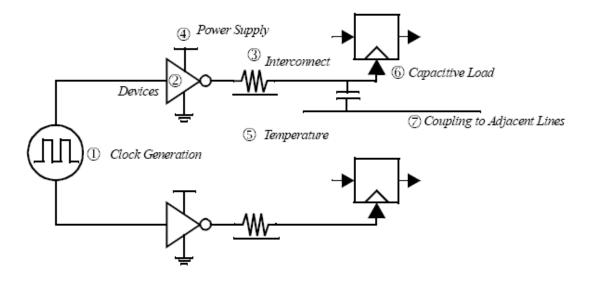

Figure 3.2: Sources of skew and jitter (JAN M. RABAEY ANANTHA P. CHAN-DRAKASAN, 2002).

| Source            | Causes     | Description                                                                                                          |

|-------------------|------------|----------------------------------------------------------------------------------------------------------------------|

| 1 - Clock genera- | Jitter     | The clock generator is an analog circuit which it-                                                                   |

| tion              |            | self causes jitter. The core of the clock generator                                                                  |

|                   |            | is a Voltage-Controlled Oscillator (VCO). This is an                                                                 |

|                   |            | analog circuit sensitive to intrinsic device noise and                                                               |

|                   |            | power supply variations.                                                                                             |

| 2 - Devices       | Skew       | Buffers are critical elements on the clock network                                                                   |

|                   |            | and, as any other device, they suffers from process                                                                  |

|                   |            | variation (threshold voltage, load capacitance). The                                                                 |

|                   |            | buffer variations affect the buffer delay, causing clock skew.                                                       |

| 3 - Interconnec-  | Skew       | Variations in vertical and lateral dimension cause the                                                               |

| tions             | SKCW       | interconnect capacitance and resistance to vary across                                                               |

|                   |            | a chip. Since this variation is static, it affects the clock                                                         |

|                   |            | skew between different paths.                                                                                        |

| 4 - Power Supply  | Jitter     | The power supply voltage is a strong function of the                                                                 |

|                   |            | switching activity. This affects the delay through                                                                   |

|                   |            | buffers as it directly affects the drive of the transis-                                                             |

|                   |            | tors.                                                                                                                |

| 5 - Temperature   | Skew       | Temperature gradients across the chip is a result of                                                                 |

|                   |            | variations in power dissipation across the die. Since                                                                |

|                   |            | the device parameters (such as threshold, mobility,                                                                  |

|                   |            | etc.) depend strongly on temperature, buffer delay for                                                               |

|                   |            | a clock distribution network along one path can vary drastically compared to another path. Although tem-             |

|                   |            | peratures varies along the time, this variation is in or-                                                            |

|                   |            | der of microseconds, which are much larger than the                                                                  |

|                   |            | clock period. Therefore, temperature is considered as                                                                |

|                   |            | a static variation, causing skew and not jitter.                                                                     |

| 6 - Capacitive    | Jitter     | The load capacitance is highly non-linear and depends                                                                |

| Load              |            | on the applied voltage. In many latches and registers                                                                |

|                   |            | this translates to the clock load being a function of                                                                |

|                   |            | the current state of the latch/register (e.g., the values                                                            |

|                   |            | stored on the internal nodes of the circuit), as well as                                                             |

|                   |            | the next state. This causes the delay through the clock                                                              |

|                   | <b>T</b> * | buffers to vary from cycle-to-cycle, causing jitter.                                                                 |

| 7 - Coupling to   | Jitter     | Any coupling between the clock wire and adjacent                                                                     |

| Adjacent Lines    |            | signal results in timing uncertainty. Since the adja-                                                                |

|                   |            | cent signal can transition in arbitrary directions and at<br>arbitrary times, the exactly coupling to the clock net- |

|                   |            | work is not fixed from cycle-to-cycle. This results in                                                               |

|                   |            | clock jitter.                                                                                                        |

|                   |            |                                                                                                                      |

# 4 A BRIEF REVIEW ON COMMON CLOCK DISTRIBU-TION ARCHITECTURES