# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

### SAMUEL NASCIMENTO PAGLIARINI

**VEasy: a Tool Suite Towards the Functional Verification Challenges**

Thesis presented in partial fulfillment of the requirements for the degree of Master of Microelectronics

Prof. Dr. Fernanda Lima Kastensmidt Advisor

### CIP - CATALOGING-IN-PUBLICATION

Pagliarini, Samuel Nascimento

VEasy: a Tool Suite Towards the Functional Verification Challenges / Samuel Nascimento Pagliarini. – Porto Alegre: PG-MICRO da UFRGS, 2011.

121 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR-RS, 2011. Advisor: Fernanda Lima Kastensmidt.

Functional verification.

Simulation.

Coverage metrics.

Automation.

Kastensmidt, Fernanda Lima.

Título.

### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Pró-Reitor de Coordenação Acadêmica: Prof. Rui Vicente Oppermann

Pró-Reitora de Pós-Graduação: Prof. Aldo Bolten Lucion Diretor do Instituto de Informática: Prof. Flávio Rech Wagner Coordenador do PGMICRO: Prof. Ricardo Augusto da Luz Reis Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

"In the days of my youth

I was told what it means to be a man

Now I've reached that age

I've tried to do all those things the best I can

No matter how I try

I find my way into the same old jam"

## **AGRADECIMENTOS**

Foram dias difíceis. Esta dissertação me tomou um tempo absurdo, mesmo tendo sido planejada do primeiro ao último item. Inicialmente o texto que eu considerava acabado tinha 90 páginas. Alguns dias depois 100. Após uma revisão foram mais 15 páginas. Cada linha parece ter sido escrita pelo menos 2, 3, 4 vezes... nunca satisfeito com o teor ou qualidade de uma frase. De certa forma, foi uma aventura. E que agora chega ao fim, finalmente.

Mas este texto não serve para que eu relate o processo, e sim para que eu torne públicos os meus agradecimentos. Inicialmente, acho que o agradecimento mais válido de todos é para minha família: meu pai, Deraldo, minha mãe, Mariângela e minha irmã, Sâmara. Talvez eles não entendam nada que aqui esteja escrito, mas pouco importa. Esta dissertação só existe através deles. Da mesma forma que a minha graduação só foi possível através deles. Portanto, obrigado a vocês.

Durante o processo de escrita e desenvolvimento desta tese ninguém se fez mais presente que minha namorada, Aline. Abusei de sua paciência. Ironizei a proximidade através da distância, sempre trabalhando. Me dediquei de uma maneira que muitos achariam desnecessária ao Mestrado. Espero que os frutos de tanto esforço um dia sejam colhidos... contigo.

Nada mais justo que também agradecer a minha orientadora, Fernanda. Ela teve ousadia em aceitar um aluno novo, em uma área diferente das suas tradicionais. Desconfio que tenha sido uma parceria proveitosa para os dois lados.

Muitos amigos também me deram forças ao longo dos últimos anos. Uns mais distantes, espalhados pelo globo, outros aqui bem próximos. Foram dias muito insanos, tudo após a graduação tem sido assim. Matando um leão por dia. Às vezes dois. Uma incerteza que irrita, amenizada pela presença dos amigos. Por fim, re-edito uma frase célebre, daquela que é uma paixão eterna: "academia do povo só tem uma". Quem sabe, sabe. E eu, caro leitor... eu sei. Em vermelho e branco.

# **CONTENTS**

| LIST                      | OF ABBREVIATIONS AND ACRONYMS            | 11                   |

|---------------------------|------------------------------------------|----------------------|

| LIST                      | OF FIGURES                               | 13                   |

| LIST                      | OF TABLES                                | 17                   |

| ABS                       | TRACT                                    | 19                   |

| RESU                      | JMO                                      | 21                   |

| 1 IN<br>1.1<br>1.2<br>1.3 | NTRODUCTION                              | 23<br>26<br>27<br>29 |

|                           | TATE OF THE ART AND CHALLENGES           | 35                   |

| 2.1                       | Coverage metrics                         | 35                   |

| 2.1.1                     | Block coverage                           | 35                   |

| 2.1.2                     | Expression coverage                      | 37                   |

| 2.1.3                     | Toggle coverage                          | 39                   |

| 2.1.4                     | Functional coverage                      | 40                   |

| 2.1.5                     | Other types of coverage metrics          | 41                   |

| 2.2                       | Stimuli generation                       | 43                   |

| 2.3                       | Checking                                 | 43                   |

| 2.4                       | Verification methodologies               | 44                   |

| 2.4.1                     | e Reuse Methodology (eRM)                | 46                   |

| 2.4.2                     | Reference Verification Methodology (RVM) | 47                   |

| 2.4.3                     | Verification Methodology Manual (VMM)    | 47                   |

| 2.4.4                     | Advanced Verification Methodology (AVM)  | 47                   |

| 2.4.5                     | Open Verification Methodology (OVM)      | 48                   |

| 2.4.6                     | Universal Verification Methodology (UVM) | 48                   |

| 2.5                       | Verification plan                        | 49                   |

| 2.5.1                     | Overview                                 | 49                   |

| 2.5.2                     | Feature list                             | 50                   |

| 2.5.3                     | Test list                                | 50                   |

| 2.5.4                     | Coverage goals                           | 51                   |

| 2.5.5                     | Other sections                           | 51                   |

| 3              | EVALUATING THE CHALLENGES :                             | 53         |

|----------------|---------------------------------------------------------|------------|

| 3.1            | Measuring simulation overhead caused by coverage        | 53         |

| 3.2            | Measuring simulation overhead caused by data generation | 56         |

| 4              | VEASY FLOW AND THE VERIFICATION PLAN                    | 59         |

| 5              | LINTING (                                               | 65         |

| 5.1            | BASE                                                    | 65         |

| <b>5.2</b>     | BCSI                                                    | 66         |

| 5.3            | DCSI                                                    | 66         |

| <b>5.4</b>     |                                                         | 67         |

| 5.5            | HCSI                                                    | 67         |

| <b>5.6</b>     | IASS                                                    | 67         |

| 5.7            | IDNF                                                    | 67         |

| <b>5.8</b>     | IDNP                                                    | 68         |

| 5.9            | LPNA                                                    | 68         |

| 5.10           | MBAS                                                    | 68         |

| 5.11           | NBCO                                                    | 69         |

| 5.12           | NOIO                                                    | 70         |

| 5.13           | RCAS                                                    | 70         |

| 5.14           | TIME                                                    | 71         |

| 5.15           | TINR                                                    | 71         |

| 5.16           | 5 VWSN                                                  | 71         |

| 5.17           | WPAS                                                    | 72         |

| 5.18           | <b>Linting Interface</b>                                | 72         |

| _              | CIMILI ATION                                            | <b>-</b> - |

| 6              |                                                         | 75<br>75   |

| 6.1            |                                                         | 75<br>70   |

| 6.2            | <b>9 1</b>                                              | 78<br>70   |

| 6.3            |                                                         | 79         |

| 6.3. 6.3.      |                                                         | 80<br>80   |

| 6.3.           |                                                         |            |

|                | E                                                       | 80         |

| 6.3.4          |                                                         | 81         |

| 6.4            | 8                                                       | 81         |

| 6.5            | 81 1                                                    | 83         |

| <b>6.6 6.7</b> | *                                                       | 84         |

| 0.7            | Validating the simulator                                | 86         |

| 7              | COVERAGE                                                | 87         |

| <b>7.1</b>     | Code coverage                                           | 87         |

| 7.1.           | 1 VEasy's block coverage algorithm                      | 87         |

| 7.1.           | 2 VEasy's expression coverage algorithm                 | 88         |

| 7.1.           |                                                         | 89         |

| 7.1.           | Experimental Results and Analysis                       | 89         |

| 7.1.           | Code coverage analysis using the GUI                    | 91         |

| 7.2            |                                                         | 92         |

| 7.2.           |                                                         | 92         |

| 7.2.           | ·                                                       | 93         |

| 8               | METHODOLOGY                                              | 95  |

|-----------------|----------------------------------------------------------|-----|

| 8.1             | Some statistics of VEasy's implementation                | 98  |

| 9               | CASE STUDY: THE PASSWORD LOCK DEVICE                     | 101 |

| 9.1             | DUT description                                          | 101 |

| 9.2             | Verification Plan                                        | 102 |

| 9.3             | Building a testcase                                      | 102 |

| 9.4             | Comparing the methodology with traditional SystemVerilog | 105 |

| 10              | CONCLUSION                                               | 109 |

| RE              | FERENCES                                                 | 113 |

| AT <sup>®</sup> | TACHMENTS                                                | 119 |

| I               | Verilog testbench used to validate the simulator         | 119 |

| II              | Web browser rendering of a verification plan file        | 120 |

| Ш               | Verilator testbench format                               | 121 |

# LIST OF ABBREVIATIONS AND ACRONYMS

AOP Aspect Oriented Programming

ASIC Application Specific Integrated Circuit

AVM Advanced Verification Methodology

BFM Bus Functional Model

CDG Coverage Directed (test) Generation

CTS Clock Tree Synthesis

DFT Design For Testability

DUT Design Under Test

DUV Design Under Verification

EDA Electronic Design Automation

eRM e Reuse Methodology

ESD Electro Static Discharge

eVC e Verification Component

FPGA Field-Programmable Gate Array

FSM Finite State Machine

FV Functional Verification

GUI Graphical User Interface

HDL Hardware Description Language

HVL Hardware Verification Language

IC Integrated Circuit

IEEE Institute of Electrical and Electronics Engineers

IP Intellectual Property

MBIST Memory Built-in Self Test

MCDC Modified Condition Decision Coverage

OO Object Oriented

OVM Open Verification Methodology

PLI Programming Language Interface

PSL Property Specification Language

RTL Register Transfer Level

RVM Reference Verification Methodology

SOP Sum of Products

STA Static Timing Analysis

URM Universal Reuse Methodology

UVM Universal Verification Methodology

VCD Value Change Dump

VMM Verification Methodology Manual

# **LIST OF FIGURES**

| Figure 1.1:  | A decreasing trend in the first silicon success rate                                                | 23 |

|--------------|-----------------------------------------------------------------------------------------------------|----|

| Figure 1.2:  | A decreasing trend in the first silicon success rate, including data from 2007                      | 24 |

| Figure 1.3:  | Causes that led to silicon failure and the respective occurrence probabilities                      | 24 |

| Figure 1.4:  | Causes that led to silicon failure and the estimated cost of a respin in different technology nodes | 25 |

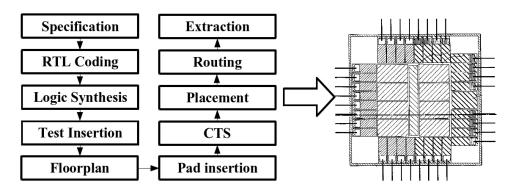

| Figure 1.5:  | Example of an ASIC implementation flow                                                              | 26 |

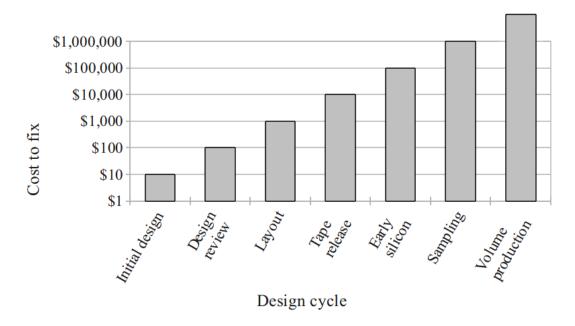

| Figure 1.6:  | Relative cost of finding an error in the various stages of the design cycle                         | 28 |

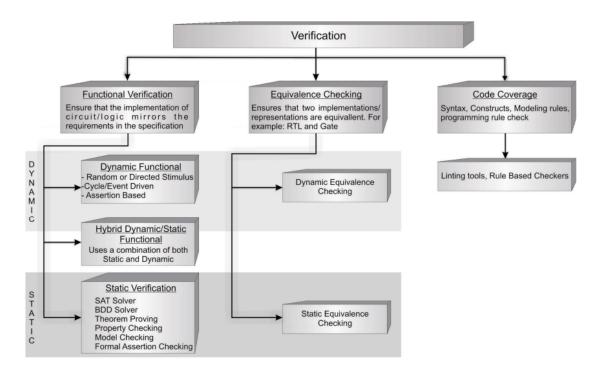

| Figure 1.7:  | Several verification methods, classified by type                                                    | 29 |

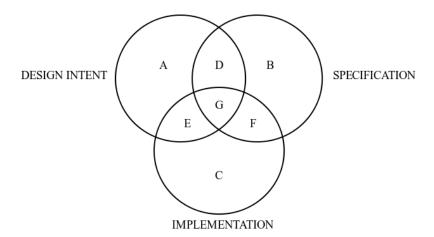

| Figure 1.8:  | The space of design behaviors                                                                       | 30 |

| Figure 1.9:  | The productivity and the verification gaps                                                          | 31 |

| Figure 1.10: | Breakdown of the effort during the development of three different                                   |    |

|              | ASICs                                                                                               | 32 |

| Figure 2.1:  | Example of Verilog code for block coverage                                                          | 36 |

| Figure 2.2:  | Example of Verilog code for expression coverage                                                     | 37 |

| Figure 2.3:  | Control flow graph of a Verilog module                                                              | 42 |

| Figure 2.4:  | All possible paths of the control flow graph from Fig 2.3                                           | 42 |

| Figure 2.5:  | FSM coverage report for states and arcs                                                             | 42 |

| Figure 2.6:  | A generic verification environment capable of performing checking                                   | 44 |

| Figure 2.7:  | Current verification practices, divided by programming language                                     | 45 |

| Figure 2.8:  | Current verification practices, divided by vendor                                                   | 45 |

| Figure 2.9:  | A timeline containing the introduction year of each of the current verification methodologies       | 46 |

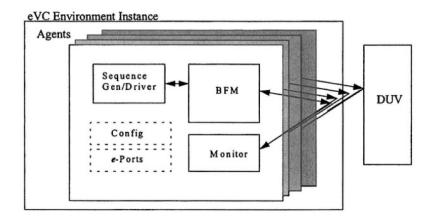

| Figure 2.10: | eVC environment instance                                                                            | 47 |

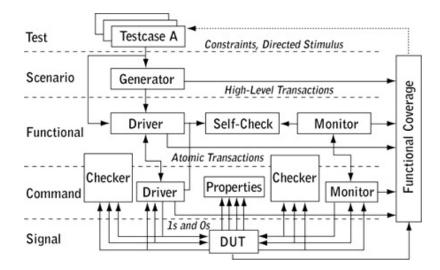

|              | Example of a VMM verification environment architecture                                              | 48 |

| _            | Simplified block diagram of the verification plan                                                   | 50 |

|              |                                                                                                     |    |

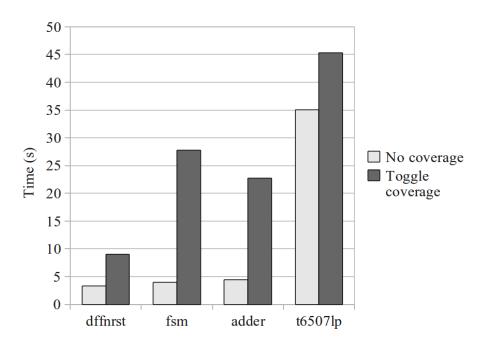

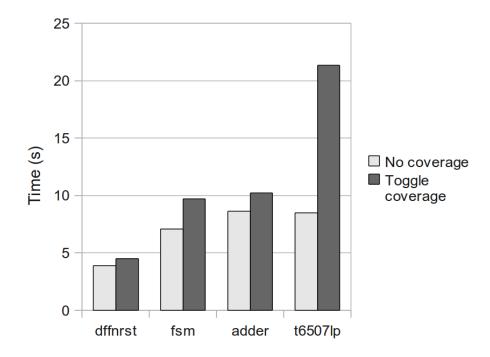

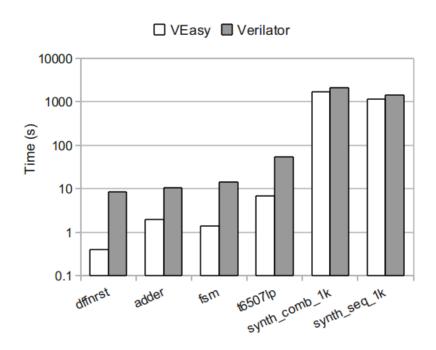

| Figure 3.1:  | Simulation overhead due to toggle coverage in simulator A                                           | 54 |

| Figure 3.2:  | Simulation overhead due to toggle coverage in simulator B                                           | 55 |

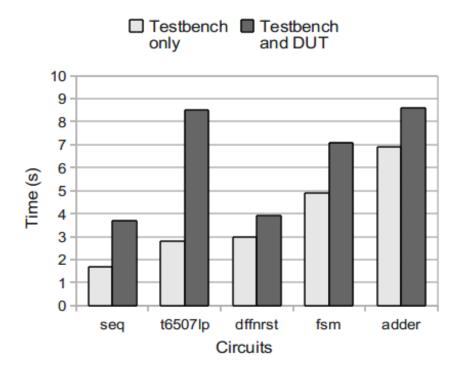

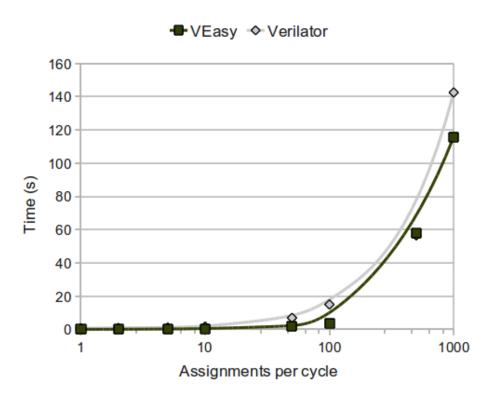

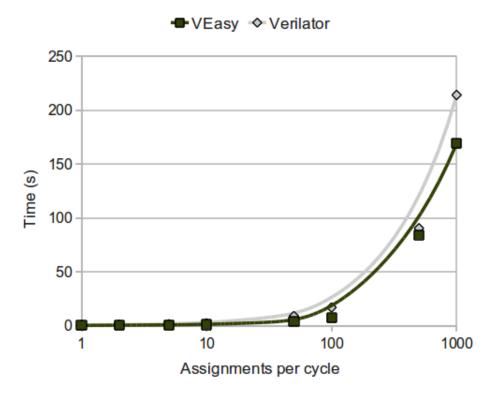

| Figure 3.3:  | Simulation overhead due to data generation                                                          | 56 |

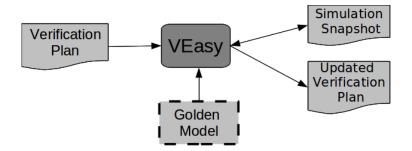

| Figure 4.1:  | VEasy assisted flow                                                                                 | 59 |

| Figure 4.2:  | VEasy simulation flow                                                                               | 60 |

| Figure 5.1:  | Example of a Verilog code that violates the BASE rule                                               | 66 |

| Figure 5.2:  | Example of a Verilog code that violates the BCSI rule            | 66  |

|--------------|------------------------------------------------------------------|-----|

| Figure 5.3:  | Example of a Verilog code that violates the DCSI rule            | 66  |

| Figure 5.4:  | Example of a Verilog code that violates the DIRE rule            | 67  |

| Figure 5.5:  | Example of a Verilog code that violates the HCSI rule            | 67  |

| Figure 5.6:  | Example of a Verilog code that violates the IASS rule            | 68  |

| Figure 5.7:  | Example of a Verilog code that violates the IDNF rule            | 68  |

| Figure 5.8:  | Example of a Verilog code that violates the IDNP rule            | 68  |

| Figure 5.9:  | Example of a Verilog code that violates the LPNA rule            | 69  |

| •            | Example of a Verilog code that violates the MBAS rule            | 69  |

| _            | Example of a Verilog code that violates the NBCO rule            | 70  |

|              | Example of a Verilog code that violates the NOIO rule            | 70  |

| •            | Example of a Verilog code that violates the RCAS rule            | 70  |

| •            | Example of a Verilog code that violates the TIME rule            | 71  |

| •            | Example of a Verilog code that violates the TINR rule            | 71  |

| _            | Example of a Verilog code that violates the VWSN rule            | 72  |

| -            | Example of a Verilog code that violates the WPAS rule            | 72  |

| _            | Linting environment GUI reporting an error                       | 73  |

| 118410 5.10. | Zinting environment corresponding an error vivivivivivivivivi    | , 5 |

| Figure 6.1:  | Pseudo-C code of the combinational logic evaluation              | 76  |

| Figure 6.2:  | Example of a Verilog code in which the combinational logic might |     |

|              | create a mismatch                                                | 76  |

| Figure 6.3:  | Pseudo-C code of the regular sequential logic evaluation         | 78  |

| Figure 6.4:  | Example of a Verilog code in which the sequential logic might be |     |

|              | misinterpreted                                                   | 78  |

| Figure 6.5:  | Reset methods available in VEasy's GUI                           | 80  |

| Figure 6.6:  | VEasy simulation results                                         | 81  |

| Figure 6.7:  | VEasy simulation results compared with Verilator                 | 82  |

| Figure 6.8:  | Scaling trends for sequential logic simulation                   | 83  |

| Figure 6.9:  | Scaling trends for combinational logic simulation                | 84  |

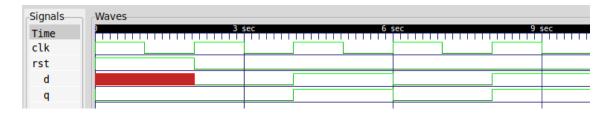

| Figure 6.10: | Initial portion of a VCD file                                    | 85  |

| Figure 6.11: | Simulation waveform equivalent to VCD of Fig. 6.10               | 85  |

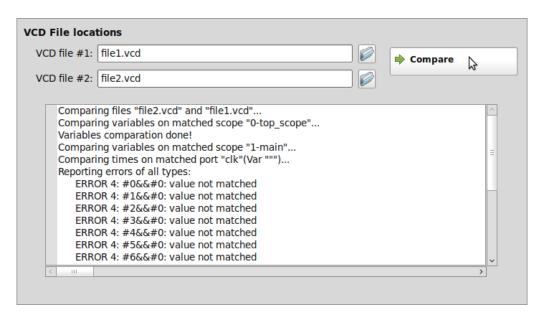

| Figure 6.12: | VCD compare environment GUI reporting errors                     | 86  |

| T. 5.4       |                                                                  | 0.0 |

| Figure 7.1:  | Block coverage collection algorithm.                             | 88  |

| Figure 7.2:  | Expression coverage collection algorithm                         | 88  |

| Figure 7.3:  | Toggle coverage collection algorithm.                            | 89  |

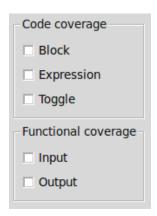

| Figure 7.4:  | Coverage metric selection GUI                                    | 91  |

| Figure 7.5:  | Code coverage analysis GUI                                       | 91  |

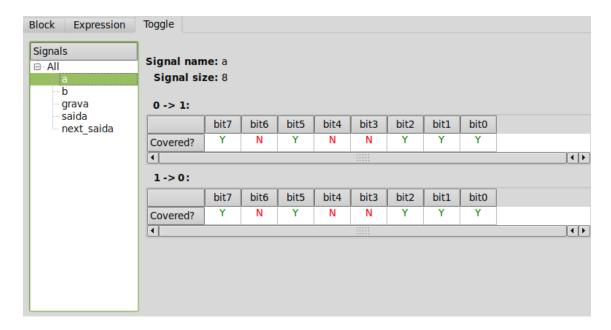

| Figure 7.6:  | Toggle coverage analysis GUI                                     | 92  |

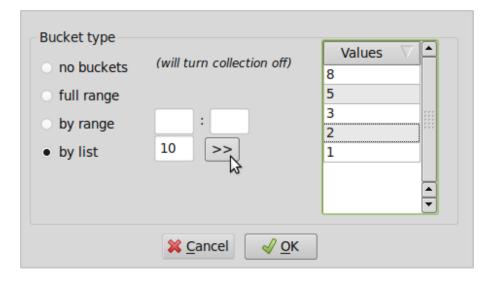

| Figure 7.7:  | Functional coverage collection algorithm                         | 93  |

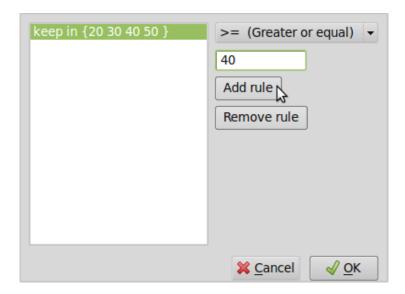

| Figure 7.8:  | Functional coverage analysis GUI                                 | 93  |

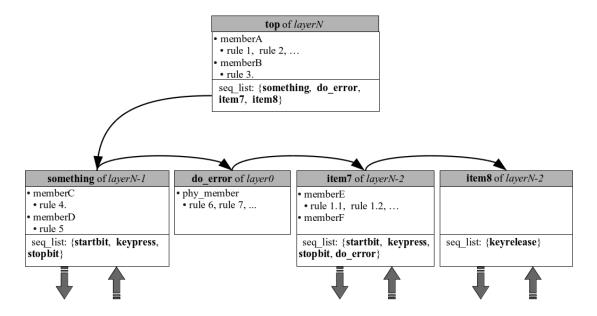

| Figure 8.1:  | Layering example                                                 | 96  |

| Figure 8.2:  | Rule editor GUI.                                                 | 97  |

| Figure 8.3:  | Execution order of VEasy's sequences.                            | 98  |

| 1 15010 0.5. | Execution order or vibusy s sequences                            | 70  |

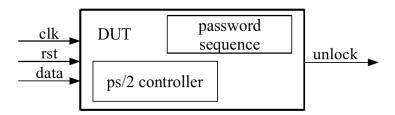

| Figure 9.1:  | DUT block diagram                                                | 101 |

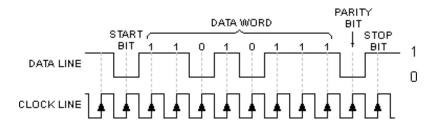

| Figure 9.2:  | Transmission of PS/2 packet                                      | 101 |

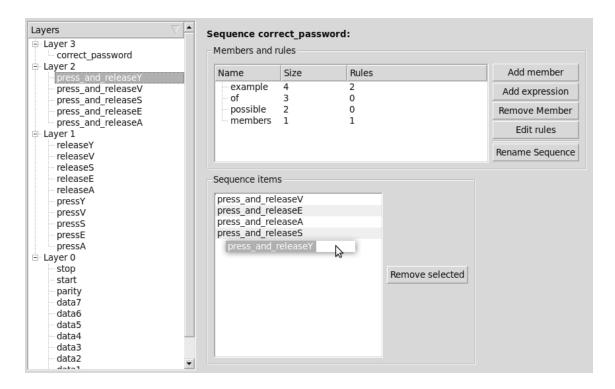

| Figure 9.3:  | VEasy's GUI being used to build a testcase                       |     |

| Figure 9.4:   | start sequence described in VEasy's format                             |  |

|---------------|------------------------------------------------------------------------|--|

| Figure 9.5:   | data0 sequence described in VEasy's format                             |  |

| Figure 9.6:   | pressV sequence described in VEasy's format                            |  |

| Figure 9.7:   | SystemVerilog code used to control the simulation time 105             |  |

| Figure 9.8:   | SystemVerilog task as a BFM                                            |  |

| Figure II.1:  | Portion of a verification plan file when rendered by a web browser 120 |  |

| Figure III.2: | Verilator testbench format                                             |  |

# **LIST OF TABLES**

| 810n (c && ( d    e))                              |

|----------------------------------------------------|

| z& ( d    e))                                      |

| $a\& (d \parallel e)$ ) and toggles of interest 39 |

| a verification plan 49                             |

| verification plan 50                               |

| fication plan 51                                   |

| als from a verification plan 51                    |

| eing analyzed 53                                   |

| sing simulator A 55                                |

| sing simulator B 55                                |

| time using commercial simulator A. 57              |

| valuation                                          |

| uation                                             |

| ation                                              |

| on                                                 |

| sing VEasy                                         |

| asured using simulator A 90                        |

| asured using simulator B 90                        |

| asured using VEasy 90                              |

| opment                                             |

| device                                             |

| enches                                             |

|                                                    |

|                                                    |

## **ABSTRACT**

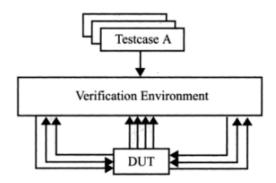

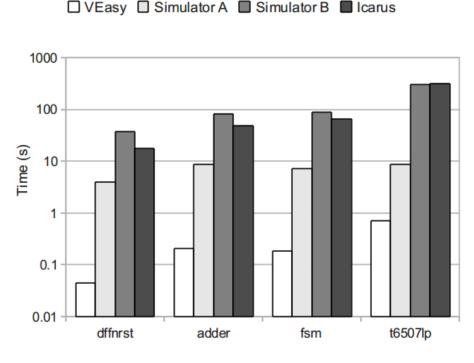

This thesis describes a tool suite, VEasy, which was developed specifically for aiding the process of Functional Verification. VEasy contains four main modules that perform linting, simulation, coverage collection/analysis and testcase generation, which are considered key challenges of the process. Each of those modules is commented in details throughout the chapters. All the modules are integrated and built on top of a Graphical User Interface. This framework enables the testcase automation methodology which is based on layers, where one is capable of creating complex test scenarios using drag-and-drop operations. Whenever possible the usage of the modules is exemplified using simple Verilog designs. The capabilities of this tool and its performance were compared with some commercial and academic functional verification tools. Finally, some conclusions are drawn, showing that the overall simulation time is considerably smaller with respect to commercial and academic simulators. The results also show that the methodology is capable of enabling a great deal of testcase automation by using the layering scheme.

**Keywords:** Functional verification, simulation, coverage metrics, automation.

## VEasy: um Conjunto de Ferramentas Direcionado aos Desafios da Verificação Funcional

## **RESUMO**

Esta dissertação descreve um conjunto de ferramentas, VEasy, o qual foi desenvolvido especificamente para auxiliar no processo de Verificação Funcional. VEasy contém quatro módulos principais, os quais realizam tarefas-chave do processo de verificação como *linting*, simulação, coleta/análise de cobertura e a geração de *testcases*. Cada módulo é comentado em detalhe ao longo dos capítulos. Todos os módulos são integrados e construídos utilizando uma Interface Gráfica. Esta interface possibilita o uso de uma metodologia de criação de *testcases* estruturados em camadas, onde é possível criar casos de teste complexos através do uso de operações do tipo *drag-and-drop*. A forma de uso dos módulos é exemplificada utilizando projetos simples escritos em Verilog. As funcionalidades da ferramenta, assim como o seu desempenho, são comparadas com algumas ferramentas comerciais e acadêmicas. Assim, algumas conclusões são apresentadas, mostrando que o tempo de simulação é consideravelmente menor quando efetuada a comparação com as ferramentas comerciais e acadêmicas. Os resultados também mostram que a metodologia é capaz de permitir um alto nível de automação no processo de criação de *testcases* através do modelo baseado em camadas.

Palavras-chave: Verificação funcional, simulação, métricas de cobertura, automação.

## 1 INTRODUCTION

The move to deep-submicron feature sizes in the latest Integrated Circuits (IC) designs has caused a paradigm shift, moving the emphasis from design to verification (BERMAN, 2005). Designers must create ICs with an excess of 50 million equivalent gates and still meet cost and time-to-market constraints. This paradigm shift has brought verification to a top position at the Electronic Design Automation (EDA) industry topics of research and development.

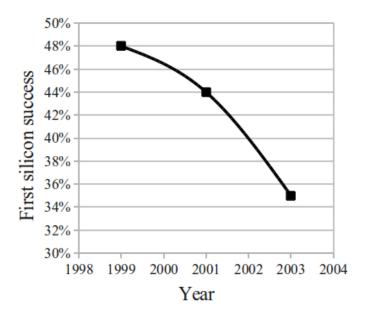

In a context where design complexity is continuously increasing (CHANG, 2007), the probability that an Integrated Circuit (IC) is going to fail is also increasing. The failure may be attributed to many sources from different types. Yet, the trend is clear: circuits are failing more and more. A 2003 study by Collett International Research (Collett International Research Inc., 2003) (FITZPATRICK; SCHUTTEN, 2003) revealed for the first time that the first silicon success rate, i.e, the rate that a given IC will function in a satisfactory manner in the first silicon spin, is dropping. Research has shown that the first silicon success rate has fallen from about 50% to 35% in a four-year time frame. This trend is illustrated in Fig. 1.1.

Figure 1.1: A decreasing trend in the first silicon success rate.

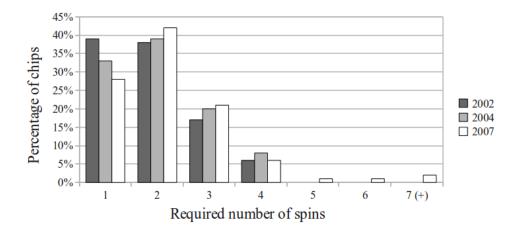

Later on a similar study was conducted by another company (Far West Research and Mentor Graphics, 2007). The trend that emerged was still the same: the first silicon success rate has fallen to 28%. The data from both studies are combined into Fig. 1.2.

Figure 1.2: A decreasing trend in the first silicon success rate, including data from 2007.

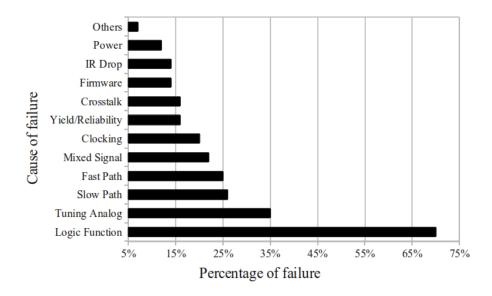

The same studies also identified the sources of errors in chip design. Chips fail for many reasons ranging from physical effects like voltage drops (IR- drop), to mixed-signal issues, power issues, and logic/functional flaws. However, logic/functional flaws are the biggest cause of flawed silicon. Of all tapeouts that required a silicon respin, the Collett International Research study shows more than 65% contained logic or functional flaws, as shown in Fig. 1.3.

Figure 1.3: Causes that led to silicon failure and the respective occurrence probabilities.

The 2007 study from Farwest showed an even higher figure: about 80% of the respins were caused by some type of logic or functional error. Since the logic/functional errors were more common than the others, the same research tried to better identify those errors. For that purpose, the errors were classified as follows:

**Design errors** About 82% of designs with respins resulting from logic/functional flaws had design errors. This means that particular corner cases simply were not covered during the verification process, and bugs remained hidden in the design flow all the way through tapeout.

**Specification errors** About 47% of designs with respins resulting from logic/functional flaws had incorrect/incomplete specifications. Moreover, 32% of designs with respins resulting from logic/functional flaws had changes in specifications.

**Reused modules and imported IP** About 14% of all chips that failed had bugs in reused components or imported IP (Intellectual Property).

All presented data shows that a silicon respin is very common. Nevertheless, the costs involved in such respins might be extremely high, easily reaching six figure amounts for the earliest technologies (TRONCI, 2006) and nine figure amounts for predicted technologies (ITRS, 2005). The additional development time and costs of a respin must be considered as well. Thus, companies that are able to curb this trend have a huge advantage over their competitors, both in terms of the ensuing reduction in engineering costs and the business advantage of being to market sooner and with high-quality products. The key to time-to-market success, for many projects, is verification.

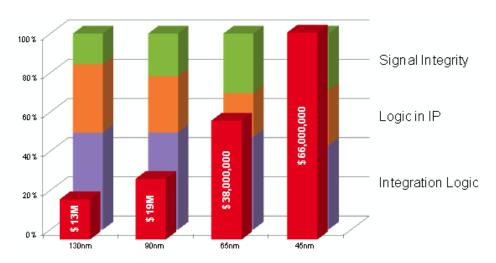

The illustration in Fig. 1.4 was obtained from a talk given by Janick Bergeron in a very recent conference (BERGERON, 2010). In such talk, the author highlights the fact that the sources of silicon failure have kept almost the same behavior throughout the technology shifts while the cost to keep such rates under control has risen exponentially. In other words, it means that verification has being doing its job but the costs of a mistake are rising with a fast-paced trend. Most of this apparent success achieved by verification comes from reuse. Although it is now possible to design chips with ten times more transistors than before, it is likely that such transistors execute the same functions that were already verified before. So, the overall picture still does not look good. This is an indication that our current verification practices are in need of changes.

Figure 1.4: Causes that led to silicon failure and the estimated cost of a respin in different technology nodes.

Regarding such context, this master thesis aims at developing a new tool suite for achieving several goals related to verification. These goals are both academia and industry related. The former type of goal is deeply explored by the easiness to create simulation scenarios using a Graphical User Interface (GUI). This interface is suitable for teaching purposes, either at undergrad or graduation levels. A deep discussion regarding the use of the developed tool for teaching purposes is given in (PAGLIARINI; KASTENSMIDT, 2011a).

The industry related type of goal is explored by introducing the simulation performance that was achieved by the tool built-in simulator. But first, before introducing such topics, and in order to better understand the need for verification and development of new verification tools, let us start by revisiting the traditional IC implementation flow. The subtleties of this flow will determine where the verification efforts should be focused.

# 1.1 IC Implementation Flow

The process of developing an IC involves several steps that must be executed towards reaching the final circuit. Depending on the technology being used and also depending on the type of circuit (digital, analog or mixed-signal), this flow may have completely different steps. Also, if considering a re-programmable device such as a Field-Programmable Gate Array (FPGA), slight changes occur on the design flow. In the context of this thesis, the flow of Fig. 1.5 will be considered, which is a generic flow for an digital Application Specific Integrated Circuit (ASIC). Such flow is based on standard cell libraries, which is a widely used methodology for developing digital circuits (WESTE; HARRIS, 2010). This type of circuit is more prone to benefit from Functional Verification (FV) since it usually has a great complexity and a high design and production cost. In other words, the cost of fixing a logical error on this type of circuit is typically higher.

Figure 1.5: Example of an ASIC implementation flow.

Each of the tasks showed in Fig. 1.5 is some form of transformation that the current design representation goes through. For instance, the project specification, typically written in some natural language, is transformed into Register Transfer Level (RTL) code. This code is usually some form of synthesizable Hardware Description Language (HDL), like Verilog (IEEE, 1995) or VHDL (IEEE, 1987). Similarly, the other tasks perform the following transformations:

Logic Synthesis The RTL description is transformed into a gate-level netlist. This task is performed by tools referred as synthesizers, like RTL Compiler (Cadence Design Systems, Inc., 2010) and Design Compiler (Synopsys, Inc., 2010). Typically some form of Static Timing Analysis (STA) is used for calculating the expected timing of the circuit. Such data are then used to perform optimizations on the circuit. The final result of the process is, if possible at all, a circuit that respects the specified timing constraints.

**Test insertion** The design is instrumented with Design For Testability (DFT) structures, like scan-chains and Memory Built-in Self Test (MBIST). These are very important for determining if the chip works properly after it has been manufactured.

- **Floorplan** In this step the circuit is organized and structured in a layout form for the first time. The power grid that will feed the circuit must be created and some routing or placement restrictions may be applied. The overall dimensions and aspect ratio of the chip must be defined as well.

- **Pad insertion** The pads of the chip must be chosen and inserted in the layout. The pads are the communication channel the circuit has with the external environment. Considerations regarding Electro Static Discharge (ESD) must be done at this step.

- **CTS** The Clock Tree Synthesis (CTS) is performed in this step. It is important for the clock signal of a chip to reach all the sequential elements at about the same time, therefore special optimizations are performed for the clock buffering and routing.

- **Placement** The standard cells are placed in this step. The overall idea is that cells that must be connected must be kept close to each other. Elements other than the proximity must be considered, such as routing congestion. After the placement is done no cell overlap should occur.

- **Routing** This step is responsible for creating the physical connections between all cells. The pads and the power rings must be connected as well.

- **Extraction** This step is responsible for extracting the resistivity and capacitance of the final layout. The extracted data is used to perform proper tuning of the previous steps as well as to perform electric simulation for sign-off purposes.

After all these transformations are done the chip is considered ready. However, such transformations are prone to errors and/or misinterpretations. Thus, some form of checking the results from these transformations must be considered. That is the role of verification: avoiding errors in the design flow. Some verification tasks are very intensive and require several resources, mostly due to the simulation nature of the verification method. This intensive behavior translates directly into cost, either due to human resources or delays in deploying a design with a tight time-to-market. However, these costs are counterbalanced because the number of errors caught late in the design cycle is diminished. Such idea is illustrated by the chart in Fig. 1.6, which contains the relative cost of finding an error in the various stages of the design cycle (GIZOPOULOS, 2006).

Obviously, different types and flavors of verification are applied in different steps of the process. Some of these types are explored in the next section.

### 1.2 Verification

The previous section focused on what is referred as the IC implementation flow. Typically, this flow is executed in parallel with another flow, the verification one. In some cases, when a company has the resources to afford it, two completely separated teams are assigned to work on each flow (BERMAN, 2005). This introduces some redundancy in the process since different views of the same project will be constructed, which actually might lead to a more efficient error detection. Ideally, the only communication channel available between these teams is the actual specification of the project.

The transformations mentioned in the previous section are not error free. Thus, every step must be properly executed and the results must be checked as well. The first transformation that the design goes through is also the most critical one, at least from a

Figure 1.6: Relative cost of finding an error in the various stages of the design cycle.

verification point of view. The process of translating a written document to a hardware description is specially susceptible to misinterpretations. This transformation in particular is explored throughout the next section. The other transformations are more mechanic and automated, which makes them less sensitive to misinterpretation errors. Obviously, regular errors due to erroneous execution of the task are still possible. To exemplify some of the possible verification tasks that are performed in a modern design flow, the image in Fig. 1.7 shows several verification methods (MOLINA; CADENAS, 2007).

The image classifies verification methods into three major types: FV, equivalence checking and code coverage. A brief explanation on each type of method is given below. The FV type, specially the dynamic flavor, is explained in details in the next section.

**Functional Verification** The most widespread method of FV is dynamic in nature. The reason it is called dynamic is because input patterns/stimuli are generated and applied over a number of clock cycles to the design, and the corresponding result is collected and compared against a reference/golden model for conformance with the specification. The static functional verification, also referred as formal verification, performs the same comparison but using some sort of mathematical proof instead of simulation.

**Equivalence checking** Given two representations of the same design, equivalence checking is capable of reasoning if they are equivalent or not. This type of comparison is widely used after logic synthesis, i.e., to compare the gate-level netlist against the RTL representation.

**Code Coverage** Code coverage indicates lines of code that were visited in a simulation. Although code coverage is reasonably easy to collect, it is an indirect metric of the overall verification progress since there is no direct mapping between lines of code and a given design functionality. Code coverage and other types of coverage are explored in details in Section 2.1.

The terms used in the literature might mislead the readers since some methods are

Figure 1.7: Several verification methods, classified by type.

shared by different techniques (e.g. assertions). This text uses the following convention: a technique is a collection of methods used in conjunction. A method is just an approach to prove a certain statement or property regarding a design. Thus, the illustration in Fig. 1.7 shows only methods, classified by type. Therefore a few words must also be said about techniques.

In general, the verification of a design has been accomplished following two principal techniques, simply referred as formal and functional verification (BERGERON, 2003). Regarding FV, one usually is referring to a set of methods that includes all of the following: random or directed stimulus, assertions, dynamic simulation and coverage. Regarding formal verification, one usually is referring to a set of methods that includes one of the following: theorem proving, property checking, formal assertion checking, etc.

To be perfectly clear, FV is mainly simulation based and it is the most common technique being used by the industry. The reason for the large adoption of FV is that, although new methodologies that benefit from formal and semi-formal methods have been proposed (COHEN et al., 2010) and sometimes adopted by the industry (ABADIR et al., 2003), these formal methods are still limited. Being so, the developed tool reported later in this text is aimed at FV.

Also, on the text that follows, the words Functional Verification (or the acronym FV) will be used referring exclusively to the Functional Verification technique, which is dynamic, i.e., the one that uses simulation. Formal methods will not be covered by this thesis. Equivalence checking will not be covered either.

### 1.3 Functional Verification

The primary goal of FV is to establish confidence that the design intent was captured correctly and preserved by the implementation (VSI Alliance, 2004) (BERGERON, 2003). The illustration of Fig. 1.8 shows how the design intent, the design specification

and the design's RTL code are related with each other to compose the space of design behaviors (PIZIALI, 2004).

Figure 1.8: The space of design behaviors.

Each circle of Fig. 1.8 represents a set of behaviors. The design intent is a set of design requirements defined by the system architect, sometimes in conjunction with a customer. It is an abstraction of what the architect expects of a certain design overall functionality. The specification is a written document that tries to exhaustively enumerate those functionalities. The specification is the guide the engineers will follow to perform the coding. The implementation is the actual intent that was coded in the RTL code. The space outside all circles represents the unintended, unspecified and unimplemented behavior. The goal of verification is to match the three circles, bringing them into coincidence.

When performing verification, i.e., matching the circles from Fig. 1.8, some very distinct results appear since very often the circles do not match. Some regions from the image are of particular interest. Region G, for instance, actually represents the best possible scenario: a certain intent was defined, specified and implemented. FV's goal is to maximize this region. Another interesting region is D, which contains a desired intent that was specified but, for some reason, it was not implemented. On the other hand, a certain functionality might be specified and implemented although it was not intended. This is what the F region represents. Clearly this type of scenario led to a waste of resources and time.

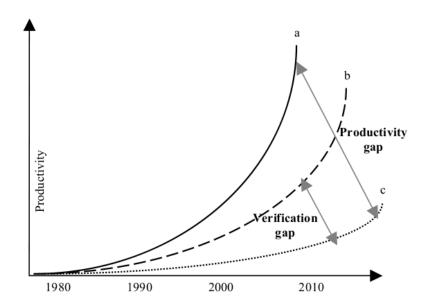

It should be clear that verification is a necessary step in the development of today's complex digital designs, either functional or not. Hardware complexity continues to grow and that obviously impacts the verification complexity. The complexity growth is leading to a even more challenging verification. In fact, it has been shown that the verification complexity theoretically rises exponentially with hardware complexity (DEMPSTER; STUART; MOSES, 2001). Both increases in complexity have created gaps (BAILEY, 2004) (DENG, 2010). Those gaps come from comparing our capabilities at designing and verifying against the actual chip capacity, as shown by the illustration of Fig. 1.9.

The verification gap is a measurement of the difference between the ability to design (dashed line) and the ability to verify (thin dashed line), which is considerably lower than the overall productivity gap. Such gap comes from the difference between the verification ability and the actual chip capacity (black line). In other words, the industry current processes are capable of filling a chip with all kinds of complex logic. Yet, it is not capable of guaranteeing that the logic works properly.

Figure 1.9: The productivity and the verification gaps.

Clearly the increase in verification complexity must be dealt properly and for that reason some new Hardware Verification Languages (HVLs) have been proposed in the last years, such as the *e* language (IEEE, 2006), the Property Specification Language (PSL) (IEEE, 2005) and the SystemVerilog language (IEEE, 2009). All those new languages were developed by the industry and later became standards of the Institute of Electrical and Electronics Engineers (IEEE). This confirms the fact that the ASIC industry already acknowledges that the verification process is extremely necessary and hard to accomplish.

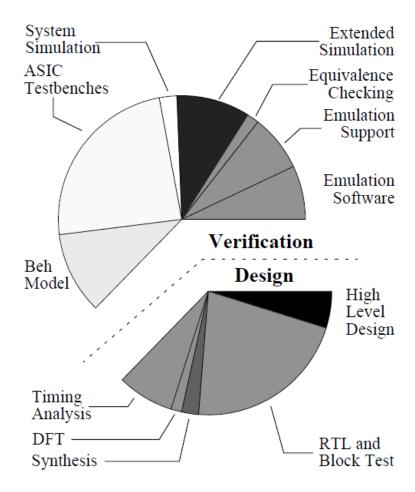

It is also known that the verification itself occupies a fair share of the design cycle time. Although there is not a clear metric to evaluate such statement, i.e., to say that verification occupies a certain definitive percentage of the design cycle, some numbers have been estimated throughout the years. In 1998 there was a reference from the industry (STEFFORA, 1998) quoting that only a few years ago verification was responsible for 20-30% of the overall design effort. Yet, by that year, verification was already acknowledged to be responsible for even 70% of the design effort for certain designs. Another study (EVANS et al., 1998) from the same year tried to breakdown and measure all the tasks executed during the design process of three different ASICs. Such breakdown is shown in Fig. 1.10. By adding up all the tasks that are related to simulation and emulation one would come up with a 60-65% figure.

Almost identical numbers have been stated by other companies throughout the years. Some examples of such statements are found in reports from Mentor (2002), Virginia Tech (2004), Denali (2005), nVidia (2006), and Jasper (2008). All the sources pointing to these reports and a in-depth discussion on the matter was done by (MARTIN, 2008). These same reports also mentioned that, although the verification occupied a large share of the design cycle, there still was a large number of silicon chips that were flawed.

One of the possible explanations for the high number of flawed silicon spins is the lack of a concise metric for the verification progress. The completeness of a design verification is defined as follows: verification is complete when every possible input scenario has been applied to the Design Under Verification (DUV)<sup>1</sup>, and every possible output signal has

<sup>&</sup>lt;sup>1</sup>In this thesis the terms DUV and Design Under Test (DUT) are used interchangeably to define the design that is currently being verified.

Figure 1.10: Breakdown of the effort during the development of three different ASICs.

been shown to have its intended value at every point in time (BORMANN et al., 2007). Measuring completeness is the actual problem that has driven verification engineers to adopt indirect metrics for measuring progress.

Those indirect metrics are referred as coverage metrics. The overall quality of the verification is obtained from coverage, either structural or functional coverage. Structural coverage is linked directly to the RTL code and therefore is also referred as code coverage. On the other hand, functional coverage is linked with the design functionalities. This is why functional coverage has become a key element in the verification process. However, the continuous increase in terms of the number of transistors per chip is resulting in a diminished validation effectiveness. Testcases being used in the simulations are more and more complex, causing simulation to get more expensive and to provide less coverage (YAN; JONES, 2010).

FV strives to cope with the complexity increase trend but some of the related challenges are overwhelming. One example of such challenge is the coverage collection and analysis. So far those challenges have been addressed with verification methodologies and EDA tools but there is a claim for more innovation and automation improvement. This is one of the goals that has driven the efforts of this thesis.

On the pages that follow, an EDA tool suite developed by the author will be described and compared. The name that such suite received is VEasy, which comes from the idea that verification should be easy. That is why VEasy's aim is to be a FV solution, including

a simulator and a Testcase<sup>2</sup>Automation interface. Therefore VEasy acts in both domains of improvement: the simulator as a simple EDA tool and the Testcase Automation solution as a verification methodology.

In the context of this thesis, verification is performed on the RTL representation of the design. In order to do that, FV often uses a combination of simple logic simulation and test cases (i.e. sequences of inputs) generated for asserting specific features of the design. Recently this approach has been enhanced by the use of constrained randomness. This element alone has aided the verification effort because it has broaden the search space of a test case while still keeping it controlled under a set of rules. This and other elements that are essential to FV will be discussed in the next chapters and sections.

The chapters that follow contain a description of the features found within the VEasy tool suite. Chapter 2, for example, describes some challenging tasks or concepts that are related to FV. Chapter 3 contains an evaluation of some of these tasks that are executed during the FV of a design, with emphasis on simulation and generation. The actual tool suite, VEasy, is presented in Chapter 4 together with the work flows and some general functionalities and features.

Later, on Chapter 5, the linting capabilities of the tool are demonstrated as well as a comprehensive list of all the available linting checks. Following this discussion, the simulation capabilities and algorithms of VEasy are described in details in Chapter 6. Chapter 7 deals with the coverage collection and analysis that is enabled by the tool, while Chapter 8 describes the methodologies that are used to create stimuli to the simulations, along with the GUI that enables some testcase automation capabilities. A case study is provided in Chapter 9 while the final chapter provides closure to the work with the final remarks and conclusions of this thesis.

<sup>&</sup>lt;sup>2</sup>In this thesis the word testcase is used when referring to a simulation scenario created within our developed tool, while the word testbench is used when referring to a traditional simulation scenario written in some form of HDL/HVL.

# 2 STATE OF THE ART AND CHALLENGES

Before introducing the developed tool, VEasy, this chapter will discuss some of the challenges related to FV. Also, the current state of the art on each of the topics will be discussed.

# 2.1 Coverage metrics

As mentioned in the previous chapter, the measurement of verification progress is given by coverage metrics (GRINWALD et al., 1998). Although most of the metrics are simple and easy to understand, the way they relate to the actual hardware functionalities is not simple nor direct. Block, expression and toggle coverage are examples of coverage metrics with such behavior. Case studies of code coverage being used to measure the verification progress are very common in the literature and date back from more than 30 years ago. One example of such studies is presented by (REDWINE S.T., 1983), where code execution coverage was applied in the software test domain in the same way that block coverage is used in hardware verification. The same particular study also conducted function, input, output and function interaction coverage.

In this thesis coverage metrics are organized in two distinct groups: structural and functional. Structural coverage is linked directly to the RTL code and therefore is also referred as code coverage. This type of coverage is the most common metric being used by the industry today and collecting it is typically a completely automated process. This is not the case for functional coverage, which requires manual intervention to be collected. Therefore it has been a hard process for some companies to shift to a coverage model based on functional metrics.

On the other hand, functional coverage is linked with the design functionalities. Being so, the verification engineer or the architect responsible for defining the coverage model must be familiarized with the design. One of VEasy's goals is to bring this type of manual intervention to a minimum. The possibilities of defining functional coverage goals in VEasy are described in Subsection 7.2.2.

The subsections that follow contain a discussion regarding some of those coverage metrics.

#### 2.1.1 Block coverage

Block coverage is the most simple of the structural metrics. A block of code is defined by one or more statements that always execute together. The principle of this metric is to measure if each block of the RTL code was simulated at least once and, because of that, it has replaced line coverage metric (in which the execution of each line of code is evaluated). Guaranteeing that each block was simulated eliminates the presence of simple errors due to unstimulated logic. Also, this type of metric is useful for detecting dead code<sup>1</sup> in the design, which might be contributing to extra logic in the final layout of the chip.

The block coverage metric is also used in the software test domain, as shown by (WONG et al., 1994), where the authors use the concept of block coverage for fault detection purposes. Even in such early studies it was already mentioned that block coverage, although an important metric, does not relate well with the actual functionality. One example is provided where two tests are examined: one that contains a decent block coverage (around 80%) and one that contains a high coverage (around 95%). Yet, the one with the high coverage is less efficient than the other when it comes to detecting faults. The authors of (BRIAND; PFAHL, 2000) also use block coverage as a metric in order to try to associate defect coverage with test coverage.

Typically, structures like *if/else* and *case* statements are considered as block starters for RTL code. For behavioral (algorithmic) codes, statements like *wait* and *sync* might be considered as well. The following code illustrated in Fig. 2.1 shows where blocks of code are defined, considering a module written in RTL Verilog.

```

module example(clk, a, b, c, d);

input clk;

input a, b;

output reg c, d;

always @(posedge clk) begin

if (a == 1'b0) begin

c <= 1'b0;

d <= 1'b0;

10

end

11

else begin

12

case (b)

13

0: begin

14

c <= 1'b0;

d <= 1'b0;

16

end

17

1: c \le 1'b1;

18

endcase

19

end

20

end

21

22

endmodule

```

Figure 2.1: Example of Verilog code for block coverage.

The code listing shown in Fig. 2.1 has five blocks of code. These blocks start on the following lines:

#### **Line 8** Due to the *always* statement.

<sup>&</sup>lt;sup>1</sup>Dead code is a portion of the code that, no matter which input or combination of inputs is considered, it will never be executed.

- **Line 9** Due to the *if* statement.

- **Line 13** Due to the *else* statement.

- **Line 15** Due to the first clause of the *case* statement.

- **Line 18** Due to the other clause of the *case* statement.

Notice that the *begin/end* pair is not necessary to start a new block of code (line 18 is an example of such situation). Also notice that the *always* statement (as in line 7) will always create a block, although this particular example has not a single assignment in such block.

### 2.1.2 Expression coverage

Expression coverage is a mechanism that factorizes logical expressions. Each factorized expression is then monitored during simulation runs. Thus, expressions are evaluated in greater detail (MICZO, 1986). Expression coverage complements block coverage because it tries to identify why a given block of code has been stimulated. The code listing from Fig. 2.2 illustrates such situation in lines 9 and 12. For instance, on line 9, a new block of code is started. The execution of this block of code may be triggered due to either of the inputs (*a* or *b*).

Expression coverage also subsumes block coverage, i.e., 100% expression coverage implies 100% block coverage. The opposite is not true. The principle of this metric is: given that the designer coded more than one situation in which a block might be executed, there was probably a different reason for each situation. One could think of the inputs a and b as two different configuration scenarios that were coded. So, it is necessary to confirm that both scenarios were simulated.

```

module example(a, b, c, d, e, f);

input a, b, c, d, e;

output reg f;

always @(*) begin

f = 1'b0;

if (a || b) begin

f = 1'b1;

10

end

11

if (c && ( d || e)) begin

12

f = 1'b1;

13

end

14

end

15

16

endmodule

```

Figure 2.2: Example of Verilog code for expression coverage.

For expressions that are more complex, such as the one in line 12, more than one scoring method might be applied. Expressions can be scored by different methods, where

one trades the amount of data to analyze against the accuracy of the results. Examples of such scoring methods are SOP (Sum of Products), control and vector scoring, which are analyzed in the following subsections. A deeper discussion on different scoring methods for logical expressions is performed in an article by (AMMANN; OFFUTT; HUANG, 2003), where several techniques based in Modified Condition Decision Coverage (MCDC) (CHILENSKI; MILLER, 1994) are compared.

## 2.1.2.1 SOP scoring

The SOP scoring mode reduces expressions to a minimum set of expression inputs that make the expression both true and false. SOP scoring checks that each input has attained both 1 and 0 state at some time during the simulation. Therefore, the expression (c && ( $d \parallel e$ )) would be scored as shown in Tab. 2.1. The dash symbol used in the table represents a *do not care* situation.

| <u>8 twert rer tire tri</u> |   |   |   |        |  |  |

|-----------------------------|---|---|---|--------|--|--|

|                             | c | d | e | result |  |  |

|                             | 1 | - | 1 | 1      |  |  |

|                             | 1 | 1 | _ | 1      |  |  |

|                             | - | 0 | 0 | 0      |  |  |

|                             | 0 | - | - | 0      |  |  |

Table 2.1: SOP scoring table for the expression (c && ( $d \parallel e$ )).

## 2.1.2.2 Control scoring

Control scoring mode checks if each input has controlled the output value of the expression at some time during the simulation. If the input changes value, then the output also changes. In a way, control scoring improves verification accuracy by applying stronger requirements in order to call an expression input covered. Control scoring is sometimes referred to as sensitized condition coverage or focused condition coverage.

Also, control scoring breaks an expression into a hierarchy of subexpressions. For example, the expression (c && (d  $\parallel$  e)) would be represented as follows:

| Table 2.2: Subexpressions hierarchy of (c && ( d    e)). |     |    |     |     |       |     |     |

|----------------------------------------------------------|-----|----|-----|-----|-------|-----|-----|

| Original expression                                      | c   | && | (   | d   | П     | e   | )   |

| First level hierarchy                                    | <1> |    | < - |     | - 2 - |     | - > |

| Second level hierarchy                                   |     |    |     | <3> |       | <4> |     |

Table 2.2: Subexpressions hierarchy of (c && (d || e)).

The resulting subexpression analysis produced two levels of hierarchy and four different expressions, numbered from 1 to 4. The resulting coverage table for the expression (c && (d || e)) using the control scoring method is illustrated in Tab. 2.3.

For instance, the and operation between <1> and <2> will be analyzed looking for three different combination of inputs. However, the combination of two zeros in both inputs is not considered due to the fact that, if you have two zero inputs and one of your inputs toggles, it would not cause a toggle in the result. Therefore, this toggle is not capable of controlling the expression. A similar analysis may be done for the or operation

| <1> | && | <2>      | result   |

|-----|----|----------|----------|

| 0   |    | 1        | 0        |

| 1   |    | 0        | 0        |

| 1   |    | 1        | 1        |

|     |    |          |          |

| <3> | Ш  | <4>      | result   |

| <3> | II | <4><br>0 | result 1 |

|     | II |          |          |

Table 2.3: Subexpressions hierarchy of (c && (d || e)) and toggles of interest.

between <3> and <4>. Instead of two zeros, the combination of inputs that is not capable of toggling the result is two ones.

### 2.1.2.3 Vector scoring

Vector scoring mode is an extension of control scoring mode. With vector scoring, each bit of a multi-bit signal is scored and reported separately. Therefore, there is a great amount of data to analyze. Since each operand is multi-bit, each operand is initially scored using a reduction table (the logical or is used for reduction). The overall expression is scored using the same scheme from control scoring, i.e, using || and && operators. Considering the same expression scored in Tab. 2.3, but assuming that c is now 3 bits wide, an additional table would be used. In this table, each bit of c must have the opportunity to control the overall expression.

### 2.1.3 Toggle coverage

Toggle coverage measures if every bit of every signal has been properly stimulated. This measurement is done by observing if a given bit has toggled from zero to one and vice-versa. In the code of Fig. 2.2 all the inputs and outputs of the module are susceptible to toggle coverage. If the module had internal signals it would be necessary to cover them as well. Even for the example of Fig. 2.2, which is quite simple, there are 6 bits that must be observed at every clock cycle. For each bit both transitions must be considered, therefore there are 12 distinct situations that must be covered and, because of that nature, it is predictable that toggle coverage is very intensive to collect. In some cases it might be interesting to collect transitions that also include X and Z values. Naturally, this type of collection makes it even more challenging to perform toggle coverage.

Although VEasy does not handle circuits at the gate level there is an important feature of the toggle coverage metric that is related to those. At gate level the design is purely structural so the use of coverage analysis is limited since expressions and blocks no longer exist. Yet, the toggle coverage metric is still able to benefit the analysis at this level.

None of the coverage metrics present so far is considered 'enough', or some sort of full solution. It is very common to see verification efforts where all of these metrics were considered. This is mostly due to the fact that the metrics are capable of examing different behaviors or facts from a circuit description. For example, achieving 100% toggle coverage, in many cases, may not lead to 100% of the other metrics, as mentioned by (WANG; TAN, 1995).

Later, on Chapter 7, some considerations about coverage collection performance will be made, specially focusing on the performance of collecting toggle and block coverage metrics.

### 2.1.4 Functional coverage

Before explaining what functional coverage is, it is important to understand why code coverage is not enough. As mentioned above, code coverage reflects how thorough the HDL code was exercised. A code coverage tool traces the code execution, usually by instrumenting or even modifying the HDL code. The set of features provided by code coverage tools usually includes line/block coverage, expression coverage, toggle coverage, etc. Some recent code coverage tools also include capabilities that automatically extract Finite State Machines (FSMs) from the design and ensure complete states and arc coverage. Nevertheless, code coverage is not enough. The reason is simple: most functional coverage requirements cannot be mapped into code structures.

For example, code coverage cannot indicate whether a particular simulation has visited all the legal combination of states in two orthogonal FSMs. Another example might be whether all the possible inputs have been tried while the DUT was in all the different internal states. Also, code coverage does not look at sequences of events, such as what else happened before, during, or after a given line of code was executed. In summary, whenever is necessary to correlate events or scenarios, code coverage fails. Yet, code coverage is a necessity since it is quite unacceptable to synthesize code that is either dead or unverified.

On the other hand, FV perceives the design from a user's (or system) point of view. Examples of questions that FV strives to answer are:

- Have you covered all of your typical scenarios?

- How about error cases? (sometimes these are as important as the correct scenarios)

- Which are the relevant corner cases?

- How to account for protocol scenarios and sequences?

The answers to all these questions comes from functional coverage, which also allows the measurement of relationships between scenarios (LACHISH et al., 2002). For instance, it might be interesting to cover that a situation was triggered from every state of a state machine. Another example: cover that a package was received when the buffer was empty and later when the buffer was full. Or even cover that a package of type A was followed by a package of type B. This characteristic elevates the discussion to specific transactions or bursts without overwhelming the verification engineer with bit vectors and/or signal names.

In a way, functional coverage might be seen as a black box testing enabler since it allows the verification to focus on the simulation scenarios from a higher level of abstraction. This level of abstraction enables natural translation from coverage results to test plan items, which will be later commented through Section 2.5. Also, functional coverage is usually divided into data-oriented and control-oriented. When performing data-oriented collection, mechanisms like covergroups of SystemVerilog are being used to sample and store values of registers or variables. On the other hand, when performing control-oriented

collection, mechanisms like assertions<sup>2</sup> are being analyzed to detect specific sequences of events that are of interest.

Also, it is important to realize that achieving a complete functional coverage is usually the primary goal of the FV. As a secondary goal then code coverage takes place. The reason is simple: there is no use to finding out if all blocks and expressions of a code have been exercised if that code does not implement all the requested functionalities. Another approach is to realize that most common, trivial or even general errors can be found when trying to reach full functional coverage. Complex errors that seem to have more of a random reason to appear, i.e., which the source is hard to identify, then might be investigated using code coverage metrics.

As functional and code coverage are complementary in nature, a tool or methodology that combines both approaches is extremely beneficial. This combined methodology will then provide a complete overview of the verification progress and a clearer correlation between the functional coverage definitions and the actual design implementation. VEasy, therefore, supports both types of coverage.

## 2.1.5 Other types of coverage metrics

This section enumerates some other types of coverage metrics that might be found in methodologies or simulators. Yet, the metrics presented so far in the latest section are more common than these.

### 2.1.5.1 Line coverage

Line or statement coverage collects information to evaluate if each line (statement) of a given code was executed. Block coverage has replaced this type of metric in some simulators and methodologies in use nowadays.

### 2.1.5.2 Path coverage

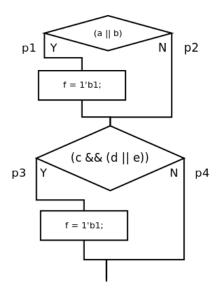

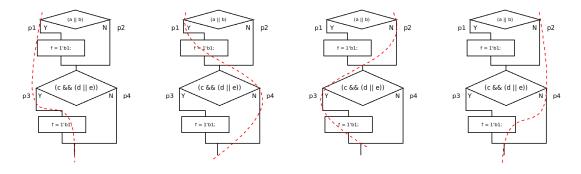

Path coverage analyzes the execution path that was stimulated in a given piece of code and it is achieved by handling the code as a decision diagram (or a control flow graph). Every possible decision must be taken at some point for the path coverage to be considered hole-free<sup>3</sup>. For example, the code of Fig. 2.2 contains four possible paths due to the two if statements.

One can see the four possible paths on Fig. 2.3. Each if statement is represented by a diamond shape and each assignment is represented by a rectangle. These possible paths are p1-p3, p1-p4, p2-p3 and p2-p4, as shown in Fig. 2.4.

### 2.1.5.3 FSM related coverage

Somewhere between code coverage and functional coverage there are coverage metrics related to FSMs. Typical metrics are based on the analysis of arcs, states and transitions. State coverage reports which states were visited, transition coverage reports what transitions occurred and arc coverage reports why each transition occurred. The illustration that follows in Fig. 2.5 contains a FSM coverage report from a commercial tool.

<sup>&</sup>lt;sup>2</sup>Assertions are checks usually embedded into the design. They are used to verify a designer's assumptions about how a design should operate. Assertions are very appropriate for verifying protocol scenarios at a design's interface. They are also used to express definitive properties about a system or circuit.

<sup>&</sup>lt;sup>3</sup>A hole is a situation of interest that was not covered, e.g., a path or a block of code. Therefore a hole-free coverage metric is one that was fully covered.

Figure 2.3: Control flow graph of a Verilog module.

Figure 2.4: All possible paths of the control flow graph from Fig 2.3.

Figure 2.5: FSM coverage report for states and arcs.

The illustration does not consider transition coverage, instead it only shows arc and state coverage. Each state is represented by a circle and each arc is represented by an arrow. If an arc (or a state) has not been excited (visited) then it is displayed in red.

## 2.2 Stimuli generation

The current practice for verification of complex designs starts with a definition of a test list, comprised by a large set of events that the verification team would like to observe during the verification process (Section 2.5 contains a discussion on those). The list of tests might be implemented using random test generators that produce a large number of tests. Producing such tests in a suitable manner is an issue. Regarding design complexity, generating a set of testbenches that will properly stimulate the circuit and provide a meaningful answer (usually through a coverage report) is not simple. It requires deep design knowledge. Also, it requires experience obtained from the verification of previous projects. Otherwise engineers could be wasting time by writing two tests that achieve the same (or near the same) coverage goals.

Recently the approach for generating stimuli data has shifted to a constraint based approach such as the ones reported by (YUAN et al., 1999) and (KITCHEN; KUEHLMANN, 2007). This allows the simulation to reach more states with a test case that once was directed towards only a single feature of the design. This element alone has aided the verification effort because it has broaden the search space of a testcase while still keeping it controlled under a set of rules.

When a constraint based approach is used, usually it requires the use of a constraint solving engine. This adds another level of complexity to FV since two constraints, perhaps written by different engineers, could create a scenario that is not of desire. In other words, it may cause the simulation of a scenario that is not of interest for the design. There is also the issue of constraint contradiction, i.e., one constraint inhibits the other. Either way, simulation cycles are wasted if the applied constraints are not correct.

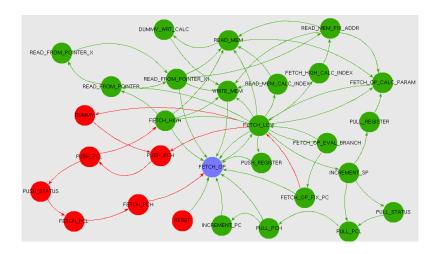

Another approach for generating stimuli data is referred as Coverage Directed (test) Generation (CDG). One example of such approach in the literature is presented by (FINE; ZIV, 2003), which is based on modeling the relationship between the coverage information and the directives to the test generator using Bayesian networks (a special type of directed graph).

# 2.3 Checking

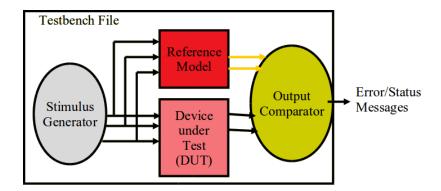

When a designer completes the coding of a design unit, a single or a few modules implementing some elementary function, he or she verifies that it works as intended. This verification is casual and usually the waveform viewer is used to visually inspect the correctness of the response (BERGERON, 2006). Regarding the efforts of a verification engineer, instead of performing a casual waveform inspection, it is advisable to create some form of self-checking environment, like the one showed in Fig. 2.6.

The output of a module might be self-checked in several different ways. Usually the checking method is chosen based tightly on the stimuli generation method. For instance, if the input is created in a transaction fashion the output might be checked in the same manner. Another simpler example might use vectors to store simulation scenarios. Let us say that, for each set of inputs sent to the design, the correct response will also be known since the same set is submitted to the checker. So, a large vector is used to store both the inputs and the expected responses of the simulation.

In general, one is interested in checking both data and timing correctness from a design. One very common practice to check the flow of data in a design is to use a score-board technique with a reference model. A scoreboard is a temporary location for holding

Figure 2.6: A generic verification environment capable of performing checking.

information that a checker will require (WILE; GOSS; ROESNER, 2005). The reference model dynamically produces the expected responses which are compared against the data already stored in the scoreboard. Once the simulation finished, if the scoreboard is not empty then something went wrong. For checking timing properties, it is more common to rely on some sort of assertion language, like the ones defined in the *e* language, SystemVerilog or PSL.

Checking is a complex subject since it is very design specific. There is no technique that is suitable for all types of designs. The verification engineer (or the verification environment architect) is responsible for choosing a method that fits well for some actual given design.

## 2.4 Verification methodologies

As explained by (IMAN; JOSHI, 2004), the focus on FV has consisted of a multi faceted approach where improvements in verification productivity were made possible through either:

- New verification methodologies, better suited for the verification of complex systems.

- Reusable verification components.

- HVLs to facilitate the new verification paradigms.

This section will discuss some of the verification methodologies that are in use as of today, as well as some of the associated HVLs of such methodologies. In the last few years different verification methodologies have been used by verification teams. The need for a verification methodology is clear nowadays: conforming to a set of standards allows the reuse of certain aspects of verification, thus diminishing the overall effort. The next subsections will detail some of the recent verification methodologies.

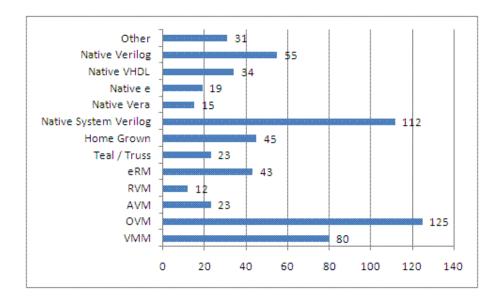

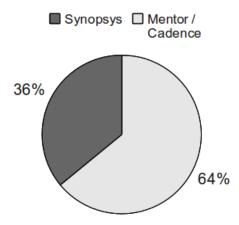

Before introducing each methodology and discussing its features, it is also important to assess which methodologies are currently most used. A few market researches have addressed this subject, such as (GRIES, 2009) and (Gary Smith EDA - GSEDA, 2009). The results of such researches is summarizes in Fig. 2.7 and Fig. 2.8, respectively.

The first research that was conducted was organized by a verification expert. He tried to answer the question of which verification solution is more widely used. Results show that a fair amount of the respondents (the horizontal axis of the image) still do not use

Figure 2.7: Current verification practices, divided by programming language.

any type of methodology, therefore performing verification using the native forms of the HVLs or homegrown solutions. These respondents were placed in the upper portion of the image. The use of languages that are not truly HVLs, like Verilog and VHDL, can also be seen in Fig. 2.7.