# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

### LEANDRO MATEUS GIACOMINI ROCHA

# Energy-Efficient Recurrent Neural Network Hardware Architecture for Heart Rate Estimation Based on Photoplethysmography

Advisor: Prof. Dr. Sergio Bampi

Porto Alegre November 2020

# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas

Coordenador do PGMICRO: Prof. Tiago Roberto Balen

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

# CIP - Catalogação na Publicação

```

Giacomini Rocha, Leandro Mateus

Energy-Efficient Recurrent Neural Network Hardware

Architecture for Heart Rate Estimation Based on

Photoplethysmography / Leandro Mateus Giacomini Rocha.

-- 2020.

159 f.

Orientador: Sergio Bampi.

Tese (Doutorado) -- Universidade Federal do Rio

Grande do Sul, Instituto de Informática, Programa de

Pós-Graduação em Microeletrônica, Porto Alegre, BR-RS,

2020.

1. Neural Networks. 2. VLSI implementation. 3.

Heart Rate estimation. 4. Photoplethysmography. 5. Low

Power. I. Bampi, Sergio, orient. II. Título.

```

| "If I have seen farther than others,               |

|----------------------------------------------------|

| it is because I stood on the shoulders of giants." |

| — SIR ISAAC NEWTON                                 |

#### **ACKNOWLEDGEMENTS**

First and foremost, I would like to thank my tutor Prof. Sergio Bampi. He has believed in me since I was in my last graduation semester. Professor Sergio has been an inspiration to me for all his achievements and his will to help us rise and shine in our personal and professional lives. I appreciate his patience and guidance during the entire development of this thesis.

Second, this Ph.D. would never be possible would the permanent support of my dear Maiquidieli Dal Berto, the love of my life, my best friend, and the best companion I could ever have. As a Ph.D. herself, she always understood the emotional roller coaster that is a Ph.D. thesis with all the anxiety, frustration, and celebration inherent to this process. Her unwavering support helped me go through tough days, especially during my internship in Belgium when we were apart. I could never find a more loving, caring, and perfect person who makes me be a better person every day, and I will always love to the moon and back.

During my Ph.D., I made a lot of friends, which I profoundly care about whose friendship I will always foster for the rest of my life. Particularly, I must thank Guilherme Paim and Eduardo da Costa, two wonderful people who are constantly seeking more research areas that can explore. Their help was quintessential during this thesis, especially with all the late nights and the never-ending barbecues.

I cannot express how grateful I am for all my colleagues in Laboratory 215, which always believed in the teamwork principle. They were always there for fruitful discussions and sharing a cup of coffee. In particular, I would like to thank Brunno Abreu, Gustavo Santana, Thomas Fontanari, Ana Mativi, Mateus Grellert, Dieison Silveira, Leonardo Soares, Eduarda Monteiro. For sure, you create a research environment that encourages students to explore the challenges of academic research.

I must also thank my best friends João de Carli and Fernanda Gaboardi, whose friendship is unpaired. The bond created in all these years is something that really makes me happy. Sharing fears, thoughts, and joys were essential to keep sanity in this crazy world.

I must also thank all those people who helped in every way during my stay in Leuven. Particularly, I would like to thank Dwaipayan Biswas for his support during my internship at IMEC. He not only helped me to adapt to the city but also shared insightful ideas for developing this work. I would also like to thank Prof. Marian Verhelst for all

the fruitful meetings and her help with university matters.

This work was only possible because my family has always supported me, providing love, affection, and everything else I ever needed. Special thanks to my father Ivan Rocha and my mother, Marilise Giacomini Rocha, for always fostering in me the desire for big dreams.

Finally, thank you CAPES, CNPq, IFRS, and every funding agency that supported my studies. I will put all my efforts into proving myself worthy of all your investments, aiming to improve and expand the Brazilian scientific community.

#### **ABSTRACT**

The increasing power density and the pervasive use of compute-intensive and powerhungry applications demand energy-efficient CMOS design. The quest for energy-efficient systems particularly concerns in wearable devices for health monitoring as they must be under non-stop operation with limited energy source available on miniaturized batteries. There is an ever-growing interest in employing neural network-based applications for data processing on edge devices. Neural networks have complex structures in their pure software or hardware implementations, or in a combination of both approaches. They require millions of data fetches and arithmetic operations that are very energy demanding, and merely reducing the data size of inputs and parameters to meet power constraints might not be the optimal strategy due to significant impact on output error. Hence, this work proposes a framework for arithmetic circuit generation, enabling an architectural exploration that seeks to maximize as much as possible the energy efficiency. As a case study, this thesis also proposes a jointly optimized software-hardware approach to implement a neural network-based heart rate estimation application from photoplethysmogram signals. This approach combines binarization and quantization techniques to reduce computation requirements, making the model more suitable for hardware implementation. A custom hardware architecture is proposed for this application to achieve real-time operation with maximum energy efficiency. The stream-based architecture minimizes the system latency adopting a full pipeline implementation exploring the application requirements. This architecture was validated on both FPGA and ASIC platforms to ensure its feasibility on embedded devices.

**Keywords:** Neural networks. VLSI design. low power CMOS. hardware accelerator. heart rate estimation. PPG.

#### **RESUMO**

O aumento da densidade de potência e do uso pervasivo de aplicações com alto custo em esforço computacional e em dissipação de potência exigem eficiência energética no projeto CMOS. A busca por sistemas eficientes energeticamente é particularmente crítica em dispositivos vestíveis para monitoramento de sinais vitais uma vez que estes devem operar ininterruptamente mesmo com uma fonte de energia limitada disponível nas baterias miniaturizadas. Há um interesse crescente no emprego de aplicações baseadas em redes neurais para o processamento de dados em dispositivos embarcados. Redes neurais possuem estruturas inerentemente complexas para implementação, seja em software, hardware ou em uma combinação estreita de ambos. Tais redes requerem milhões de operações aritméticas e acessos à memória que demandam um gasto de energia elevado, e simplesmente reduzir a largura de representação dos parâmetros e dados de entrada para respeitar as restrições de dissipação de energia pode não ser a melhor estratégia devido ao impacto no erro percebido no resultado da aplicação. Assim, esse trabalho propõe um framework para geração de circuitos aritméticos, permitindo uma exploração arquitetura para buscar a máxima eficiência energética. Como estudo de caso, essa tese também propõe uma abordagem de otimização conjunta de hardware e software para implemetar um aplicação para estimação de frequência cardíaca a partir de sinais de fotopletismografia baseada em uma implementação de redes neurais. Essa abordagem combina técnicas de binarização e quantização para reduzir os requisitos de processamento, transformando o modelo em uma implementação mais adequada para a execução em hardware. Uma arquitetura de hardware customizada é proposta para esta aplicação para operação em tempo real com máxima eficiência energética. Esta arquitetura baseada em fluxo de dados minimiza a latência do sistema ao adotar uma implementação com *pipeline* em todos os estágios, explorando os requisitos da aplicação. Esta arquitetura foi validada em plataformas FPGA e ASIC para garantir sua viabilidade em sistemas embarcados.

**Palavras-chave:** Neural networks. VLSI design. low power CMOS. hardware accelerator. heart rate estimation. PPG.

# LIST OF FIGURES

| Figure 2.1 Artificial intelligence subareas division                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Figure 2.2 Example of an artificial neural network and artificial neuron                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |

| Figure 2.3 Evolution of machine learning implementation flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |

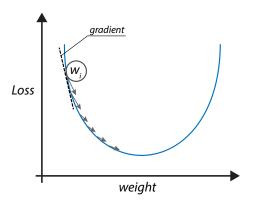

| Figure 2.4 Weight update using the gradient descent approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |

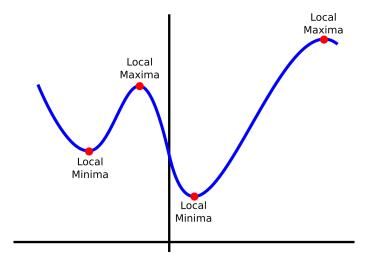

| Figure 2.5 Multiple local minima and maxima points in a loss function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                          |

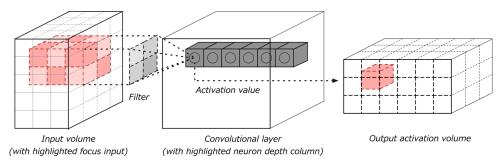

| Figure 2.6 Example a $3 \times 3$ 2-D convolution over a single input channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |

| Figure 2.7 View of a 2D convolutional layer with multiple input channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |

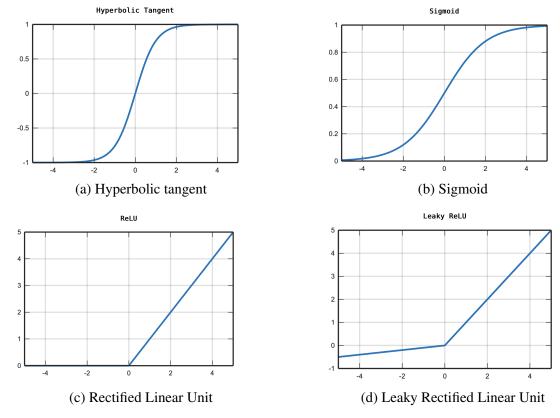

| Figure 2.8 Non-Linear Activation Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          |

| Figure 2.9 Multiple pooling algorithms for a $2 \times 2$ analysis window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          |

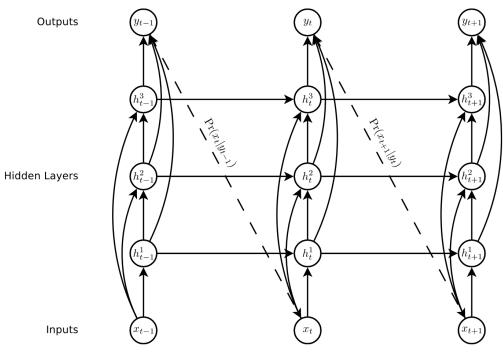

| Figure 2.10 Deep recurrent neural network example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                          |

| Figure 2.11 Internal LSTM unit implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                          |

| Figure 3.1 Baseline DNN hardware accelerator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |

| Figure 3.2 Overview of data reuse topologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |

| Figure 3.3 Energy cost of data movement at different levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                          |

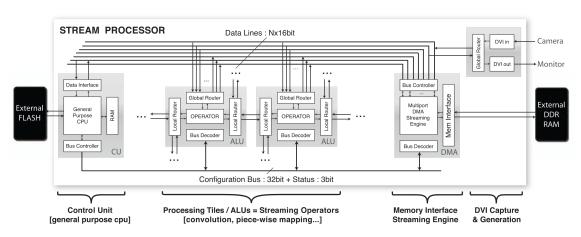

| Figure 3.4 ConvNet Stream Processor architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                          |

| Figure 3.5 Row Stationary dataflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

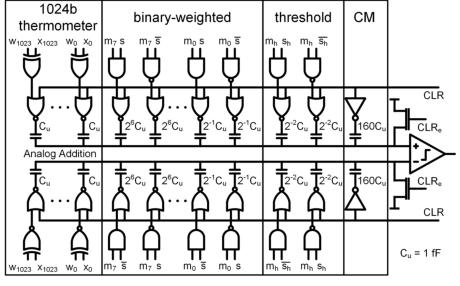

| Figure 3.6 Switched capacitor-based neuron                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          |

| Figure 3.7 PIM Module on the BRein Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 59                                                       |

| E' 41.00 ( C 1') 1 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | (2                                                       |

| Figure 4.1 Structure of a <i>n</i> -bit ripple carry adder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          |

| Figure 4.2 Structure of a fixed-group size carry-select adder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |

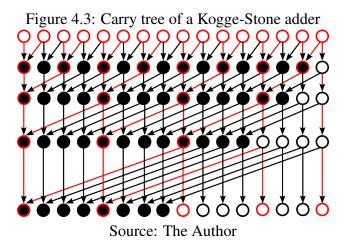

| Figure 4.3 Carry tree of a Kogge-Stone adder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |

| Figure 4.4 Carry tree of a Brent-Kung adder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                          |

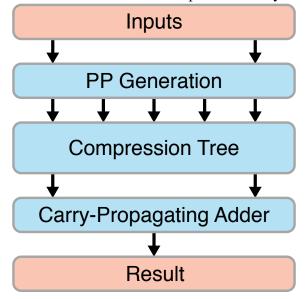

| Figure 4.5 General architecture for parallel binary multipliers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                          |

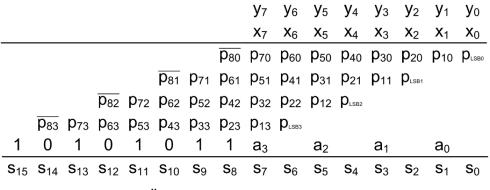

| Figure 4.6 Modified-Booth multiplier with sign extension and LSBs pre-calculation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

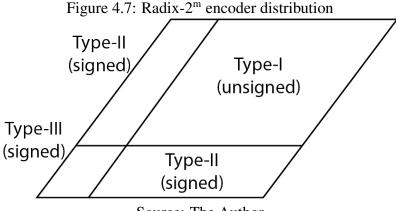

| Figure 4.7 Radix-2 <sup>m</sup> encoder distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          |

| Figure 4.8 Type-I and II encoders on Radix-4 multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          |

| Figure 4.9 Type-III encoder on Radix-4 multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                          |

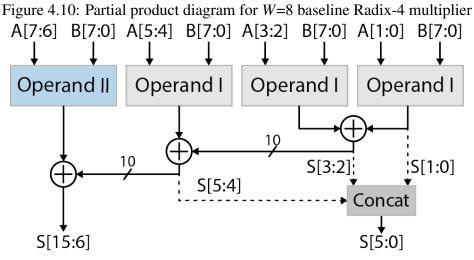

| Figure 4.10 Partial product diagram for W=8 baseline Radix-4 multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12                                                       |

| Eleven A.1.1. Intermed atmentions of W. O. andry A. an around I. blook                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

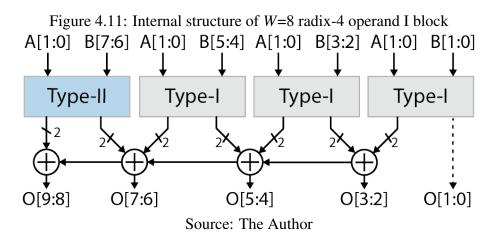

| Figure 4.11 Internal structure of W=8 radix-4 operand I block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 73                                                       |

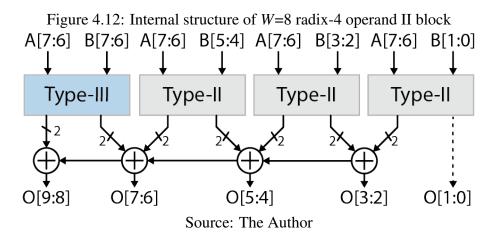

| Figure 4.12 Internal structure of W=8 radix-4 operand II block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 73                                                       |

| Figure 4.12 Internal structure of <i>W</i> =8 radix-4 operand II block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 73<br>73<br>74                                           |

| Figure 4.12 Internal structure of $W$ =8 radix-4 operand II block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 73<br>73<br>74<br>76                                     |

| Figure 4.12 Internal structure of $W$ =8 radix-4 operand II block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 73<br>74<br>76<br>77                                     |

| Figure 4.12 Internal structure of $W$ =8 radix-4 operand II block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 73<br>74<br>76<br>77                                     |

| Figure 4.12 Internal structure of $W$ =8 radix-4 operand II block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 73<br>74<br>76<br>77<br>78                               |

| Figure 4.12 Internal structure of $W$ =8 radix-4 operand II block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 73<br>74<br>76<br>77<br>78<br>78                         |

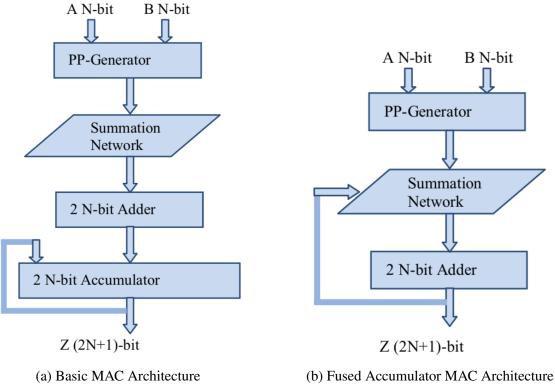

| Figure 4.12 Internal structure of $W$ =8 radix-4 operand II block  Figure 4.13 Partial products layout for the Baugh-Wooley algorithm  Figure 4.14 $8 \times 8$ multiplier with a Wallace compression tree  Figure 4.15 $8 \times 8$ Dadda multiplier reduction tree  Figure 4.16 Adder compressors variants  Figure 4.17 Multiple 8-2 adder compressor structures  Figure 4.18 Sum of multiple 8-bit inputs  Figure 4.19 Multiply-Accumulate Hardware Architecture                                                                                                                                                                                                                                                                                                                               | 73<br>74<br>76<br>77<br>78<br>78<br>79                   |

| Figure 4.12 Internal structure of $W$ =8 radix-4 operand II block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 73<br>74<br>76<br>77<br>78<br>78<br>79                   |

| Figure 4.12 Internal structure of <i>W</i> =8 radix-4 operand II block.  Figure 4.13 Partial products layout for the Baugh-Wooley algorithm.  Figure 4.14 8 × 8 multiplier with a Wallace compression tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 73<br>74<br>76<br>77<br>78<br>78<br>79<br>80             |

| Figure 4.12 Internal structure of <i>W</i> =8 radix-4 operand II block.  Figure 4.13 Partial products layout for the Baugh-Wooley algorithm.  Figure 4.14 8 × 8 multiplier with a Wallace compression tree.  Figure 4.15 8 × 8 Dadda multiplier reduction tree.  Figure 4.16 Adder compressors variants.  Figure 4.17 Multiple 8-2 adder compressor structures.  Figure 4.18 Sum of multiple 8-bit inputs.  Figure 4.19 Multiply-Accumulate Hardware Architecture.  Figure 4.20 Multiple computation phases on CNN-optimized MAC.  Figure 5.1 Circuit generation flow of the RTLGen.                                                                                                                                                                                                              | 73<br>74<br>76<br>77<br>78<br>78<br>79<br>80<br>81       |

| Figure 4.12 Internal structure of <i>W</i> =8 radix-4 operand II block.  Figure 4.13 Partial products layout for the Baugh-Wooley algorithm.  Figure 4.14 8 × 8 multiplier with a Wallace compression tree.  Figure 4.15 8 × 8 Dadda multiplier reduction tree.  Figure 4.16 Adder compressors variants.  Figure 4.17 Multiple 8-2 adder compressor structures.  Figure 4.18 Sum of multiple 8-bit inputs.  Figure 4.19 Multiply-Accumulate Hardware Architecture.  Figure 4.20 Multiple computation phases on CNN-optimized MAC.  Figure 5.1 Circuit generation flow of the RTLGen.  Figure 5.2 Back-end framework architecture.                                                                                                                                                                 | 73<br>74<br>76<br>77<br>78<br>79<br>80<br>81             |

| Figure 4.12 Internal structure of <i>W</i> =8 radix-4 operand II block.  Figure 4.13 Partial products layout for the Baugh-Wooley algorithm.  Figure 4.14 8 × 8 multiplier with a Wallace compression tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 73<br>74<br>76<br>77<br>78<br>79<br>80<br>81             |

| Figure 4.12 Internal structure of <i>W</i> =8 radix-4 operand II block.  Figure 4.13 Partial products layout for the Baugh-Wooley algorithm.  Figure 4.14 8 × 8 multiplier with a Wallace compression tree.  Figure 4.15 8 × 8 Dadda multiplier reduction tree.  Figure 4.16 Adder compressors variants.  Figure 4.17 Multiple 8-2 adder compressor structures.  Figure 4.18 Sum of multiple 8-bit inputs.  Figure 4.19 Multiply-Accumulate Hardware Architecture.  Figure 4.20 Multiple computation phases on CNN-optimized MAC.  Figure 5.1 Circuit generation flow of the RTLGen.  Figure 5.2 Back-end framework architecture.  Figure 5.3 Weight-aligned bit-hash for signal management.  Figure 5.4 Synthesis and simulation flow.                                                           | 73<br>74<br>76<br>77<br>78<br>79<br>81<br>83<br>84<br>87 |

| Figure 4.12 Internal structure of <i>W</i> =8 radix-4 operand II block.  Figure 4.13 Partial products layout for the Baugh-Wooley algorithm.  Figure 4.14 8 × 8 multiplier with a Wallace compression tree.  Figure 4.15 8 × 8 Dadda multiplier reduction tree.  Figure 4.16 Adder compressors variants.  Figure 4.17 Multiple 8-2 adder compressor structures.  Figure 4.18 Sum of multiple 8-bit inputs.  Figure 4.19 Multiply-Accumulate Hardware Architecture.  Figure 4.20 Multiple computation phases on CNN-optimized MAC.  Figure 5.1 Circuit generation flow of the RTLGen.  Figure 5.2 Back-end framework architecture.  Figure 5.3 Weight-aligned bit-hash for signal management.  Figure 5.4 Synthesis and simulation flow.  Figure 5.5 Weight-aligned partial products without RCAs. | 73<br>74<br>76<br>77<br>78<br>79<br>81<br>83<br>84<br>90 |

| Figure 4.12 Internal structure of <i>W</i> =8 radix-4 operand II block.  Figure 4.13 Partial products layout for the Baugh-Wooley algorithm.  Figure 4.14 8 × 8 multiplier with a Wallace compression tree.  Figure 4.15 8 × 8 Dadda multiplier reduction tree.  Figure 4.16 Adder compressors variants.  Figure 4.17 Multiple 8-2 adder compressor structures.  Figure 4.18 Sum of multiple 8-bit inputs.  Figure 4.19 Multiply-Accumulate Hardware Architecture.  Figure 4.20 Multiple computation phases on CNN-optimized MAC.  Figure 5.1 Circuit generation flow of the RTLGen.  Figure 5.2 Back-end framework architecture.  Figure 5.3 Weight-aligned bit-hash for signal management.  Figure 5.4 Synthesis and simulation flow.                                                           | 73<br>74<br>76<br>77<br>78<br>79<br>81<br>83<br>84<br>90 |

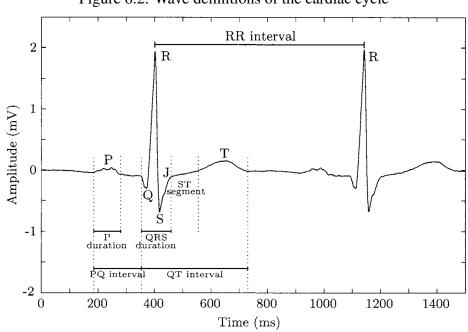

| Figure 6.2  | Wave definitions of the cardiac cycle                             | 102 |

|-------------|-------------------------------------------------------------------|-----|

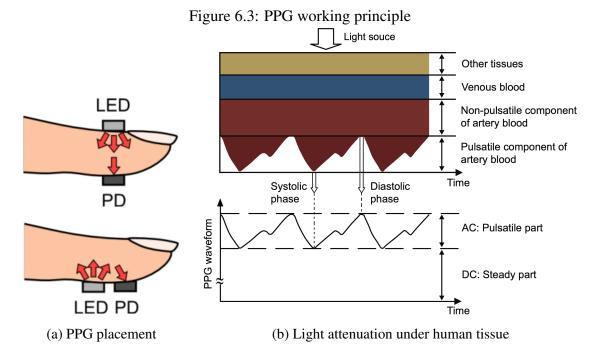

| Figure 6.3  | PPG working principle                                             | 103 |

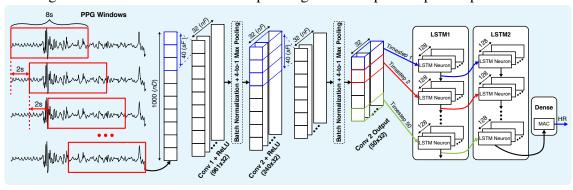

| Figure 6.4  | CorNET architecture operating on 1-D input samples to predict HR. | 107 |

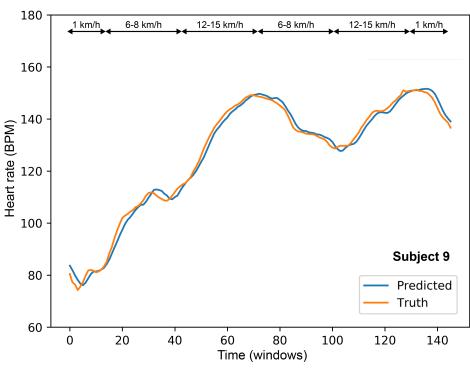

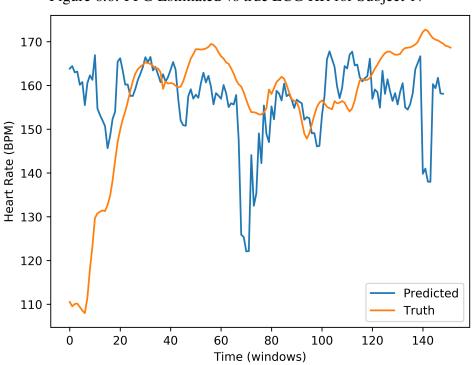

| Figure 6.5  | PPG Estimated vs true ECG HR for Subject 9                        | 112 |

| Figure 6.6  | PPG Estimated vs true ECG HR for Subject 17                       | 112 |

|             | bCorNET hardware accelerator architecture                         |     |

| Figure 7.2  | CNN1 layer architecture                                           | 119 |

| Figure 7.3  | Binarizer architecture                                            | 121 |

|             | Binary max-pooling unit                                           |     |

|             | Transposition buffer architecture                                 |     |

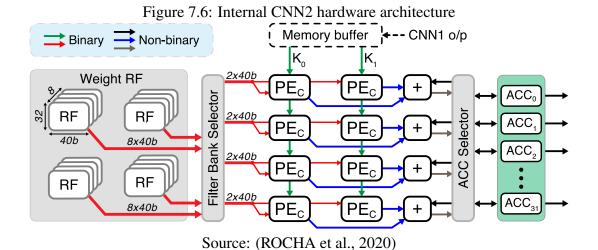

| Figure 7.6  | Internal CNN2 hardware architecture                               | 124 |

| Figure 7.7  | The internal architecture of a PE <sub>C</sub>                    | 126 |

| Figure 7.8  | CNN2 execution sequence diagram                                   | 127 |

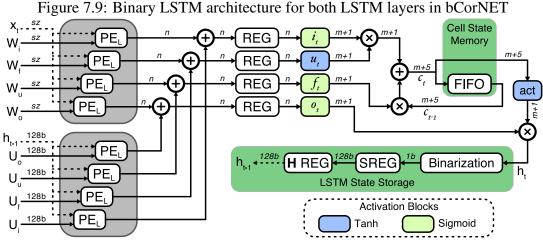

| Figure 7.9  | Binary LSTM architecture for both LSTM layers in bCorNET          | 128 |

| Figure 7.10 | Internal architecture of a PE <sub>L</sub>                        | 129 |

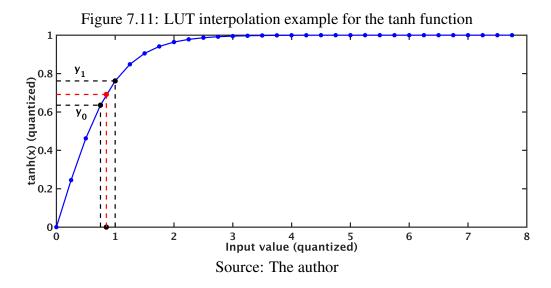

| Figure 7.11 | LUT interpolation example for the tanh function                   | 131 |

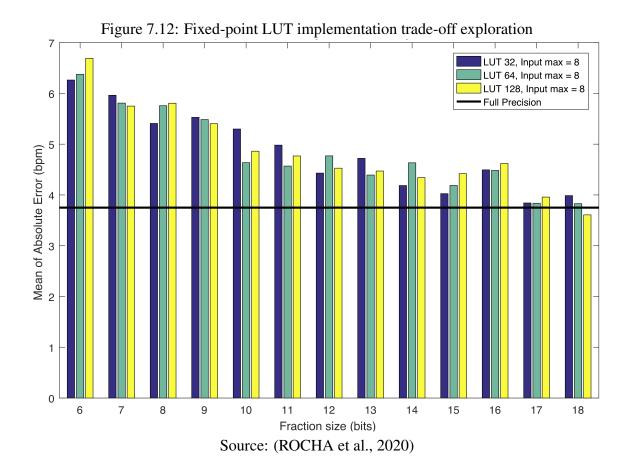

| Figure 7.12 | 2 Fixed-point LUT implementation trade-off exploration            | 132 |

| Figure 7.13 | 3 Lookup table architecture for tanh function                     | 132 |

| Figure 7.14 | 4 Quantized dense layer architecture                              | 133 |

| Figure 7.15 | 5 Overall architecture timing sequence                            | 134 |

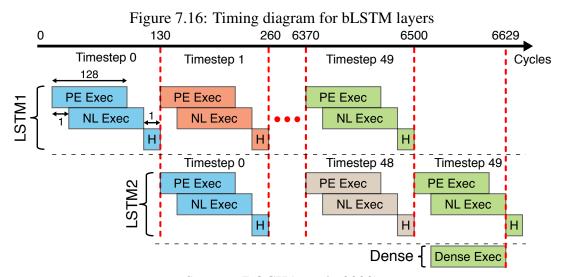

| Figure 7.16 | 5 Timing diagram for bLSTM layers                                 | 135 |

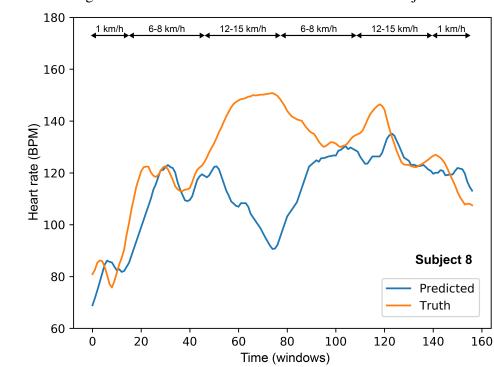

| Figure 7.17 | 7 PPG Estimated vs true ECG HR for Subject 23                     | 138 |

| Figure 7.18 | PPG Estimated vs true ECG HR for Subject 8                        | 138 |

# LIST OF TABLES

| Table 2.1 | Shape parameters on a CNN layer                                | 37   |

|-----------|----------------------------------------------------------------|------|

| Table 3.1 | Summary of Optimization Techniques and their Applications      | 61   |

| Table 5.1 | Circuit Speed, Area and Power Dissipation Comparison @ Maximum |      |

| Frequ     | uency and Worst-case PVT conditions                            | 92   |

|           | Synthesis QoR Comparison at same frequency of operation.       |      |

| Table 5.3 | Circuit Area and Power Dissipation Comparison at Maximum Speed | 98   |

| Table 6.1 | IEEE SPC dataset overview                                      | 105  |

| Table 6.2 | Complexity Evaluation of CorNET                                | 108  |

| Table 6.3 | Performance evaluation of HR estimation algorithms and CorNET  | .111 |

| Table 7.1 | Resource allocation analysis on CNN2 architecture              | .125 |

|           | Binary CorNET Evaluation                                       |      |

| Table 7.3 | FPGA Implementation results                                    | 139  |

|           | ASIC Implementation results                                    |      |

|           |                                                                |      |

# LIST OF ABBREVIATIONS AND ACRONYMS

ASIC Application-Specific Integrated Circuits

ANN Artificial Neural Network

AV Atrioventricular node

BPTT Backpropagation Through Time

BN Batch Normalization Layer

bCNN Binary CNN

bCorNET Binary CorNET

bLSTM Binary LSTM

BLAS Basic Linear Algebra Subprograms

BRAM Block RAM

CGEN Carry Generator Module

CLA Carry Look-ahead Adder

CPA Carry-propagating Adder

CPU Central Processing Unit

CMOS Complementary Metal-Oxide-Semiconductor

CEC Constant Error Carousel

CNN Convolutional Neural Networks

DNN Deep Neural Networks

DL Dense Layer

DUT Design Under Test

DVFAS Dynamic voltage-frequency-ccuracy Scaling

ECG Electrocardiogram

FPGA Field Programmable Gate Array

FA Full Adder

GRU Gated Recurrent Unit

GOPS Giga-operations per second

GPU Graphic Processing Unit

HR Heart Rate

HLS High-level Synthesis

HOG Histogram of Oriented Gradients

IFM Input Feature Map

LSB Least Significant Bit

LOSO Leave-one-subject-out strategy

LOWO Leave-one-window-out strategy

LED Light-emitting Diode

LSTM Long short-term memory

LUT Lookup Table

ML Machine Learning

MAE Mean Absolute Error

MSE Mean Squared Error

MSB Most Significant Bit

MA Motion Artifacts

MLP Multi-Layer Perceptrons

MAC Multiply-and-accumulate

NFU Neural Functional Unit

NN Neural Networks

NL Non-linear

OCR Optical Character Recognition

OFM Output Feature Map

PD Photodetector

PPG Photoplethysmography

PLE Physically-Aware Layout Estimation

PE Processing Element

PIM Processing-in-Memory

QoR Quality of Results

ReLU Rectified Linear Unit

RNN Recurrent Neural Network

RF Register File

RCA Ripple Carry Adder

RMSProp Root Mean Square Propagation

SPC Signal Processing Cup

SNR Signal-to-noise ratio

SIMD Single Instruction, Multiple Data

SIMT Single Instruction, Multiple Thread

SA Sinoatrial node

SRAM Static Random Access Memory

SDF Standard Delay Format

SDAE Standard Deviation of the Absolute Error

SGD Stochastic Gradient Descent

STE Straight-through Estimator

SUT Subject Under Test

SAIF Switching Activity Interchange Format

SL System Latency

TCF Toggle Count Format

UVM Universal Verification Methodology

VCD Value Change Dump

VALU Vector Arithmetic and Logic Unit

# CONTENTS

| 1 INTRODUCTION                                            |     |

|-----------------------------------------------------------|-----|

| 1.1 Problem formulation                                   |     |

| 1.2 Thesis claim and objectives                           |     |

| 1.3 Thesis Organization                                   |     |

| 2 OVERVIEW OF DEEP LEARNING                               |     |

| 2.1 Deep Learning Algorithms                              |     |

| 2.2 Supervised Learning                                   |     |

| 2.2.1 Loss Function                                       |     |

| 2.2.2 Backpropagation Algorithm                           |     |

| 2.2.3 Optimization algorithms                             |     |

| 2.3 Feed-forward Networks                                 |     |

| 2.3.1 Convolutional Neural Networks                       |     |

| 2.3.2 Activation Layer                                    |     |

| 2.3.3 Pooling Layer                                       |     |

| 2.3.4 Batch Normalization Layer                           |     |

| 2.4 Recurrent Neural Networks                             |     |

| 2.4.1 Long-Short Term Memory                              |     |

| 2.5 Training frameworks                                   |     |

| 2.6 Chapter Summary                                       | .40 |

| TEMS                                                      | 47  |

| 3.1 Exploiting network structure                          |     |

| 3.2 Exploiting network reliability                        |     |

| 3.3 Exploiting network sparsity                           |     |

| 3.4 Computational Platforms                               |     |

| 3.4.1 Central Processing Unit (CPU)                       |     |

| 3.4.2 Graphic Processing Unit (GPU)                       |     |

| 3.4.3 Hardware Accelerators                               |     |

| 3.5 Chapter Summary                                       |     |

| 4 ARITHMETIC KERNELS ON NEURAL NETWORKS                   |     |

| 4.1 Two-operand Binary Adders                             | .62 |

| 4.1.1 Ripple Carry Adder (RCA)                            | 63  |

| 4.1.2 Carry Select Adder                                  | 63  |

| 4.1.3 Carry Look-Ahead Adder                              | 64  |

| 4.1.3.1 Kogge-Stone Adder                                 | 66  |

| 4.1.3.2 Brent-Kung Adder                                  | .67 |

| 4.2 Parallel Binary Multipliers                           | .68 |

| 4.2.1 Partial Product Generation Algorithms               |     |

| 4.2.1.1 Booth Multiplier                                  |     |

| 4.2.1.2 Radix-2 <sup>m</sup> multiplier                   |     |

| 4.2.1.3 Baugh-Wooley Multiplier                           |     |

| 4.2.2 Compression trees                                   |     |

| 4.2.2.1 Wallace Tree                                      |     |

| 4.2.2.2 Dadda Tree                                        |     |

| 4.2.2.3 High-order Compressors for Multi-Operand Circuits |     |

| 4.3 Multiply-and-Accumulate (MAC) Units                   |     |

| 4.4 Chapter Summary                                       | .81 |

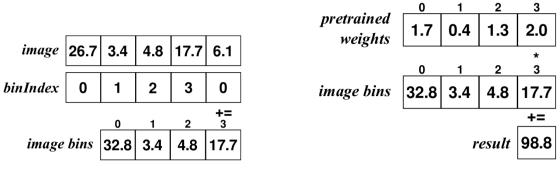

| 5.1 Framework architecture       83         5.1.1 Back-end engine       85         5.1.2 Verification module       85         5.1.3 Front-end engine       87         5.2 Framework Evaluation       89         5.2.1 Power Extraction Methodology       89         5.2.2 Multipliers Architectural Exploration with RTLGen: Synthesis Results       91         5.3 Case study: optimized Radix-2 <sup>m</sup> multiplier       94         5.3.1 Efficient Signal Extension Method for Radix-2 <sup>m</sup> Parallel Multiplier       95         5.3.2 Performance evaluation       98         5.4 Chapter Summary       99         6 CORNET FRAMEWORK: A DEEP LEARNING-BASED SOLUTION FOR       10         6.1 Heart Rate estimation       100         6.1.1 Electrocardiogram (ECG)       101         6.1.2 Photoplethysmography (PPG)       103         6.1.3 Public datasets for HR estimation       104         6.2 CorNET framework for HR estimation       106         6.2.1 Network structure       107         6.2.2 Training methodology and evaluation       108         6.3 Chapter Summary       113         7 STREAM-BASED HARDWARE IMPLEMENTATION FOR BINARY CORNET FRAMEWORK       114         7.1. Data quantization       114         7.2.1 CNN1 Layer       119 <t< th=""><th>5 RTLGEN FRAMEWORK FOR ARITHMETIC KERNELS EXPLORATION</th><th>N .82</th></t<> | 5 RTLGEN FRAMEWORK FOR ARITHMETIC KERNELS EXPLORATION                                | N .82 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------|

| 5.1.2 Verification module       85         5.1.3 Front-end engine       87         5.2 Framework Evaluation       89         5.2.1 Power Extraction Methodology       89         5.2.2 Multipliers Architectural Exploration with RTLGen: Synthesis Results       91         5.3 Case study: optimized Radix-2 <sup>m</sup> multiplier       94         5.3.1 Efficient Signal Extension Method for Radix-2 <sup>m</sup> Parallel Multiplier       95         5.3.2 Performance evaluation       98         5.4 Chapter Summary       99         6 CORNET FRAMEWORK: A DEEP LEARNING-BASED SOLUTION FOR HR ESTIMATION       100         6.1 Heart Rate estimation       100         6.1.2 Photoplethysmography (PPG)       103         6.1.3 Public datasets for HR estimation       104         6.2.1 Network structure       107         6.2.2 Training methodology and evaluation       108         6.3 Chapter Summary       113         7 STREAM-BASED HARDWARE IMPLEMENTATION FOR BINARY CORNET FRAMEWORK       114         7.1.1 Data quantization       114         7.1.2 Model binarization       115         7.1.3 Training optimization for model binarization       117         7.2.2 System architecture       117         7.2.1 CNN1 Layer       119         7.2.2 Binarizer and Max-pooling layers                                                              | 5.1 Framework architecture                                                           | 83    |

| 5.1.3 Front-end engine       87         5.2 Framework Evaluation       89         5.2.1 Power Extraction Methodology       89         5.2.2 Multipliers Architectural Exploration with RTLGen: Synthesis Results       91         5.3 Case study: optimized Radix-2 <sup>m</sup> multiplier       94         5.3.1 Efficient Signal Extension Method for Radix-2 <sup>m</sup> Parallel Multiplier       95         5.3.2 Performance evaluation       98         5.4 Chapter Summary       99         6 CORNET FRAMEWORK: A DEEP LEARNING-BASED SOLUTION FOR HR ESTIMATION       100         6.1 Heart Rate estimation       100         6.1.1 Electrocardiogram (ECG)       101         6.1.2 Photoplethysmography (PPG)       103         6.1.3 Public datasets for HR estimation       104         6.2 CORNET framework for HR estimation       106         6.2.1 Network structure       107         6.2.2 Training methodology and evaluation       108         6.3 Chapter Summary       113         7 STREAM-BASED HARDWARE IMPLEMENTATION FOR BINARY CORNET FRAMEWORK       114         7.1.1 Data quantization       114         7.1.2 CONNET model modifications       114         7.1.3 Training optimization for model binarization       117         7.2.3 Image and Max-pooling layers       120                                                                 | 5.1.1 Back-end engine                                                                | 83    |

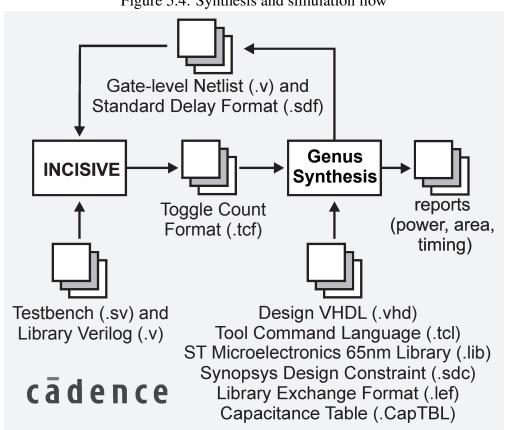

| 5.2 Framework Evaluation       89         5.2.1 Power Extraction Methodology       89         5.2.2 Multipliers Architectural Exploration with RTLGen: Synthesis Results       91         5.3.1 Efficient Signal Extension Method for Radix-2 <sup>m</sup> Parallel Multiplier       94         5.3.2 Performance evaluation       98         5.4 Chapter Summary       99         6 CORNET FRAMEWORK: A DEEP LEARNING-BASED SOLUTION FOR HR ESTIMATION       100         6.1.1 Electrocardiogram (ECG)       101         6.1.2 Photoplethysmography (PPG)       103         6.1.3 Public datasets for HR estimation       104         6.2.1 Network structure       107         6.2.2 Training methodology and evaluation       108         6.3 Chapter Summary       113         7 STREAM-BASED HARDWARE IMPLEMENTATION FOR BINARY CORNET FRAMEWORK       114         7.1.1 Data quantization       114         7.1.2 Model binarization       115         7.1.3 Training optimization for model binarization       117         7.2.1 CNN1 Layer       119         7.2.2 System architecture       117         7.2.1 CNN1 Layer       119         7.2.2 Binarizer and Max-pooling layers       120         7.2.3 Transposition Buffer       122         7.2.4 CNN2 Layer       124                                                                                           | 5.1.2 Verification module                                                            | 85    |

| 5.2.1 Power Extraction Methodology       89         5.2.2 Multipliers Architectural Exploration with RTLGen: Synthesis Results       91         5.3 Case study: optimized Radix-2 <sup>m</sup> multiplier       94         5.3.1 Efficient Signal Extension Method for Radix-2 <sup>m</sup> Parallel Multiplier       95         5.3.2 Performance evaluation       98         5.4 Chapter Summary       99         6 CORNET FRAMEWORK: A DEEP LEARNING-BASED SOLUTION FOR HR ESTIMATION       100         6.1 Heart Rate estimation       100         6.1.1 Electrocardiogram (ECG)       101         6.1.2 Photoplethysmography (PPG)       103         6.1.3 Public datasets for HR estimation       104         6.2 CORNET framework for HR estimation       106         6.2.1 Network structure       107         6.2.2 Training methodology and evaluation       108         6.3 Chapter Summary       113         7 STREAM-BASED HARDWARE IMPLEMENTATION FOR BINARY CORNET FRAMEWORK       114         7.1 CorNET model modifications       114         7.1.1 Data quantization       115         7.1.2 System architecture       117         7.2.2 System architecture       117         7.2.3 Transposition Buffer       120         7.2.4 CNN2 Layer       124         7.2.5 Binary LSTM layer                                                                       | 5.1.3 Front-end engine                                                               | 87    |

| 5.2.2 Multipliers Architectural Exploration with RTLGen: Synthesis Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5.2 Framework Evaluation                                                             | 89    |

| 5.3 Case study: optimized Radix-2 <sup>m</sup> multiplier       .94         5.3.1 Efficient Signal Extension Method for Radix-2 <sup>m</sup> Parallel Multiplier       .95         5.3.2 Performance evaluation       .98         5.4 Chapter Summary       .99         6 CORNET FRAMEWORK: A DEEP LEARNING-BASED SOLUTION FOR HR ESTIMATION       .100         6.1.1 Electrocardiogram (ECG)       .101         6.1.2 Photoplethysmography (PPG)       .103         6.1.3 Public datasets for HR estimation       .104         6.2 CorNET framework for HR estimation       .106         6.2.1 Network structure       .107         6.2.2 Training methodology and evaluation       .108         6.3 Chapter Summary       .113         7 STREAM-BASED HARDWARE IMPLEMENTATION FOR BINARY CORNET FRAMEWORK       .114         7.1 CorNET model modifications       .114         7.1.1 Data quantization       .115         7.1.2 Model binarization       .117         7.2 System architecture       .117         7.2.1 CNN Layer       .119         7.2.2 Binarizer and Max-pooling layers       .120         7.2.3 Transposition Buffer       .122         7.2.4 CNN2 Layer       .124         7.2.5 Binary LSTM layer       .128         7.2.6 Quantized dense layer       .133      <                                                                                     |                                                                                      |       |

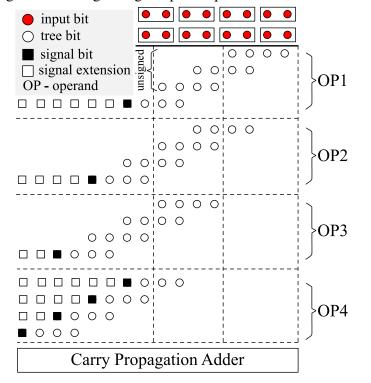

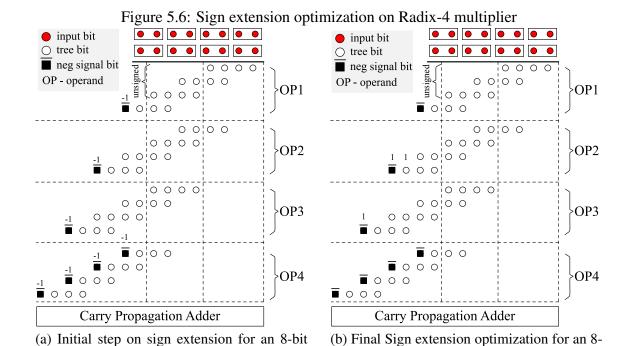

| 5.3.1 Efficient Signal Extension Method for Radix-2 <sup>m</sup> Parallel Multiplier       95         5.3.2 Performance evaluation       98         5.4 Chapter Summary       99         6 CORNET FRAMEWORK: A DEEP LEARNING-BASED SOLUTION FOR HR ESTIMATION       100         6.1 Heart Rate estimation       100         6.1.1 Electrocardiogram (ECG)       101         6.1.2 Photoplethysmography (PPG)       103         6.1.3 Public datasets for HR estimation       104         6.2 CorNET framework for HR estimation       106         6.2.1 Network structure       107         6.2 Carnining methodology and evaluation       108         6.3 Chapter Summary       113         7 STREAM-BASED HARDWARE IMPLEMENTATION FOR BINARY CORNET FRAMEWORK       114         7.1 CorNET model modifications       114         7.1.2 Model binarization       114         7.1.3 Training optimization for model binarization       117         7.2 System architecture       117         7.2.1 CNN1 Layer       119         7.2.2 Binarizer and Max-pooling layers       120         7.2.3 Transposition Buffer       122         7.2.4 CNN2 Layer       124         7.2.5 Binary LSTM layer       124         7.2.6 Quantized dense layer       133         7.3                                                                                                           | 5.2.2 Multipliers Architectural Exploration with RTLGen: Synthesis Results           | 91    |

| 5.3.2 Performance evaluation       98         5.4 Chapter Summary       99         6 CORNET FRAMEWORK: A DEEP LEARNING-BASED SOLUTION FOR HR ESTIMATION       100         6.1 Heart Rate estimation       100         6.1.1 Electrocardiogram (ECG)       101         6.1.2 Photoplethysmography (PPG)       103         6.1.3 Public datasets for HR estimation       104         6.2 CorNET framework for HR estimation       106         6.2.1 Network structure       107         6.2.2 Training methodology and evaluation       108         6.3 Chapter Summary       113         7 STREAM-BASED HARDWARE IMPLEMENTATION FOR BINARY CORNET FRAMEWORK       114         7.1.1 Data quantization       114         7.1.2 Model binarization       115         7.1.3 Training optimization for model binarization       117         7.2 System architecture       117         7.2.1 CNN1 Layer       119         7.2.2 Binarizer and Max-pooling layers       120         7.2.3 Transposition Buffer       122         7.2.4 CNN2 Layer       124         7.2.5 Guantized dense layer       123         7.3 Timing Analysis       133         7.4 Evaluation of the bCorNET framework on ASIC and FPGA platforms       136         7.5 Chapter Summary<                                                                                                                     | 5.3 Case study: optimized Radix-2 <sup>m</sup> multiplier                            | 94    |

| 5.4 Chapter Summary       99         6 CORNET FRAMEWORK: A DEEP LEARNING-BASED SOLUTION FOR HR ESTIMATION       100         6.1 Heart Rate estimation       100         6.1.1 Electrocardiogram (ECG)       101         6.1.2 Photoplethysmography (PPG)       103         6.1.3 Public datasets for HR estimation       104         6.2 CorNET framework for HR estimation       106         6.2.1 Network structure       107         6.2.2 Training methodology and evaluation       108         6.3 Chapter Summary       113         7 STREAM-BASED HARDWARE IMPLEMENTATION FOR BINARY CORNET FRAMEWORK       114         7.1 CorNET model modifications       114         7.1.1 Data quantization       115         7.1.2 Model binarization       115         7.1.3 Training optimization for model binarization       117         7.2 System architecture       117         7.2.1 CNN1 Layer       119         7.2.2 Binarizer and Max-pooling layers       120         7.2.3 Transposition Buffer       122         7.2.4 CNN2 Layer       124         7.2.5 Binary LSTM layer       128         7.3 Timing Analysis       133         7.4 Evaluation of the bCorNET framework on ASIC and FPGA platforms       136         7.5 Chapter Summary </td <td>5.3.1 Efficient Signal Extension Method for Radix-2<sup>m</sup> Parallel Multiplier</td> <td>95</td>         | 5.3.1 Efficient Signal Extension Method for Radix-2 <sup>m</sup> Parallel Multiplier | 95    |

| 6 CORNET FRAMEWORK: A DEEP LEARNING-BASED SOLUTION FOR HR ESTIMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5.3.2 Performance evaluation                                                         | 98    |

| HR ESTIMATION       100         6.1 Heart Rate estimation       100         6.1.1 Electrocardiogram (ECG)       101         6.1.2 Photoplethysmography (PPG)       103         6.1.3 Public datasets for HR estimation       104         6.2 CorNET framework for HR estimation       106         6.2.1 Network structure       107         6.2.2 Training methodology and evaluation       108         6.3 Chapter Summary       113         7 STREAM-BASED HARDWARE IMPLEMENTATION FOR BINARY CORNET FRAMEWORK       114         7.1 Data quantization       114         7.1.1 Data quantization       115         7.1.3 Training optimization for model binarization       117         7.2 System architecture       117         7.2.1 CNN1 Layer       119         7.2.2 Binarizer and Max-pooling layers       120         7.2.3 Transposition Buffer       122         7.2.4 CNN2 Layer       124         7.2.5 Binary LSTM layer       128         7.2.6 Quantized dense layer       133         7.3 Timing Analysis       133         7.4 Evaluation of the bCorNET framework on ASIC and FPGA platforms       136         7.5 Chapter Summary       136         7.5 Chapter Summary       136                                                                                                                                                                         |                                                                                      |       |

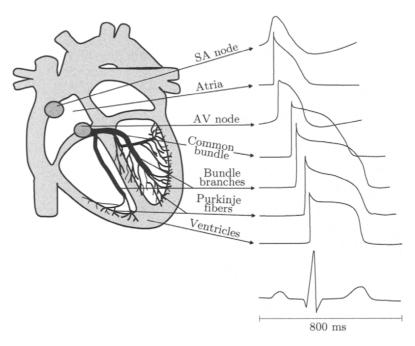

| 6.1 Heart Rate estimation       100         6.1.1 Electrocardiogram (ECG)       101         6.1.2 Photoplethysmography (PPG)       103         6.1.3 Public datasets for HR estimation       104         6.2 CorNET framework for HR estimation       106         6.2.1 Network structure       107         6.2.2 Training methodology and evaluation       108         6.3 Chapter Summary       113         7 STREAM-BASED HARDWARE IMPLEMENTATION FOR BINARY CORNET FRAMEWORK       114         7.1 CorNET model modifications       114         7.1.2 Model binarization       115         7.1.3 Training optimization for model binarization       117         7.2 System architecture       117         7.2.1 CNN1 Layer       119         7.2.2 Binarizer and Max-pooling layers       120         7.2.3 Transposition Buffer       122         7.2.4 CNN2 Layer       124         7.2.5 Binary LSTM layer       128         7.2.6 Quantized dense layer       133         7.3 Timing Analysis       133         7.4 Evaluation of the bCorNET framework on ASIC and FPGA platforms       136         7.5 Chapter Summary       139         8 CONCLUSIONS       141         8.1 Main findings       141                                                                                                                                                                 | 6 CORNET FRAMEWORK: A DEEP LEARNING-BASED SOLUTION FOR                               |       |