## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

## INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

#### **VLADIMIR AFONSO**

## **High-Throughput Dedicated Hardware Design Targeting the 3D-HEVC-Prediction Coding Tools**

Thesis presented as partial requirement for the Ph.D. degree in Microelectronics.

Advisor: Prof. Dr. Altamiro Amadeu Susin Co-advisor: Prof. Dr. Luciano Volcan Agostini

## CIP – CATALOGAÇÃO NA PUBLICAÇÃO

Afonso, Vladimir

High-Throughput Dedicated Hardware Design Targeting the 3D-HEVC-Prediction Coding Tools / Vladimir Afonso. – Porto Alegre: PGMicro da UFRGS, 2019.

204 f.:il.

Orientador: Altamiro Amadeu Susin; Coorientador: Luciano Volcan Agostini.

Tese (Doutorado) — Universidade Federal do Rio Grande do Sul, Instituto de Informática, Programa de Pós-Graduação em Microeletrônica. Porto Alegre, BR — RS, 2019.

1. Video Coding. 2. 3D-HEVC. 3. Depth Maps. 4. Real-Time Embedded System. 5. Low-Energy Hardware Design. I. Susin, Altamiro Amadeu, orient. II. Agostini, Luciano Volcan, coorient. III. Título.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Profª. Carla Maria Dal Sasso Freitas

Coordenador do PGMICRO: Prof. Tiago Roberto Balen

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **AGRADECIMENTOS**

Quando se inicia um curso de doutorado, várias são as incomodações que permeiam os nossos pensamentos. E uma das dúvidas predominantes é a de como lidar com o tempo que temos para trabalhar, que por horas parece tão pouco e por horas parece mais do que o necessário. Um doutorado talvez seja a mais perfeita analogia para o entendimento da relatividade, usando o tempo (depois do exemplo dado por Albert Einstein), pois em um relance de pensamento pode nos parecer que vivemos outra vida ou, ainda, que não vivemos um dia sequer. Por isso, toda tese de doutorado (também) deveria se chamar: Uma Breve História do Tempo.

Qual será o tempo de um doutorado? É o tempo suficiente para comprometer o corpo. É o tempo suficiente para comprometer a mente. É o tempo suficiente para atravessar uma separação. É o tempo suficiente para se afastar de um irmão. É o tempo suficiente para ver a pessoa mais forte que conhecia desabar. É o tempo suficiente para ver várias pessoas queridas partir. É o tempo suficiente para ver a pessoa mais corajosa que conhecia findar. É o tempo suficiente para ver o mundo ruir.

Mas o tempo de um doutorado também é o tempo suficiente para se levantar. É o tempo suficiente para se sentir literalmente mais leve. É o tempo suficiente para correr longas distâncias. É o tempo suficiente para se reinventar. É o tempo suficiente para se apaixonar e se desapaixonar. É o tempo suficiente para ser perdoado e para perdoar. É o tempo suficiente para entender o valor das coisas, da vida e das pessoas. Enfim, é o tempo suficiente para recomeçar.

Qual será o tempo de um doutorado? É o tempo suficiente para entender que o nosso tempo é finito. É o tempo suficiente para entender que o momento derradeiro é imprevisível. É o tempo suficiente para entender o tempo.

Por entender o valor da vida e das pessoas, em primeiro lugar, agradeço aos meus pais, Eledir Lobo Afonso e Neli Afonso (*in memoriam*), que apesar de todas as adversidades que lhes foram impostas pela vida, tomaram a decisão de permitir que eu deixasse a pequena cidade de Herval/RS em 1997, ainda adolescente, para cursar um curso técnico em Eletrônica na antiga ETFPel (Escola Técnica Federal) em Pelotas/RS. Por sabedoria, eles me deram uma das coisas mais importantes, senão a mais importante, que pais podem dar aos seus filhos, a oportunidade de estudar e ter uma profissão. Deram-me a oportunidade a qual eles mesmos não puderam usufruir plenamente durante suas vidas. O destino impôs que minha mãe partisse antes de ver a concretização dessa etapa da minha vida, mas antes ficou claro para nós dois a

importância de cada um na vida do outro. Sou grato por isso. Agradeço também a minha avó Sirena, meu irmão Rogério, minha sobrinha Ana Júlia e aos meus demais familiares, assim como aos meus amigos, pela compreensão da ausência em diversos momentos durante o desenvolvimento desse trabalho.

Faço um agradecimento especial ao meu orientador, Prof. Altamiro Susin, e ao meu coorientador, Prof. Luciano Agostini, que além de me oportunizarem a pesquisa de um tema extremamente relevante, disponibilizaram parte do seu tempo para me orientar no desenvolvimento de cada etapa desse trabalho. Sou grato pelas discussões, revisões e todas outras contribuições dadas por vocês. Ao Prof. Luciano Agostini também agradeço por ter colaborado para o meu desenvolvimento como ser humano, e para o meu melhor entendimento sobre todo o contexto em que as relações humanas se estabelecem.

Agradeço ao Prof. Marcelo Porto, com quem tenho uma relação de amizade desde 1998, ou seja, há mais de 20 anos, por ter participado ativamente do meu doutorado, dando contribuições para o trabalho mesmo sem ter orientação formal. Da mesma forma, agradeço enormemente ao Prof. Bruno Zatt, que por diversos momentos, quando eu tinha dúvidas gigantescas sobre o desenvolvimento do trabalho, me direcionou para as escolhas que hoje entendo terem sido as mais acertadas.

A todos os professores, bolsistas de iniciação científica, mestrandos e doutorandos do GACI (Grupo de Arquiteturas e Circuitos Integrados) e do ViTech (*Video Technology Research Group*) da UFPel, fica o meu agradecimento pela oportunidade de aprendizado e pela boa convivência estabelecida durante esses anos de pesquisa. Poderia citar dezenas de nomes de amigos que fiz durante o doutorado, fica aqui o meu abraço fraterno em todos vocês. Em especial, agradeço aos amigos doutorandos Ruhan Conceição (a quem chamo de maninho) e Mario Saldanha (um craque de bola) e ao amigo mestrando Murilo Perleberg (o golden boy) que colaboraram do início ao fim para que este trabalho se tornasse realidade. Não posso deixar de agradecer também a Mariana Ucker, o Luan Audibert, o Henrique Maich e o Jones Goebel, que colaboraram ou participaram de forma importante nesse trabalho, em diferentes momentos.

Deixo o meu agradecimento aos colegas de doutorado do PGMicro e do PPGC da UFRGS, em especial, aos amigos Alexandra Zimpeck, Louise Etcheverry, Renato Campana, Guillermo Daniel Ortega Galeano e Fabio Irigon com quem dividi muitos instantes, várias tarefas, momentos de estudo e de trabalho pela universidade.

Agradeço aos colegas professores do Curso Técnico em Eletromecânica do IFSul que ministraram as aulas da disciplina de Eletrônica Industrial enquanto eu estava afastado para o

doutorado. Faço um agradecimento especial aos professores e amigos Mario Farias, Jair Jonko Araujo, Andrea Fisher, Claudio Machado e Igor Bederode por terem me dado apoio incondicional enquanto não conseguia o afastamento no IFSul para cursar o doutorado em Microeletrônica em Porto Alegre/RS. Agradeço também aos professores Carlos Corrêa, José Octávio Badia, Rafael Griep, Rodrigo Souza, Velington Neumman e André Oldoni, que juntamente com os professores Andrea, Claudio e Igor se comprometeram em assumir a minha carga horária (2015) até que um professor substituto fosse disponibilizado pelo IFSul.

Por fim, agradeço a todos aqueles, que de alguma forma, seja participando da minha formação profissional ou como ser humano, contribuíram para que este objetivo fosse alcançado.

#### **ABSTRACT**

The popularization of multimedia services has pushed forward the development of 2D/3D (Two and Three Dimensional) video-capable embedded mobile devices. In this scenario, 3D-video systems based on the simultaneous exhibition of multiple views are also expected, including systems capable of dealing with high and ultra-high resolutions. To meet this demand and the huge amount of data to be processed and stored, an extension for the HEVC (High Efficiency Video Coding) standard targeting three-dimensional video coding was developed by the ISO/IEC (International Organization for Standardization / International Electrotechnical Commission) and ITU-T (International Telecommunication Union -Telecommunication) experts. The HEVC is state-of-the-art for 2D video coding, and its 3D extension is called 3D-HEVC. The 3D-HEVC uses the MVD (Multi-view plus Depth) concept which associates a depth-map with each texture frame for each view that composes the video sequence. Because of that, 3D-HEVC defines several novel coding tools to make possible the 3D-video processing with multiple views with increasing resolutions under this novel perspective. As a result, the 3D-HEVC extension requires a high computational effort. Since 2D/3D video-capable embedded mobile devices require efficient energy/memorymanagement strategies to deal with severe memory/processing requirements and limited energy supply, the development of energy and memory-aware systems targeting the 3D-HEVC is essential.

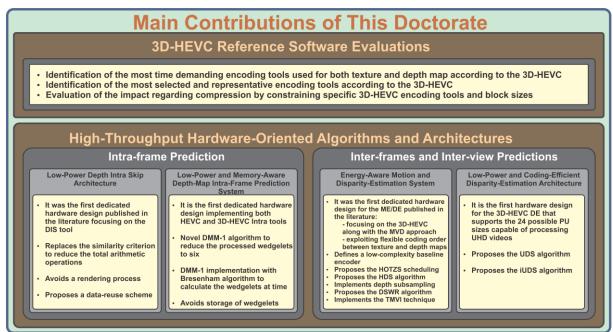

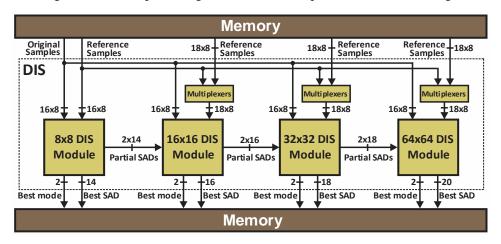

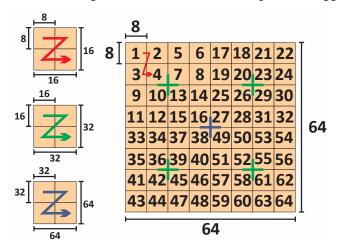

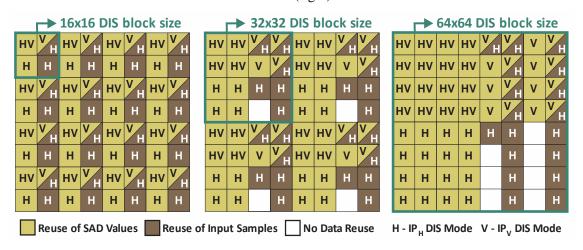

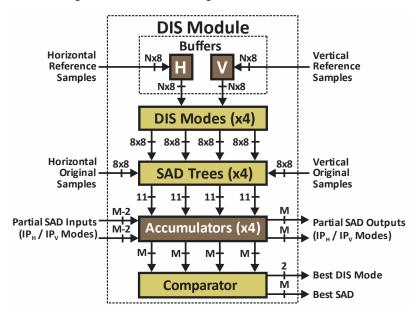

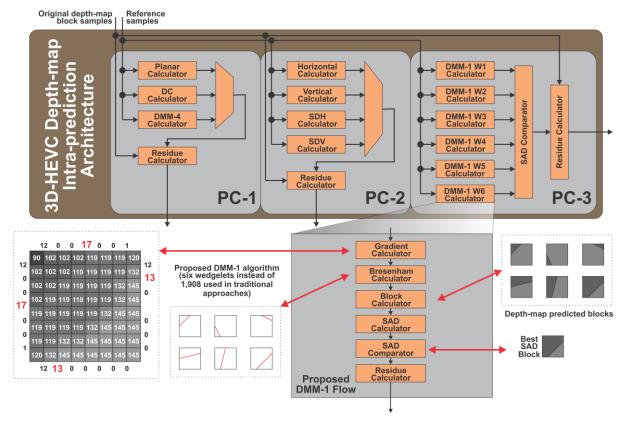

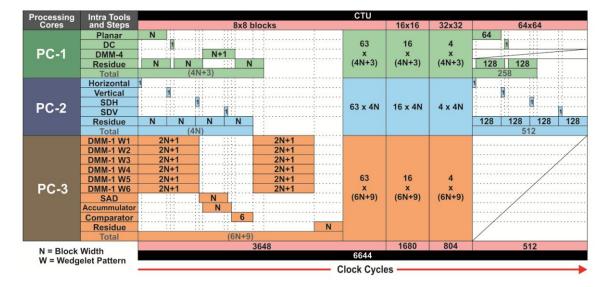

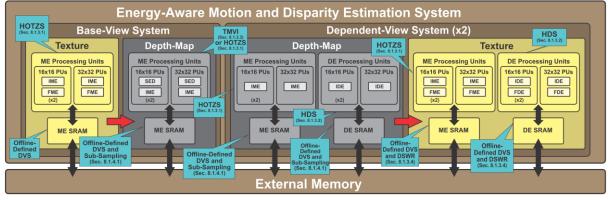

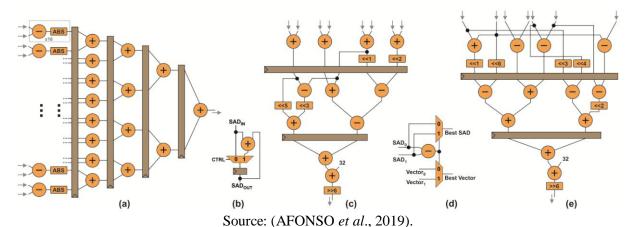

This thesis brings contributions for high-throughput and low-power architectures targeting the 3D-HEVC. These contributions are mainly centered on four designed architectures, as follows: (i) a low-power and high-throughput hardware design for the DIS (Depth Intra Skip) coding tool; (ii) a low-power and memory-aware depth-map Intra-frame prediction system based on complexity-reduction strategies; (iii) a ME/DE (Motion and Disparity Estimation) system that was designed for low-energy consumption, featuring a runtime adaptive memory hierarchy; (iv) a low-power and coding-efficient disparity estimation architecture based on the proposed iUDS (Improved Unidirectional Disparity-Search) algorithm. The contributions of these architectures to the state-of-the-art are confirmed by the publications made so far in high-quality conferences/journals.

**Keywords**: Video Coding. 3D-HEVC. Depth Maps. Real-Time Embedded System. Low-Energy Hardware Design.

# Projeto de Hardware Dedicado de Elevada Taxa de Processamento para as Ferramentas de Codificação da Predição do 3D-HEVC

#### **RESUMO**

A popularização de serviços multimídia tem alavancado o desenvolvimento de dispositivos portáteis capazes de lidar com vídeos 2D/3D. Nesse cenário, sistemas de vídeo 3D baseados na exibição simultânea de múltiplas vistas também são esperados, incluindo sistemas capazes de lidar com altas e ultra-altas resoluções. Para atender essa demanda e a grande quantidade de dados que precisa ser processada e armazenada, uma extensão do padrão HEVC (High Efficiency Video Coding) visando à codificação de vídeos 3D foi desenvolvida por especialistas da ISO/IEC (International Organization for Standardization / International Electrotechnical Commission) e da ITU-T (International Telecommunication *Union – Telecommunication*). O HEVC é o estado da arte para codificação de vídeos 2D e sua extensão para 3D é chamada 3D-HEVC. O 3D-HEVC usa o conceito MVD (Multi-view plus Depth) em que um mapa de profundidade é associado a cada quadro de textura para cada vista que compõem a sequência de vídeo. Devido a isso, o 3D-HEVC define diversas novas ferramentas de codificação para tornar possível o processamento de vídeos 3D com múltiplas vistas com resoluções crescentes sob essa nova perspectiva. Como um resultado, a extensão 3D-HEVC requer um elevado esforço computacional. Uma vez que dispositivos móveis embarcados capazes de lidar com vídeos 2D/3D requerem estratégias eficientes para gerenciamento de memória/energia e para lidar com os severos requisitos de processamento/memória e fornecimento limitado de energia, o desenvolvimento de sistemas voltados para eficiência em energia e memória visando o 3D-HEVC é essencial.

Esta tese traz contribuições para arquiteturas com alta taxa de processamento e baixa dissipação de potência visando o 3D-HEVC. Estas contribuições estão principalmente centradas em quatro arquiteturas, como segue: (i) um projeto de hardware com baixa dissipação de potência e alta taxa de processamento para a ferramenta de codificação DIS (*Depth Intra Skip*); (ii) um sistema para predição *Intra-frame* de mapas de profundidade com baixa dissipação de potência e voltado para eficiência em memória baseado em estratégias de redução de complexidade; (iii) um sistema para a ME/DE (*Motion/Disparity Estimation*) projetado para baixo consumo de energia, apresentando uma hierarquia de memória adaptável em tempo real; (iv) uma arquitetura para estimação de disparidade com baixa dissipação de potência e eficiência em codificação baseada no algoritmo proposto iUDS (*Improved*

*Unidirectional Disparity-Search*). As contribuições destas arquiteturas para o estado da arte são confirmadas pelas publicações feitas até o momento em conferências e revistas qualificadas.

**Palavras-chave**: Codificação de Vídeos. 3D-HEVC. Mapas de Profundidade. Sistema Embarcado de Tempo Real. Projeto de Hardware de Baixo Consumo Energético.

## LIST OF FIGURES

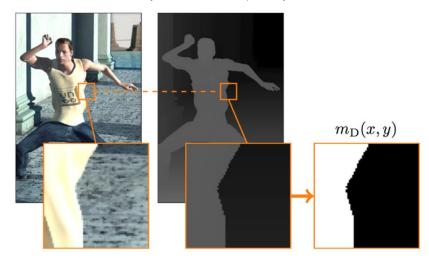

| Figure 1.1 – Example of texture pictures and their respective depth maps considering a syste                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| two original and three synthetic views                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |

| Figure 1.2 – Examples of electronic devices based on emerging acquisition and dispersion technologies.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |

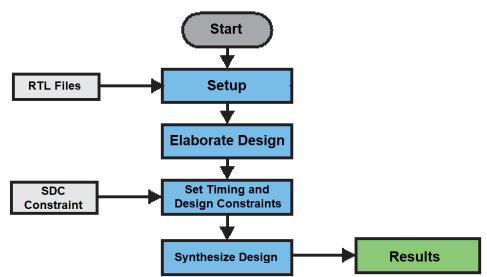

| Figure 1.3 – Main contributions of this doctorate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

| rigure 1.5 – Main contributions of this doctorate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21      |

| Figure 2.1 – Sequence of temporal neighboring frames and a frame divided into blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 30      |

| Figure 2.2 – Generic 2D-video encoder model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |

| Figure 2.3 – RD curves used to (a) BD-BR and (b) BD-PSNR calculations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |

| 1 Igure 2.5 RD curves used to (a) DD BR and (b) DD 1 DTR calculations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 50      |

| Figure 3.1 – Example of a CTU divided into CUs and its respective quaternary tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40      |

| Figure 3.2 – Types of partition of a CU in PUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

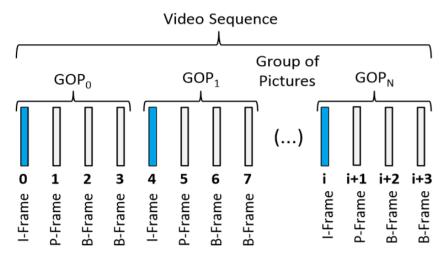

| Figure 3.3 – Example of a video sequence divided into GoPs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |

| Figure 3.4 – IO temporal configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |

| Figure 3.5 – RA Temporal Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |

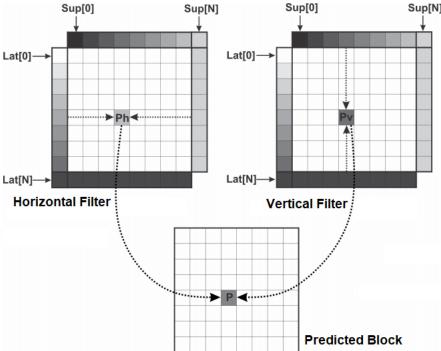

| Figure 3.6 – Example of an 8x8 block calculated using the Planar mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |

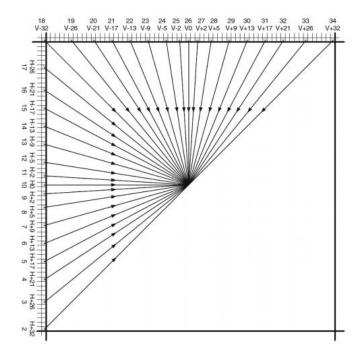

| Figure 3.7 – Angular modes definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 45      |

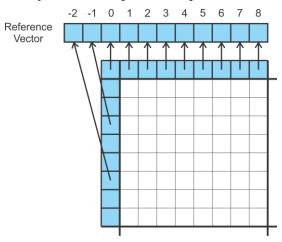

| Figure 3.8 – Projection of samples to complete the reference vector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 46      |

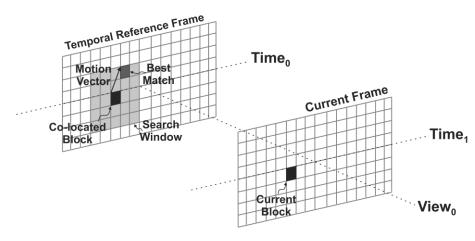

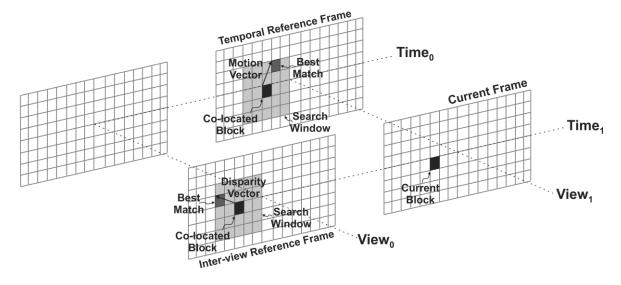

| Figure 3.9 – Illustration of the ME process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 48      |

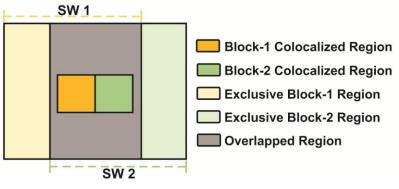

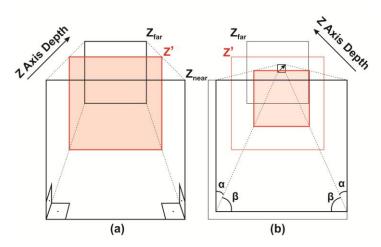

| Figure 3.10 – Level-C scheme overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |

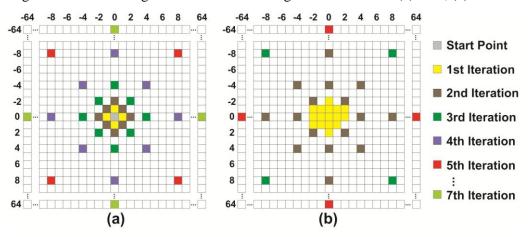

| Figure 3.11 – TZS Algorithm: (a) Flowchart; (b) Expansions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |

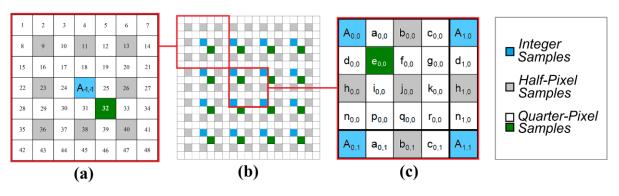

| Figure 3.12 – Fractional Motion Estimation: (a) First samples of the 48 fractional blocks; (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

| block; (c) Samples at integer and fractional positions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |

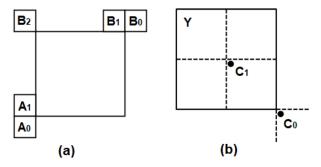

| Figure 3.13 - Merge candidates: (a) Spatial-neighboring candidates; (b) Temporal-neighboring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _       |

| candidates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 53      |

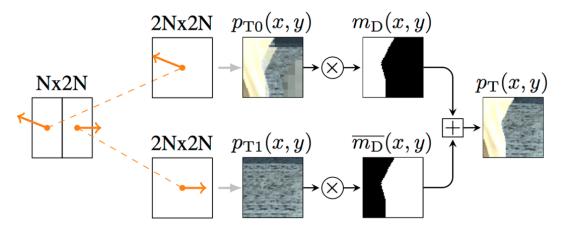

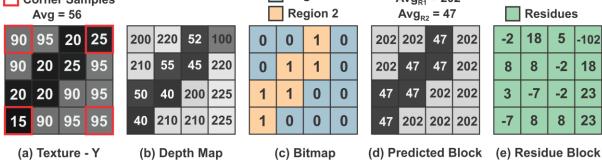

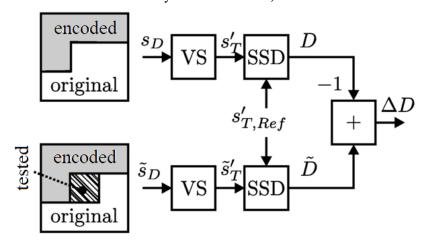

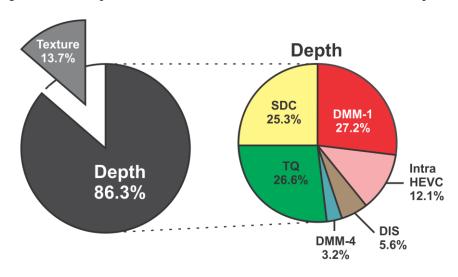

| Figure 4.1 – Overview of the basic 3D coding structure in conformance with the 3D-HEVC ex                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | tension |

| Tigure Will Great view of the busic 3D country structure in comportance with the 3D Till view.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

| Figure 4.2 – Encoding process based on Access Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |

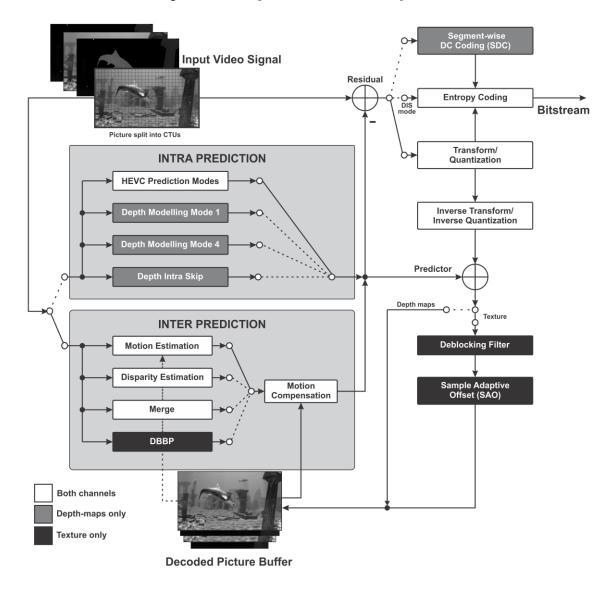

| Figure 4.3 – Simplified 3D-HEVC encoding model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

| Figure 4.4 – CCO base structure of the encoder with Inter-component and Inter-view predictions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

| Figure 4.5 – FCO base structure of the encoder with Inter-component and Inter-view predictions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

| Figure 4.6 – Examples of MCP and DCP predictions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 61      |