# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

## PABLO ILHA VAZ

Design flow methodology for Radiation Hardening by Design CMOS Enclosed Layout Transistor based standard cell library for aerospace applications

> Thesis presented in partial fulfillment of the requirements for the degree of PhD in Microelectronics

Advisor: Prof. Dr.-Ing. Gilson Inácio Wirth

## CIP — CATALOGING-IN-PUBLICATION

Ilha Vaz, Pablo

Design flow methodology for Radiation Hardening by Design CMOS Enclosed Layout Transistor based standard cell library for aerospace applications / Pablo Ilha Vaz. – Porto Alegre: PGMI-CRO da UFRGS, 2019.

124 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR-RS, 2019. Advisor: Gilson Inácio Wirth.

1. Radiation-Hardening. 2. Aerospace applications. 3. Enclosed Layout Transistor. 4. Standard Cell Library. 5. Bulk CMOS. 6. Full-custom design flow. I. Inácio Wirth, Gilson. II. Título.

## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenadora do PGMICRO: Prof. Fernanda Gusmão de Lima Kastensmidt Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

## ACKNOWLEDGMENTS

First and foremost, I would like to thank my parents João Carlos and Ana Lúcia, who have been given to me a life of privileges, enabling me to devote myself full time to my academic and professional qualification, because they have always believed that "the greatest wealth we have is the knowledge". I have always been able to work with what I love and what makes me happy.

Inicialmente, gostaria de agradecer aos meus pais João Carlos e Ana Lúcia, que me proporcionaram uma vida de privilégios, possibilitando que eu me dedicasse primordialmente à minha qualificação profissional, pois sempre acreditaram e me ensinaram que "o maior bem que temos na vida é o conhecimento". Com isso, sempre pude trabalhar com o que amo e que me faz feliz.

I thank my advisor Prof. Dr-Ing. Gilson Wirth who, since my college days, trusted and believed in my potential always giving me freedom to perform my work "with my own hands", which motivated me not only to invite him to be my master's and doctoral advisor, but also to embrace a project of this magnitude, exploiting my full potential. He was always present when I needed technical, bureaucratic help and suggestions to make decisions throughout the project.

In addition, without the support of my laboratory colleagues, this thesis would not exist. In many times, the help was not only with technical knowledge, but the support very often came in moments of talks, motivation and joy. Raphael Brum, Thiago Both, Fábio Vidor and Alan Rossetto, thank you very much for the companionship and friendship.

A work of this magnitude, lasting a few years, where much depends on "your own efforts" ends up invariably going through some "ups and downs". I am very lucky to have friends who believed in me even more than I did sometimes, causing the moments of discouragement to end up being very short, if they existed.

I am very grateful to my longtime companion Gabriela Zuchi and my friends Cristiano Pires, Mauricio Grando, Silvio Junior, Júlio Cesar, Paulo Almeida, Alberto Wiltgen and Israel Mello who, in one way or another, have always been supporting me and being by my side — if you have good friends, everything else is possible.

Letícia Temp, thank you for the English lessons and accurate manuscript corrections which, certainly, improved the technical quality of this thesis. Even in the context of electrical engineering, physics, ionizing radiation, transistors and so on you accepted the challenge (when many others refused).

Finally, I would like to thank CNPq for their financial support.

## **ABSTRACT**

Applications exposed to incidence of ionizing radiation, such as aerospace applications, may have their performance and reliability degraded by the interaction of high-energy ions. Thus, applications exposed to incidence levels of such ions can be severely affected over time. In these cases, hardening techniques are required for the proper operation of those devices when subject to harsh environments. Unfortunately, Brazil does not produce radiation-tolerant integrated circuits and, over time, the lack of this expertise not only hinder R&D opportunities but also drastically increases the costs of buying hardened and reliable circuits. For the most part, the increase occurs because in the overwhelming majority of cases these circuits are subjected to territorial regulations by other countries or have restricted availability (proprietary right) or are only discussed within academic institutions. To synthesize complex circuits as, for example, Application Specific Integrated Circuits -ASICS, the use of an automated design flow is inherently necessary mainly due to a huge number of transistors, reaching, in some cases, the order of some billions. To face the lack of reliable foundry-provided Radiation-Hardening by Design (RHBD) cell libraries, this thesis promotes a complete RHBD flow methodology employing enclosed-layout transistors (ELTs) and guard rings, transparent to the designer, and fully compatible with commercial CAD tools and standard fabrication processes. The proposed flow includes the automated calculation of the effective aspect ratio (W/L) of the ELTs, promoting state-ofthe-art improvements to key points of the ICs design flow such as the template proposal for digital cells, as well as its series and parallel arrangements. Moreover, it also covers employing for the first time, for the sake of our knowledge, the calculation of PN ratio and output buffers dimension using Logical Effort (LE) methodology, i.e., time optimization approach with enclosed devices. To validate the proposed methodology test structures, enclosing single n,pMOS devices, series and parallel arrangements, inverter cells, ring oscillators, and output buffers, were fabricated in two different technology nodes (600 nm and 180 nm). Subsequently to their electrical characterization, they were compared to SPICE simulations and, after irradiated, the increase in the leakage current and shift in the threshold voltage were compared with related works. Besides, two silicon-proven case studies presented fully functional behavior under typical conditions even after  $500 \ krad$  of absorbed dose, achieving success in the radiation test. The results and experimental data indicate that the radiation tolerant cells designed with the proposed flow are feasible to implement and their hardness degree is in accordance with the findings in the literature, where the transistors and circuits were manually designed. Therefore, the novel methodology of automated design flow is an elegant solution to efficiently reduce time and costs for the development of RHBD devices for sensitive applications in harsh environments, consolidating the proposed thesis and contributing with the ability to tape-out such circuits in the Brazilian semiconductor industry.

**Keywords:** Radiation-Hardening. Aerospace applications. Enclosed Layout Transistor. Standard Cell Library. bulk CMOS. Full-custom design flow.

# Metodologia para fluxo de projeto de biblioteca de células CMOS tolerantes à radiação baseada em dispositivos de geometria de gate fechado para aplicações aeroespaciais

#### **RESUMO**

Aplicações sujeitas à incidência de radiação ionizante, tais como aplicações aeroespaciais, podem ter sua performance e confiabilidade afetadas devido à interação de íons de alta energia. Para estes casos, a aplicação de técnicas de tolerância à radiação são necessárias a fim de possibilitar o funcionamento prolongado de dispositivos em ambientes sujeitos à incidência de tais íons. Infelizmente, o Brasil não produz dispositivos tolerantes à radiação, o que, no presente momento, não somente prejudica a pesquisa e desenvolvimento destes equipamentos, como aumenta drasticamente seu custo de produção. Em sua grande maioria, esses empecilhos e aumento de custo ocorrem devido às taxas alfandegárias e de importação entre países; por se tratar de propriedade intelectual (patentes registradas); ou, ainda, por serem apenas abordadas no âmbito acadêmico. Como alternativa a esse conjunto de demandas, esta tese apresenta um fluxo de projeto para o desenvolvimento e síntese de circuitos tolerantes à radiação utilizando dispositivos de *gate* fechado (ELTs). O fluxo proposto visa a síntese de circuitos digitais complexos, com um grande número de transistores, na ordem de alguns bilhões. Por este motivo, esta tese implementa a automatização do cálculo da razão de aspecto (W/L) dos ELTs, possibilitando que a síntese seja transparente para o projetista e totalmente compatível com as ferramentas de projeto comerciais. A proposta de fluxo de projeto possui vários aspectos inovadores como, por exemplo, o template para células digitais e sua organização em arranjos em série e paralelo. Ademais, de acordo com nosso conhecimento, aplicando também o método do Logical Effort (LE) pela primeira vez no contexto dos ELTs, tanto no cálculo da razão PN quanto no dimensionamento de *buffers* de saída. Para a validação da tese proposta foram fabricadas estruturas de teste com dispositivos de gate fechado, tanto n como pMOS, arranjos em série e paralelo, células inversoras, osciladores em anel e buffers de saída em dois nós tecnológicos distintos (600 nm e 180 nm). A caracterização elétrica dos dispositivos foi comparada às simulações elétricas SPICE e, após estresse de radiação, seu incremento na corrente de fuga e desvios na tensão de threshold foram analisados e comparados com base em trabalhos relacionados. Ambos os chips de teste tiveram sua funcionalidade integralmente verificada já na primeira rodada de fabricação em silício, dentro das margens

de tolerância e condições típicas de funcionamento, atingindo sucesso no teste de radiação mesmo após 500 krad de Dose. Os resultados e dados experimentais indicam que as células tolerantes projetadas através do fluxo proposto têm sua implementação viável e o nível de tolerância obtido está de acordo com os referenciados na literatura, nos quais os dispositivos e circuitos são projetados manualmente. Portanto, a nova proposta de projeto de fluxo automatizado é uma solução elegante para a redução, de forma eficiente, de tempo e custo no desenvolvimento de dispositivos tolerantes para aplicações sensíveis à radiação, consolidando a tese proposta e contribuindo para a habilidade de produção de dispositivos tolerantes na indústria Brasileira de semicondutores.

**Palavras-chave:** Tolerância à radiação. Aplicações aeroespaciais. Geometria de *gate* fechado. Biblioteca de células. *bulk CMOS*. Fluxo de projeto *full-custom*.

# LIST OF ABBREVIATIONS AND ACRONYMS

ASIC Application-Specific Integrated Circuit

BSIM Berkeley Short-channel IGFET Model

CAD Computed Aided Design

CLM Channel Length Modulation

CMOS Complementary Metal Oxide Semiconductor

DD Displacement Damage

DRC Design Rule Checking

ECSS European Cooperation for Space Standardization

ECT Edge and Corners Transistors

ELT Enclosed Layout Transistor

ESA European Space Agency

ESD Electrostatic Discharge Protection

FIT Failure in Time

FoM Figure of Merit

FOX Field Oxide

FO4 Fanout-of-four

GDSII Graphic Database System

HEP High Energy Physics

IC Integrated Circuit

ICR Transient current pulse

IP Intellectual Property

ITAR International Traffic in Arms Regulation

LE Logical Effort

LEF Layout Extend Format

LET Linear Energy Transfer

LOCOS Local Oxidation of Silicon

LVS Layout Versus Schematic

MOS Metal Oxide Semiconductor

PCB Printed Circuit Board

PDK Process Design Kit

PEX Parameter Extraction

RTL Register Transfer Level

RHBD Radiation-Hardening by Design

R&D Research and Development

SEE Single-Event Effects

SPICE Simulation Program with Integrated Circuit Emphasis

SPT Sum of Parallel Transistors

S&S Space and Satellite

STD Standard Device

STI Shallow Trench Isolation

TB Test Bench

TE Two-Edged Device

TID Total Ionizing Dose

UFRGS Federal University of Rio Grande do Sul

# LIST OF SYMBOLS

B Path's branching effort [-]

$C_{in,out}$  Input and Output capacitances [F]

$C_L$  Load capacitance [F]

$C_{gox_{n,p}}$  Gate oxide capacitance  $[F/\mu m^2]$

$C_{g_{n,p}}$  Gate oxide n and p capacitances [F]

$\gamma$  Gamma ratio (or PN aspect ratio) [-]

$d_{hor}, d_{ver}$  ELT's horizontal and vertical internal diffusion distances [m]

D Absorbed ionized doze [Gy]

$\Delta I_D$  Drain current variation [A]

$\Delta G_{di,o}$  Output device's conductance variation for drain in- and outside [-]

$\Delta L$  Channel length variation [m]

$\Delta L_{di,o}$  Pinch-off region variation for drain in- and outside [m]

$\Delta V_{DS}$  Source/drain voltage variation [V]

$E, E_0$  Energy dissipation and its value at position X = 0 [J]

$ar{e}/h$  Electron/hole pairs [-]

$f_T$  Transition frequency [Hz]

L Transistor's length [nm]

F Path's effort [-]

$\hat{f}$  Stage effort [-]

G Path's Logical Effort [-]

$G_{area_{n,p}}$  Gate area over an n and p diffusion  $[m^2]$

$g_{avg}$  Medium value for Logical Effort [-]

$G_{out}$  Output device's conductance [S]

$g_{sd}$  Source/drain conductance [S]

$g_{u,d}$  Logical Effort for rising (u) and falling (d) transitions [-]

$I_0$  Current generated by the charges [A]

$K_{n,p}(S)$  Series factor for nMOS and pMOS devices [-]

H Electrical Effort [-]

LET Linear energy transfer of ionizing radiation  $[MeV/(mg/cm^2)]$

N Linear density of electron-hole pairs [LET/eV]

$\mu$  Gamma ratio for a balanced inverter cell [-]

$\hat{N}$  Best number of stages [-]

$NM_{H,L}$  Noise margins High and Low [V]

$P_{avg}$  Average power [W]

q Electron charge [C]

$Q_{crit}$  Minimum amount of charge necessary to induce an upset [C]

$Q_D$  Drift charge component [C]

$Q_DF$  Diffusion charge component [C]

$Q_F$  Funnel charge component [C]

$Q_t$  Total Spurious Charge [C]

$r_{hi,lo}$  Skewing factors High and Low [-]

$\rho$  Material density  $[g/cm^3]$

$au_{r,f}$  Transient current rise time and fall time [s]

$\theta$  Incident ion hit angle [°]

$t_{ox}$  Oxide thickness [nm]

$t_p$  Propagation delay [s]

$t_{rise,fall}$  Rise and Fall times [s]

$V_{DD}$  Positive supply voltage [V]

$V_{SS}$  Negative (or ground) supply voltage [V]

$V_{th}$  Threshold voltage [V]

X Unit cell size current capability or drive strength [-]

W Transistor's width [nm]

$W_{n,p}$  n and pMOS transistor's width [nm]

(W/L) Device's aspect ratio [-]

$\bar{\mu}$  Carrier mean mobility  $[cm^2/V \cdot s]$

$\lambda$  Mean separation distance between  $\bar{e}/h$  pairs [nm]

# LIST OF FIGURES

| Figure 1.1            | Thesis organization and contributions                                                                             | .28 |

|-----------------------|-------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2.1            | Electron/hole pairs production                                                                                    | .32 |

| Figure 2.2            | Stopping power for electrons and protons on silicon.                                                              | .33 |

| Figure 2.3            | Ion path components and the related transient current pulse                                                       |     |

| Figure 2.4            | Energy band diagram for charge generation and its transport in $SiO_2$                                            |     |

| Figure 2.5            | $I_D$ vs. $V_{GS}$ for n,pMOS devices pre- and post-irradiation                                                   |     |

| Figure 2.6            | $\Delta V_{th}$ for n,pMOS devices pre- and post-irradiation                                                      |     |

| Figure 3.1            | Quantitative insight of hardness degrees                                                                          | .41 |

| Figure 3.2            | Mitigation techniques embedded at different abstraction levels                                                    |     |

| Figure 3.3            | Representative cross section of leakage current paths                                                             | .43 |

| Figure 3.4            | Guard rings layout examples for n,pMOS devices                                                                    | .44 |

| Figure 3.5            | Summary of Enclosed gate geometries                                                                               |     |

| Figure 3.6            | Electric field lines under the gate                                                                               |     |

| Figure 3.7            | (W/L) prediction methods from Anelli and Giraldo                                                                  |     |

| Figure 3.8            | (W/L) prediction methods from Xue and Chen                                                                        |     |

| Figure 3.9            | (W/L) prediction methods work's variables                                                                         |     |

| _                     | ELT Rectangular and its $(W/L)$ contributions                                                                     |     |

|                       | ELT Rectangular BC and its $(W/L)$ contributions                                                                  |     |

|                       | ELT and its $(W/L)$ contributions for all related methods                                                         |     |

|                       | $(W/L)_{eff}$ for RecBC and Rec devices                                                                           |     |

|                       | ~J J                                                                                                              |     |

|                       | Transfer function $(I_D \ vs. \ V_{DS})$ and space/charge distribution  Output conductance for TE and ELT devices |     |

| Figure 4.1            | LE variables of an Inverter cell                                                                                  | .60 |

| Figure 4.2            | Summary of the acquisition steps of the LE variables                                                              |     |

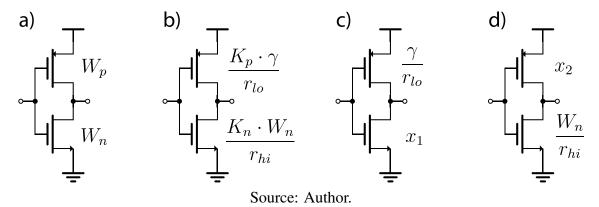

| Figure 4.3            | TB configurations for simulate $K_n(S)$                                                                           |     |

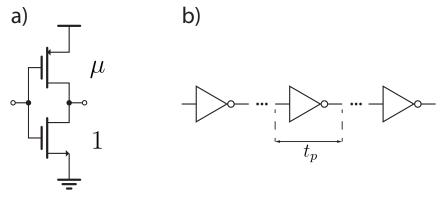

| Figure 4.4            | TB configurations for simulate $\mu$                                                                              |     |

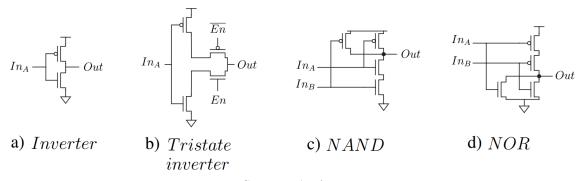

| Figure 4.5            | Schematic diagrams for combinational cells                                                                        |     |

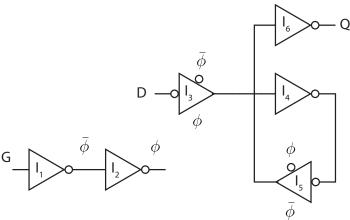

| Figure 4.6            | Schematic of a latch DLHQ                                                                                         |     |

| Figure 5.1 Figure 5.2 | Inverter cell configurations combining n,pSTD and n,pELT devices ELT when varying $X$ and $L$                     |     |

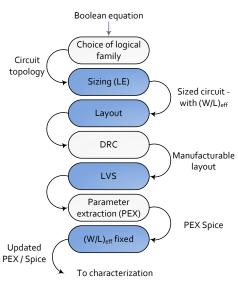

| Figure 6.1            | Bird's eye view of full-custom design flow                                                                        | .78 |

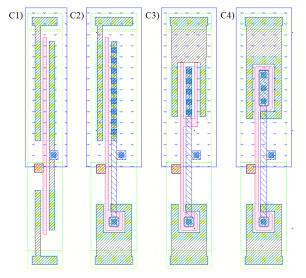

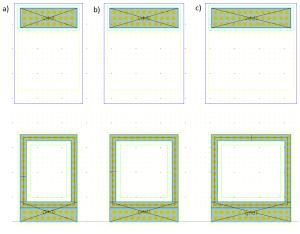

| Figure 6.2            | Template for digital cells                                                                                        | .80 |

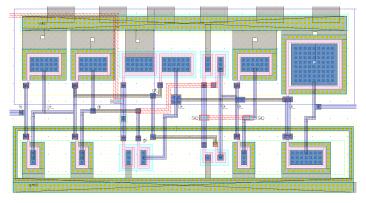

| Figure 6.3            | Template devices examples in 180 nm                                                                               | .81 |

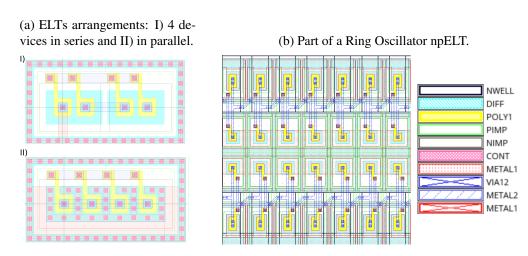

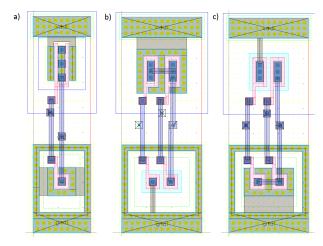

| Figure 6.4            | Digital cells INV, NAND and NOR                                                                                   |     |

| Figure 6.5            | Digital cell Latch (DLHQ)                                                                                         |     |

| Figure 6.6            | Ring Oscillators calibration test structures                                                                      |     |

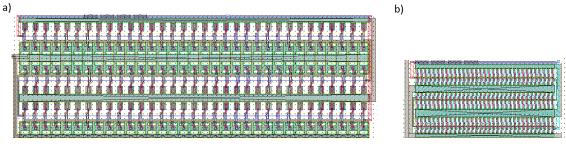

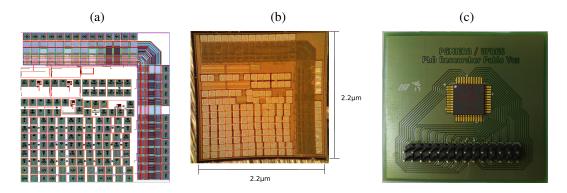

| Figure 7.1            | Layout, laid-out and final test chip in 600 nm                                                                    | .87 |

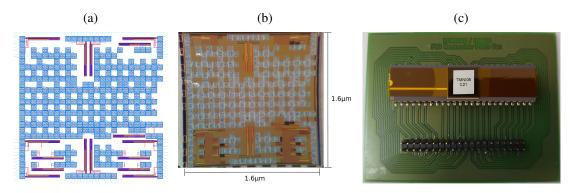

| Figure 7.2            | Layout, laid-out and final test chip in 180 nm                                                                    | .88 |

| Figure 8.1            | Output characteristic and transfer function in $180 \ nm$                                                         |     |

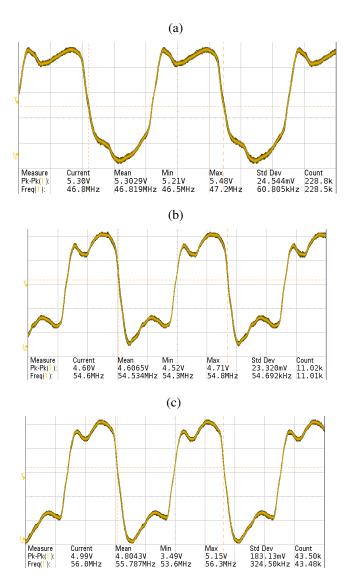

| Figure 8.2            | Ring Oscillators' output characteristics                                                                          |     |

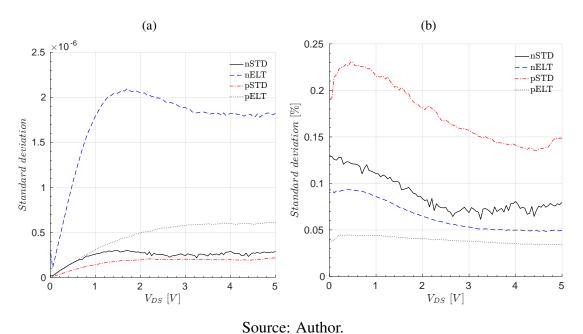

| Figure 8.3            | Standard deviation for output characteristic                                                                      |     |

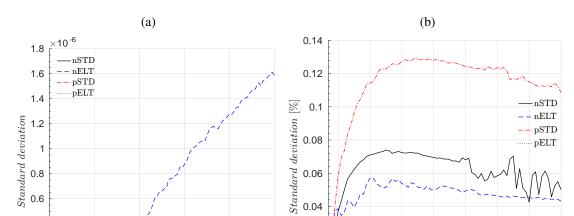

| Figure 8.4            | Standard deviation for transfer function                                                                          | .97 |

| Figure 8.5 | Output and transfer function characteristics for nMOS devices | 98  |

|------------|---------------------------------------------------------------|-----|

| Figure 8.6 | Output and transfer function characteristics for pMOS devices | 99  |

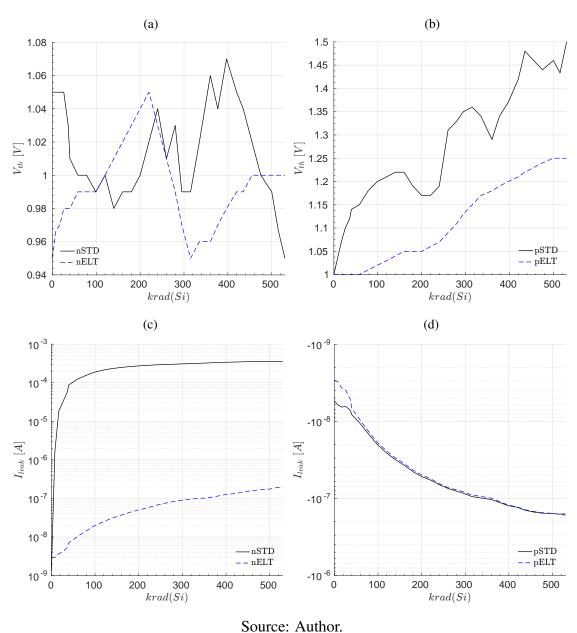

| Figure 8.7 | $V_{th}$ and $I_{leak}$ trends for n and pMOS devices         | 100 |

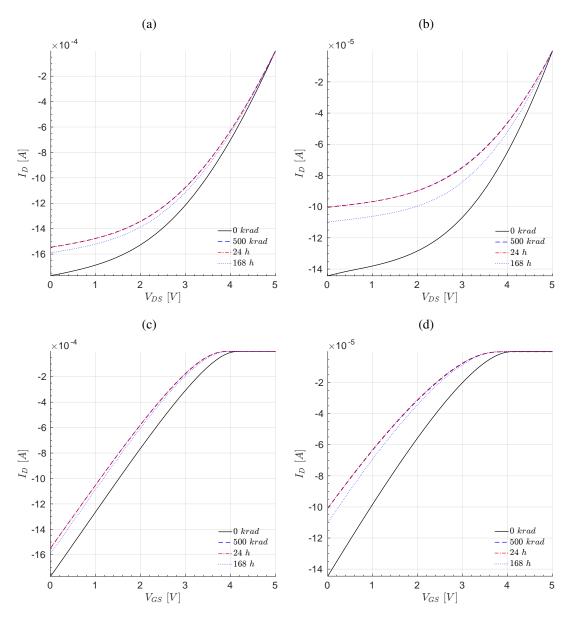

| Figure 8.8 | Annealing effects for pELT and pSTD                           | 101 |

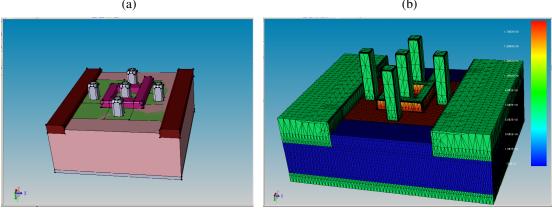

| Figure 9.1 | TCAD ELT doping profile                                       | 108 |

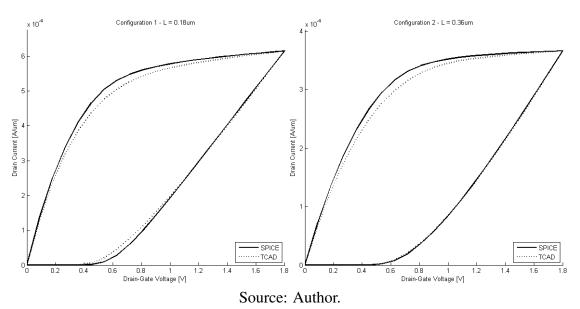

| Figure 9.2 | TCAD versus SPICE simulation results for an ELT device        | 108 |

# LIST OF TABLES

| Table 2.1  | $\bar{e}/h$ pairs generation energies, densities and pair densities    | 34 |

|------------|------------------------------------------------------------------------|----|

| Table 4.1  | N,pMOS factors series.                                                 | 65 |

| Table 4.2  | Proposed Skew factors for standard HI and LO-Skew gates                |    |

| Table 5.1  | Simulated values for series factor $K_{n,p}(S)$ up to 4 series devices | 69 |

| Table 5.2  | Calculated $\gamma_{ideal}$ value.                                     | 69 |

| Table 5.3  | Test Bench related variables for 600 nm and 180 nm                     | 71 |

| Table 5.4  | Sim. results (Typical) of $X_{1,2}$ ELT-based INV cells in 600 $nm$    | 72 |

| Table 5.5  | Sim. results (Typical) of $X_{1,2}$ ELT-based INV cells in 180 $nm$    | 72 |

| Table 5.6  | Sim. results (Corners) of $X_1$ ELT-based INV cells in 600 $nm$        | 73 |

| Table 5.7  | Sim. results (Corners) of $X_1$ ELT-based INV cells in 180 $nm$        | 73 |

| Table 5.8  | Sim. results (Monte Carlo) of $X_1$ ELT-based INV cells in 600 $nm$    | 74 |

| Table 5.9  | Sim. results (Monte Carlo) of $X_1$ ELT-based INV cells in 180 $nm$    | 74 |

| Table 5.10 | Simulation frequency for Ring oscillators                              |    |

| Table 6.1  | RHBD core cells                                                        | 82 |

| Table 8.1  | Difference between sim. and meas. $I_D$ values for n,pSTD devices      | 90 |

| Table 8.2  | RMS Difference for individual nELT devices                             | 91 |

| Table 8.3  | RMS Difference for series n,pELT devices                               | 92 |

| Table 8.4  | RMS Difference for parallel n,pELT devices                             |    |

| Table 8.5  | Ring oscillators frequency comparison                                  |    |

| Table 8.6  | Values for standard deviation.                                         |    |

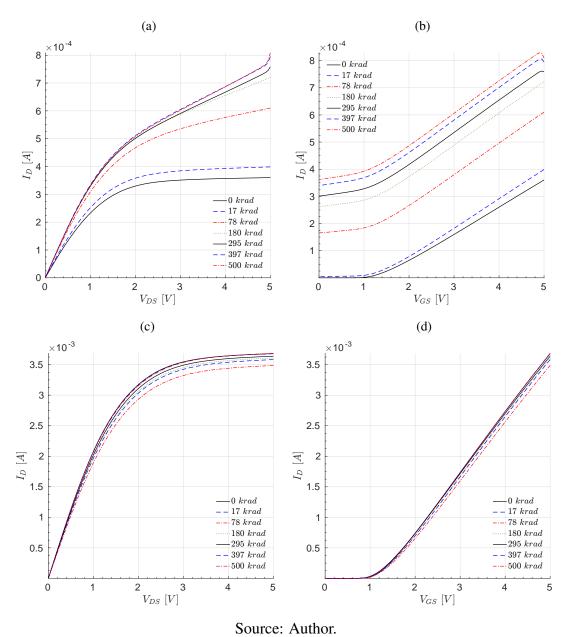

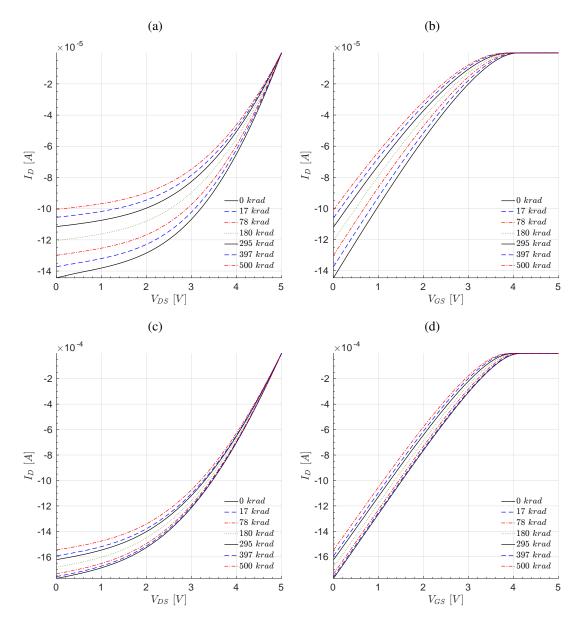

| Table 8.7  | TID values for $I_D$ $vs.$ $V_{DS,GS}$ for n,pMOS devices              | 98 |

|            |                                                                        |    |

# **CONTENTS**

| 1 INTR | ODUCTION                                                | 25 |

|--------|---------------------------------------------------------|----|

| 1.1    | Motivation                                              | 25 |

| 1.2    | Thesis structure and contributions                      | 26 |

| 1.3    | Important information                                   | 28 |

| 2 IONI | ZING RADIATION BASIC PHENOMENA AND DEFINITIONS          | 31 |

| 2.1    | Introduction                                            | 31 |

| 2.2    | Single Event Effects (SEE)                              | 32 |

| 2.3    | Total Ionizing Dose (TID)                               | 36 |

| 2.4    | Summary and Discussion                                  | 38 |

| 3 RHB  | D LAYOUT TECHNIQUES                                     | 41 |

| 3.1    | Introduction                                            | 41 |

| 3.2    | Guard Rings                                             | 43 |

| 3.3    | Enclosed Layout Transistor (ELT)                        | 44 |

|        | 3.3.1 Effective $(W/L)$ aspect ratio prediction problem | 46 |

|        | 3.3.2 Effective $(W/L)$ aspect ratio prediction methods | 46 |

|        | 3.3.3 Effective $(W/L)$ aspect ratio limitations        | 52 |

|        | 3.3.4 Source/drain asymmetry                            | 52 |

| 3.4    | Summary and Discussion                                  | 55 |

| 4 SCHI | EMATIC DESIGN FLOW PROPOSAL                             | 59 |

| 4.1    | Introduction                                            | 59 |

| 4.2    | Deriving Logical Effort equations                       | 59 |

|        | 4.2.1 Assigning input variables                         | 63 |

| 4.3    | Combinational logic cells                               | 64 |

| 4.4    | Multi-stage and best number of stages                   | 65 |

| 4.5    | Sequential logic cells                                  | 66 |

| 4.6    | Summary and Discussion                                  | 67 |

| 5 ELEC | CTRIC LEVEL SIMULATIONS PROPOSAL                        | 69 |

| 5.1    | Introduction                                            | 69 |

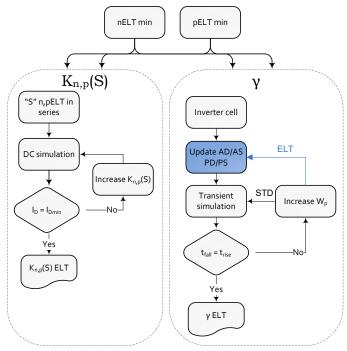

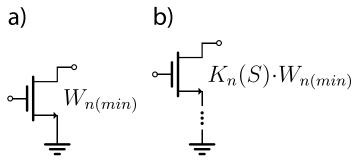

| 5.2    | Simulation of assigned input variables                  | 69 |

|        | 5.2.1 $K_{n,p}(S)$ and $\gamma_{ideal}$                 | 69 |

| 5.3    | Core digital logic cells                                | 70 |

|        | 5.3.1 Inverter cells                                    | 70 |

|       | 5.3.2  | Ring oscillators                  | 75  |

|-------|--------|-----------------------------------|-----|

| 5.4   | Sumr   | nary and Discussion               | 75  |

| 6 PHY | SICAL  | DESIGN FLOW PROPOSAL              | 77  |

| 6.1   | Intro  | duction                           | 77  |

| 6.2   | Desig  | n flow diagram                    | 77  |

| 6.3   | Temp   | late                              | 80  |

| 6.4   | Digita | al cells                          | 82  |

| 6.5   | Sumr   | nary and Discussion               | 83  |

| 7 TES | Γ STRI | UCTURES                           | 85  |

| 7.1   | Intro  | duction                           | 85  |

| 7.2   | Desig  | ned devices and cells             | 86  |

| 7.3   | Tape-  | out                               | 87  |

| 7.4   | Sumr   | nary and Discussion               | 88  |

| 8 EXP | ERIMI  | ENTAL RESULTS                     | 89  |

| 8.1   | Intro  | duction                           | 89  |

| 8.2   | Pre-ii | radiation                         | 89  |

|       | 8.2.1  | Introduction                      | 89  |

|       | 8.2.2  | Individual transistors            | 90  |

|       | 8.2.3  | Series and parallel arrangements  | 91  |

|       | 8.2.4  | Ring Oscillator                   | 92  |

|       | 8.2.5  | Summary and Discussion            | 93  |

| 8.3   | Durir  | ng and post irradiation           | 94  |

|       | 8.3.1  | Introduction                      | 94  |

|       | 8.3.2  | Measured data (600 nm)            | 96  |

|       | 8.3.3  | Summary and Discussion            | 100 |

| 9 CON | CLUS   | ION                               | 105 |

| 9.1   | Final  | discussion                        | 105 |

| 9.2   | Futui  | e works                           | 107 |

| REFE  | RENCI  | ES                                | 111 |

| APPE  | NDIX A | A — SUMMARY IN PORTUGUESE         | 117 |

| A.1   | Intro  | duçãodução                        | 117 |

|       | A.1.1  | Motivação                         | 117 |

|       | A.1.2  | Estrutura da tese e contribuições | 119 |

|       | A.1.3  | Informações importantes           | 120 |

| <b>A.2</b> | Conclusão                | 120 |

|------------|--------------------------|-----|

|            | A.2.1 Discussão final    | 120 |

|            | A.2.2 Trabalhos futuros. | 123 |

## 1 INTRODUCTION

#### 1.1 Motivation

When observing the success of CMOS technology, it is indubitably necessary to refer to the steady progression of technology scaling. The aggressive increase at an integration level has lead the semiconductor industry to a vertiginous rise, improving Integrated Circuits (ICs) functions and resources in the process (PELLISH, 2012).

To synthesize complex circuits, which demand a huge number of functions and resources (e.g., microprocessors or Application-Specific Integrated Circuits - ASICs), the use of a design flow automation is inherently necessary to reduce design time and production costs. The core of this process is a group of digital cells pre-designed and properly characterized named digital library. These cells are the effective link between Computed Aided Design (CAD) tools, which allow a high-level description of the system (coded in a hardware language, such as VHDL or Verilog), and the actual physical implementation of the system (SCHUCH et al., 2009).

Nonetheless, the incidence of ionizing radiation may result in undesirable effects in the ICs, such as upset and even permanent damage to the device's materials. Therefore, applications exposed to a radioactive environment may behave unpredictably, reducing reliability and expected lifetime (LIU et al., 2014b; KNUDSEN; CLARK, 2006).

Ground-level applications are naturally less susceptible to the incidence of ionizing radiation when compared to Aeronautics and Space & Satellite (S&S) devices, mostly due to the Earth's natural magnetic shielding. The magnetic field traps incoming ionizing particles, especially those ejected from the solar coronal mass, giving rise to radiation belts known as Van Allen belts. However, not only space applications, but also on a ground-level ones, High Energy Physics (HEP) experiments are severely affected by ionizing radiation (VELAZCO et al., 2007, BOUDENOT in).

The robust physical design proposal referred to as Radiation-Hardening by Design (RHBD) provides the possibility to achieve higher levels of tolerance to accumulated effects of ionizing radiation. By employing RHBD techniques it is possible to mitigate even Total Ionizing Dose (TID) or Single Event Effects (SEE) through a combination of layout and design hardening techniques (KNUDSEN; CLARK, 2006). In the context of design flow automation, the main issue lies in the fact that cell libraries employing RHBD techniques are not commercially available being, therefore, proprietary IPs subject

to territorial regulations (CHANG et al., 2014).

While HEP, S&S, reliable control systems and deep space exploration have been studied and supported in other countries (such as USA, China and France) (YIN et al., 2016), here in Brazil they are a relatively recent field of study. In our context (ICs R&D industry in Brazil), the knowledge to design such hardened devices has been a growing interest in the last few years, even in cases where there are no embargoes regarding International Traffic in Arms Regulation (ITAR). Brazil buys these IPs but does not produce it and, over time, the lack of this technology not only usurps R&D opportunities but also drastically increases the costs of buying hardened and reliable circuits.

Therefore, aiming to provide radiation-tolerant ICs, this thesis presents a methodology to develop RHBD cell libraries in bulk CMOS technology, using real world constraints. In this sense, state-of-the-art improvements to key points of the ICs design flow are proposed: the analysis and implementation of core models to predict the device's effective (W/L) aspect ratio; and the design of library cells based on full-custom analog optimizations, generating the necessary characterization files, completely compatible with commercial design flow. These contributions are crucial to improve the ability of the Brazilian semiconductor industry to tape-out RHBD circuits.

Nonetheless, despite all technical analyses and advancements, I conceive that the major contribution of this thesis, which has required great effort (and some experience), was to assemble all the knowledge from the first steps of design (i.e., the layout transistor) to the final steps (i.e., final tape-out of digital cells).

Furthermore, this thesis applies all the RHBD techniques to technology nodes available in the Brazilian semiconductor industry, enabling the whole chain of production to fully incorporate Register Transfer Level (RTL) to the automated design flow of Graphic Database System (GDSII).

#### 1.2 Thesis structure and contributions

Figure 1.1 illustrates the structure of this thesis, highlighting the original aspects and analyses presented throughout this work.

Colored in light green are the sections (or subsections) in which I gave minor contributions, considering original analysis, new data or minor adjustments in equations' parameters. Colored in dark green are the most important contributions of this thesis, i.e., the areas that play a key role in this work, aiming to advance the state-of-the-art (in terms

of what is available in the literature), establishing a solid link throughout all design flow steps.

Following these criteria, after this introduction, Chapter 2 introduces the basic concepts related to the interaction of ionizing radiation with matter. Chapter 3 discusses some hardening techniques, which can be applied through all circuit abstraction levels, under a commercially available fabrication process, facing emblematic challenges of the most common (and effective) employed techniques. Besides, minor expansion in related  $(W/L)_{eff}$  predictive equations are proposed (and validated through analysis and simulations) in order to enlighten, and ease, the acquisition of aspect ratios for non-square gate geometries.

Chapter 4 proposes a generalization of the well know Logical Effort method (LE), which takes into account all design variables at the same equation allowing the automation of gate size calculation for n-and p-MOS transistors, and also the PN aspect ratio for the least average delay. Chapter 5 explores the electrical level simulations of digital cells based on enclosed gate topology through their small and large signal behaviors. Chapter 6 presents and explains the proposed design flow methodology. Chapter 7 introduces the laid out test structures in technology nodes of 600 nm and 180 nm, aiming to validate the proposed methodology. Chapter 8 presents the pre- and post-irradiation experimental results and, finally, Chapter 9 provides the conclusions and final remarks.

Figure 1.1: Thesis organization and contributions.

Source: Author.

# 1.3 Important information

In order to be used in the present work, terms related to ionizing radiation, and space projects and applications follow the standards provided by European Cooperation for Space Standardization (ECSS) (ECSS, 2004).

The preceding terms referred as qualified or hardened device means that device is

designed to properly operate between acceptable error margins (i.e., failure tolerance), with the ability to fulfill specified requirements taking into account the environment specification for baseline application given a time interval. Moreover, the preceding term *mitigation* refers to attenuation or reduction of the impact of the related phenomena, making it less severe.

The compendium of design-oriented *mitigation* and *hardening techniques*, the focus of this work, is proposed in order to substantially reduce the ionizing radiation effects in bulk CMOS. And, for this reason, the origin of the term *Radiation-Hardening by Design* (RHBD).

## 2 IONIZING RADIATION BASIC PHENOMENA AND DEFINITIONS

# 2.1 Introduction

The transmission of energy in the form of particles or waves through space or matter is defined as radiation. Moreover, when radiation particles travel through solid materials transferring kinetic energy to atomic electrons, causing them to be liberated (ionized), they are defined as ionizing radiation (FB, 1987).

In the context of integrated circuits, there is a plethora of ionizing particles capable of carrying enough energy to disrupt electric atomic bound, spanning from  $\alpha$ -particles to  $\gamma$ - and X-rays (SEONG, 2008). The former ( $\alpha$ -particles) are commonly related to metal interconnecting layers as  $P_b/S_n$  solder balls and Uranium ( $^{238}U$ ) and Thorium ( $^{232}Th$ ), which may be presented in device packaging process (ROCKETT, 2004; SEONG, 2008); and the latter ( $\gamma$ - and X-rays), due to their higher energy, are predominantly referred to space radiation environment, and consequently being a particular issue to space and satellite applications.

The interaction of ionizing radiation with matter produces a plasma-like track composed by electron-hole pairs ( $\bar{e}/h$ ) in the shape of a cylindrical funnel with a radius in the order of 1  $\mu m$  or even less (OHRING, 1998; ROCKETT, 2004). Additionally, for heavy ions, this damage may slightly vary depending on the mass, charge and kinetic energy of the incident particle and the mass, charge, and density of the target material (FB, 1987; SEONG, 2008).

After the generation, the natural process is a rearrangement of these charges in such a way that free electrons and holes recombine themselves. Indeed, in an unbiased device (i.e., when no external electric field is applied) in a few picoseconds 80% to 90% of these pairs effectively recombine (ANELLI, 2000; VAZ, 2015). In fact, the recombination of charges vary depending on the resistance of the materials: higher recombination rates are observed in materials with lower resistances (VAZ, 2015).

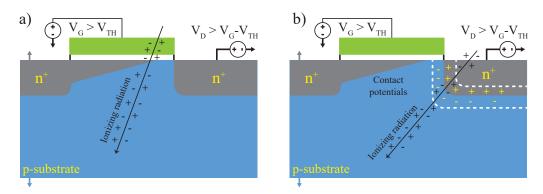

In bulk CMOS transistors, due to the applied electric fields, the generation of  $\bar{e}/h$  pairs is a concern not only in reverse-biased PN junctions, Figure 2.1 (b), but also in silicon dioxide ( $SiO_2$ ) regions (a) (ANDREOU et al., 2015).

In these particular regions, hereafter named as *sensitive regions*, the movement of charges, accordingly to the electric field they experiment, give rise to transient upsets or permanent damages both for analog and digital circuit operations.

Figure 2.1: Electron/hole pairs production through: a) gate oxide region  $(SiO_2)$ , and b) reversely biased PN junction.

Source: Author.

When the observed or measurable changes in the device's response are caused by a single energetic particle, the effect is defined as Single Event Effect (SEE). On the other hand, the accumulation and long term degradation of changes in semiconductor materials and devices performance is categorized as Total Ionizing Dose effect (TID) (MUNTEANU; AUTRAN, 2008).

The former effect is caused mainly due to heavy charged particles (protons, alpha, and other ions) and the second one is produced, directly and indirectly, by all ionizing radiations (X- and  $\gamma$  rays, electrons, neutrons, protons,  $\alpha$  and other heavy ions).

# 2.2 Single Event Effects (SEE)

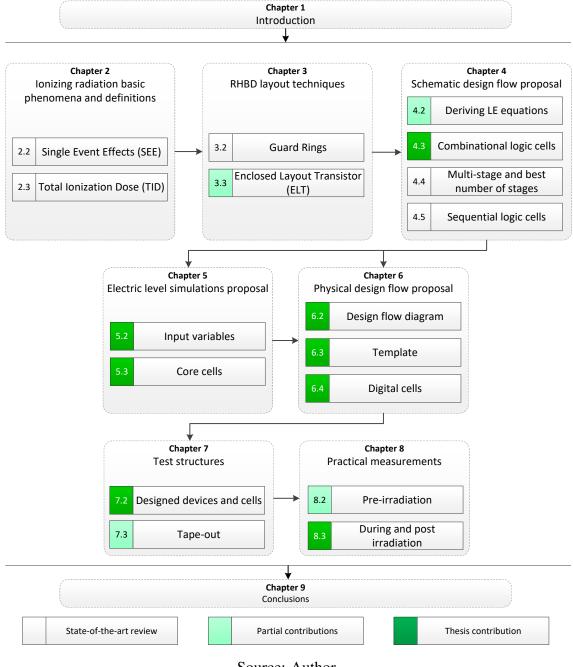

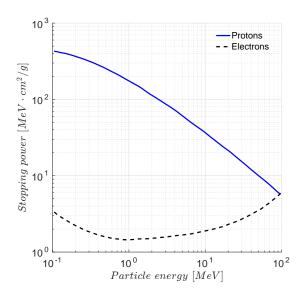

Whilst the incident ion crosses the device's material, it loses its energy by the Linear Energy Transfer mechanism (LET), also referred as medium *stopping power*. The LET describes the amount of energy that goes into ionization, in other words, the energy deposited in the target material per unit length of the ion path, expressed in terms of  $(MeV \cdot cm^2/g)$ , according to:

$$LET = \left(\frac{1}{\rho} \cdot \frac{\partial E}{\partial x}\right),\tag{2.1}$$

where  $\rho$  is the material density in  $(g/cm^3)$  (FB, 1987). The Figure 2.2 shows the stopping power for incident protons and electrons on silicon material (FB, 1987; SROUR, 1982).

Figure 2.2: Stopping power for electrons and protons on silicon.

Source: Plotted data acquired from (SROUR, 1982).

The energy deposited per gram of material is called absorbed ionized dose (D) and its SI unit is the gray (Gy). Although the radiation effects community historically adopted the unit rad (acronym for radiation absorbed dose), which is equal to:

$$1(Gy) = 1 \cdot \left(\frac{J}{Kg}\right) = 100(rad) = 6.24 \cdot 10^{15} \cdot \left(\frac{eV}{g}\right). \tag{2.2}$$

Moreover, while the energy loss depends on the mass of the target material, it must be specified as rad (Si) or rad  $(SiO_2)$ , for example. For this purpose, considering the materials commonly used in bulk CMOS technology, the conversion factor presented in 2.3 can be used (SROUR, 1982).

$$1 \cdot rad(Si) = 0.58 \cdot rad(SiO_2) = 0.94 \cdot rad(GaAs) \tag{2.3}$$

It is worth to note that is possible to obtain the number of generated  $\bar{e}/h$  pairs by dividing the deposited energy into the energy necessary to create each  $\bar{e}/h$  pair and multiply by the material density. The Table 2.1 summarizes these aforementioned parameters for commonly employed MOS materials (SROUR, 1982; ANELLI, 2000; OLDHAM; MCLEAN, 2003).

| Table 2.1: Materials and related electron-hole | e pairs generation energies. | , densities and pair |

|------------------------------------------------|------------------------------|----------------------|

| densities*.                                    |                              |                      |

| Material                  | Pair generation          | Density (P) | Pair density generated       |  |

|---------------------------|--------------------------|-------------|------------------------------|--|

|                           | energy $(E_{eh})$ $(eV)$ | $(g/cm^3)$  | per $rad (g_0) (pairs/cm^3)$ |  |

| Si - Silicon              | 3.6                      | 2.328       | $4.0 \cdot 10^{13}$          |  |

| $SiO_2$ - Silicon Dioxide | 17                       | 2.2         | $8.1\cdot10^{12}$            |  |

| GaAs - Galium Arsenide    | 4.8                      | 5.32        | $7.0\cdot10^{13}$            |  |

| Ge - Germanium            | 2.8                      | 5.38        | $1.2\cdot 10^{14}$           |  |

<sup>\*</sup> Complemented data from (FB, 1987; PELLISH, 2012).

In silicon dioxide, the thermalization distance (i.e., the initial separation between a hole and its corresponding electron of the same pair after they reach thermal energy) is evaluated to be ranging from 5~nm to 10~nm with the average of about 8~nm (FB, 1987; ANELLI, 2000). Also, the mean separation distance between  $\bar{e}/h$  pairs ( $\lambda$ ) is inversely proportional to the LET. With the aim of quantifying its order of magnitude, works such as (FB, 1987; ANELLI, 2000) point out for a LET of  $100~MeV \cdot cm^2/g$  a  $\lambda \approx 1~nm$  and for a LET of  $10~MeV \cdot cm^2/g$  a  $\lambda \approx 10~nm$ , which in terms of capacitance per unit length was calculated as  $100~MeV \cdot cm^2/mg \approx 1~pC/\mu m$  in silicon (MUNTEANU; AUTRAN, 2008).

For an in-depth view on the methods to investigate  $\lambda$  distances, I invite the reader to first consult *Columnar* and *Geminate* models (ANELLI, 2000; FB, 1987; SROUR, 1982).

Due to direct interactions, the first amount of energy is converted into  $\bar{e}/h$  pairs. Due to indirect interactions, the remaining energy is converted into heat, and a very small quantity into atoms displacement (MUNTEANU; AUTRAN, 2008).

The displacement of atoms disarranges the original structure of the crystal lattice by knocking an atom from its lattice site, giving rise to displacement damage (DD). Nonetheless, the rate of energy deposited during this process is more than three orders of magnitude lower than in SEE, or in TID (SROUR; MCGARRITY, 1988). For this reason, this work is focused on SEE and TID effects. For more information on DD, check (CLAEYS; SIMOEN, 2002; SROUR; MCGARRITY, 1988).

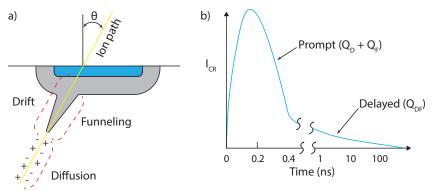

According to Fig. 2.3 (a), the plasma-like track, originated by ion interaction in a reverse biased PN junction, distorts the depletion layer in the metallurgical junction in such a way that it propels equipotential regions into a form of cylindrical funnel, which has duration of the order of  $1 \, ns$  or less (ROCKETT, 2004). In these regions, the higher electric

field moves electrons to the depletion layer and the holes to the silicon bulk (OHRING, 1998), causing an additional transient current pulse (ICR), whose behavior is illustrated in Fig. 2.3 (b).

Figure 2.3: a) The ion path. b) The main funnel components and the related transient current pulse.

Source: Adapted from (ROCKETT, 2004).

According to the literature, the post interaction of high-energy particle with MOS devices, in the sensitive regions, is usually analyzed by the sum of drift (or conduction component) and diffusion component (MUNTEANU; AUTRAN, 2008; ROCKETT, 2004), pointed out in Fig. 2.3 (a). The integral over time of this transient current, expressed in (2.4), gives the total spurious charge in the silicon structure (Qt) (BARTRA; REIS, 2014),

$$Q_t = \int_0^\infty I_0 \left( e^{-t/\tau_f} - e^{-t/\tau_r} \right) dt,$$

(2.4)

with

$$I_0 = q \cdot \bar{\mu} \cdot N \cdot E_0 \cdot \sec \theta$$

, (2.5)

and

$$\tau_f = \left[\bar{\mu} \cdot \frac{\partial E}{\partial X}\right]^{-1}$$

. (2.6)

Where  $I_0$  is the current generated by the charges;  $\tau_r$  and  $\tau_f$  are the rise/fall time of transient current, respectively; q is the electron charge;  $\bar{\mu}$  is the mean carrier mobility; E and  $E_0$  are, respectively, the electric field and its value at position X=0, and  $\theta$  the incident ion hit angle, depicted in Fig. 2.3 (a).

Finally, there are two main metrics to qualify SEEs: the minimum amount of charge necessary to induce an upset  $(Q_{crit})$ , and the rate at which occurs an upset, referred as Failure in Time (FIT), expressed in number of failures per  $10^9$  hours of operation

(MUNTEANU; AUTRAN, 2008).

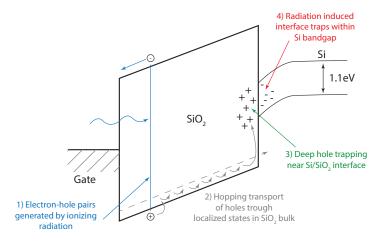

## 2.3 Total Ionizing Dose (TID)

For TID effect, the cause is fundamentally the same as for SEEs, i.e., the generation of electron and hole pairs. Yet, in this case, it's a long-term and cumulative effect. While the ionizing radiation hits the oxide regions, such as the gate-oxide  $(SiO_2)$ , the electric field, inherently existent due to device bias, may disrupt electronic bounds transporting the generated carriers. Through this process, as depicted in Fig. 2.4, the electrons, which have a higher mobility, ( $\approx 20 \ cm^2/V \cdot s$ ) are removed from the dielectric, leaving the less mobile holes ( $\approx 2 \cdot 10^{-5} \ cm^2/V \cdot s$ ) in the oxide (SROUR, 1982; OLDHAM et al., 1987; SROUR; MCGARRITY, 1988; ANDREOU et al., 2015; VAZ; WIRTH, 2015).

Figure 2.4: Energy band diagram for charge generation and charge transport in  $SiO_2$ .

Source: Adapted from (ANDREOU et al., 2015).

The holes within  $SiO_2$  experiment a stochastic hopping transport through localized states toward the cathode direction, until they become trapped near the  $SiO_2/Si$  interface. This positive (and accumulated) charge near the interface between the dielectric and silicon bulk may consequently induce the formation of an inversion layer in the channel region (ANDREOU et al., 2015).

The presence of this positive parasitic charge has observable effects, such as a threshold voltage shift for the device (SROUR, 1982; OLDHAM et al., 1987), increasing the subthreshold voltage swing (MCLAIN et al., 2009) and the leakage current (intra-and inter-device) (SROUR, 1982; VAZ; WIRTH, 2015; OLDHAM et al., 1987; VAZ, 2015; CLAEYS; SIMOEN, 2004), reducing mobility (CLAEYS; SIMOEN, 2004), and

increasing flicker noise (ANELLI, 2000; VAZ, 2015).

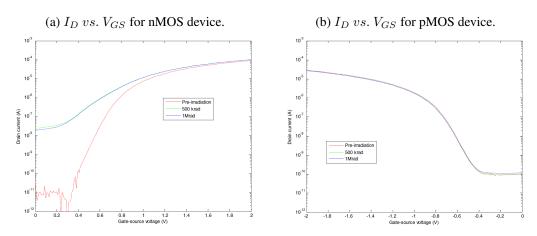

Figure 2.5 shows an example of the transfer function  $(I_D \ vs. \ V_{GS})$  for n and pMOS devices designed with minimum DRC features (in referred case  $W=L=0.42\ \mu m$ ) (GREIG et al., 2013). The presented cases are shown in typical conditions for pre- and post-irradiation up to  $500\ krad$  and  $1\ Mrad$ . As can be observed, the effect of increase in leakage current is much more prominent in nMOS (index (a)) than in pMOS devices (index (b)) since the accumulation of positive charge has a negative (decreasing) impact on leakage current (ANELLI, 2000).

Figure 2.5: Transfer function  $(I_D \ vs. \ V_{GS})$  for n,pMOS devices in typical conditions (pre-irradiated and post-irradiated up to  $500 \ krad$  and  $1 \ Mrad$ ).

Source: From (GREIG et al., 2013).

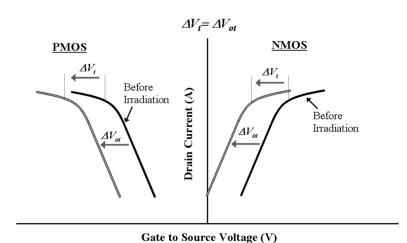

In the perspective of  $\Delta V_{th}$  the shift occurs in a negative way; analyzing Fig. 2.6, which exhibits the output DC characteristic  $(I_D \ vs. \ V_{GS})$  for both n,pMOS devices (BARNABY, 2006). In other words, for a fixed  $I_D$ , the irradiation tends to lead the  $V_{GS}$  to a more negative value.

The transistor scaling reduces the dielectric volumes so the total amount of parasitic trapped charge is reduced as well. Therefore, the scaling down of device geometries intrinsically reduces the threshold voltage deviations ( $\Delta V_{th}$ ). Related works (SAKS; ANCONA; MODOLO, 1984) suggest that oxide thickness ( $t_{ox}$ ) above 20 nm has a quadratic dependence on  $\Delta V_{th}$  (i.e.,  $\Delta V_{th} \propto t_{ox}^2$ ), rapidly decreasing otherwise, (i.e.,  $\Delta V_{th} \propto t_{ox}^n$  with n > 2).

Nonetheless, despite quantum tunneling effect (in which the holes are removed outside oxide volumes (BENEDETTO et al., 1985)), the literature addresses that for  $t_{ox}$  below 2.2~nm (which occurs in gate lengths of about 240~nm) the  $\Delta V_{th}$  related to ionizing radiation can be neglected (FACCIO et al., 2008; KLOUKINAS et al., 1998).

Figure 2.6: Threshold voltage deviation for n,pMOS devices before and after irradiation.

Source: From (BARNABY, 2006).

As a final consideration, for large dose rates, i.e., near than  $1 \ Mrad(SiO_2)$  the number of trapped holes tends to saturate (FB, 1987). For such doses, in case of n-channel devices, by expanding the behavior illustrated by Fig. 2.6 a turnaround in threshold voltage deviation is observed.

Thus, a "shifting back" in the positive  $V_{th}$  direction occurs at increasing dose levels. For p-channel devices, negative biased at  $V_{GS}$ , the interface trapped charge continues increasing, and, therefore, continuing with a negative shift in its  $V_{th}$ .

To a more detailed physical phenomena involved for large dose rates, I invite the reader to consult (FB, 1987).

## 2.4 Summary and Discussion

This Chapter briefly introduced the basic concepts related to the interaction of ionizing radiation with bulk CMOS materials, discussing how it affects their characteristics as a consequence of generated  $\bar{e}/h$  pairs along its trajectory.

Depending on the energy of the incident particle or whether the device is in a long term exposure to such ions, two main types of effects may occur; a transient upset (i.e., a momentary voltage spike) at certain device's regions, or even permanent damages when occurring permanent changes in their physical components.

Indeed, the most sensitive regions to radiation effects that primarily cause failures on MOS devices are the insulating layers and the reversely biased PN junctions. Where even the accumulation of trapped charges or its migration degrade device's parameters

reducing its reliability and expected lifetime.

In the next Chapter, it is discussed how to improve the radiation tolerance of MOS devices laid out in a commercial fabrication process.

# **3 RHBD LAYOUT TECHNIQUES**

#### 3.1 Introduction

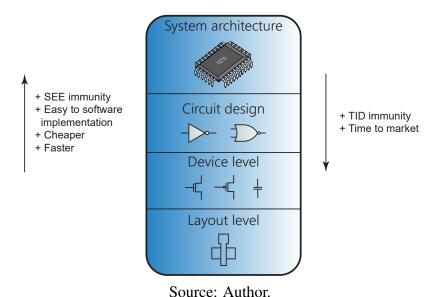

As illustrated in Fig. 3.1, RHBD mitigation techniques can be applied through all circuit abstraction levels. In the figure, the left and right arrows represent what is better suited for each abstraction level in terms of RHBD techniques.

Figure 3.1: Quantitative insight of hardness degree in terms of circuit abstraction level.

For example, the left arrow indicates that higher abstraction levels tend to have cheaper and faster to implement solutions, since many techniques involve redundancies and voters schemes acting directly on RTL code, easily providing hardening against SEEs.

In contrast, the approach to hardening a circuit against TID, in a standard fabrication process, usually requires modifications at the layout level. Thus, requiring the post-fabrication and characterization of these hardened devices (i.e., the new proposals) in order to be further used in the design flow automation. This process increases design time, costs and, consequently, time to market.

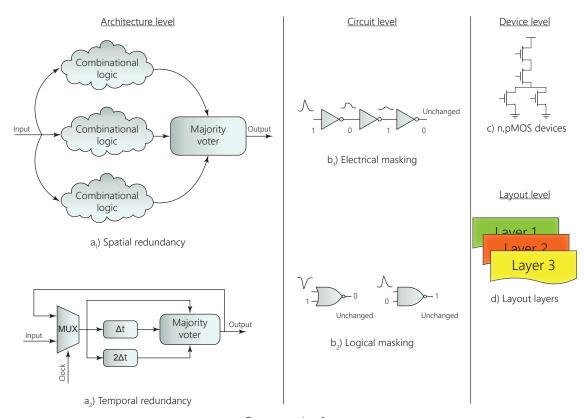

Figure 3.2 summarizes the most fundamental concepts involved in Radiation Hardening on the three major abstraction levels.

In case of spatial redundancy  $(a_1)$ , the key idea is that if any disturbances occur in a logic block, the parallel processing of the same signal promotes a majority vote between all outputs processed by other multiple physical instances. Besides, it is noteworthy that the voter ought be carefully designed to avoid propagating an error itself; as well as the

Figure 3.2: Summary of emblematic concepts of mitigation techniques embedded at different abstraction levels.

physical placement of these circuit copies should be laid out as far as possible from each other in order to reduce the probability of a double error occurrence (e.g., caused by a heavy ion crossing a large silicon area). To mitigate such an occurrence (i.e., when occurring multiple bit-flips), a temporal redundancy  $(a_2)$ , in which a signal delay (supposed to be in the order of strikes settle down  $\approx$  hundreds of ps), is proposed to guarantee that a single event does not induce a voting error.

At a circuit level, the electrical masking  $(b_1)$  attenuates the transient pulses with bandwidths higher than the CMOS cutoff frequency (i.e., transition frequency -  $f_T$ ), by reducing its amplitude until it, eventually, becomes a spurious signal that is neglected by the circuit (MUNTEANU; AUTRAN, 2008). Still at a circuit level, the logical masking  $(b_2)$  lies in the combinational logic *force* where, as exemplified by the NOR gate, the controlling state (i.e., one input tied to high -  $V_{DD}$ ) forces the output to be unchanged, independently of the other input signal (analogously, the same applies to other logic gates with equivalent truth table, as the NAND gate with one input tied to low -  $V_{SS}$ ) (MUNTEANU; AUTRAN, 2008).

On device level, a specific network arrangement can be adopted, i.e., a change

in the way of n,pMOS devices are connected to implement the same logic function (MUNTEANU; AUTRAN, 2008). Finally, proposing changes at the layout level, it is possible to substantially reduce not just SEEs, but also TID effects by avoiding critical sensitive regions responsible, for example, for the increase in the leakage current. This is discussed in the upcoming Sections 3.2 and 3.3.

## 3.2 Guard Rings

Submicron and deep submicron commercial CMOS technologies have reduced geometry volumes. In these technologies are observed smaller space/charge regions to collect, store, and process data. The movement of charges, in these reduced volumes, is deleterious when a device operates in higher frequencies. Thus, the leakage current has been the first addressed topic to be prevented (or reduced).

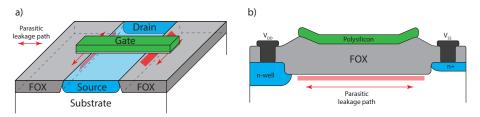

As depicted in Fig. 3.3 (a) and (b), the lateral field oxide (FOX) regions introduce susceptible areas for charge buildup when hole trapping occurs. In these regions, where the FOX lateral isolation, in LOCOS (or STI) process, experiment high mechanical stress, a leakage current path may form between the source and drain areas of the same device, as represented by the red regions in Fig. 3.3 (a); or between n-well layers of adjacent devices, depicted in (b).

Figure 3.3: Representative cross section of leakage current path between: a) source and drain of the same device (intra-device), and b) adjacent n-well regions of different devices (inter-device).

Source: Adapted from (LEE; LEE, 2013).

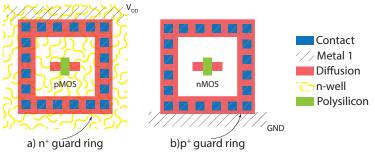

In these cases, considering standard commercial fabrication processes, the use of guard rings, Fig. 3.4, can substantially mitigate the leakage current underneath isolation oxides between adjacent devices and n-well layers (inter-device leakage), isolating all  $n^+$  diffusions that are at different potentials (MCLAIN et al., 2009; KLOUKINAS et al., 1998).

Figure 3.4: Guard rings layout example for: a) pMOS and b) nMOS devices.

## 3.3 Enclosed Layout Transistor (ELT)

For intra-device leakage path (i.e., the parasitic current which flows between the diffusion areas of an individual device), the proposal of an Enclosed Layout Transistor (ELT) entails the elimination of the transition region where the polysilicon layer extends over the well-to-substrate boundary, i.e., the red area in Fig. 3.3 (a), (ANELLI, 2000; MCLAIN et al., 2009; SNOEYS; GUTIERREZ; ANELLI, 2002).

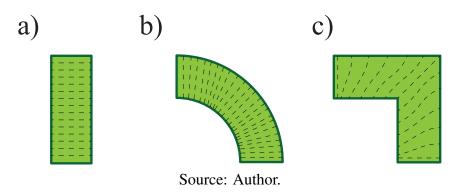

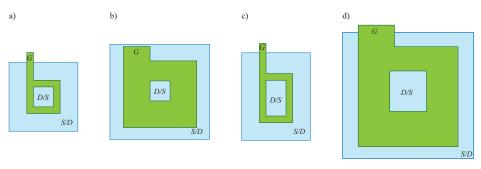

Under those circumstances, a myriad of possibilities exist for enclosing diffusion areas, allowing to eliminate leakage paths, as depicted in Fig. 3.5 from (a) to (f). These are some of the classical enclosed gate topologies, largely adopted in literature. Once literature is vast and some topologies may have slight variations, the classical topologies can be generally categorized as follows:

- a) <u>Circular (or Radial)</u>: (GIRALDO; PACCAGNELLA; MINZONI, 2000; LóPEZ et al., 2009)

- b) Rectangular (or Square): (GIRALDO; PACCAGNELLA; MINZONI, 2000; XUE et al., 2011)

- c) Rectangular Broken Corners (or Hexagonal; Annular): (ANELLI et al., 1999; ANELLI, 2000; GIRALDO; PACCAGNELLA; MINZONI, 2000; NOWLIN et al., 2005; CHEN; GINGRICH, 2005; MCLAIN et al., 2009; FLORES-NIGAGLIONI et al., 2015)

- d) Dog-bone: (SNOEYS; GUTIERREZ; ANELLI, 2002; LIMA, 2006)

- e) Ringed-source: (NOWLIN et al., 2005; MCLAIN et al., 2009; XUE et al., 2011)

- f) <u>Under-lap (or Dual-drain Ringed-source)</u>: (NOWLIN et al., 2005; MCLAIN et al., 2009)

a) d) b) S/D D/S D/SD/SS/D S/D S/D f) e) GG Gate area S/D Source/Drain D/S D/S S/D S/D S/D diffusion areas

Figure 3.5: Enclosed gate geometries named as: a) Circular, b) Rectangular, c) Rectangular Broken Corners, d) Dog-bone, e) Ringed-source, and f) Under-lap.

Source: Adapted and complemented from (MCLAIN et al., 2009).

Nonetheless, each topology has its own advantages and disadvantages. The Circular does not comply with many lithography processes; the Dog-bone has the largest area overhead; both Ringed-source & Under-lap require less area than the Dog-bone, but more area when compared to the Rectangular or even to the Rectangular Broken Corners.

In terms of gate style, considerable efforts have been done to investigate and characterize the layout geometry named as *diamond MOSFET* (GIMENEZ, 2016; SEIXAS et al., 2017; SEIXAS et al., 2019). In this structure, the gate is designed to use the corner effect in the longitudinal direction of the channel.

As authors suggest, this layout style has better electrical performance than standard devices and it is also capable to enhance its intrinsically TID tolerance. Nonetheless, in order to provide a more fairly comparison, this work focuses on clear *enclosed* gate disposals.

Thus, between the aforementioned geometries, which are widely investigated in the literature, this work adopted the Rectangular and Rectangular Broken Corners solutions. The main reasons for this choice are the fact that they tolerate doses up to  $30\ Mrad(SiO_2)$  (LEE; LEE, 2013); provide the possibility of a re-usable design (such as in Lambda units, scalable for different technology nodes); comply with the design rules of most, if not all, Process Design Kits (PDKs).

## **3.3.1** Effective (W/L) aspect ratio prediction problem

The classical gate topology, presented in Fig. 3.6 (a), which has single, straight polysilicon stripe, allows for a simple and direct acquisition of its width (W) and length (L), because the electric field is approximately uniform under the gate when the device is biased.

Figure 3.6: Electric field lines under the gate on topologies: a) Standard, b) Circular, and c) Rectangular.

In Circular geometries, shown in Fig. 3.6 (b), the uniform electric field under the gate allows for an analytical model of the (W/L) ratio of the transistor when, for instance, cylindrical coordinates are employed for basic long channel equations (GIRALDO; PACCAGNELLA; MINZONI, 2000).

Nonetheless, for other topologies, the acquisition of this ratio is not so trivial, mainly because there is not a clear physical equivalent to the width of the transistor, especially due to the electric field fringing effects when the gate has acute angles, as shown, for example, in Fig. 3.6 (c).

Nowadays, there are no available commercial Process Design Kits (PDKs) with native standard cells employing ELTs capable of performing an accurate prediction neither for W nor for L. Thus, the use of ELTs leads to challenges on the estimation of an effective (W/L) aspect ratio. Providing a reasonable estimation is a key factor in order to obtain an accurate transistor output and transfer the curves  $(I_D \ vs. \ V_{DS})$  and  $(I_D \ vs. \ V_{GS})$ .

# **3.3.2** Effective (W/L) aspect ratio prediction methods

Enclosed gate devices have been researched for decades. They were first proposed in the end of the 70's by the RCA Solid State Division (DINGWALL; STRICKER, 1977),

being called  $C^2L$  at the time. From that time, the technology scaling and the advances in modeling and simulation of integrated circuits, and components as well, have been leading us to a better understanding of the physical phenomena involved in ultra-scaled CMOS devices, such as quantum effects, tunneling current and ballistic operation (MUNTEANU; AUTRAN, 2008).

In this context, researchers have made a substantial contribution to the High Energy Physics community, which has investigated and characterized commercial devices under ionizing radiation (ANELLI, 2000).

In the field of RHBD, the works of Anelli and Giraldo (ANELLI et al., 1999; ANELLI, 2000; GIRALDO; PACCAGNELLA; MINZONI, 2000) were pioneers in the investigation of ELT device matching. Through several test chips, accurate models to predict the aspect ratio (W/L) were proposed for these devices.

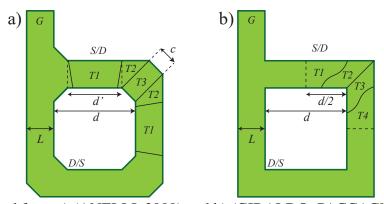

Based on these referred works, in order to provide an analytical methodology to calculate (W/L) in our case study, the gate structure was divided into linear contributions. Each of these parts with its own drain contribution, being the total (W/L) the sum of all individual parts, as shown in Fig. 3.7 (a) and (b) by transistors 1 to 3 (T1 to T3) and T1 to T4, respectively.

Figure 3.7: (W/L) prediction methods named as: a) Sum of parallel transistors and b) Edge and Corner transistors.

Source: Adapted from a) (ANELLI, 2000) and b) (GIRALDO; PACCAGNELLA; MINZONI, 2000).

In this methodology, the extraction of the experimental (or simulated) (W/L) values comes from the comparison of the  $I_D\ vs.\ V_{DS}$  characteristics between enclosed and standard devices with the same L (GIRALDO; PACCAGNELLA; MINZONI, 2000). Thus, the  $I_D$  expression can be calculated by integrating the resistance of the infinitesimal element along the channel on the hypothesis of current continuity (no generation or recombination inside the channel) and by integrating the electric field under the gate.

In the analytical model for rectangular devices, which has been derived from a 2-D analysis of the electric field magnitudes under the gate, the distribution of the electric field lines are obtained by solving the electrostatic equations in complex coordinates (through the conformal mapping method). The resulting electric field lines allow to separate the gate topology in several equivalent parts. After the decomposition, the polygonal regions were grouped together, assuming a similar behavior in the electric field lines, preserving the current continuity.

From this analysis, the integration of current contributions leads to equations (3.1) and (3.2) for Rectangular (Rec) and Rectangular Broken Corners (Rec BC) devices, respectively.

$$\left(\frac{W}{L}\right)_{eff}^{Rec.} = 4 \cdot 2 \cdot \left(\left(\frac{W}{L}\right)_{eff}^{T1} + \left(\frac{W}{L}\right)_{eff}^{T2}\right) \tag{3.1}$$

$$\left(\frac{W}{L}\right)_{eff}^{Rec.BC} = 4 \cdot \left(\frac{W}{L}\right)_{eff}^{T1} + 2 \cdot k \cdot \left(\frac{W}{L}\right)_{eff}^{T2} + 3 \cdot \left(\frac{W}{L}\right)_{eff}^{T3} \tag{3.2}$$

For a complete and more detailed explanation about the aforementioned methods, I invite the reader to consult the original references (ANELLI, 2000) for SPT and (GIRALDO; PACCAGNELLA; MINZONI, 2000) for ECT.

In the final analysis, it is noteworthy that the current of ECT method is only expressed in terms of T1 and T2 due to the symmetry. In the SPT, the parameter k is geometry dependent and has the value 3.5 for channel lengths smaller than  $0.5\mu m$  and the value 4 otherwise; and, the T3 contribution is only multiplied by 3 because the tail of the gate substantially reduces the drain current contribution at that point.

More recently, the model proposed by (XUE et al., 2011) introduces a computation inexpensive expression for (W/L). This model also computes the gate geometry as a sum of several parallel transistors, as shown in Fig. 3.8 (a) from S1 to S8 and modeled by 3.3. The value  $C_{ab}$  is an internal method's variable and represents the corner contribution which may vary with the down-scaling of the devices.

$$\left(\frac{W}{L}\right)_{eff} = \frac{2a_1 + 2a_2}{b} + C_{ab} \tag{3.3}$$

There are still some references with slight variations from (3.2) as in (CHEN;

Figure 3.8: (W/L) prediction methods from references: a) (XUE et al., 2011) and b) (CHEN; GINGRICH, 2005).

Source: Adapted from a) (XUE et al., 2011) and b) (CHEN; GINGRICH, 2005).

GINGRICH, 2005), show in Fig. 3.8 (b), in which the tail of the gate exists as a variable value (A). In this case, the constant term  $(2 \cdot k)$  preceding the contribution T2 in (3.2) is expressed as (K) in (3.4), which, on its turn, is given by K = 8 - A/L.

$$\left(\frac{W}{L}\right)_{eff}^{Rec.BC} = 4 \cdot \left(\frac{W}{L}\right)_{eff}^{T1} + K \cdot \left(\frac{W}{L}\right)_{eff}^{T2} + 3 \cdot \left(\frac{W}{L}\right)_{eff}^{T3}$$

(3.4)

At last, there is still another group of equations that aims to predict the drain current, as in (LOPEZ et al., 2009). Nonetheless, since only the drain current is estimated, it is not possible to use BSIM equations nor to make a direct comparison between other models. For this reason, this work focuses on methodologies to predict the ratio (W/L).

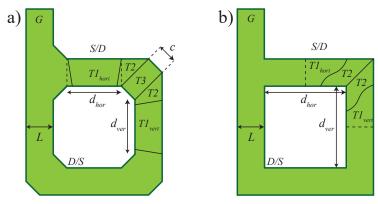

Under these circumstances, this work takes into consideration the same analysis discussed for topologies shown in Fig. 3.7 (a) and (b). Additionally, it is proposed to explicit the horizontal and vertical internal diffusion distances, variables  $(d_{hor})$  and  $(d_{ver})$ , respectively, in order to particularize their linear contributions, as represented in Fig. 3.9 (a) and (b).

The purpose of these explicit horizontal and vertical components is to enable the use of a wider range of aspect ratios, i.e., not only square symmetry but also rectangular symmetry. This is of particular importance to the layout phase, in order to satisfy cell pitch in layout template standardization, in which cells have a fixed height and a variable width. Additionally, to the best of our knowledge, this degree of freedom in a design was applied for the first time in the generation of custom RHBD cell library (VAZ et al., 2018).

Thus, (3.5) and (3.6) are adopted throughout this work. Moreover, also throughout this work, the distance c (i.e., the cathetus related to  $45^{\circ}$  corner), shown in Fig. 3.9 (a) is

Figure 3.9: (W/L) prediction methods with horizontal and vertical explicit variables for a) Sum of parallel transistors and b) Edge and Corner transistors.

conventionalized to be the same for each one of the four corners of internal gate edges of the proposed annular devices, unless indicated otherwise.

$$\left(\frac{W}{L}\right)_{eff}^{Rec.} = 4 \cdot \left[\left(\frac{W}{L}\right)_{eff}^{T1_{hori}} + \left(\frac{W}{L}\right)_{eff}^{T1_{vert}}\right] + 8 \cdot \left(\frac{W}{L}\right)_{eff}^{T2} \tag{3.5}$$

$$\left(\frac{W}{L}\right)_{eff}^{Rec.BC} = 2 \cdot \underbrace{\left[\left(\frac{W}{L}\right)_{eff}^{T1_{hori}} + \left(\frac{W}{L}\right)_{eff}^{T1_{vert}}\right]}_{\left(\frac{W}{L}\right)_{eff}^{T1}} + 2 \cdot k \cdot \left(\frac{W}{L}\right)_{eff}^{T2} + 3 \cdot \left(\frac{W}{L}\right)_{eff}^{T3}$$

(3.6)

The conceptual support to validate the preceding equations lies in the fact that, as authors claim, each transistor has a *linear* contribution. For this reason, in the context of a cell library, in which each cell should consider fixed height and variable width, it is convenient to explicit these two contributions (i.e., horizontal and vertical) to better fit at the layout phase.

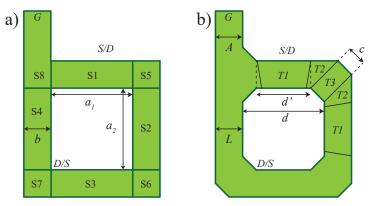

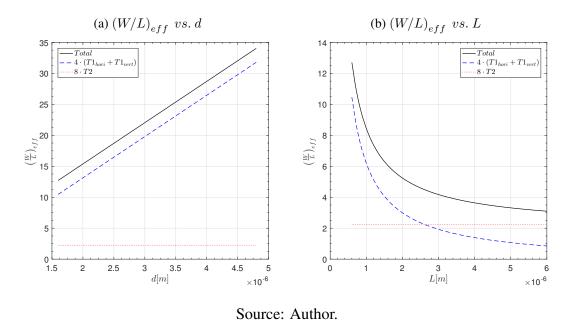

The curves in Figs. 3.10 and 3.11 summarize each individual device's contribution in terms of their (W/L), respectively for Rectangular and Rec. BC. In Figs. 3.10 and 3.11 index (a), it is possible to verify the linear increment from T1, T2 and T3 (expressed in (3.5) and (3.6)). Similarly, in Figs. 3.10 and 3.11 index (b), it is possible to observe the decrescent trend of total (W/L) when increasing the channel length. It is noteworthy that the "discontinuity" seen in Fig. 3.11 (b) (in the term 2K(T2)) occurs because an internal

method's variable increase their fitting value when the channel length becomes greater than  $500 \ nm$ .

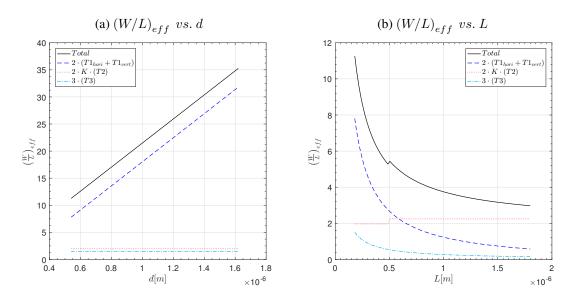

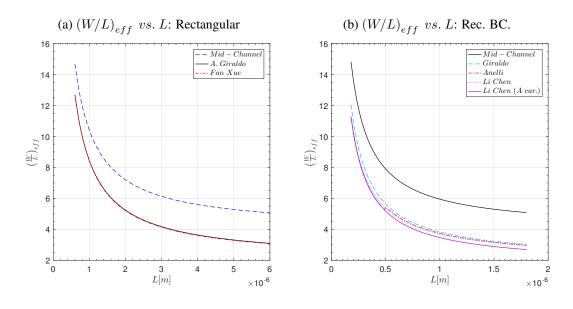

Figure 3.12 summarizes all related methods in terms of their (W/L) contributions. The index (a) presents the Rectangular method's compilation and (b) the RecBC.

Figure 3.10: ELT Rectangular and its (W/L) contributions.

Figure 3.11: ELT Rectangular BC and its (W/L) contributions.

Source: Author.

Figure 3.12: ELT and its (W/L) contributions for all related methods for: a) Rectangular and b) Rectangular Broken Corners.

# 3.3.3 Effective (W/L) aspect ratio limitations

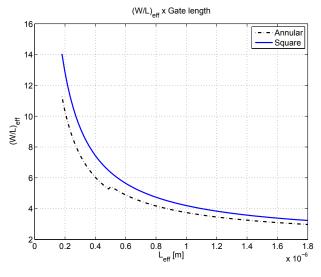

In an Annular device, while it is possible to reduce its (W/L) ratio by increasing the gate length, the required silicon area grows exponentially, with an asymptotic behavior to the value of 2.26 (LEE; LEE, 2013). Figure 3.13 illustrates this behavior for Rectangular Broken Corners (RecBC) and Rectangular geometries. The curves were obtained through simulation using their analytical models, (3.2) and (3.1), respectively. In these cases, the aspect ratio of 3 in SPT is achievable with almost 10 times of the minimum channel length (ANELLI, 2000).

Calculating the (W/L) for 10 and 20 times the channel length leads to:

$$10 \cdot L_{min} \rightarrow \left(\frac{W}{L}\right)_{annular} = 2.97 \text{ and } \left(\frac{W}{L}\right)_{square} = 3.23$$

$$20 \cdot L_{min} \ o \ \left( rac{W}{L}

ight)_{annular} = 2.33 \ {

m and} \ \left( rac{W}{L}

ight)_{square} = 2.61$$

# 3.3.4 Source/drain asymmetry

When the channel region operates in strong inversion, the drain/source voltage  $\left(V_{DS}\right)$  may strangle the channel region (i.e., the distance between the drain/source and

Figure 3.13: Effective (W/L) aspect ratio for Rec.BC (Annular) and Rectangular (Square) devices in  $180\ nm$ .

where the inversion layer charge almost reach zero density). This effect, known as pinchoff, causes the distance between drain and source to be reduced by  $(\Delta L)$ (TSIVIDIS; MCANDREW, 2011).

These variations, related to channel length modulation (CLM), give origin to nonidealities in the output transfer function ( $I_D \ vs. \ V_{DS}$ ), which can be seen in Fig. 3.14 (a) as the slope comprised for  $\Delta I_D$  and  $\Delta V_{DS}$ . This slope refers to the conductance of the output devices ( $G_{out}$ ) (also known as the source-drain conductance -  $g_{sd}$ ), expressed in (3.7) (ANELLI, 2000; TSIVIDIS; MCANDREW, 2011).

Figure 3.14: a) Transfer function  $(I_D \ vs. \ V_{DS})$  and b) Space/charge distribution for in and outside drain possibilities.

Source: Adapted from (ANELLI, 2000).

$$G_{out} = g_{sd} = \frac{\partial I_D}{\partial V_{DS}} \bigg|_{V_{GS}, V_{BS} = const}$$

(3.7)

Moreover, these variations in CLM correspond to a certain space/charge density distribution which, in Two-Edged (TE) devices, regarding its symmetry, the interchangeable source and drain terminals causes an equal slope. In other words, independently whether the drain or source is assigned to the left or right position, the pinchoff region should ideally be the same.

In ELT designs, the channel length variations are different when enclosing the drain or the source. As depicted in Fig. 3.14 (b), if the drain is enclosed, then the pinchoff region, represented for  $\Delta L_{di}$ , should be higher (larger) than if the drain stands outside ( $\Delta L_{do}$ ). These 2-D different areas result in an equal 3-D carrier volumes (i.e., space/charge density distribution).

Indeed, when taking  $\Delta L$  into account when calculating  $G_{out}$ , it is possible to verify that if  $\Delta L$  increases, then the total  $G_{out}$  also increases, as expressed in (3.8) for an Rectangular device (ANELLI, 2000).

$$G_{out} = \frac{I_D}{\Delta V_{DS}} \cdot \frac{\Delta L_{i,o}}{L - \Delta L_{i,o}}$$

(3.8)

On this perspective, it is possible to surmise that if the drain is placed on the inner (enclosed) diffusion area, the output conductance should be higher (worse), which is not ideal. The curve presented in Fig. 3.15 corroborates this fact. It is possible to visualize the output conductance in terms of gate length variation for TE, as well as both drain inside and drain outside ELT devices.

Figure 3.15: Comparison between output conductance for Two-Edged device and ELT device for drain as inner and outer diffusion regions (ANELLI, 2000).

Source: Data plot from (ANELLI, 2000).

This case study also reveals that when gate length is increased, the difference between ELT and TE devices approximates the arithmetic mean between  $G_{di}$  and  $G_{do}$  (ANELLI, 2000).

However, due to a small area, the inner terminal capacitance is lower than the outer and, when a high frequency operation is desirable, the terminals with higher capacitance (outer diffusion regions) should be assign to fixed (or more stable) potentials, such as  $V_{DD}$  or  $V_{SS}$ . In this case, there is a clear tradeoff between speed and gain if is considered designing amplifiers (ANELLI, 2000). Thus, designers usually prefer to assign the drain inside.

A comparison between the transition times of inverter cells using TE and ELT devices with inside-placed drain was performed. Results indicate that the ELTs were up to 12% faster than the TE counterparts. Even though these devices were reasonably faster, the area penalty related to enclosing a gate geometry was at least 15% for a single transistor and 150% for an inverter cell. For more complex cells, the area overhead is expected to increase for ELT devices (VAZ; JUNIOR; WIRTH, 2015; VAZ; WIRTH, 2015).

## 3.4 Summary and Discussion

Techniques to harden a device against ionizing radiation effects can be applied through the entire IC design flow hierarchy: from the higher levels (e.g., system architec-

ture) to the basic building blocks or circuits, i.e., the single transistor.

To decide at which level(s) the technique(s) should be implemented is not a trivial task. It depends on several aspects, such as where the device will operate, how long it will operate and how many ions should cross the device in a given time interval (or unit area).

In a rough comparison, thinking the transistor of an entire DIE as a single brick of an entire building, a hardened wall can be built with various layers of bricks or by a more ingenious interlacing (with a minor number of them).

Nowadays, in technology nodes that are in the deep submicron range (180 nm, 130 nm, 90 nm, 45 nm and beyond), gate oxides are about 2 nm thick. These thin gate oxides are almost immune to total ionizing dose effects. FOX lateral isolation, however, is about  $100 \ nm$  thick; in these oxides, TID effects may increase leakage path between source and drain, increasing leakage current (FACCIO et al., 2008; ANELLI, 2000).

In some cases, neither various layers of bricks (i.e., multiple redundancies or voters schemes) nor ingenious interlacing (i.e., place structures at different regions or designing sensors to detect current spikes) are sufficient to produce a circuit capable of properly operate in harsh environments, as, for instance, is required to be qualified for space and satellite applications.