# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

### ROBERT DETTENBORN

# Parametric Analysis and Optimization of MOSFET Macromodels for ESD Circuit Simulation

Dissertation submitted in partial fulfillment of the requirements for the degree of Master of Microeletronics

Advisor: Prof. Dr. Marcelo de Oliveira Johann

Porto Alegre December 2018

#### **CIP** — CATALOGING-IN-PUBLICATION

Dettenborn, Robert

Parametric Analysis and Optimization of MOSFET Macromodels for ESD Circuit Simulation / Robert Dettenborn. – Porto Alegre: PGMICRO da UFRGS, 2018.

100 f.: il.

Dissertation (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2018. Advisor: Marcelo de Oliveira Johann.

1. ESD. 2. Circuit simulation. 3. MOSFET macromodels. 4. Parametric analysis. 5. Optimization. I. Johann, Marcelo de Oliveira. II. Título.

### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenadora do PGMICRO: Prof<sup>a</sup>. Fernanda Gusmão de Lima Kastensmidt Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

## **ACKNOWLEDGMENTS**

I would like to thank my advisor Prof. Dr. Marcelo de Oliveira Johann for making this work possible, Eng. Everton Luis Granado Ghignatti Junior for the many advices, discussions and technical support, and Dr. Artur Vicente Pfeifer Coelho as well as Dr. Laurent Courcelle for providing the necessary resources at CEITEC S.A.

I dedicate this dissertation to my family and to the memory of my grandmother.

#### **ABSTRACT**

Electrostatic discharge (ESD) is a major reliability concern in semiconductor industry. An ESD event may degrade or destroy an integrated circuit (IC), impacting on production yields, manufacturing costs, product quality, product reliability and company profitability. Additionally, the breakdown voltages and failure currents of semiconductor devices are becoming lower with the technology scaling, placing severe constraints on robust IC design. As a result, effective onchip ESD protection without compromising area and performance requirements is becoming a challenge in deeply-scaled technologies. In this context, circuit simulation can provide the required assistance in on-chip protection design, including robustness analysis of the circuits and performance prediction prior to silicon. However, modeling the MOSFET operation under ESD conditions for circuit simulation is still a challenging issue. The large current and voltage characteristics are typically not well covered by most standard SPICE compact models. To overcome such limitation, a practical modeling approach is highly desired. This work presents a study of MOSFET macromodels for ESD circuit simulation. First, it gives an overview of the device operation under ESD conditions. Then, it presents the evolution of MOSFET macromodels for ESD circuit simulation. Finally, a novel macromodel development approach based on parametric analysis and optimization is introduced.

**Keywords:** ESD. Circuit simulation. MOSFET macromodels. Parametric analysis. Optimization.

# Análise Paramétrica e Otimização de Macromodelos para Simulação Elétrica de Descarga Eletrostática em MOSFETs

### **RESUMO**

Descarga eletrostática (ESD) é uma importante preocupação em relação à confiabilidade de produtos na indústria de semicondutores. Uma descarga eletrostática pode degradar ou destruir circuitos integrados, afetando o rendimento da produção, os custos de fabricação, a qualidade e a confiabilidade dos produtos, bem como a lucratividade da empresa. Além disso, a redução das dimensões dos dispositivos com o avanço da tecnologia resulta em menores tensões de ruptura e correntes de falha, impondo severas restrições no projeto de circuitos integrados robustos. Com isso, o projeto de proteções intra-chip eficazes contra ESD, sem comprometer os requisitos de área e desempenho, está se tornando um desafio cada vez maior em tecnologias avançadas. Neste contexto, a simulação elétrica pode prover a assistência necessária ao projeto de proteções intra-chip, incluindo a análise de robustez dos circuitos e a estimativa de desempenho antes da fabricação em silício. No entanto, modelar a operação de MOSFETs sob condições de ESD para simulação elétrica ainda é um problema desafiador. O comportamento destes dispositivos sob altas correntes e tensões normalmente não é bem descrito pela maioria dos modelos compactos SPICE convencionais. Para contornar essa limitação, uma abordagem prática de modelagem é altamente desejada. Este trabalho apresenta um estudo acerca de macromodelos para simulação elétrica de ESD em MOSFETs. Primeiro, uma visão geral da operação de um MOSFET sob condições de ESD é fornecida. Em seguida, a evolução dos macromodelos para simulação elétrica de ESD em MOSFETs é apresentada. Por fim, uma nova abordagem para o desenvolvimento de macromodelos baseada em análise paramétrica e otimização é introduzida.

**Palavras-chave:** Descarga eletrostática, simulação elétrica, macromodelos de MOSFETs, análise paramétrica, otimização.

#### LIST OF ABBREVIATIONS AND ACRONYMS

ADE Cadence Virtuoso Analog Design Environment (EDA tool)

BGA Ball grid array

BJT Bipolar junction transistor

BSIM Berkeley short-channel insulated-gate field-effect transistor model

BVOX Gate oxide breakdown voltage

CAD Computer-aided design

CDM Charged device model

CMOS Complementary metal-oxide semiconductor

DC Direct current (circuit analysis domain)

DIP Dual in-line package

DNO MunEDA WiCkeD Deterministic Nominal Optimization (EDA tool)

DUT Device under test

EDA Electronic design automation

EKV Enz-Krummenacher-Vittoz (MOSFET compact model)

ESD Electrostatic discharge

FDSOI Fully-depleted silicon on insulator

GCNMOS Gate-coupled n-type metal-oxide semiconductor

GGNMOS Gate-grounded n-type metal-oxide semiconductor

GND Ground (reference voltage)

GNO MunEDA WiCkeD Global Nominal Optimization (EDA tool)

GPDK Generic process design kit

HBM Human body model

HDL Hardware Description Language

HICUM High current model (bipolar compact model)

I/O Input/output

IC Integrated circuit

LGA Land grid array

MEXTRAM Most exquisite transistor model

MM Machine model

MOS Metal-oxide semiconductor (common abbreviation of MOSFET)

MOSFET Metal-oxide semiconductor field-effect transistor

NDR Negative differential resistance

NMOS N-type metal-oxide semiconductor

PMOS P-type metal-oxide semiconductor

RF Radio-frequency

RH Relative humidity

SCR Silicon-controlled rectifier

SPICE Simulation program with integrated circuit emphasis

SQP Sequential quadratic programming

STI Shallow trench isolation

STNMOS Substrate-triggered n-type metal-oxide semiconductor

TLP Transmission-line pulse

UTBB Ultra-thin body and buried oxide

VBIC Vertical bipolar inter-company

VDD Voltage drain drain (power supply voltage)

# LIST OF FIGURES

| Figure 1.1  | Failures in the drain junction of a MOS I/O transistor (a) and in the gate       |    |

|-------------|----------------------------------------------------------------------------------|----|

| oxide       | of a core transistor (b)                                                         | 14 |

| Figure 1.2  | Failures in two NMOS transistors (a) and in the gate oxide of an input           |    |

| transis     | stor (b)                                                                         |    |

| Figure 1.3  | Typical HBM (a), MM (b) and CDM (c) test circuits.                               | 15 |

| Figure 1.4  | Current waveforms for HBM, MM and CDM ESD events                                 | 15 |

| Figure 1.5  | Typical TLP pulse shape. The annotations indicate relevant features that         |    |

|             |                                                                                  | 16 |

| Figure 1.6  | HBM oxide breakdown voltage and core supply voltage as a function of             |    |

|             |                                                                                  | 17 |

| Figure 1.7  | CDM oxide breakdown voltage (red line with circles), drain junction              |    |

| break       | down voltage (black line with stars) and core supply voltage as a function       |    |

|             |                                                                                  | 18 |

| -           | HBM current density for failure of metal interconnects as a function of          |    |

|             | ology scaling.                                                                   | 18 |

|             | CDM current density for failure of metal interconnects as a function of          |    |

|             | ology scaling.                                                                   | 18 |

|             | Impact of technology scaling on the ESD design window from 130 nm                |    |

|             | nm nodes.                                                                        | 19 |

| _           | Impact of technology scaling on the ESD design window beyond the                 |    |

|             | node                                                                             | 20 |

|             | Required area to achieve 2 kV HBM ESD protection as the technology               |    |

|             | scales.                                                                          |    |

| _           | Generic ESD protection scheme for a bidirectional I/O circuit                    | 21 |

| _           | Pad-based protection scheme and examples of applicable ESD protection            |    |

|             | es                                                                               | 22 |

| Figure 1.15 | Rail-based ESD protection scheme.                                                | 23 |

| Figure 2.1  | NMOS transistor cross section schematic.                                         | 26 |

| Figure 2.2  | I-V curves of an NMOS transistor under high-voltage conditions                   |    |

| Figure 2.3  | Schematic of the intrinsic lateral <i>npn</i> transistor in an NMOS device cross | 20 |

| sectio      |                                                                                  | 29 |

| Figure 2.4  | Avalanche current ( $I_{avl}$ ) schematic                                        |    |

|             | I-V curve of an $npn$ transistor in self-bias operation under high-current       | 51 |

|             | tions                                                                            | 32 |

|             | $I-V$ curve of an NMOS transistor with $V_G=0$ under high-current con-           | 52 |

|             | S                                                                                | 33 |

|             | NMOS transistor operation under typical ESD conditions.                          |    |

| 1 15010 2.7 | 144105 transistor operation under typical Lob conditions                         | 55 |

| Figure 3.1  | Modeling the avalanche breakdown of a BJT with a current source $(I_{avl})$ .    | 37 |

| Figure 3.2  | Modeling the avalanche breakdown of an NMOS transistor with a paral-             |    |

| _           | T and a current source $(I_{avl})$ .                                             | 37 |

| Figure 3.3  |                                                                                  |    |

| lel BJ      | T and two current sources ( $I_{avl1}$ and $I_{avl2}$ )                          | 39 |

| Figure 3.4  | Modeling the avalanche breakdown with BSIM3 and VBIC compact model               |    |

| Figure 3.5  | Snapback modeling with BSIM4 and MEXTRAM-like compact models                     |    |

| Figure 3.6  | Modeling the impedance for negative $V_{DS}$ with diodes and resistors           | 45 |

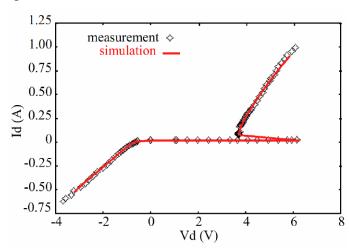

|                          | Comparison between simulation and measurement data of a GGNMOS                          | 46 |

|--------------------------|-----------------------------------------------------------------------------------------|----|

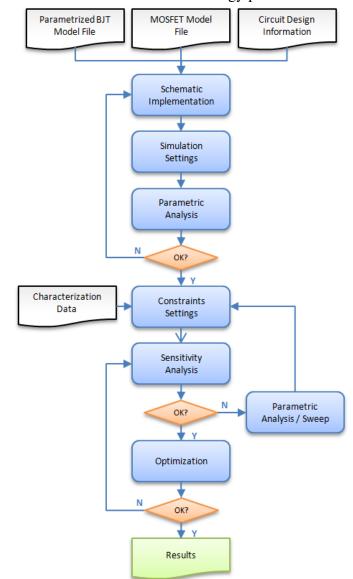

| Figure 4.1<br>Figure 4.2 | Flow chart of the methodology presented in this work                                    | 48 |

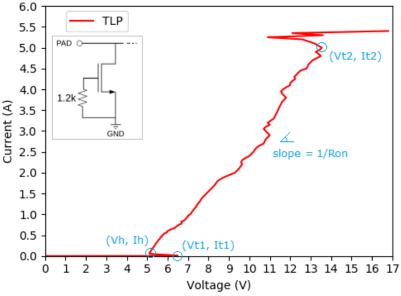

| _                        | n device.                                                                               | 50 |

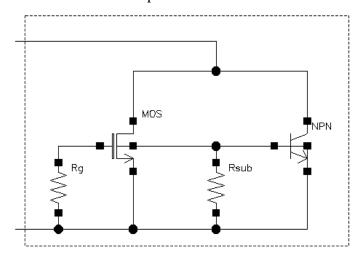

| Figure 4.3               | Initial schematic implementation of the GGNMOS macromodel                               |    |

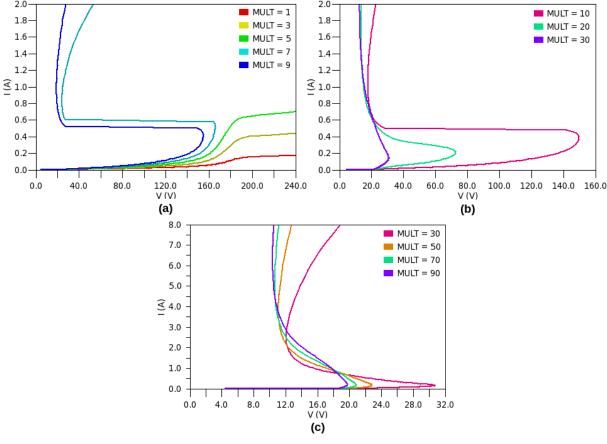

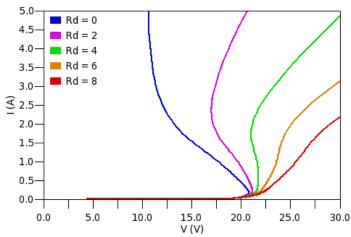

| Figure 4.4               | Effect of $MULT$ parameter on the macromodel $I-V$ characteristics                      |    |

| Figure 4.5               | Effect of $R_{sub}$ (defined in $\Omega$ ) on the macromodel $I-V$ characteristics      |    |

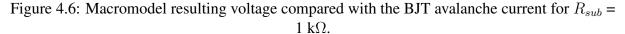

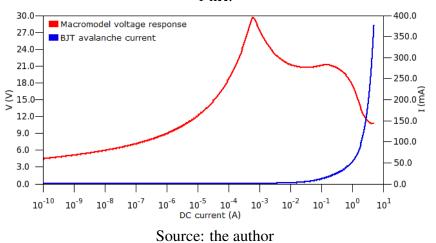

| Figure 4.6               | Macromodel resulting voltage compared with the BJT avalanche current                    |    |

| C                        | $_{nb}$ = 1 k $\Omega$ .                                                                | 56 |

| Figure 4.7               | Macromodel $I-V$ characteristics for $MULT = 70$ and without $R_{sub}$                  |    |

| _                        | Macromodel schematic without $R_{sub}$ and with an additional series resis-             |    |

| -                        |                                                                                         | 57 |

| •                        | Effect of $R_d$ (defined in $\Omega$ ) on the macromodel $I-V$ characteristics          |    |

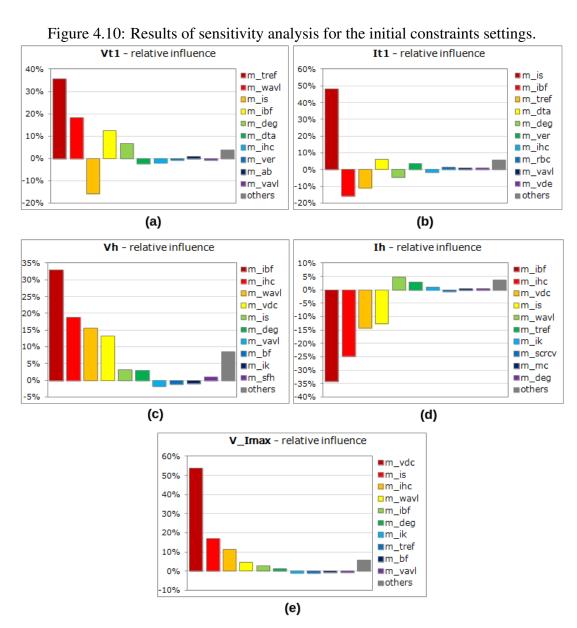

| _                        | Results of sensitivity analysis for the initial constraints settings                    |    |

| _                        | Effect of $T_{ref}$ (a) and $W_{avl}$ (b) parameters on $V_{t1}$ and $V_h$ performances |    |

|                          | Evolution of the Global Nominal Optimization after 5 sample genera-                     |    |

| _                        | or each target performance.                                                             | 64 |

|                          | A scatter plot example (a) (b) and the 10-best samples (c) of the Global                |    |

|                          | nal Optimization.                                                                       | 65 |

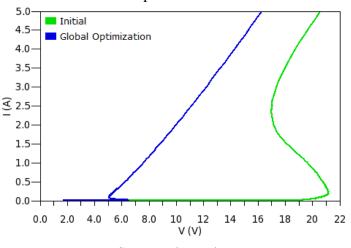

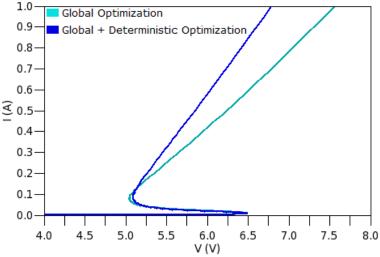

|                          | Macromodel $I-V$ characteristics before and after the Global Nominal                    |    |

|                          | ization.                                                                                | 66 |

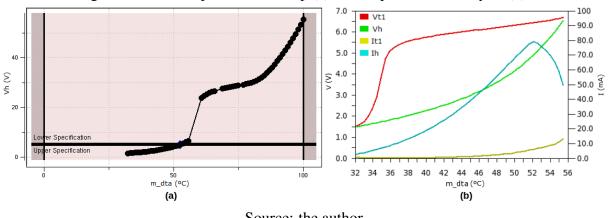

| Figure 4.15              | DTA parameter sweep (a) and its parametric analysis (b)                                 | 67 |

|                          | Results of sensitivity analysis after the Global Nominal Optimization and               |    |

| _                        | ne new constraints settings for the $DTA$ parameter                                     | 68 |

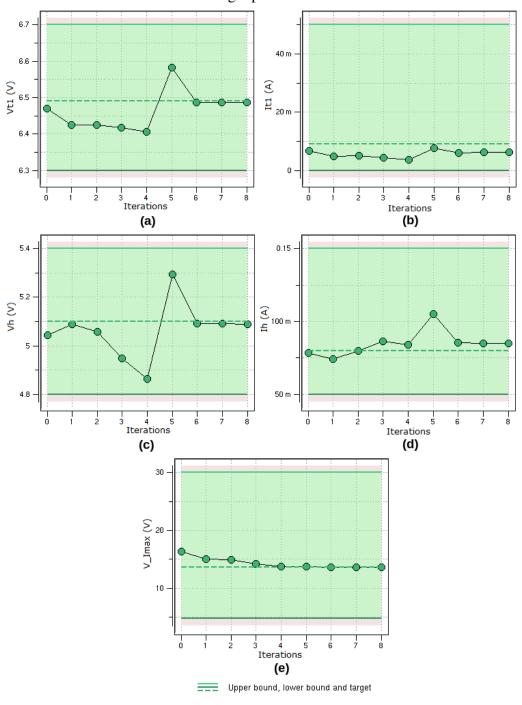

|                          | Evolution of the Deterministic Nominal Optimization after 8 iterations                  |    |

|                          | ch target performance                                                                   | 70 |

|                          | Macromodel $I-V$ characteristics before and after the Deterministic Nom-                |    |

|                          | ptimization                                                                             | 71 |

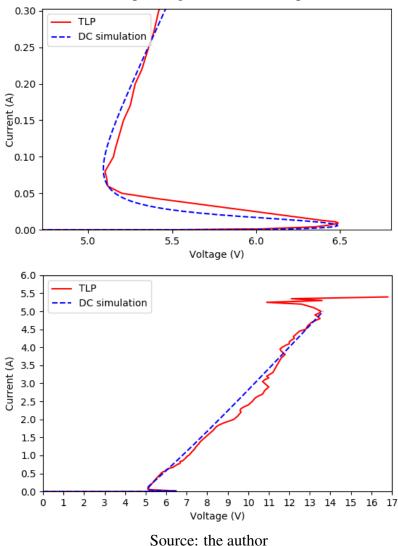

|                          | Comparison between the final macromodel $I-V$ characteristics and the                   |    |

| _                        | esults of the corresponding GGNMOS ESD protection device                                | 72 |

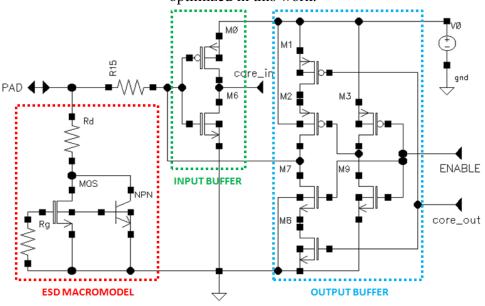

|                          | Schematic of a bidirectional I/O circuit including the macromodel devel-                |    |

| _                        | and optimized in this work.                                                             | 73 |

|                          | Input buffer (a) and output buffer (b) responses to a periodic-pulse voltage            |    |

|                          | Safe operating area (SOA) for the bidirectional I/O circuit (simulation)                |    |

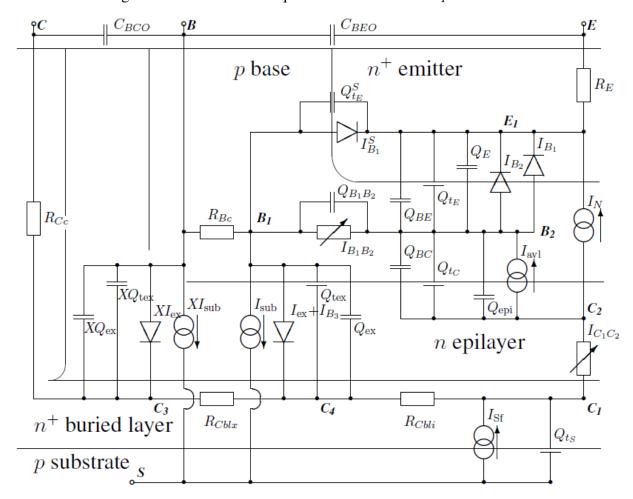

|                          | MEXTRAM equivalent circuit for the <i>npn</i> transistor                                |    |

# LIST OF TABLES

|           | Examples of electrostatic charge generation and the typical resulting volt- |    |

|-----------|-----------------------------------------------------------------------------|----|

| age le    | evels                                                                       | 13 |

| m.1.1.4.4 |                                                                             |    |

| Table 4.1 | List of constant and variable parameters defined for the MEXTRAM com-       |    |

| pact 1    | nodel                                                                       | 59 |

| Table 4.2 | Performances specifications for the Global Nominal Optimization             | 63 |

| Table 4.3 | Algorithm and settings for the Global Nominal Optimization                  | 63 |

| Table 4.4 | Performances specifications for the Deterministic Nominal Optimization      | 69 |

| Table 4.5 | Algorithm and settings for the Deterministic Nominal Optimization           | 69 |

| Table 4.6 | Final results after the optimization of the macromodel performances         | 71 |

| Table 4.7 | List of failed devices for an input DC current sweep from 0 to 5 A          | 75 |

|           |                                                                             |    |

# **CONTENTS**

| 1 INTRODUCTION                                                                | . 13 |

|-------------------------------------------------------------------------------|------|

| 1.1 Electrostatic discharge                                                   | . 13 |

| 1.2 Impact on integrated circuits                                             | . 13 |

| 1.3 Trends and challenges                                                     | . 16 |

| 1.4 On-chip ESD protection                                                    | . 21 |

| 1.5 ESD modeling and simulation                                               | . 24 |

| 2 MOSFET OPERATION UNDER ESD CONDITIONS                                       | . 26 |

| 2.1 Low-current operation                                                     | . 26 |

| 2.2 Avalanche breakdown                                                       | . 27 |

| 2.3 Lateral bipolar transistor activation                                     | . 29 |

| 2.4 Snapback and negative differential resistance                             | . 32 |

| 2.5 Low-impedance operation and thermal breakdown                             | . 33 |

| 2.6 Summary of the major ESD effects                                          | . 34 |

| 3 MOSFET MACROMODELS FOR ESD CIRCUIT SIMULATION                               | . 36 |

| 3.1 Modeling the avalanche breakdown with a parallel BJT and a current source | . 36 |

| 3.2 Modeling the avalanche breakdown with BSIM3 and VBIC compact models       | . 41 |

| 3.3 Snapback modeling with BSIM4 and MEXTRAM-based compact models             | . 43 |

| 3.4 Modeling the impedance for negative drain-to-source voltage               | . 45 |

| 4 AN OPTIMIZATION-BASED METHODOLOGY FOR MACROMODELS DESIGN                    | . 47 |

| 4.1 Methodology overview                                                      | . 47 |

| 4.2 Characterization data, circuit design information and model files         | . 49 |

| 4.3 Schematic implementation, simulation settings and parametric analysis     | . 52 |

| 4.4 Constraints settings and sensitivity analysis                             | . 58 |

| 4.5 Optimization of the macromodel I-V characteristics                        | . 62 |

| 4.6 Macromodel application example                                            | . 72 |

| 5 CONCLUSIONS                                                                 | . 77 |

| REFERENCES                                                                    | . 81 |

| APPENDIX A — THE AVALANCHE CURRENT MODEL OF MEXTRAM                           | . 85 |

| APPENDIX B — OPTIMIZATION BOUNDARIES, INITIAL AND FINAL VALUES                | . 89 |

| ANNEX A — MEXTRAM PARAMETERS DESCRIPTION                                      | . 93 |

| ANNEX B — MEXTRAM PARAMETERS DEFAULT AND CLIPPING VALUES                      | . 97 |

#### 1 INTRODUCTION

#### 1.1 Electrostatic discharge

Electrostatic discharge (ESD) is defined as the rapid, spontaneous transfer of electrostatic charge between two bodies at different electrostatic potentials, either through contact or via an ionized ambient discharge (a spark) induced by a high electrostatic field (ESD Association, 2013). Means of creating electrostatic charge on a material include induction, ion bombardment, contact with another charged material or *triboelectric charging*<sup>1</sup>. Table 1.1 illustrates typical charge generation scenarios, their resulting voltage levels and the influence of the relative humidity (RH) on reducing charge accumulation.

Table 1.1: Examples of electrostatic charge generation and the typical resulting voltage levels.

| Means of generation           | 10-25% RH | 65-90% RH |

|-------------------------------|-----------|-----------|

| Walking across carpet         | 35,000 V  | 1,500 V   |

| Walking across vinyl tile     | 12,000 V  | 250 V     |

| Worker at a bench             | 6,000 V   | 100 V     |

| Poly bag picked up from bench | 20,000 V  | 1,200 V   |

| Chair with urethane foam      | 18,000 V  | 1,500 V   |

Source: ESD Association (2013)

## 1.2 Impact on integrated circuits

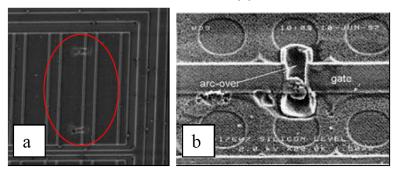

Electrostatic discharge may degrade or destroy semiconductor devices. In the first case, the device continues to perform its intended function. However, its operating life may be reduced (*latent failure*). In the second case, the device stops performing its intended function, partially or totally (*catastrophic failure*). Typical examples of ESD damage in CMOS integrated circuits include **metal melt**, **junction breakdown** and **oxide failure**. Figure 1.1 and Figure 1.2 illustrate common ESD failure signatures. Such failures naturally represent costs to semiconductor industry, impacting on production yields, manufacturing costs, product quality, product reliability and profitability.

<sup>&</sup>lt;sup>1</sup>Triboelectric charging is the effect of creating electrostatic charge by contact and separation of materials.

Figure 1.1: Failures in the drain junction of a MOS I/O transistor (a) and in the gate oxide of a core transistor (b).

Source: Industry Council on ESD Target Levels (2010)

Figure 1.2: Failures in two NMOS transistors (a) and in the gate oxide of an input transistor (b).

Source: Industry Council on ESD Target Levels (2010)

ESD damage in electronic devices is usually caused by one of the three basic ESD events below (ESD Association, 2013):

**Discharge to the device** The electrostatic charge is transferred from any charged conductor to the electronic device. A charged conductor, in this case, may be either the human body or a conductive object, such as a metallic tool or an automatic equipment. The models used to reproduce these events are, respectively, the *Human Body Model (HBM)* and the *Machine Model (MM)*. Figure 1.1 illustrates typical HBM-like failure signatures.

**Discharge from the device** Electronic devices may accumulate static charge themselves, for example, while they move across a surface or vibrate in a package. The electrostatic charge is then transferred from the electronic device to a conductor. The model used to reproduce this event is the *Charged Device Model (CDM)*. Figure 1.2 illustrates typical CDM-like failure signatures.

**Field-induced discharge** The electrostatic charge is induced on the electronic device when it is subjected to an electrostatic field associated to a charged object. If the device is then grounded while within the electrostatic field, the transfer of charge is the same described by the *Charged Device Model (CDM)*.

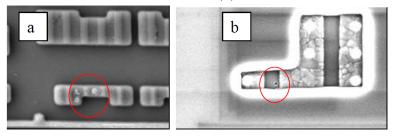

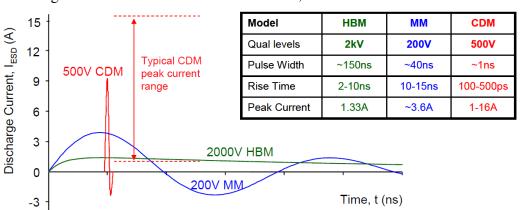

ESD Association, IEC, U.S. Department of Defense, JEDEC and JEITA are examples of

organizations that provide a significant amount of different standardized test methods to evaluate the ESD sensitivity levels of electronic devices. Figure 1.3 illustrates the test circuits<sup>2</sup> adopted by the ESD Association to reproduce ESD events described by HBM, MM and CDM. Figure 1.4 illustrates examples of typical current waveforms for each model. Recently, the industry has been driving efforts to remove the Machine Model (MM) test from device qualification requirements (Industry Council on ESD Target Levels, 2012) (DUVVURY et al., 2013) (ESD Association, 2014) (JEDEC, 2014). The Industry Council on ESD Target Levels provided data supporting that the MM qualification requirements are unnecessary when HBM and CDM specifications are both met (DUVVURY et al., 2013). These two primary models of ESD events have been proven to successfully reproduce over 99% of all ESD failure signatures found in field (ESD Association, 2014).

Figure 1.3: Typical HBM (a), MM (b) and CDM (c) test circuits.

Source: ESD Association (2014) (modified)

Figure 1.4: Current waveforms for HBM, MM and CDM ESD events.

Source: Industry Council on ESD Target Levels (2010)

80

100

60

40

20

<sup>&</sup>lt;sup>2</sup>Test circuits may differ in standards from one organization to another.

As mentioned above, there is a significant amount of different standardized test methods to evaluate the ESD sensitivity levels of electronic devices. However, the default method for characterizing the behavior of devices under ESD conditions is the Transmission-Line Pulse (TLP) testing (SMEDES, 2017). In contrast to HBM and CDM testing methods, TLP provides more than a pass/fail result. It also provides a quasi-static I-V characteristic that describes the behavior of the device under test (DUT). The method basically consists in charging up and then discharging a transmission line (typically of  $50~\Omega$ ) into a DUT, using pulses with duration, rise time and current levels that are relevant for ESD events. From measurements in a predefined stable part of the pulse, a quasi-static I-V point can be determined. By repeating this charge/discharge procedure for multiple charge levels, a complete characteristic is established. Figure 1.5 illustrates a typical TLP pulse shape. In general, a low-current DC measurement is performed after each TLP pulse. A change in the DC measurement from one pulse to another is often an indication that the DUT has been damaged by the preceding pulse.

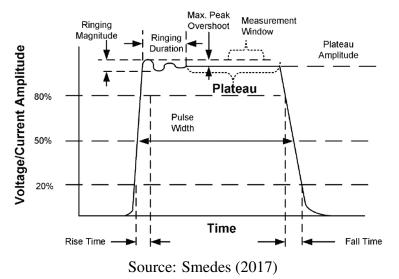

Figure 1.5: Typical TLP pulse shape. The annotations indicate relevant features that are defined in standard documents.

# 1.3 Trends and challenges

Technology scaling contributes to improve circuits speed, with shorter channel lengths and thinner gate oxides, as well as to reduce area costs. However, it places severe constraints on robust ESD design of integrated circuits:

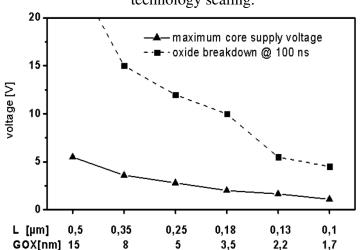

**Gate oxide** is becoming thinner, resulting in lower breakdown voltages under ESD regime. Figures 1.6 and 1.7 show the trends of gate oxide breakdown voltages under HBM stress and CDM stress, respectively, with CMOS technology scaling. Consequently, the design of protection devices for the circuit inputs is becoming more difficult.

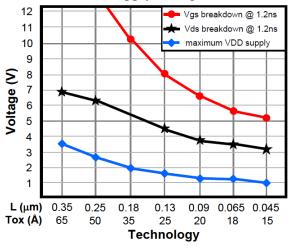

**Drain junction** Feature size is becoming smaller, source-to-drain distance is becoming shorter and integration density is increasing, resulting in lower drain junction breakdown voltages and lower failure currents under ESD regime (DUVVURY, 2008b). Figure 1.7 shows the trends of drain junction breakdown voltages under CDM stress with CMOS technology scaling. Consequently, the design of adequate protection devices for the circuit outputs is becoming more difficult.

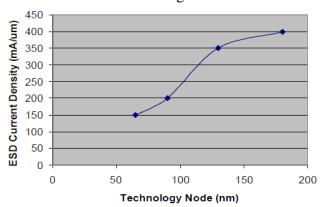

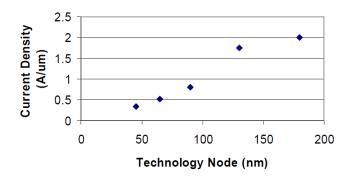

Metal interconnects are becoming thinner, resulting not only in reduced capacitance (usually desired for demanding performance requirements) but also resulting in increased resistance per square and reduced current density failure thresholds. As a consequence, resistive bus connections elevate the pad voltage at relatively low ESD currents (DUVVURY, 2008b). Trends of ESD current density for failure in metal interconnects with technology scaling are shown in Figures 1.8 (HBM) and 1.9 (CDM). As expected, failure currents are different for HBM and CDM discharges, since these events have different durations (pulse widths) and different current rise times, as seen in Figure 1.4.

Figure 1.6: HBM oxide breakdown voltage and core supply voltage as a function of technology scaling.

Source: Industry Council on ESD Target Levels (2011)

Figure 1.7: CDM oxide breakdown voltage (red line with circles), drain junction breakdown voltage (black line with stars) and core supply voltage as a function of technology scaling.

Source: Industry Council on ESD Target Levels (2010)

Figure 1.8: HBM current density for failure of metal interconnects as a function of technology scaling.

Source: Industry Council on ESD Target Levels (2011)

Figure 1.9: CDM current density for failure of metal interconnects as a function of technology scaling.

Source: Industry Council on ESD Target Levels (2010)

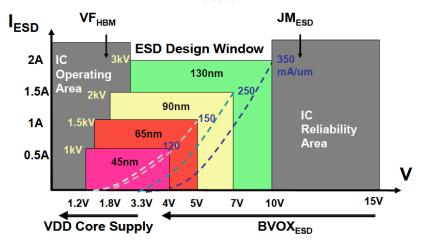

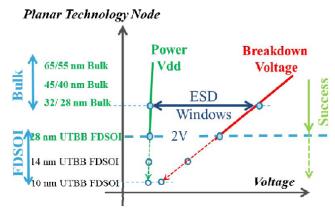

Technology scaling also impacts the **ESD design window**<sup>3</sup>. For instance, Figure 1.10 illustrates the trends in the ESD design window of High-Speed Serial Link designs at 15–20 Gbps. As the technology downscales, the gate oxide breakdown voltage ( $BVOX_{ESD}$ ) reduces at a faster rate than the maximum VDD core supply voltage. It means that the voltage range available for ESD protection circuits to operate is becoming more narrow. Also, the current density failure thresholds for metal interconnects ( $JM_{ESD}$ ), which are determined by the metal thickness, are becoming lower. The overall effect is a reduction of the practical ESD performance ( $VF_{HBM}$ ) from 3 kV in the 130 nm node to eventually 1 kV in the 45 nm node. Figure 1.11 illustrates the ESD design window trends beyond the 65 nm node, where the ESD design margin is reaching the volt.

Figure 1.10: Impact of technology scaling on the ESD design window from 130 nm to 45 nm nodes.

Source: Duvvury (2008b)

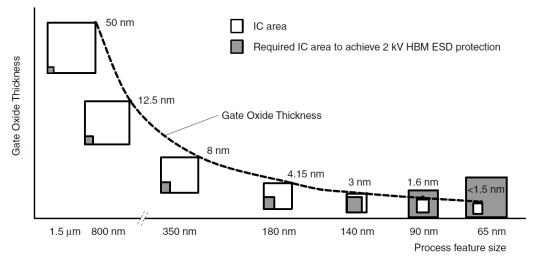

Effective ESD protection without compromising area and performance requirements is clearly becoming a challenge in deeply-scaled technologies. Figure 1.12 illustrates a projection of required area for ESD protection as the technology downscales. Beyond the 90 nm node, the required area to achieve 2 kV HBM ESD protection is becoming bigger than the area of the core circuit itself. In addition, package type (e.g. DIP, LGA and BGA), package size and number of circuit pins have significant impact on the protection against discharge currents at a

<sup>&</sup>lt;sup>3</sup>ESD design window is a two-dimensional representation of the ESD protection design space for meeting a specific ESD robustness level. In the horizontal axis, the window is constrained by the application voltage and the ESD-regime gate oxide breakdown voltage (for input circuit protection) or drain junction breakdown voltage (for output circuit protection). In the vertical axis, the window is constrained by the maximum current carrying capacity of the ESD protection circuit. These constraints usually include a safety margin. ESD protection circuits must turn on beyond the application voltage and reach the ESD current specification before approaching the gate oxide or drain junction breakdown voltages.

Figure 1.11: Impact of technology scaling on the ESD design window beyond the 65 nm node.

Source: Galy (2014)

given stress voltage, especially under CDM stress. The average package area and the number of circuit pins are increasing, driven by markets such as microprocessors and internet switching (Industry Council on ESD Target Levels, 2010). In general, larger is the package area (and its effective capacitance), higher are the CDM peak currents (DUVVURY, 2008a). It means that the I/O tolerance to CDM stress is being reached at lower voltage levels and, consequently, more robust ESD protection is required. The core circuit performance is also a concern. RF and high-speed digital I/O designs, for instance, can tolerate very little parasitic capacitance from the ESD protection devices (CAO et al., 2010) (KER; LIN; HSIAO, 2011). In analog design, another challenge expected in advanced technology nodes is the mismatch of ESD devices and ESD networks, which may lead to both local and global variation issues (VOLDMAN, 2012).

Figure 1.12: Required area to achieve 2 kV HBM ESD protection as the technology downscales.

Source: NXP Semiconductors (2010)

Technology trends and their associated challenges to ESD protection severely increase the costs of semiconductor industry. These costs come from silicon area, circuit performance demands, resources, design respins and eventually from time-to-market. Clearly, product qualification levels for HBM and CDM might become impractical in advanced technology nodes. In this context, the Industry Council on ESD Target Levels has recently proposed a reduction from 2 kV to 1 kV for HBM (Industry Council on ESD Target Levels, 2011) and from 500 V to 250 V for CDM (Industry Council on ESD Target Levels, 2010) product qualification. Such new levels are supposed to be achievable with proper static control in production environments and modern ESD design methods.

### 1.4 On-chip ESD protection

Approaches to avoid ESD events and consequently increase manufacturing yields include proper handling of IC devices and the implementation of a controlled handling environment. However, an essential technique to reduce overall costs and improve the product reliability is the implementation of on-chip ESD protection circuits. As the breakdown voltages under ESD regime are in general very low (few volts) compared to the stress voltages (e.g. 250 V CDM, 8 kV HBM), the challenge is to hold the voltage surge below the technology breakdown voltage and shunt the discharge current from an I/O pin to a power supply pin (VDD or GND).

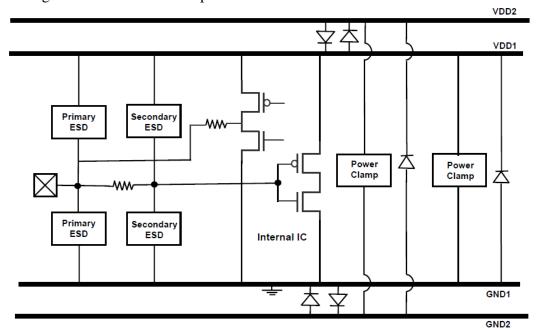

Figure 1.13: Generic ESD protection scheme for a bidirectional I/O circuit.

Source: Chun (2006)

Figure 1.13 illustrates a generic ESD protection scheme for a bidirectional I/O circuit. The purpose of the primary ESD devices is to limit the I/O pad voltage below the failure level of the output driver, shunting most of the ESD stress current to the power rails. The function of the secondary ESD devices with a series resistor between the primary and the secondary devices is to limit the gate voltage of the input receiver. It also aims to limit the current for low source impedance ESD stresses, thus being essential for CDM protection. The purpose of the power clamps and their parallel diodes is to provide a direct ESD current path between VDD and GND, protecting the devices of both the I/O circuit and the internal circuit against an ESD stress between these two power supply pins. Finally, the anti-parallel diodes between VDD1 and VDD2 and also between GND1 and GND2 aim to provide a direct ESD current path between two different power domains.

VDD Gate-grounded NMOS (ggNMOS) Power Clamp Gate-coupled NMOS (gcNMOS) D3 Prim Secondary ES ESD Internal D2 D1 Circuit Sub-triggered (-)NMOS (stNMOS)

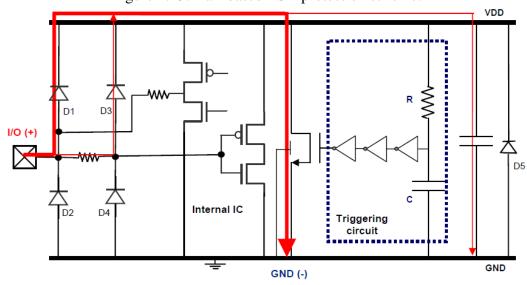

Figure 1.14: Pad-based protection scheme and examples of applicable ESD protection devices.

Source: Chun (2006)

Two common on-chip ESD protection approaches are the **pad-based protection** and the **rail-based protection** (CHUN, 2006). Figure 1.14 illustrates a pad-based protection scheme, where a positive ESD stress is applied from the I/O pad to GND. The ESD current, in this case, is directly shunted to GND by the primary and the secondary ESD devices. If a positive stress is applied from the I/O pad to VDD (instead of GND), the intended ESD current path also involves the diode D3. On the other hand, for a negative ESD stress applied from the I/O pad to GND, the intended ESD current path should involve only the diodes D1 and D2. If the negative stress is applied from the I/O pad to VDD (instead of GND), the intended

ESD current path consists not only of the diodes D1 and D2 but also of the power clamp. The function of the power clamp, in this case, is to hold the I/O pad voltage below the failure voltage of the I/O devices in parallel to it. Figure 1.14 also illustrates typical NMOS-based ESD protection devices used in pad-based configurations: the gate-grounded NMOS (GGNMOS<sup>4</sup>), the gate-coupled NMOS (GCNMOS) and the substrate-triggered NMOS (STNMOS). Another example of typical ESD protection device is the silicon-controlled rectifier (SCR), which has a very high current handling capability, resulting from the combination of two intrinsic bipolar transistors in a self-regenerative on-condition.

Figure 1.15 illustrates a rail-based protection scheme, where a positive ESD stress is applied from the I/O pad to GND. In this case, the ESD current is firstly redirected to the VDD power rail by the upper diodes D1 and D3, and then shunted to GND by the RC-triggered power supply clamp. If a positive stress is applied from the I/O pad to VDD (instead of GND), the intended ESD current path involves only the diodes D1 and D3. On the other hand, for a negative ESD stress applied from the I/O pad to GND, the intended ESD current path involves only the diodes D2 and D4. If the negative stress is applied from the I/O pad to VDD (instead of GND), the current flows from the VDD supply pad, passing through the power clamp and the lower diodes D2 and D4.

Figure 1.15: Rail-based ESD protection scheme.

Source: Chun (2006)

Both pad-based and rail-based ESD protection strategies have benefits and drawbacks. The design of pad-based ESD protection, for instance, is quite straightforward. However, the

<sup>&</sup>lt;sup>4</sup>The *GGNMOS* is the most basic configuration among NMOS-based ESD protection devices. Its intrinsic *npn* lateral bipolar transistor has a large current handling capability which enables the device to bypass a significant amount of the ESD current.

snapback devices typically used are very sensitive to process variations, not being portable from one process to another (CHUN, 2006). Also, the compact circuit models of such snap-back devices are not often provided, becoming difficult to verify the pad-based ESD protection effectiveness with circuit simulations. Rail-based ESD protection, on the other hand, often uses conventional devices (e.g. diodes and regular MOSFETs) which are much less susceptible to process variations, being relatively portable from one process to another. Also, as the compact circuit models of conventional devices are usually provided, the ESD protection circuit effectiveness can consequently be verified by circuit simulations.

### 1.5 ESD modeling and simulation

As explained in the previous sections, effective on-chip ESD protection without compromising area and performance requirements is becoming a challenge in deeply-scaled technologies. In this context, circuit simulation can provide the required assistance to on-chip ESD protection design, including robustness analysis of the circuits and performance prediction prior to silicon. However, modeling the MOSFET operation under ESD conditions for circuit simulation is still a challenging issue. The large current and voltage characteristics are typically not well covered by most standard SPICE compact models, such as BSIM3 (LIU et al., 1999) and BSIM4 (MORSHED et al., 2011). To overcome such limitation, a practical modeling approach is highly desired. For this purpose, **macromodels** can be very helpful.

A macromodel is a combination of conventional SPICE elements, optionally including math functions, to describe the observable *behavior* (not necessarily the implementation) of a device or circuit. Macromodels are often used to model devices that SPICE does not directly support. Most macromodels have many possible implementations. A classic example of a macromodel still in use today is the Boyle op-amp (BOYLE et al., 1974), which combines conventional SPICE elements with simple math functions to model the behavior of an op-amp. Instead of including all the transistors of the device (which would change from one op-amp design to another), simplified functions and parameters allow the adjustment of the model behavior.

The usage of macromodels to describe the I-V characteristics of an ESD protection device for circuit simulation instead of using a hardware description language (HDL) such as Verilog-A, for example, reduces convergence issues. Also, there is no need to switch between different models and there is no need of a specific circuit simulator other than a regular SPICE simulator. With macromodels, both the efficacy of the ESD protection device and its influence

on the core circuits performance can be evaluated.

This work presents a study of MOSFET macromodels for ESD circuit simulation. First, Chapter 2 gives an overview of the device operation under ESD conditions. Then Chapter 3 presents the evolution of MOSFET macromodels for ESD circuit simulation. Finally, Chapter 4 introduces a novel macromodel development approach based on parametric analysis and optimization.

#### 2 MOSFET OPERATION UNDER ESD CONDITIONS

During an ESD event, devices in the ESD path might operate outside their normal operating ranges. Thus, an understanding of devices operation under ESD stress conditions is essential to properly model their behavior. This chapter focuses on the MOSFET operation with emphasis on NMOS transistors. However, the description presented here is also applicable to PMOS transistors, with changes in the polarity of the majority and minority carriers.

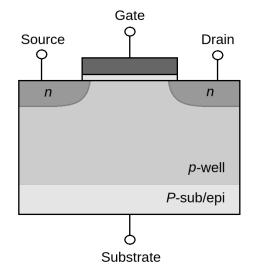

## 2.1 Low-current operation

Figure 2.1 illustrates a simplified NMOS cross section schematic. When a positive gate-to-source voltage  $V_{GS}$  is applied, majority carriers of the p region below the gate are pushed away by the electric field, creating a depletion region. With further increase in  $V_{GS}$ , a significant amount of minority carriers of the p region are attracted towards the gate, eventually creating a conductive channel between the source and the drain terminals. The gate-to-source voltage at which a conductive channel between the source and the drain terminals is created is called threshold voltage  $(V_T)$ .

Figure 2.1: NMOS transistor cross section schematic.

Source: the author

For low current densities, the typical operating regions of an NMOS device are **cut-off**, **linear** and **saturation**. While  $V_{GS} \leq V_T$ , the NMOS transistor is in the cut-off mode and the drain-to-source current  $I_{DS}$  is approximately zero. For  $V_{GS} > V_T$ , a conductive channel

is formed below the gate and the drain-to-source voltage  $V_{DS}$  determines whether the NMOS transistor is in the linear or in the saturation mode. When  $V_{DS} \leq V_{GS} - V_T$ , the NMOS transistor is in linear mode and the drain-to-source current  $I_{DS}$  is approximately

$$I_{DS} = \mu_n C_{ox} \frac{W}{L} \left[ (V_{GS} - V_T) V_{DS} - \frac{V_{DS}^2}{2} \right] (1 + \lambda V_{DS})$$

(2.1)

where  $\mu_n$  is the electron effective mobility,  $C_{ox}$  is the gate oxide capacitance per unit area, W is the channel width, L is the channel length and  $\lambda$  is a fitting parameter to consider effects such as channel length modulation, drain-induced barrier lowering or two-dimensional field distributions. In this case, the drain-to-source current  $I_{DS}$  is a linear function of the gate-to-source voltage  $V_{GS}$ . When  $V_{DS} > V_{GS} - V_T$ , the NMOS transistor is in the saturation mode and the drain-to-source current  $I_{DS}$  is a quadratic function of the gate-to-source voltage  $V_{GS}$ , given approximately by

$$I_{DS} = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_T)^2 (1 + \lambda V_{DS})$$

(2.2)

Cut-off, linear and saturation are the typical operating regions of the MOS transistor. Equations (2.1) and (2.2) are indeed relevant models to understand which are the main parameters that influence the NMOS drain-to-source current  $I_{DS}$ . However, the current equations in modern MOSFET compact models, such as BSIM3 and BSIM4, are usually more complex than that (LIU et al., 1999) (MORSHED et al., 2011). Also, during an ESD event, the high current and voltage levels may lead MOS transistors to operate outside their typical operating regions.

### 2.2 Avalanche breakdown

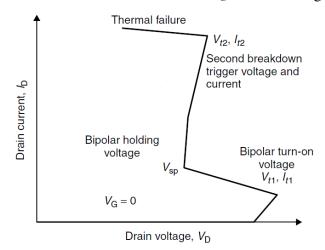

Under ESD conditions, the high voltage levels may lead MOS transistors to operate in the **avalanche** and in the **snapback** regions. Figure 2.2 illustrates the drain current  $I_D$  as a function of the drain voltage  $V_D$  for different gate voltages  $V_G$ , as well as the corresponding regions of operation. From Figure 2.2, it is possible to notice that for a gate voltage  $V_G$  greater than the threshold voltage  $V_T$ , the drain current contributes to reduce the drain voltage at which the device enters the avalanche and snapback regions.

To simplify the understanding of the high-voltage operation of the NMOS device, let us assume gate, source, and substrate terminals are grounded (0 V) and an ESD event occurs, accumulating a significant amount of positive charges at the drain terminal in a very short time duration. As the electric potential at the drain terminal increases, majority carriers are pushed away from the reverse-biased drain-substrate junction, which becomes depleted. When the

potential drop across the depletion region reaches a few tenths of a volt, the reverse current is given by (AMERASEKERA; DUVVURY, 2002)

$$I_R = \frac{qADN_CN_V}{L_dN_B} \exp\left(-\frac{E_g}{kT}\right) + \frac{qW}{\tau_e} \sqrt{N_CN_V} \exp\left(-\frac{E_g}{2kT}\right)$$

(2.3)

where q is the electronic charge  $(1.602 \times 10^{-19} \text{ C})$ , A is the pn junction area (proportional to the diffusion area), D is the minority carrier diffusion coefficient,  $N_C$  and  $N_V$  are the density of states in the conduction band and in the valence band, respectively,  $L_d$  is the diffusion length,  $N_B$  is the background doping concentration,  $E_g$  is the energy bandgap (about 1.12 eV for Silicon), k is the Boltzmann's constant  $(1.38 \times 10^{-23} \text{ JK}^{-1})$ , T is the temperature, W is the width of the depletion region and  $\tau_e$  is the effective carrier lifetime. In this case, the polarity of the voltage biasing the drain-substrate junction allows the flow of electrons from the p substrate to the p diffusion and holes from the p diffusion (minority carriers), the reverse current of Equation (2.3) is usually very small.

Increasing  $V_{\rm G}$ Linear (region 1)

V<sub>G</sub> = 0

Drain voltage,  $V_{\rm D}$ Snapback (region 4)

Avalanche (region 3)

Figure 2.2: I-V curves of an NMOS transistor under high-voltage conditions.

Source: Amerasekera and Duvvury (2002)

As the reverse voltage across the depletion layer increases even further, the resulting electric field E eventually reaches a critical value  $E_{crit}$ . Under such critical electric field, some accelerated electrons can impart enough kinetic energy in a collision with the lattice to lift electrons from the valence band into the conduction band, thereby creating new electron-hole pairs, which become free carriers. This process is known as **impact ionization**. The electrons and holes created by impact ionization are themselves also accelerated by the electric field and may also collide with the lattice, creating even more free carriers. An avalanche effect is then

triggered (region 3 in Figure 2.2). The carrier creation rate and the reverse current  $I_R$  rise abruptly. This process is known as **avalanche breakdown**. The critical electric field  $E_{crit}$  depends on the n and p doping concentrations. In a submicron process,  $E_{crit}$  is reached at about  $10^5 \, \mathrm{Vcm^{-1}}$  (AMERASEKERA; DUVVURY, 2002). It means that, in a rough calculation, impact ionization and avalanche breakdown can be triggered when approximately  $10 \, \mathrm{V}$  is applied in a depletion width of  $1 \, \mu \mathrm{m}$ . In the case of an ESD event, the resulting peak voltage may reach not only tens, but hundreds (CDM) or even thousands (HBM) of a volt.

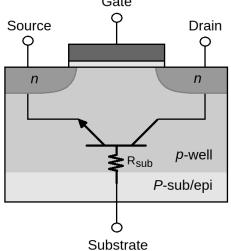

## 2.3 Lateral bipolar transistor activation

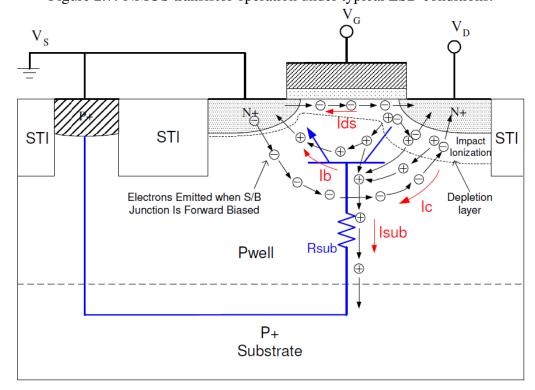

Both NMOS and PMOS devices have an intrinsic lateral bipolar transistor, which eventually turns on under ESD conditions and dominates the device behavior. Figure 2.3 illustrates the schematic of a lateral *npn* transistor in an NMOS device cross section. When the *npn* turns on, part of the NMOS drain becomes the bipolar collector, part of the NMOS source becomes the bipolar emitter and part of the NMOS substrate becomes the bipolar base. The NMOS regions that will effectively compose the lateral bipolar structures will depend on factors such as the effective area of the *pn* junctions that will be biased as well as the current density distribution across the structures.

Figure 2.3: Schematic of the intrinsic lateral npn transistor in an NMOS device cross section.

Gate

Source

Drain

Source: the author

During the avalanche breakdown, electrons are swept across the drain junction towards the drain contact, while holes drift towards the substrate contact, giving rise to a substrate current  $I_{sub}$ . An increase in  $I_{sub}$  also increases the voltage drop in the effective substrate resistance  $R_{sub}$  of Figure 2.3. When this voltage drop reaches the built-in voltage of the source-substrate junction (typically about 0.5 V), i.e.

$$V_{sub} = R_{sub} I_{sub} > 0.5 V$$

(2.4)

the source-substrate junction becomes forward-biased. Electrons are then emitted from the source into the substrate and eventually reach the drain-substrate junction, depending on the distance between the n diffusions (equivalent to the base width of the intrinsic bipolar transistor) and the recombination rate in the substrate, which is dependent on the substrate hole concentration. When the electrons emitted from the source reach the reverse-biased junction, they contribute to the total drain current. With the drain-substrate junction operating in reverse bias condition and the source-substrate junction operating in forward bias condition, the intrinsic bipolar transistor is in the on-state, under active bias condition. The time it takes to the lateral npn to turn on is basically given by the **base transit time** ( $\tau_B$ ), which is dependent on the NMOS gate length L. Under active bias condition, the collector current is given by (AM-ERASEKERA; DUVVURY, 2002)

$$I_c = \frac{qn_i^2 \tilde{D}}{N_B} A \exp\left(\frac{qV_{be}}{kT}\right)$$

(2.5)

where  $n_i$  is the intrinsic carrier concentration,  $\tilde{D}$  is the effective minority carrier diffusion coefficient,  $N_B$  is the total number of impurities per unit area of the base, A is the base-emitter junction area and  $V_{be}$  is the base-emitter voltage. It is important to notice in Equation (2.5) that the collector current  $I_c$  (equivalent to the NMOS drain current) is an exponential function of  $V_{be}$  (equivalent to the voltage drop in the NMOS source-substrate junction).

In this case, the lateral npn transistor operates in **self-triggering** or **self-biasing** mode. The collector-base junction itself, under avalanche breakdown, forward biases the emitter-base junction, self-triggering the transistor. Figure 2.4 illustrates the NMOS cross section schematic with its intrinsic bipolar transistor operating in the self-triggering mode.  $I_{avl}$  represents the current resulting from the avalanche effect in the collector-base (drain-substrate) junction. Its relation with an incident current  $I_{ESD}$  in the high-field region is given by (AMERASEKERA; DUVVURY, 2002)

$$I_{avl} = (M-1)I_{ESD}$$

(2.6)

where M is a multiplication factor in the collector-base (drain-substrate) depletion region. By definition, M is the ratio of the output current  $I_{out}$  to the input current  $I_{in}$  at the avalanching junction, i.e.

$$M = \frac{I_{out}}{I_{in}} \tag{2.7}$$

Source Drain

n

n

p-well

P-sub/epi

Figure 2.4: Avalanche current ( $I_{avl}$ ) schematic.

Substrate

Source: the author

Source: the author

An approximation for M may be obtained by Miller's empirical formulation (MILLER, 1957) (DUTTON, 1975)

$$M = \frac{1}{1 - \left(\frac{V_{cb}}{BV_{cb}}\right)^n} \tag{2.8}$$

where  $V_{cb}$  is the external applied collector-base voltage,  $BV_{cb}$  is the collector-base breakdown voltage and n is a fitting parameter ranging from 2 to 7, depending on the type of junction being considered. With n as a constant, this empirical expression is only accurate for relatively low collector current densities. In the case of large current densities, n may be described as a variable dependent on the collector current to obtain a more accurate M (DIVEKAR; LOVELACE, 1982) (KLOOSTERMAN; GRAAFF, 1989).

Before the lateral npn turns on,  $I_{avl} = I_{sub}$ . Once it turns on, the electrons emitted from the forward-biased emitter-base (NMOS source-substrate) junction that eventually reach the reverse-biased collector-base (NMOS drain-substrate) junction are also subjected to the high electric field in the depletion layer and potentially contribute to the generation of more electronhole pairs by impact ionization, increasing even more the avalanche process and, consequently, the avalanche current  $I_{avl}$ .

## 2.4 Snapback and negative differential resistance

Figures 2.5 and 2.6 illustrate the I-V curves of an npn transistor and an NMOS transistor, respectively, under ESD conditions. When the intrinsic lateral npn transistor turns on and the emitter-base electron current start to contribute to the avalanche process in the collector-base junction, the relation between the base current  $I_b$  and the emitter current  $I_e$  is given by (AM-ERASEKERA; DUVVURY, 2002)

$$I_b \propto (M-1)I_e \tag{2.9}$$

Figure 2.5: I-V curve of an npn transistor in self-bias operation under high-current conditions.

Source: Amerasekera and Duvvury (2002)

As the emitter current  $I_e$  increases, contributing to the avalanche multiplication and to the total current in the collector-base junction, the collector-base voltage  $V_{cb}$  and thus the multiplication factor M start to decrease. At this moment, a snapback characteristic is observed in the  $npn\ I-V$  curve (Figure 2.5), and consequently in the NMOS I-V curve (Figure 2.6). The snapback triggering voltage, i.e. the voltage at which  $V_c$  and  $V_D$  begins to decrease, is represented by  $V_{t1}$  in the Figures 2.5 and 2.6, respectively. Likewise, the snapback triggering current, i.e. the total collector current  $I_c$  at which  $V_c$  begins to decrease or, equivalently, the total drain current  $I_D$  at which  $V_D$  begins to decrease, is represented by  $I_{t1}$ . The condition for snapback is given by (AMERASEKERA; DUVVURY, 2002)

$$\beta \left( M - 1 \right) \ge 1 \tag{2.10}$$

Figure 2.6: I-V curve of an NMOS transistor with  $V_G=0$  under high-current conditions.

Source: Amerasekera and Duvvury (2002) (modified)

where  $\beta$  is the npn common-emitter current gain. The snapback characteristic of the npn transistor is a consequence of the positive feedback loop between the avalanche generation of holes in the collector-base junction and the injection of electrons from the emitter-base junction into the npn base. At high-current conditions, injected electrons and generated holes change the carriers balance, especially in the p region, significantly changing the device conductivity. Such change in the conduction properties of a particular structure region can be defined as **conductivity modulation** (VASHCHENKO; SHIBKOV, 2010). In the case of the lateral npn transistor, the internal conductivity modulation results in a unstable **negative differential resistance** (NDR) effect between its terminals,

$$\frac{dR}{dt} < 0 \tag{2.11}$$

i.e. as the collector current  $I_c$  increases, the collector voltage  $V_c$  decreases,

$$\frac{\Delta V_c}{\Delta I_c} < 0. {(2.12)}$$

Consequently, the electric field across the collector-base depletion region also decreases. The region between  $(V_{t1}, I_{t1})$  and  $V_{sp}$  in the Figures 2.5 and 2.6 illustrates the I-V characteristics of the snapback behavior and the NDR effect.

## 2.5 Low-impedance operation and thermal breakdown

The NDR effect saturates when the npn collector voltage  $V_c$  reaches the minimum level required to maintain the bipolar transistor in a stable on-condition. Such voltage level is denoted

by  $V_{sp}$  in the Figures 2.5 and 2.6. The I-V curve now shows a positive resistance and the device provides a low-impedance path to the injected current.

As the injected current increases, the temperature in the device also rises due to power dissipation, mostly in the reverse-biased collector-base (drain-substrate) junction where the current density and the electric field are both high. At a certain level, the temperature becomes high enough to thermally generate a significant amount of free carriers, which are also accelerated by the electric field in the reverse-biased junction, inducing a new avalanche process due to impact ionization. Once again, the free carriers density changes, especially in the base region of the bipolar (or in the substrate region of the NMOS), and the resulting conductivity modulation leads the device into another unstable differential negative resistance condition. The voltage drops for the second time. This condition is known as **second breakdown** or **thermal breakdown**. The voltage and the current at which the second breakdown takes place is denoted by  $V_{t2}$  and  $I_{t2}$ , respectively, in the Figure 2.6. With further increase in the current, the temperature in hot spots may quickly reach the semiconductor melt temperature and permanently damage the device (AMERASEKERA; DUVVURY, 2002).

### 2.6 Summary of the major ESD effects

Figure 2.7 schematically summarizes the major effects on an NMOS transistor under typical ESD conditions. In this example, we assume the gate is biased and an ESD event occurs at the drain terminal. As the gate-to-source voltage  $V_{GS}$  starts to increase and reaches the threshold voltage  $V_T$ , an n channel is formed below the gate and the device enters first the **linear** and then the **saturation** regions. The drain-to-source current is denoted by  $I_{ds}$  in Figure 2.7. With the high ESD-induced current levels, the drain capacitance rapidly charges up, generating a high electric field across the reverse-biased drain-substrate junction. Such high electric field eventually causes carriers generation in the depletion region due to impact ionization. These new carriers are also subjected to the high electric field and consequent impact ionization, generating even more carriers. With the resulting avalanche effect, the device enters the avalanche region. Electrons flow towards the drain contact while holes flow towards the substrate contact, giving rise to a substrate current (denoted by  $I_{sub}$  in Figure 2.7). When the resulting voltage drop across the effective substrate resistance (denoted by  $R_{sub}$  in Figure 2.7) reaches about 0.5 V, the source-substrate junction becomes forward-biased and the lateral npn transistor is then triggered, operating in self-biasing mode. The npn collector and base currents are denoted by  $I_c$  and  $I_b$ , respectively, in Figure 2.7. With the positive feedback loop between the avalanche generation of holes in the collector-base junction and the injection of electrons from the emitter-base junction into the base, the device exhibits a **negative differential resistance** and enters the **snapback region**. In this region, the drain voltage decreases with an increase in the drain current until a stable holding voltage condition is reached. The device now starts to provide a low and positive impedance path to the ESD current. As the incident current increases even more, the temperature becomes high enough to thermally generate a significant amount of new carriers and the device eventually enters the **thermal** or **second breakdown region**. In this region, the temperature in hot spots may permanently damage the device.

Figure 2.7: NMOS transistor operation under typical ESD conditions.

Source: Zhou et al. (2005a)

#### 3 MOSFET MACROMODELS FOR ESD CIRCUIT SIMULATION

Macromodels might not accurately reflect the target circuit behavior under every possible condition, since they might not necessarily include all available circuit parameters. Despite such limitation, under specific conditions, a macromodel may significantly reduce the model complexity and thus its simulation speed, as well as the modeling time, while maintaining a reasonable accuracy. Also, it may help to resolve convergence issues sometimes present in more complex and detailed models. In the context of this work, macromodels are particularly interesting to describe the large current and voltage characteristics of a MOSFET under ESD stress, which are typically not well covered by most standard SPICE compact models.

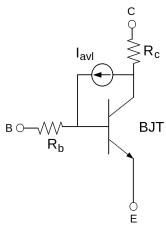

## 3.1 Modeling the avalanche breakdown with a parallel BJT and a current source

First efforts on modeling the avalanche breakdown for circuit simulation started in the early 70's (POON; MECKWOOD, 1972) (FOSSUM, 1973) to overcome a limitation of BJT compact models available at that time, especially of those based on Ebers-Moll (EBERS; MOLL, 1954) and Gummel-Poon (GUMMEL; POON, 1970) models. Figure 3.1 illustrates Dutton's bipolar equivalent circuit (DUTTON, 1975), where a voltage-dependent current source  $I_{avl}$  is added between the collector and the base resistances,  $R_c$  and  $R_b$ , respectively, of an Ebers-Moll-based compact model to include the avalanche breakdown effect. In this case,  $I_{avl}$  is given by

$$I_{avl} = K_1(M-1)I_{ES} \exp\left(\frac{qV_{be}}{kT}\right)$$

(3.1)

where  $K_1$  is a fitting parameter, M is given by the Equation (2.8),  $I_{ES}$  is the collector intercept current, q is the electronic charge,  $V_{be}$  is the base-emitter voltage, k is the Boltzmann's constant and T is the temperature. Equation (3.1) shows the exponential dependency of the avalanche current on the base-emitter voltage.

Concerning the model implementation, the inclusion of the voltage-dependent current source between the collector and the base resistances required direct access to the internal structures of the BJT compact model adopted. Besides, the circuit simulation program had to be modified to include not only  $I_{avl}$  equation, but also its partial derivatives and the avalanche conductance and transconductance equations. Although the implementation was not straightforward, Dutton's model represented a significant contribution on modeling the avalanche breakdown of BJTs for circuit simulation.

Figure 3.1: Modeling the avalanche breakdown of a BJT with a current source ( $I_{avl}$ ).

Source: the author

Likewise, MOSFET compact models also had (and still have) limitations on modeling the device high-current operation. Figure 3.2 illustrates one of the first equivalent circuits adopted to model the avalanche breakdown of a short-channel MOSFET for circuit simulation (SUN et al., 1978). The role of the parallel BJT is to model the influence of the intrinsic lateral bipolar transistor on the NMOS device. The voltage-dependent current source  $I_{avl}$  aims to model the avalanche breakdown effect.  $R_{sub}$  intends to model the NMOS substrate resistance, which may also include the conductivity modulation effect if a current-dependent resistance is adopted. Later, analytical models including the high-current effects in MOSFETs were published by Hu and Chi (1982) and Hsu et al. (1982). However, despite the analytical results were comparable to measured data, these models were not implemented for circuit simulation. Actually, given the amount of equations and conditions, their implementation would require deep and complicated modifications in the MOSFET compact models and in the circuit simulator.

Figure 3.2: Modeling the avalanche breakdown of an NMOS transistor with a parallel BJT and a current source  $(I_{avl})$ .

Source: the author

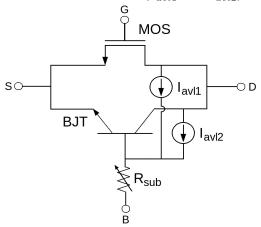

Probably the first successful application of a short-channel MOSFET breakdown model for circuit simulation was performed by Pinto-Guedes and Chan (1988). Their model consisted in a modified version of the analytical model proposed by Hsu et al. (1982), where the impact ionization current of the substrate was replaced by an improved version of the impact ionization current model published by Mar, Li and Yu (1982). Also, a channel length dependence was included in the gain of the intrinsic lateral bipolar transistor to better describe the I-V characteristics for a wider range of MOSFET channel lengths. Figure 3.3 illustrates the resulting equivalent circuit. Two current sources represent two components of the impact ionization current.  $I_{avl1}$  represents the current component due to avalanche multiplication of the MOSFET channel current, which is given by

$$I_{avl1} = (M_{CH} - 1)I_{CH} (3.2)$$

where  $M_{CH}$  the is impact ionization multiplication factor for the channel current and  $I_{CH}$  is the MOSFET channel current. The other component,  $I_{avl2}$ , represents the current due to avalanche multiplication of the intrinsic lateral BJT emitter current, which is given by

$$I_{avl2} = \alpha \left( M_e - 1 \right) I_e \tag{3.3}$$

where  $\alpha$  is the bipolar common-base current gain,  $M_e$  is the impact ionization multiplication factor for the emitter current and  $I_e$  is the bipolar emitter current. The bipolar current gain  $\alpha$  can be given by

$$\alpha = \gamma \, \alpha_T \tag{3.4}$$

where  $\gamma$  is the emitter injection efficiency and  $\alpha_T$  is the base transport factor of the lateral BJT. However, to account for the channel length dependence of the model, an empirical expression for  $\alpha$  was used by Pinto-Guedes and Chan, which is given by

$$\alpha = \frac{\alpha_0}{1 + \frac{L}{L_0}} \tag{3.5}$$

where  $\alpha_0$  and  $L_0$  are two characterization constants and L is the effective channel length of the MOSFET.

Concerning  $R_{sub}$  in Figure 3.3, it is possible to use a current-dependent resistor to account for the conductivity modulation effect in the substrate, however Pinto-Guedes and Chan have neglected this effect and assumed  $R_{sub}$  as being constant to simplify the model. The implementation of the model basically consisted in adding the current components and the con-

ductances related to the intrinsic BJT directly into the circuit simulator. However, the task of implementing equations directly into the circuit simulator is not straightforward, especially considering the simulator source code is usually not available.

Figure 3.3: Modeling the avalanche breakdown of an NMOS transistor with a parallel BJT and two current sources ( $I_{avl1}$  and  $I_{avl2}$ ).

Source: the author

Significant advances on modeling the avalanche breakdown with a parallel BJT and a current source have also been made by Amerasekera et al. (1996). Based on the equivalent circuit of Figure 3.2, they developed a set of equations which describes the high-current operation of a MOSFET and implemented these equations directly in a circuit simulator. In this model, the avalanche current  $I_{avl}$  is given by

$$I_{avl} = (M - 1)(I_{DS} + I_c) (3.6)$$

where M is the avalanche multiplication factor in the high-field region of the drain,  $I_{DS}$  is the drain-to-source current (from the standard MOSFET compact model adopted) and  $I_c$  is the bipolar collector current. The avalanche multiplication factor in Equation (3.6) is given by

$$M = \frac{1}{1 - K_1 \exp\left(-\frac{K_2}{V_D - V_{D_{sat}}}\right)}$$

(3.7)

where  $K_1$  and  $K_2$  are fitting parameters,  $V_D$  is the applied drain voltage and  $V_{D_{sat}}$  is the drainsource saturation voltage. The Miller's empirical formulation of M described by Equation (2.8) was not used by Amerasekera *et al.* because it does not take into account the effect of the gate voltage  $V_G$  on the electric field at the drain junction. Such effect of  $V_G$  is then included through  $V_{D_{sat}}$ , which is given by

$$V_{D_{sat}} = \frac{V_G - V_T}{a_1 + b_1 (V_G - V_T)}$$

(3.8)

where  $V_T$  is the MOSFET threshold voltage,  $a_1$  and  $b_1$  are parameters of the standard MOSFET compact model adopted, with  $b_1$  dependent on the channel length. The bipolar collector current  $I_c$  in Equation (3.6) is given by

$$I_c = I_{oc} \left[ \exp\left(\frac{V_{be}}{V_{thermal}}\right) - \exp\left(\frac{V_{bc}}{V_{thermal}}\right) \right]$$

(3.9)

where  $I_{oc}$  is the reverse saturation current due to the diffusion of electrons in the base of the npn,  $V_{be}$  is the voltage across the base-emitter junction,  $V_{thermal}$  is the thermal voltage (kT/q) and  $V_{bc}$  is the voltage across the base-collector junction. The bipolar base-emitter current  $I_b$ , on the other hand, is modeled by

$$I_b = I_{oe} \left[ \exp\left(\frac{V_{be}}{V_{thermal}}\right) - 1 \right]$$

(3.10)

where  $I_{oe}$  is the reverse saturation current due to the diffusion of holes in the emitter of the npn,  $V_{be}$  and  $V_{thermal}$  are the same parameters of Equation (3.9). The substrate resistance in the circuit of Figure 3.2 is given by

$$R_{sub} = \frac{V_{be}}{I_{sub}} \tag{3.11}$$

where  $V_{be}$  is the voltage across the base-emitter junction and  $I_{sub}$  is the substrate current (measured at the snapback point).

It is important to observe the discontinuity of M in Equation (3.7). Such discontinuity may introduce simulation convergence issues. Therefore, it is preferably to use a continuous function instead, such as the one proposed by Lim et al. (1997)

$$M = \exp[K_1(V_D - V_{D_{sat}} - d_1)] + \exp[K_2(V_D - V_{D_{sat}} - d_2)]$$

(3.12)

where  $K_1$ ,  $K_2$ ,  $d_1$ ,  $d_2$  are fitting parameters,  $V_D$  is the applied drain voltage and  $V_{D_{sat}}$  is the drain-to-source saturation voltage.

Last, it is also important to notice that the implementation of the equation set mentioned above in a circuit simulator is far from being a straightforward task. Besides, a parameter extraction methodology is required not only for the MOSFET compact model but also for  $K_1$ ,  $K_2$ ,  $I_{oc}$  and  $I_{oe}$  parameters of the equation set.

## 3.2 Modeling the avalanche breakdown with BSIM3 and VBIC compact models

The efforts on modeling the avalanche breakdown with a parallel BJT and a current source detailed in Section 3.1 were mostly motivated by the lack of such feature in the compact models available at that time, such as the BSIM models for the MOSFET and the Ebers-Moll and Gummel-Poon models for the BJT. The first popular BJT compact model to include the avalanche breakdown effect was VBIC (MCANDREW et al., 1996), by implementing the avalanche model proposed by Kloosterman and Graaff (1989). In fact, improvements in VBIC over Gummel-Poon compact model included not only a base-collector avalanche model but also a base-emitter breakdown model, a self-heating model, an improved depletion and diffusion charge model, an improved temperature model and an Early effect model based on depletion charge (MCANDREW et al., 2003). With the VBIC compact model release, the need of a current source to model the avalanche breakdown has been extinguished.

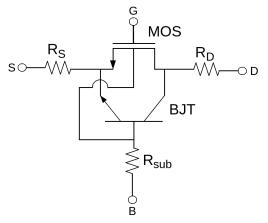

One of the first macromodels using advanced MOSFET and BJT compact models for ESD circuit simulation was proposed by Zhou et al. (2005b). Figure 3.4 illustrates the macromodel equivalent circuit, consisting of standard SPICE components only. The MOSFET is modeled with BSIM3v3 and the intrinsic BJT is modeled with VBIC.  $R_{sub}$  represents the substrate resistance,  $R_S$  and  $R_D$  represent the source and the drain resistances, respectively. In this case, BSIM3v3 and VBIC parameters were extracted using a regular methodology, while  $R_{sub}$  was extracted from snapback curves of GGNMOS structures measured with TLP.

Figure 3.4: Modeling the avalanche breakdown with BSIM3 and VBIC compact models.

Source: the author

The resulting drain-to-substrate current in the macromodel proposed by Zhou *et al.* is mainly composed by the substrate current of BSIM3v3 and the collector-base avalanche current

of VBIC. The substrate current in BSIM3v3, which includes the impact ionization effect, is modeled by (LIU et al., 1999)

$$I_{sub} = \frac{\alpha_0 + \alpha_1 L_{eff}}{L_{eff}} (V_{DS} - V_{DS_{eff}}) \exp\left(-\frac{\beta_0}{V_{DS} - V_{DS_{eff}}}\right) \cdot \frac{I_{DS_0}}{1 + \frac{R_{DS} I_{DS_0}}{V_{DS_{eff}}}} \left(1 + \frac{V_{DS} - V_{DS_{eff}}}{V_A}\right)$$

(3.13)

where  $\alpha_0$  is the first parameter of impact ionization current (fitting parameter),  $\alpha_1$  is the channel length scaling parameter of impact ionization current (fitting parameter),  $L_{eff}$  is the effective channel length of the MOSFET,  $V_{DS}$  is the drain-to-source voltage,  $V_{DS_{eff}}$  is the effective drain-to-source voltage, which is modeled as a function that follows  $V_{DS}$  in the linear region and tends to  $V_{Dsat}$  in the saturation region,  $\beta_0$  is a  $V_{DS}$  dependent parameter of impact ionization current (fitting parameter),  $I_{DS_0}$  is the drain-to-source current without considering the impact ionization,  $R_{DS}$  is the parasitic drain-to-source resistance and  $V_A$  is the Early voltage due to the substrate current. It is possible to notice in Equation (3.13) the exponential dependency of the substrate current on the drain-to-source voltage.

The avalanche current in the collector-base junction is, in turn, modeled in VBIC by (MCANDREW et al., 1996)

$$I_{avl} = (I_{cc} - I_{bc})A_{VC_1}(P_C - V_{bci}) \exp\left[-A_{VC_2}(P_C - V_{bci})^{ME-1}\right]$$

(3.14)

where  $I_{cc}$  is the forward transport current (or the collector current without the avalanche effect),  $I_{bc}$  is the base-collector component of the base current,  $A_{VC_1}$  and  $A_{VC_2}$  are fitting parameters,  $P_C$  is the built-in potential of the base-collector junction,  $V_{bci}$  is the intrinsic voltage across the base-collector junction and ME is the grading coefficient of the base-emitter junction.

The most significant contribution of the macromodel proposed by Zhou *et al.* is its straightforward CAD implementation using standard SPICE components only. It improves the macromodel availability since there is no need of implementing special equations directly in the circuit simulator. When compared to previous models discussed in Section 3.1, the improved BSIM3 and VBIC compact models reduce the convergence issues. VBIC also includes other relevant effects for ESD circuit simulation such as a self-heating model, an improved temperature model and an improved depletion and diffusion charge model. One of the major drawbacks of this macromodel is that VBIC is restricted to model the avalanche effect at low current densities only (weak avalanche) (BERKNER, 2002).

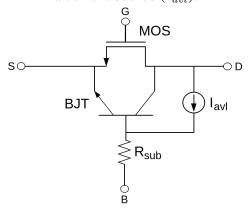

### 3.3 Snapback modeling with BSIM4 and MEXTRAM-based compact models

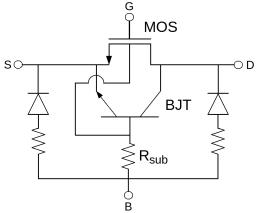

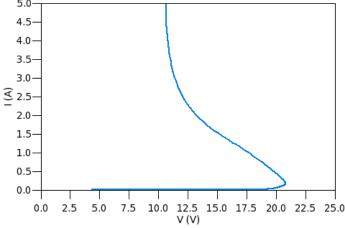

After introducing a macromodel using BSIM3v3 and VBIC compact models (detailed in Section 3.2), Zhou, Hajjar and Lisiak (2006) introduced a new macromodel using BSIM4 and a proprietary MEXTRAM-based BJT compact model instead. Figure 3.5 illustrates the equivalent circuit, which is similar to the equivalent circuit of Figure 3.4 but omitting the  $R_S$  and  $R_D$  resistances. In this case, the parameters of the BSIM4 and the MEXTRAM-based compact models were also extracted using a regular methodology and  $R_{sub}$  was also extracted from the snapback curves of GGNMOS structures measured with TLP.

SO MOS

BJT

R<sub>sub</sub>

Figure 3.5: Snapback modeling with BSIM4 and MEXTRAM-like compact models.

Source: the author

The total substrate current of this macromodel is the sum of the substrate terminal current in BSIM4 and the avalanche current in the MEXTRAM-based BJT compact model. The substrate current due to impact ionization in BSIM4 is the same as that in BSIM3v3, described by Equation (3.13) (MORSHED et al., 2011). What is new in BSIM4 and relevant to ESD circuit simulation is that, besides the substrate current due to impact ionization, the total substrate terminal current also includes the gate-induced drain leakage current  $I_{GIDL}$  and the gate-induced source leakage current  $I_{GISL}$ .  $I_{GIDL}$  in BSIM4 (using the compact model default settings) is modeled by (MORSHED et al., 2011)

$$I_{GIDL} = AGIDL W_{eff_{CJ}} N_f \frac{V_{DS} - V_{GSe} - EGIDL}{3 T_{oxe}}$$

$$\cdot \exp\left(-\frac{3 T_{oxe} BGIDL}{V_{DS} - V_{GSe} - EGIDL}\right) \frac{V_{DB}^3}{CGIDL + V_{DB}^3}$$

(3.15)

where AGIDL is the pre-exponential coefficient of  $I_{GIDL}$  (fitting parameter),  $W_{eff_{CJ}}$  is the effective drain diffusion width for parasitics modeling,  $N_f$  is the number of device fingers,