# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

# Functional Timing Analysis of VLSI Circuits Containing Complex Gates

by

JOSÉ LUÍS ALMADA GÜNTZEL

Thesis submitted as partial fulfillment of the requirements for obtaining the degree of "Doutor em Ciência da Computação"

Prof. Ricardo Augusto da Luz Reis Advisor

Porto Alegre, November 2000.

#### C.I.P. - Catalogação na Publicação

#### Güntzel, José Luís Almada

Functional Timing Analysis of VLSI Circuits Containing Complex Gates / by José Luís Almada Güntzel. – Porto Alegre: PPGC da UFRGS, 2000. 182 p.: il.

Tese (doutorado) — Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR — RS, 2000. Orientador: Reis, Ricardo Augusto da Luz.

1. Microeletrônica. 2. Ferramentas de CAD para Microeletrônica. 3. Verificação de Timing. 4. Análise de Timing. 5. Portas Lógicas Complexas. I. Reis, Ricardo Augusto da Luz. II. Título.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitora: Profa. Wrana Panizzi

Pró-Reitor de Ensino: Prof. José Carlos Ferraz Hennemann

Pró-Reitor Adjunto de Pós-Graduação: Prof. Philippe Olivier Alexandre Navaux Diretor do Instituto de Informática: Prof. Philippe Olivier Alexandre Navaux

Coordenadora do PPGC: Profa. Carla Maria Dal Sasso Freitas

Bibliotecária Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

# Acknowledgments

This work is the result of more than five years of research. During this time many people contributed to its development and I will probably forget to mention somebody that helped me along the way.

First of all, I thank my family for their support and constant encouragement, mainly during the difficult periods when I could not see the light at the end of the tunnel. I also thank my fiancée, Margarida, for her friendship and patience, accepting my excuses for each working weekend.

I also thank my advisor, Ricardo Reis, for his unconditional support and friendship.

Timing analysis became the focus of my research since the time I have spent at the Laboratoire d'Informatique, de Robotique et de Micro-électronique de Montpellier - LIRMM (France). I acknowledge Prof. Daniel Auvergne who kindly accepted me in his working group. I thank Nadine Azemard, my direct supervisor, and Séverine Cremoux, my team mate, for their willingness in working with me and for their patience with my poor French skills. During 1996, the year I spent in France, I had the chance of meeting many interesting people whose friendship I really miss. Ricardo Pires, Véronique Moreda, Daniel Séverac, Éric Vanier, Jean-Michel Daga, Lionel Torres and many others, I thank you for all moments we have shared together. Still during that time, I have the support and friendship of many other people that I previously knew. I am particularly indebted with André Reis, who has hosted me during the first two weeks in France. I also thank André Reis for our discussions on logic synthesis, technology mapping, timing analysis, BDDs, test and so many other philosophical topics! I should also mention Renato Ribas, Gilson Wirth and Reginaldo Tavares for both technical and philosophical discussions.

During the other four years of research, I had the help of undergraduate and graduate students. I specially thank Ana Cristina Medina Pinto for helping me in the tediously task of testing so many versions of path enumeration algorithms. I also thank her for our endless discussions on ATPG-based timing analysis. I also thank Guilherme Dal Pizzol for helping me with the *ad hoc* timing analysis of carry skip adders and Eduardo d'Ávila for the first implementation of the extended three-valued timed calculus for complex gates.

During all the five years I could always count with the support and friendship of Fernando Moraes, including some "on-line" helps during my stay in France, for what I sincerely acknowledge.

Although timing analysis is my main topic of interest, I could not resist checking other topics. In this sense, I thank to Fernanda Lima, Luigi Carro and Marcelo Johann for having shared several discussions and some papers on Masterslices Architectures for FPGAs. I also thank to Fábio Klein Ferreira for developing the path-based power evaluation tool, as final paper of his undergraduate course.

I could not forget to mention the friendship and support of all colleagues of the UFRGS Microelectronics Group (GME) along all these years. So, thank to all of you: Marcelo Johann, Marcus Kindel, João Leonardo Fragoso, Fernanda Lima, Érika Cota, César Zeferino, Eduardo Costa, Jung Choi, Leandro Indrusiak, José Luis Gómez, Rosaldo Rossetti, Alessandro Adario, Márcio Kreutz and so many others. I also thank to all professors of the GME for their

unquestionable contribution to my research profile: Ricardo Reis, Sergio Bampi, Tiaraju Wagner, Altamiro Susin, Luigi Carro, Marcelo Lubaszewski and Flávio Wagner.

During the first four years of this work, including the year I was in France, I had the financial support of CAPES Brazilian Agency (Coordenação de Aperfeiçoamente de Pessoal de Nível Superior), for what I gratefully acknowledge.

Finally, I thank God for providing me with so many opportunities of learning!

To Margarida

# **Table of Contents**

| List of Abbreviations                                               | •••       |

|---------------------------------------------------------------------|-----------|

| List of Figures                                                     |           |

| List of Tables                                                      |           |

| Abstract                                                            |           |

| Resumo                                                              | •••       |

| 1 Introduction                                                      |           |

| 1.1 Thesis Organization                                             |           |

| 2 The Timing Analysis Approach                                      |           |

| 2.1 Topological Timing Analysis                                     |           |

| 2.2 False Paths                                                     |           |

| 2.3 Functional Timing Analysis and Circuit Delay Computation Models | ·         |

| 2.4 Component Delay Models                                          | •••       |

| 2.5 Gate Delay Computation Models                                   |           |

| 2.6 Robustness and Correctness of FTA Algorithms                    | ••••      |

| 2.7 Delay Computation Models, Path Sensitization and FTA Algorithms | •         |

| 3 Timing Analysis Related Terminology                               |           |

| 3.1 Boolean Algebra                                                 | . <b></b> |

| 3.2 Test Generation Terminology                                     | •••       |

| 3.3 Delay Testing and Timing Analysis Terminology                   |           |

| 4 Path Sensitization Criteria and Delay Computation Models          | •••       |

| 4.1 Delay Computation Models and the Robustness Property            |           |

| 4.2 Path Sensitization Criteria                                     |           |

| 4.2.1 Static Sensitization                                          | ••••      |

| 4.2.2 Static Cosensitization                                        | ••••      |

| 4.2.3 Viability Analysis                                            |           |

| 4.2.4 Exact Floating-Mode Sensitization                             | •         |

| 4.2.5 Other Sensitization Criteria                                  | •••       |

| 4.3 Qualitative Comparison Between Sensitization Criteria           |           |

| 5 Functional Timing Analysis Algorithms                             |           |

| 5.1 Classification of FTA Algorithms and Historical Review          | •••       |

| 5.2 ATG-Based Single Path Sensitization Algorithms                  |           |

| 5.2.1 The Best-First Search Path Enumeration Procedure of Yen et al. [YEN89]                                  |       |

|---------------------------------------------------------------------------------------------------------------|-------|

| 5.2.2 Best-First Search Path Enumeration Considering Different Fall and Rise Gate Delays                      |       |

| 5.3 ATG-Based Multiple Path Sensitization Algorithms                                                          |       |

| 5.3.1 The PODEM Algorithm                                                                                     |       |

| 5.3.2 Cube Simulation                                                                                         |       |

| 5.3.3 Timed Test Generation                                                                                   |       |

| 5.3.4 Backtrace                                                                                               |       |

| 5.4 SAT-Based Multiple Path Sensitization Algorithms                                                          |       |

| 5.4.1 Philosophy of the SAT-Based Method of [MCG93]                                                           |       |

| 5.4.2 Ternary Delay Simulation and Waveform Calculus                                                          |       |

| 5.4.3 Computing the Floating Delay under the XBD0 Model                                                       |       |

| 6 Functional Timing Analysis of Combinational Circuits Containing<br>Complex Gates                            |       |

| 6.1 Technology Mapping and Layout Generation for Circuits Containing Complex Gates 6.1                        |       |

| 6.1.1 Simple Gates, General Complex Gates and Static CMOS Complex Gates                                       |       |

| 6.2 The Applicability of Existing Functional Timing Analysis Techniques for Circuits Containing Complex Gates |       |

| 6.3 ATPG-Based FTA of Circuits Containing Complex Gates 6.3                                                   |       |

| 6.3.1 Extending the Timed-Calculus to Complex Gates                                                           |       |

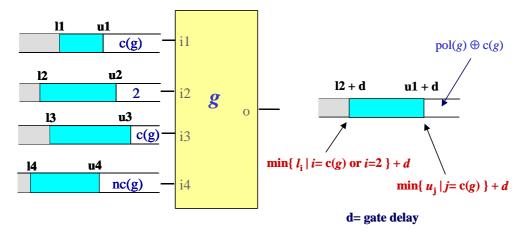

| 6.3.2 The Floating Delay of a Gate                                                                            | •••   |

| 6.3.3 Gate Delay Computational Models and Timed Forward Implication for SCCGs $\dots$                         | · • • |

| 6.3.4 Timed Backward Implication for SCCGs                                                                    | · • • |

| 7 Conclusions                                                                                                 |       |

| 7.1 Future Work                                                                                               |       |

| <b>Appendix 1</b> The Need for Functional Timing Analysis: a Case Study                                       |       |

| Appendix 2 Gate Delay Computation Models and the Complexity of Best-<br>First Search Procedures               |       |

| Appendix 3 Análise de Timing Funcional de Circuitos VLSI Contendo Portas Complexas                            |       |

| References                                                                                                    |       |

## **List of Abbreviations**

| ATPG | Automatic | Test Pattern | Generation |

|------|-----------|--------------|------------|

|      |           |              |            |

- BDD Binary Decision Diagram

- CAD Computer-Aided Design

- BFS Breadth-First Search

- CMOS Complementary Metal-Oxide Silicon

- Csa Carry-skip Adder

- DAG Direct Acyclic Graph

- DFS Depth-First Search

- EDA Electronic Design Automation

- FTA Functional Timing Analysis

- FSM Finite State Machine

- FUCAS FUll Custom Automatic Synthesis

- iff if and only if

- mdt Maximal Delay to Node t

- MSF Multiple Stuck Fault

- ps picoseconds

- SCCG Static CMOS Complex Gate

- sgd single gate delay

- spgd single pair gate delay

- SAT satisfiability

- SSF Single Stuck Fault

- TTA Topological Timing Analysis

- VLSI Very Large Scale Integration

- XDB Extended Bounded Delay Model

- XBD0 Extended Bounded-Zero Delay Model

# **List of Figures**

| FIGURE 1.1 - Synchronous sequential circuit model.                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| FIGURE 2.1 - Combinational circuit example.                                                                                                 |

| FIGURE 2.2 - Processed DAG for the circuit example of figure 2.1.                                                                           |

| FIGURE 2.3 - First example of false path: Hrapcenko's circuit.                                                                              |

| FIGURE 2.4 - Second example of false path: a 2-bit carry-skip adder.                                                                        |

| FIGURE 2.5 - The delay of circuits depends upon the type of inputs considered                                                               |

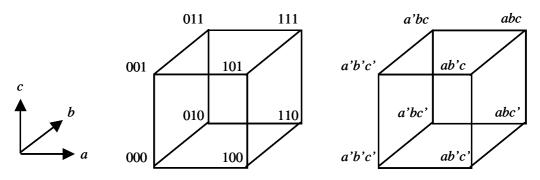

| FIGURE 3.1 - Cube representation for the 3-dimensional Boolean space                                                                        |

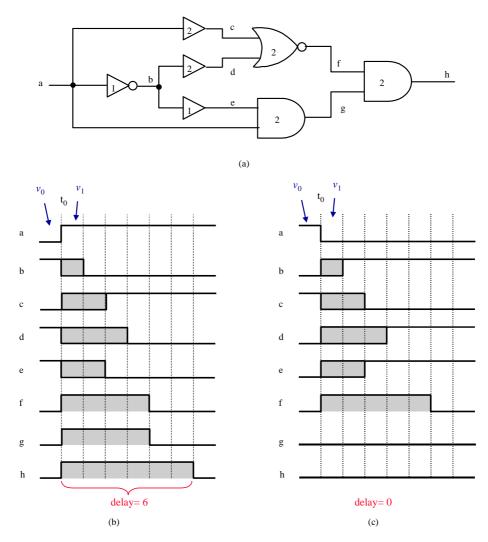

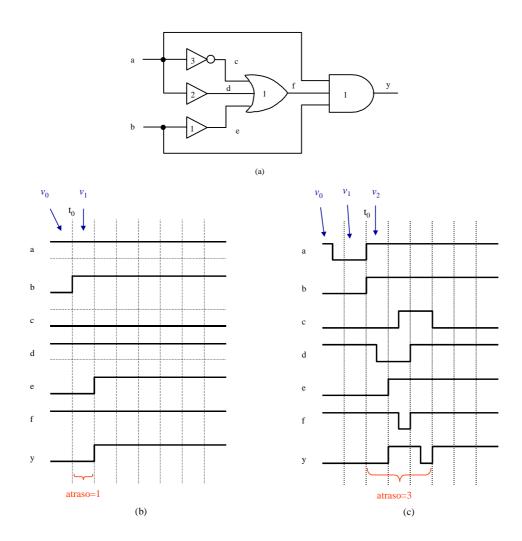

| FIGURE 4.1 - Transition delay with fixed gate delays: test circuit (a) and timing diagrams (b),(c).                                         |

| FIGURE 4.2 - Transition delay with fixed gate delays: another instance of the test circuit of figure 4.1a (a) and timing diagrams (b),(c)   |

| FIGURE 4.3 - Transition delay with unbounded gate delays: test circuit of figure 4.1a with unbounded delays (a) and timing diagrams (b),(c) |

| FIGURE 4.4 - Conditions for Static Sensitization.                                                                                           |

| FIGURE 4.5 - Example of static sensitization of a path.                                                                                     |

| FIGURE 4.6 - Static sensitization on the csa example.                                                                                       |

| FIGURE 4.7 - Static sensitization underestimating circuit delay.                                                                            |

| FIGURE 4.8 – Conditions for static cosensitization.                                                                                         |

| FIGURE 4.9 - Example of static cosensitization of paths.                                                                                    |

| FIGURE 4.10 - Static cosensitization can be pessimistic.                                                                                    |

| FIGURE 4.11 - Conditions for viability.                                                                                                     |

| FIGURE 4.12 - Example of viable path that is not statically cosensitizable                                                                  |

| FIGURE 4.13 - Conditions for exact floating-mode sensitization.                                                                             |

| FIGURE 4.14 - First example of exact floating-mode sensitization                                                                            |

| FIGURE 4.15 - Second example of exact floating-mode sensitization.                                                                          |

| FIGURE 4.16 - Third example of exact floating-mode sensitization                                                                            |

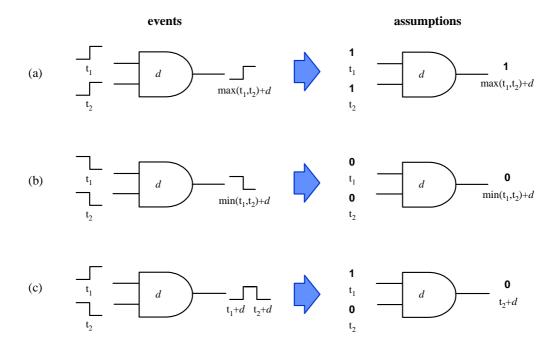

| FIGURE 4.17 - Fundamental assumptions made in single-vector exact floating mode.                                                            |

| FIGURE 4.18 - Comparison between sensitization criteria.                                                                                    |

| FIGURE 5.1 - Single path sensitization procedure.                                                                                           |

| FIGURE 5.2 - DAG for circuit of figure 2.1, pre-processed according to the best-first search procedure.                                     |

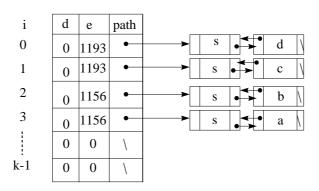

| FIGURE 5.3 - k-list structure initialized with the first partial paths of the circuit of figure 5.2.                                        |

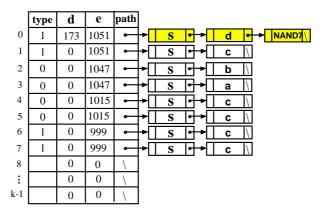

| FIGURE 5.4 - k-list structure for the best-first procedure that considers separate fall and rise delays.                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FIGURE 5.5 - Pseudocode for the topmost call of the PODEM algorithm                                                                                                      |

| FIGURE 5.6 - Pseudocode for the first search procedure.                                                                                                                  |

| FIGURE 5.7 - Pseudocode for the second search procedure                                                                                                                  |

| FIGURE 5.8 - PODEM algorithm example.                                                                                                                                    |

| FIGURE 5.9 - Binary decision tree for PODEM algorithm.                                                                                                                   |

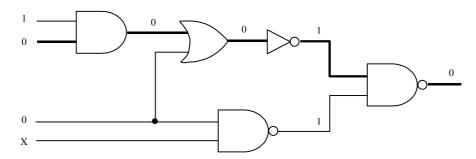

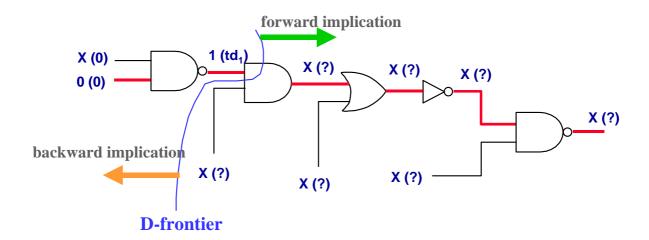

| FIGURE 5.10 - Cube simulation using timed calculus.                                                                                                                      |

| FIGURE 5.11 - Timed test generation example.                                                                                                                             |

| FIGURE 5.12 - Backtrace example.                                                                                                                                         |

| FIGURE 5.13 - Basic operation of SAT-based FTA algorithms.                                                                                                               |

| FIGURE 5.14 - Example of ternary waveform.                                                                                                                               |

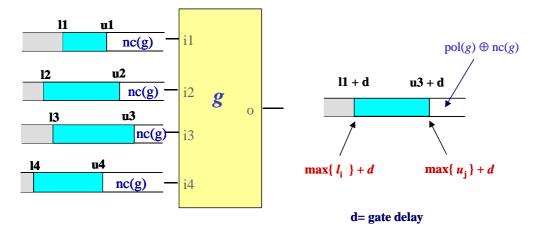

| FIGURE 5.15 - Delay model for a gate in the wave space                                                                                                                   |

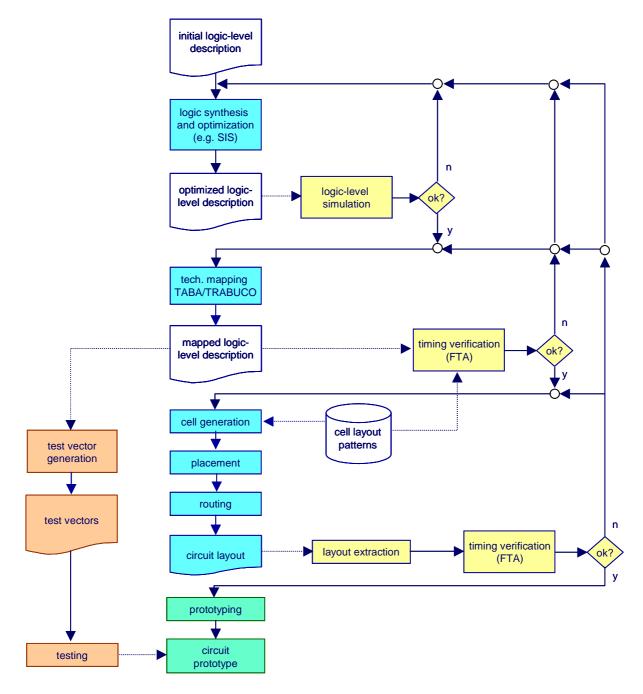

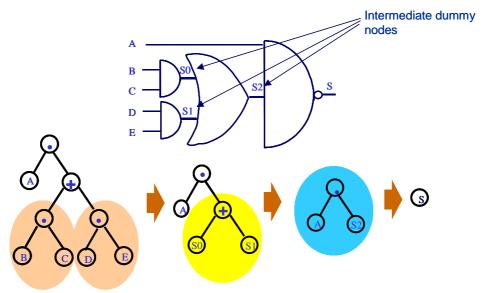

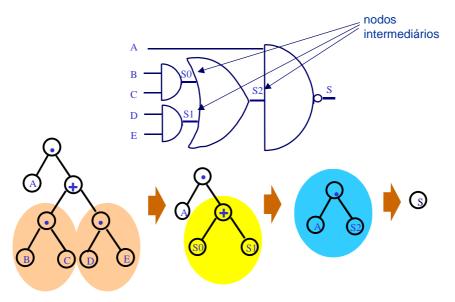

| FIGURE 6.1 - Physical design flow using the FUCAS layout generation strategy                                                                                             |

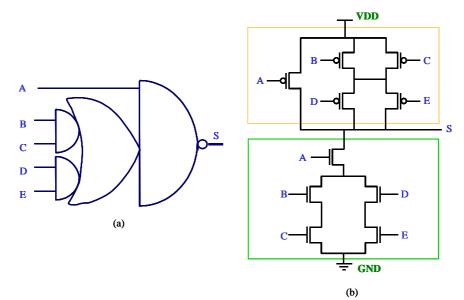

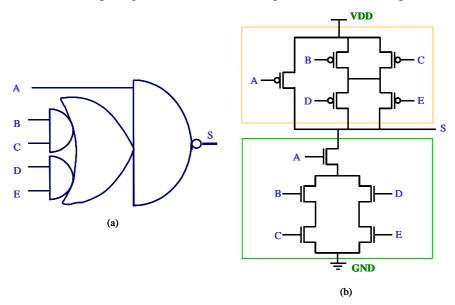

| FIGURE 6.2 - Example of SCCG                                                                                                                                             |

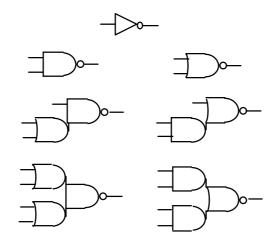

| FIGURE 6.3 - Elements of the virtual library SCG(2,2)                                                                                                                    |

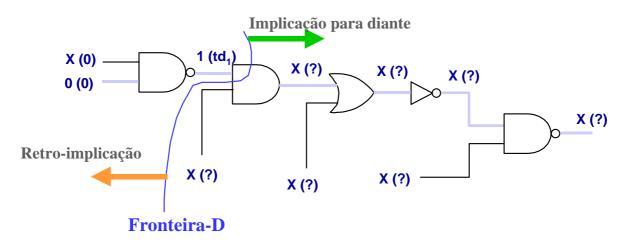

| FIGURE 6.4 - Timed-test generation procedure applied to a single-output circuit                                                                                          |

| FIGURE $6.5$ - Pseudo-code for the topmost call of the timed-test generation procedure .                                                                                 |

| FIGURE 6.6 - Pseudo-code for the first search procedure                                                                                                                  |

| FIGURE 6.7 - Pseudo-code for the second search procedure                                                                                                                 |

| FIGURE 6.8 - Pseudo-code for the imply procedure                                                                                                                         |

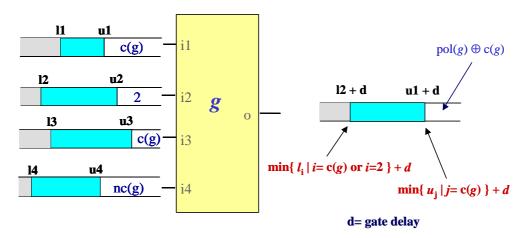

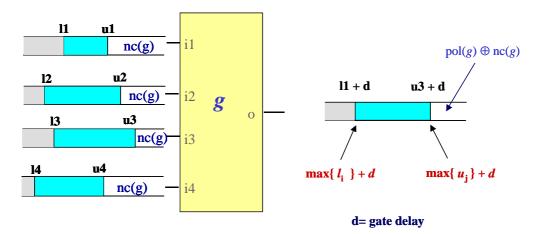

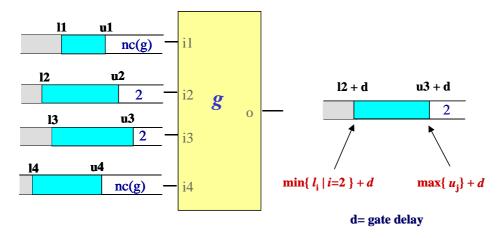

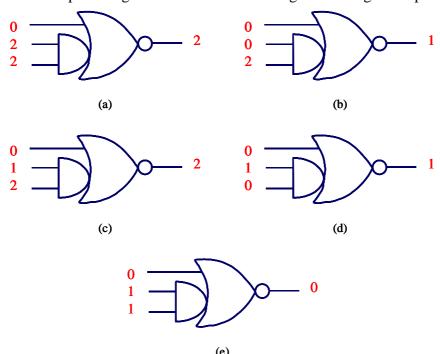

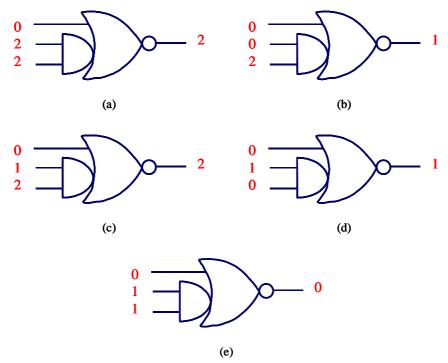

| FIGURE 6.9 - Three-valued timed calculus for group 1                                                                                                                     |

| FIGURE 6.10 - Three-valued timed calculus for group 2                                                                                                                    |

| FIGURE 6.11 - Three-valued timed calculus for group 3                                                                                                                    |

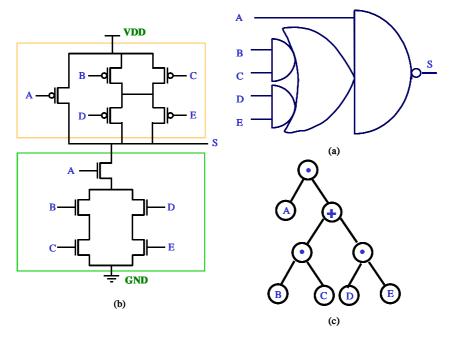

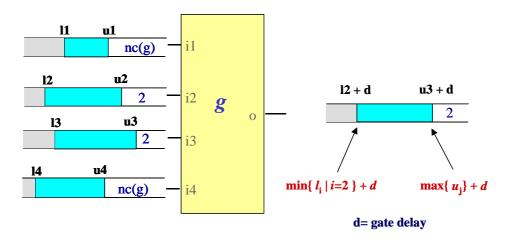

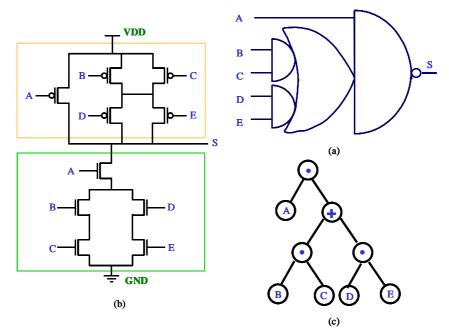

| FIGURE 6.12 - Example of SCCG: logic-level symbol (a), transistor schematics (b) and function tree (c)                                                                   |

| FIGURE 6.13 - Using the three-valued timed calculus for evaluating a SCCG                                                                                                |

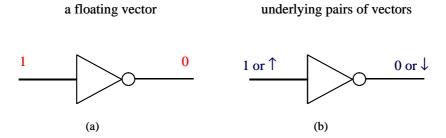

| FIGURE 6.14 - The relationship between floating mode (a) and transition mode (b)                                                                                         |

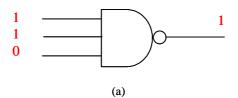

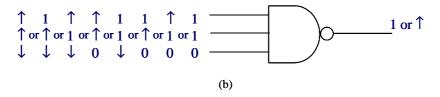

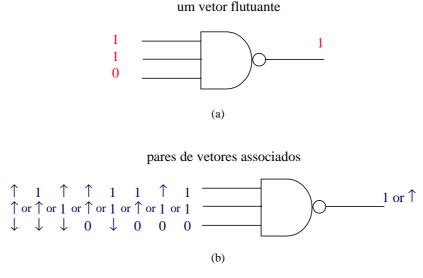

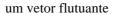

| FIGURE 6.15 - The relationship between floating mode and transition mode: a floating vector applied to a 3-input NAND gate (a) and the 8 underlying pairs of vectors (b) |

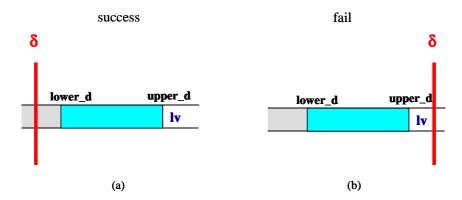

| FIGURE 6.16 - Success (a) and fail (b) conditions for the timed-test generation procedure                                                                                |

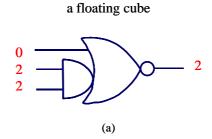

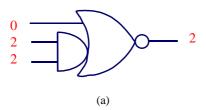

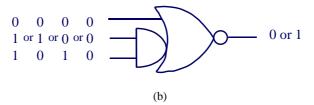

| FIGURE 6.17 - Delay of a SCCG under a floating cube                                                                                                                      |

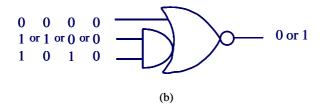

| FIGURE 6.18 - Backward implication in a SCCG by using forward implication rules                                                                                          |

# **List of Tables**

| TABLE 3.1 – Main properties of the Boolean algebra                                        | 39  |

|-------------------------------------------------------------------------------------------|-----|

| TABLE 3.2 - Truth-table for the 5-valued AND operation.                                   | 45  |

| TABLE 3.3 - Truth-table for the 5-valued OR operation.                                    | 45  |

| TABLE 5.1 - Classification of existing FTA algorithms.                                    | 69  |

| TABLE 5.2 - Timed calculus with unknown values.                                           | 80  |

| TABLE 5.3 - Truth table for the AND function in ternary algebra.                          | 86  |

| TABLE 5.4 - Truth table for the OR function in ternary algebra                            | 86  |

| TABLE 6.1 - Number of elements for various virtual libraries [DET87]                      | 99  |

| TABLE 6.2 - Three-valued timed calculus for a 2-input AND gate                            | 105 |

| TABLE 6.3 - Three-valued timed calculus for a 2-input OR gate                             | 105 |

| TABLE 6.4 - Generalized three-valued timed calculus for <i>n</i> -input simple gates      | 106 |

| TABLE 6.5 - Three-valued timed calculus for evaluating SCCGs                              | 108 |

| TABLE 6.6 - Relationship between floating model vectors and transition model vectors      | 112 |

| TABLE 6.7 - Equivalence between floating and transition modes for the SCCG of figure 6.17 | 115 |

## **Abstract**

The recent advances in CMOS technology have allowed for the fabrication of transistors with submicronic dimensions, making possible the integration of tens of millions devices in a single chip that can be used to build very complex electronic systems. Such increase in complexity of designs has originated a need for more efficient verification tools that could incorporate more appropriate physical and computational models.

Timing verification targets at determining whether the timing constraints imposed to the design may be satisfied or not. It can be performed by using circuit simulation or by timing analysis. Although simulation tends to furnish the most accurate estimates, it presents the drawback of being stimuli dependent. Hence, in order to ensure that the critical situation is taken into account, one must exercise all possible input patterns. Obviously, this is not possible to accomplish due to the high complexity of current designs. To circumvent this problem, designers must rely on timing analysis. Timing analysis is an input-independent verification approach that models each combinational block of a circuit as a direct acyclic graph, which is used to estimate the critical delay.

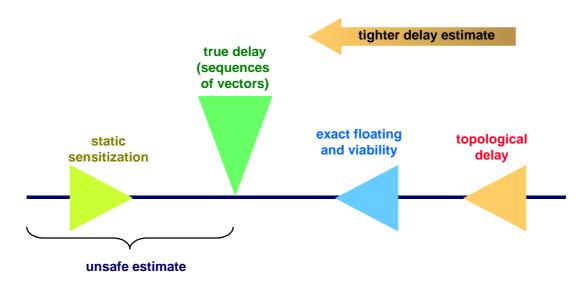

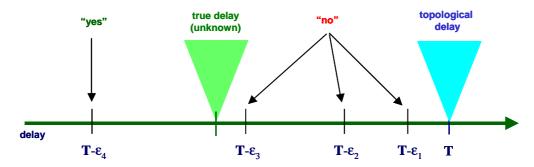

First timing analysis tools used only the circuit topology information to estimate circuit delay, thus being referred to as topological timing analyzers. However, such method may result in too pessimistic delay estimates, since the longest paths in the graph may not be able to propagate a transition, that is, may be false. Functional timing analysis, in turn, considers not only circuit topology, but also the temporal and functional relations between circuit elements.

Functional timing analysis tools may differ by three aspects: the set of sensitization conditions necessary to declare a path as sensitizable (i.e., the so-called path sensitization criterion), the number of paths simultaneously handled and the method used to determine whether sensitization conditions are satisfiable or not. Currently, the two most efficient approaches test the sensitizability of entire sets of paths at a time: one is based on automatic test pattern generation (ATPG) techniques and the other translates the timing analysis problem into a satisfiability (SAT) problem.

Although timing analysis has been exhaustively studied in the last fifteen years, some specific topics have not received the required attention yet. One such topic is the applicability of functional timing analysis to circuits containing complex gates. This is the basic concern of this thesis. In addition, and as a necessary step to settle the scenario, a detailed and systematic study on functional timing analysis is also presented.

**Keywords:** design verification of VLSI circuits, timing analysis, functional timing analysis (FTA), path sensitization problem, critical delay estimation, complex gates, automatic test pattern generation (ATPG), satisfiability (SAT).

**TITLE**: "ANÁLISE DE *TIMING* FUNCIONAL DE CIRCUITOS VLSI CONTENDO PORTAS COMPLEXAS."

#### Resumo

Os recentes avanços experimentados pela tecnologia CMOS tem permitido a fabricação de transistores em dimensões submicrônicas, possibilitando a integração de dezenas de milhões de dispositivos numa única pastilha de silício, os quais podem ser usados na implementação de sistemas eletrônicos muito complexos. Este grande aumento na complexidade dos projetos fez surgir uma demanda por ferramentas de verificação eficientes e sobretudo que incorporassem modelos físicos e computacionais mais adequados.

A verificação de *timing* objetiva determinar se as restrições temporais impostas ao projeto podem ou não ser satisfeitas quando de sua fabricação. Ela pode ser levada a cabo por meio de simulação ou por análise de *timing*. Apesar da simulação oferecer estimativas mais precisas, ela apresenta a desvantagem de ser dependente de estímulos. Assim, para se assegurar que a situação crítica é considerada, é necessário simularem-se todas as possibilidades de padrões de entrada. Obviamente, isto não é factível para os projetos atuais, dada a alta complexidade que os mesmos apresentam. Para contornar este problema, os projetistas devem lançar mão da análise de *timing*. A análise de *timing* é uma abordagem independente de vetor de entrada que modela cada bloco combinacional do circuito como um grafo acíclico direto, o qual é utilizado para estimar o atraso do circuito.

As primeiras ferramentas de análise de *timing* utilizavam apenas a topologia do circuito para estimar o atraso, sendo assim referenciadas como analisadores de *timing* topológicos. Entretanto, tal aproximação pode resultar em estimativas demasiadamente pessimistas, uma vez que os caminhos mais longos do grafo podem não ser capazes de propagar transições, i.e., podem ser falsos. A análise de *timing* funcional, por sua vez, considera não apenas a topologia do circuito, mas também as relações temporais e funcionais entre seus elementos.

As ferramentas de análise de *timing* funcional podem diferir por três aspectos: o conjunto de condições necessárias para se declarar um caminho como sensibilizável (i.e., o chamado critério de sensibilização), o número de caminhos simultaneamente tratados e o método usado para determinar se as condições de sensibilização são solúveis ou não. Atualmente, as duas classes de soluções mais eficientes testam simultaneamente a sensibilização de conjuntos inteiros de caminhos: uma baseia-se em técnicas de geração automática de padrões de teste (ATPG) enquanto que a outra transforma o problema de análise de *timing* em um problema de solvabilidade (SAT).

Apesar da análise de *timing* ter sido exaustivamente estudada nos últimos quinze anos, alguns tópicos específicos não têm recebido a devida atenção. Um tal tópico é a aplicabilidade dos algoritmos de análise de *timing* funcional para circuitos contendo portas complexas. Este constitui o objeto básico desta tese de doutorado. Além deste objetivo, e como condição *sine qua non* para o desenvolvimento do trabalho, é apresentado um estudo sistemático e detalhado sobre análise de *timing* funcional.

**Palavras-chave:** verificação de projeto de circuitos VLSI, análise de *timing*, análise de *timing* funcional (FTA), sensibilização de caminhos, estimativa do atraso crítico, portas complexas, geração automática de padrões de teste (ATPG), solvabilidade (SAT).

### 1 Introduction

The remarkable advances achieved by CMOS fabrication technology in the last three decades have made possible the amazing expansion that consumer electronics market has been going through. Thanks to the continuously increasing transistor integration density offered by CMOS technology, ever more complex systems can be integrated on a single chip, allowing more sophisticated electronic equipment to be available at relatively low prices.

Obviously, higher transistor densities are obtained by reducing the dimensions of onchip components. To a first approximation, reducing transistor and wiring dimensions would lead us to believe that higher clock frequencies could easily be achieved, since smaller transistors switch faster. Indeed, this used to be a well-established law for a long time. However, since CMOS technology has allowed for submicronic devices, some up till then ignored side effects have grown in importance, resulting in new phenomena that partially invalidate the previously mentioned law. One of such phenomena, probably the most cited in recent years, is the dominance of wiring delays over gate delays, as a consequence of the increase in RC factor of interconnections.

Since the 80's the increasing complexity of electronic systems has made mandatory the use of automatic synthesis tools. Electronic design automation (EDA) tools covering all steps of circuit design, from the behavioral to the physical level, were developed. Such tools incorporated efficient algorithms, able to treat systems with hundreds of thousand gates. However, by the time submicronic technologies began to be used, the models used by these tools for estimating performance were revealed completely wrong. Since then, a lot of effort has been concentrated on developing more accurate circuit models, able to account for the side effects resulting from submicronic technologies.

Among the available EDA tools, those devoted to design verification are currently playing a key role. Since it is not practical to directly prototype the circuit in order to test it on its working environment, designers must rely on verification tools to certify, before fabrication, that the circuit will operate properly. Besides certifying proper operation, one may also desire to explore the target technology in all its extension, looking for achieving the maximal performance. Hence, we can conclude that verification tools must offer a minimum of reliability.

**Timing verification** targets at determining whether the timing constraints imposed to the design may be satisfied or not. More strictly, timing verification is concerned with estimating the **critical delay** of circuits and the **maximal operating frequency**, in case of clocked circuits.

As any other type of verification, the accuracy of timing verification is completely dependent on the accuracy of the adopted circuit models. By circuit models it is meant not only the physical delay model used to quantify the delay of each component, but also the models for computing circuit component delay and the circuit delay itself. Such models are strongly dependent on the circuit operation model, that is, whether the circuit is assumed to operate in a synchronous or in an asynchronous manner.

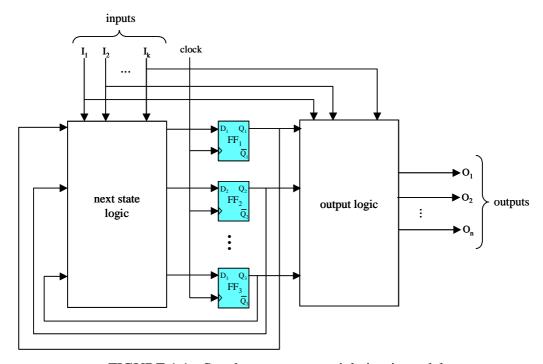

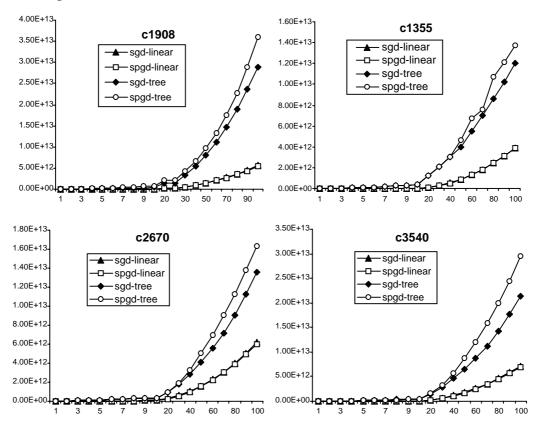

Many of the existing timing verification techniques target at synchronous sequential circuits. Thus, let us consider the issues arriving while estimating the maximal operating frequency of a sequential circuit that may be represented as a Mealy finite state machine (FSM). The Mealy FSM model, depicted by figure 1.1, divides the combinational part into

two distinct blocks: the next state logic and the output logic [GAJ99]. The next state logic computes the next state variables while the output logic is responsible for the output signals. If memory elements are edge-triggered flip-flops, then at each active clock edge the next state is loaded into the flip-flops, becoming the current state. At that time, the next state begins to be computed by the next state logic. Outputs may change as a consequence of a change in current state (stored in the flip-flops) or as a consequence of a change at the inputs or even both.

FIGURE 1.1 - Synchronous sequential circuit model.

Consider that the next state logic has maximum and minimum propagation delays  $T_{next}$  and  $t_{next}$ , respectively, while the output logic has maximum and minimum propagation delays  $T_{out}$  and  $t_{out}$ , respectively. Consider also that the edge-triggered flip-flops present maximum propagation delay  $T_{ff}$ , setup time  $t_s$  and hold time  $t_h$ . Then, in order to assure correct circuit operation, the following conditions must be observed:

- $\tau > \max\{ (T_{ff} + T_{next} + t_s), (T_{ff} + T_{out}) \}$ , where  $\tau$  is the clock period

- $t_{\text{next}} > t_{\text{h}}$

- circuit's inputs must be stable and valid for a period greater than  $T_{next} + t_s$  before each active clock edge.

The derived conditions above are quite conservative but allow for a safe synchronous operation. The first condition assures that clock period is long enough to accommodate the worst case delay within the next state loop ( $T_{ff} + T_{next} + t_s$ ) and the worst case delay for the output logic ( $T_{ff} + T_{out}$ ). The second condition avoids excessively short clock periods that could prevent flip-flops from sampling valid new states. The third condition assures that the input signals to the next state logic are computed in time, such that all outputs of this block are stable and valid for an amount of time equal or greater than  $t_s$  before the next clock edge.

In fact, the third condition may be disregarded if extra flip-flops are used to synchronize the inputs. Moreover, the first condition is conservative enough to allow the outputs to be sampled using the same clock phase applied to state flip-flops. In case a different phase is available, this condition could be loosen to  $\tau > \max\{\ (T_{ff} + T_{next} + t_s)\ ,\ T_{out}\ \}$ .

21

Let us go a little bit further on evaluating how circuit operation model may affect the procedure for estimating the clock frequency. Consider that the already discussed circuit operation model is to be adopted and assume that inputs are synchronized by flip-flops that are controlled by the same clock applied to the state flip-flops. If the variation in propagation delays of flip-flops is not significant, one may assume that each combinational block operates in a completely synchronous manner, in that propagation delay is a consequence of two consecutive input vectors. However, if the propagation delays of flip-flops vary significantly, combinational blocks operate in an asynchronous manner, as fast sequences of input vectors were applied to the circuit before its outputs settle to their final values.

Another important issue is the critical delay estimation of combinational blocks, which is a complex task *per se*. The most conservative approach relies on using the topological delay, that is, the delay of the longest path in the circuit. However, more accurate techniques test whether the longest path or paths are able to propagate transitions<sup>1</sup>.

The considerations stated in the last two paragraphs are very important for developing timing verification tools that are stimuli-independent or use simplified component models, such as switch level simulators. However, in case of detailed circuit simulation, the circuit operation model is implicitly considered in the context of circuit-level detailed models, such as differential equations or signal waveforms.

Electrical simulation is the most accurate method for verifying the timing requirements of CMOS circuits. Detailed electric level simulators such as Spice [NAG75] represent the circuit as a network of passive and active elements (resistors, capacitors, inductors and controlled sources) and solve the related system of ordinary linear differential equations for each time step of the simulation run. Unfortunately, electric level simulation demands huge execution times even for moderately small circuits. To speedup electrical simulation relaxation methods have been proposed and used (equation relaxation in ELOGIC [KIM86] and waveform relaxation in RELAX [LEL82], for instance). Even though, electrical simulation cannot be used solely for determining time performance of state-of-the-art digital designs.

An alternative to electrical simulation is **timing simulation**. Timing simulation is accomplished by simplified electric level simulators, such as XPSIM [BAU88], or enhanced switch level simulators, such as Motis [CHA75], TV [JOU87] and Crystal [OUS85]. Timing simulation is faster than electrical simulation because it uses less accurate models. In case of Crystal and TV, for instance, effective resistances are used to model transistors. On the other hand, results are less accurate than those obtained through electrical simulation.

There are three serious difficulties in using the simulation approach (electrical or timing simulation) for verifying the timing requirements of circuits. The first is the execution time to accomplish all necessary computations, which was already discussed. A second problem is the effort required for preparing a set of input patterns, since the simulation approach is stimuli driven. Third one, and maybe the most stringent, is ensuring that the set of patterns exercises the critical situation that determines the circuit's critical delay. This constitutes a problem due to the high complexity of current digital designs. For instance, a combinational network with n inputs exhibits  $2^n$  possible input vectors. Even for medium combinational blocks, where n is of the order 100, exhaustive circuit simulation would not be possible. Hence, determining a minimum set of vectors that guarantees to find the circuit delay is not trivial.

-

<sup>&</sup>lt;sup>1</sup> This is known as **the critical path problem**, which is discussed along the next chapters of this thesis.

22

Due to these difficulties, the input-independent approach has replaced simulation for estimating the critical delay of VLSI circuits. This approach, known as **timing analysis**<sup>2</sup>, represents each combinational block of the circuit as a weighted direct acyclic graph (DAG), where nodes represent gates and edges represent connections. The weights of nodes and edges represent the delays of gates and connections, respectively. The critical delay of each combinational block is determined by analyzing the length of the paths in the graph.

The most naïve solution relies on disregarding logic behavior of gates and assuming the delay of the longest path as the critical delay of the combinational block. Hence, the critical delay problem of a combinational block is reduced to finding its longest path, which can be solved in linear time by the well-known topological sort algorithm [COR90]. Such approach, referred to as **static** or **topological timing analysis** (TTA), was probably born with the IBM PERT Project [KIR66] and was used by other timing analyzers such as [HIT82].

However, there may not exist any input pattern that exercises the longest path in the circuit, or equivalently, it may never transmit any signal transition. In this case, the critical delay may be smaller than the delay of the topologically longest path. Paths that never transmit a signal transition are called **false paths** [HRA78] (or **unsensitizable paths**). A circuit may contain many false paths. In order to improve the accuracy of delay estimates, timing analysis tools must take path sensitizability into account. Unfortunately, performing false path-aware timing analysis constitutes a NP-complete problem and thus, many assumptions must be done in order to obtain safe critical delay estimates.

Although some work has been done for allowing automatic generation of false path-free circuits (e.g., [KEU91][SAL94][KUK97a][PRA00]), most of available high-level synthesis systems may generate circuits with false paths [BER91].

In late years a lot of research has focused on developing efficient timing analysis algorithms that consider the path sensitization problem. But as long as CMOS technology evolves very fast and higher clock rates are continuously being demanded, improving the accuracy of critical delay estimation is still an issue of relevant importance in design verification.

Furthermore, some specific topics have not received sufficient attention yet. One such topic is the applicability of **functional timing analysis** (FTA), i.e., false path-aware timing analysis, to circuits containing complex gates. Some works on logic synthesis have reported the possibility of area reduction and performance improvements when static CMOS complex gates (SCCGs) are used [REI98][RIE96]. However, timing analysis of circuits containing complex gates is rarely mentioned in the literature. Indeed, only some of the existing algorithms can handle such circuits. The study of functional timing analysis applied to circuits containing complex gates is the main concern of this thesis.

#### 1.1 Thesis Organization

This thesis is organized as follows. Chapter 2 reviews the basic issues of the timing analysis approach. Topological timing analysis is discussed in detail and the reason why it may furnish too pessimistic estimates is addressed. Functional timing analysis is then introduced. The component delay models and the circuit delay computation models underlying FTA tools are presented. The basic properties to assure that FTA furnishes safe critical delay estimates are also presented.

<sup>&</sup>lt;sup>2</sup> In this thesis, the term **timing verification** is used to refer to any method that can verify timing requirements of circuits. However, the term **timing analysis** will only be used for input-independent timing verification methods.

Chapter 3 presents a comprehensive collection of definitions that are necessary to understand the theory behind FTA and the related algorithms.

Chapter 4 is devoted to the path sensitization problem. The three most important sensitization criteria, the static sensitization, viability and the exact floating sensitization are presented.

The main issues that are considered in the development of a FTA tool are presented and classified in chapter 5. This includes the adopted sensitization conditions and the method used to determine whether the sensitization conditions are satisfiable. This chapter also discusses some of the most important existing algorithms.

Chapter 6 justifies the use of CMOS complex gates in the design of VLSI circuits. It also discusses the limitations of existing timing analysis methods for estimating the delay of circuits containing such type of gates. A new solution for performing functional timing analysis of circuits containing complex gates is then proposed. This solution relies on extending the three-valued timed calculus used within the timed-test generation procedure of Devadas et al. [DEV93a] in order to handle complex gates in a friendly manner (i.e., without using macro-expansion). The advantages and disadvantages of the proposed solution are discussed.

Finally, some concluding remarks are offered.

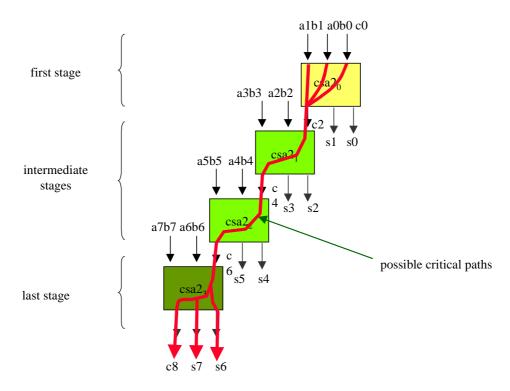

The appendices bring extra information on specific topics. Appendix 1 justifies the importance of taking into account false paths by studying false paths in carry-skip adders. Appendix 2 presents an informal evaluation of the time complexity of the best-first algorithm, used by path enumeration-based FTA tools. Appendix 3 is an extended abstract of the thesis in portuguese.

This thesis may also be used as a quick introduction to the basic concepts on timing analysis and timing models used within high level and logic level synthesis algorithms. Chapters 1 and 2 introduce most of the necessary concepts without using any formalism. For those interested in going further, the definitions presented in chapter 3 are essential, though.

25

# 2 The Timing Analysis Approach

During the 80's, as design complexity augmented quickly, the verification of timing requirements of circuits through simulation became impractical due to the increasing execution time demanded and also to the difficulty in determining a safe set of input vectors that proven to exercise the critical delay situation. Then, the attention was turned to stimuli-independent verification methods, in opposition to simulation methods.

But even before, more precisely in 1966, Kirkpatrick and Clark [KIR66] proposed the use of the management method called PERT (Program Evaluation Review Technique) to estimate the critical delay of circuits. In their work, a combinational block was represented as a weighted direct acyclic graph (DAG), with the nodes representing circuit gates and the edges representing circuit connections. The longest path in the DAG was discovered by using the topological sort algorithm [COR90] and its delay was assumed to be the critical delay of the block.

The idea of using PERT to estimate critical delay of combinational circuits was retaken by Hitchcock in the development of its "Timing Analyzer" program [HIT82], which also came up with the innovative concept of signal time slacks. Also the expression **timing analysis**, currently used by EDA community to designate any input-independent timing verification tool, seems to be borrowed from Hitchcock's work.

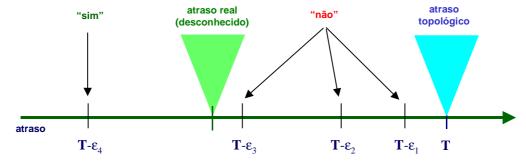

However, there may not exist any input pattern<sup>3</sup> that exercises the longest path in the circuit, in the sense that no signal transition (or event) can propagate along it. Since PERT-based timing analysis disregards the logic behavior at circuit's nodes, it may furnish a needless pessimistic critical delay estimate. In addition, the fact that PERT-based timing analysis considers only circuit topology has motivated some authors to call it **topological timing analysis** (TTA) (e.g., [DEV94]).

Paths that never transmit any signal transition are called **false paths** [HRA78]. (Some authors also use the term **unsensitizable paths**.) A circuit may contain many false paths. The problem of determining whether a path may be exercised or not is referred to as **the path sensitization problem** or as **the (general) false path problem** [DU89]. According to [MCG89], although false paths were known for some time, the first complete discussion on this topic was due to Hrapcenko, who designed a parametric circuit to show that for some circuits the true delay could differ from the topological critical delay [HRA78].

Early timing analysis tools took into account false paths by allowing **case analysis**. The Timing Analysis program (TA) from Hitchcock [HIT82], for instance, had a facility called delay modifiers that could be used to indicate paths that, in the designer's opinion, would never be activated. However, as long as manual detection of all false paths in complex circuits is impossible, since early it became clear that automatic false path detection should be pursued. The first attempts for including automatic false path detection was the work of Brand and Iyngar [BRA88] and that of Benkoski et al. [BEN87]. Since then, most of research in timing analysis has concentrated on this issue, looking for algorithms that could lead to accurate delay estimates in a reasonable amount of time. More recently, timing analysis

<sup>&</sup>lt;sup>3</sup> The majority of existing timing analysis techniques do not consider explicitly all possible input patterns. Actually, the definition of which patterns are allowed depends on how inputs are assumed to be made of, what is taken into account by the adopted circuit delay computation model (see section 2.3).

techniques that consider false paths have been termed **functional timing analysis** (FTA) [ASH95][KUK97]. Such terminology is also adopted in this text.

This chapter is concerned with the basic aspects underlying the timing analysis approach, with special attention to the models used in FTA. Section 2.1 describes how the topological sort algorithm is adapted to perform TTA. In section 2.2 the false path problem is introduced by means of two circuit examples. Section 2.3 discusses delay computation models in the context of FTA, showing that circuit delay computation depends on the type of inputs considered. It also associates the possible types of inputs to circuit operation models and to the so-called modes of operation. Section 2.4 summarizes the most relevant physical component delay models, while section 2.5 presents the gate delay computation models commonly used in FTA tools. Section 2.6 discusses the correctness and robustness properties of timing analysis algorithms. Such properties allow us to evaluate whether a given FTA technique is able to furnish safe delay estimates or not and in affirmative case, how accurate such estimates are. Finally, section 2.7 gives an overview on the spectrum of model possibilities while implementing a FTA tool.

#### 2.1 Topological Timing Analysis

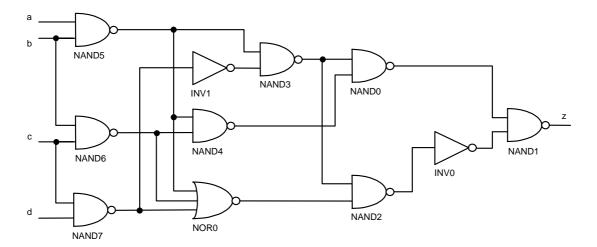

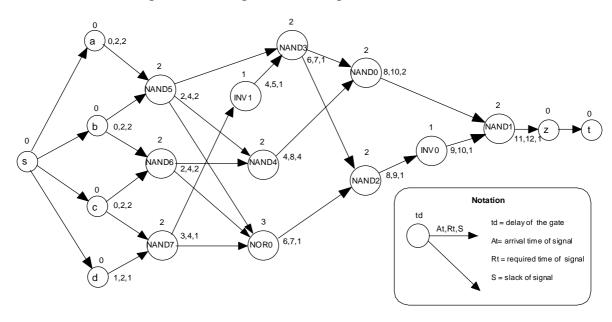

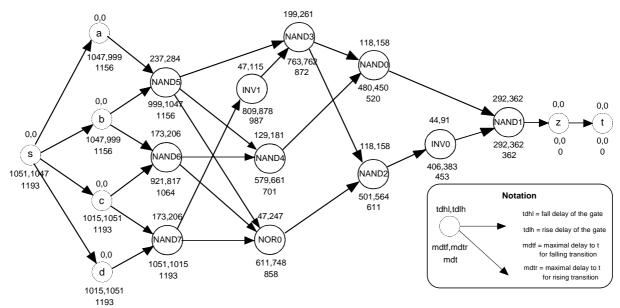

Any timing analysis technique represents each combinational block as a weighted DAG. In this DAG nodes are associated with gates and edges are associated with connections (sometimes, nets). The delay of each gate (connection) may be stored at the respective node (edge). Another possibility is to concentrate (or lump) at each node (or edge) the sum of the delays of the gate and its output connections. This choice depends on the data structure used to store DAG information and on the accuracy of physical models used to estimate component (gates and connections) delays. Dummy nodes, i.e., nodes with zero delay, represent primary inputs and primary outputs. Frequently, *source* and *terminal* (dummy) nodes are added to the DAG to transform it into a canonical DAG. This may help the development of graph traversal functions that operate both forward and backwards. In a canonical DAG representation, any **complete path** assumes the form ( $\mathbf{s}$ ,  $e_{\mathbf{s}}$ ,  $v_0$ ,  $e_0$ ,  $v_1$ ,  $e_1$ , ...,  $v_n$ ,  $e_n$ ,  $v_{n+1}$ ,  $e_t$ ,  $\mathbf{t}$ ), where  $v_0$  and  $v_{n+1}$  represent the primary input and the primary output, respectively,  $\mathbf{s}$  and  $\mathbf{t}$  are the source and terminal nodes and  $e_{\mathbf{s}}$  and  $e_{\mathbf{t}}$  are dummy edges. Figure 2.2 shows a DAG representation for the circuit of figure 2.1.

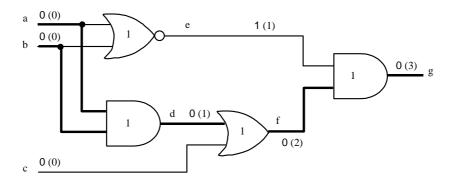

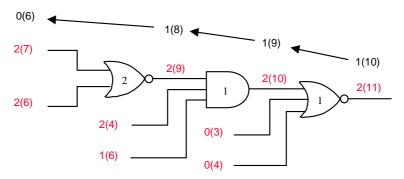

FIGURE 2.1 - Combinational circuit example.

Topological timing analysis finds the longest path in the DAG, which corresponds to the path with greatest delay, and assumes it as responsible for the critical delay of the circuit. This is accomplished by using the topological sort algorithm [COR90], which is known to execute in linear time with respect to the graph size. It also may compute the time slack of signals, which can be used in a performance optimization step.

FIGURE 2.2 - Processed DAG for the circuit example of figure 2.1.

Let us illustrate the topological timing analysis procedure on the circuit of figure 2.1. (DAG of figure 2.2 holds the timing information gathered from such procedure.) For the current example, assume that graph edges represent circuit nets (instead of connections). Assume also that the delay of the gates and their output nets are lumped at graph nodes. For any circuit signal e a 3-tuple of timing values is calculated and annotated at the related graph edge: the **arrival time** of e, At(e) which is the time that the signal at edge e settles to its final (steady state) value, the **required time** of e, Rt(e), which is the time at which the signal at e is required to be stable and the **slack** S(e), calculated as the difference between the required time and the arrival time (Rt(e)-At(e)). The arrival times of the primary inputs and the required times of the primary outputs are set by the timing constraints for the block under analysis. Non-zero arrival times for the primary inputs may be necessary in case of hierarchical analysis. The topological analysis begins by computing the arrival times for each signal in a forward manner, beginning from the primary inputs. The arrival time of a signal e, which is the output of node v, is calculated by:

$$At(e) = \max_{i} \left\{ At(e_i) \right\} + d(v)$$

(2.1)

where d(v) is the delay of the gate represented by v and  $e_i$  is the set of input signals to v. Once the arrival times of all primary outputs are calculated (or alternatively, node t is reached), the procedure performs a backward step for calculating the required times of signals, using the required times of primary outputs. The required time of a signal e is calculated by:

$$Rt(e) = min|_{i} \{Rt(e_{i}) - d(v_{i})\}$$

(2.2)

where  $v_j$  represents the gates that have e as fanin and  $e_j$  are the output edges (nets) of such gates. Having calculated the required time of a signal, its slack can also be computed.

Sometimes this computation of arrival times, required times and slacks is called **delay trace** through the network [DEV94].

Once the graph has been completely processed, the **topologically longest path** or **topological critical path** is the path where each signal has the minimum slack and can be easily traced. In this example the topological critical path is (**s**, d, NAND7, NOR0, NAND2, INV0, NAND1, z, **t**), with delay 11 and slack 1. The slack is also a measure of the criticality of paths and may be used for identifying gates for resizing and/or buffer insertion points in case of a delay optimization procedure [JU91][JOU87][CHE93a].

Although topological timing analysis may overestimate the critical delay of circuits, it surely is an upper bound on the critical delay of a combinational circuit. Indeed, most of existing high-level and architectural-level synthesis tools still use it as a fast means of verifying the timing requirements of designs, since at these levels there is an implicit lack of accuracy in physical delay models of components. However, as operating frequency of VLSI designs enters the gigahertz range, more accurate delay estimates are demanded. Hence, considering path sensitizability is mandatory. In the next section the false path problem is introduced by means of two circuit examples.

#### 2.2 False Paths

Currently, timing, power, area and testability are the criteria used to guide design optimization during synthesis. Unfortunately, most of optimization procedures introduce redundancies into designs [KEU91], which constitute one known source of false paths.

If input vector *v* does not activate a path P, then P is said not to be sensitizable by *v*. If P is not sensitizable by any input vector, then P is said to be false.

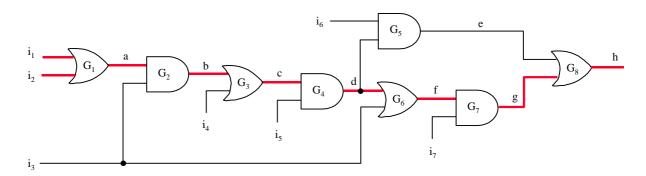

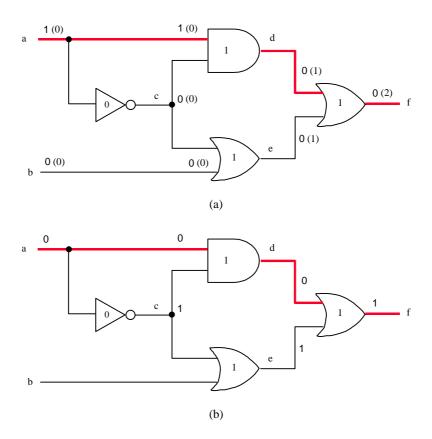

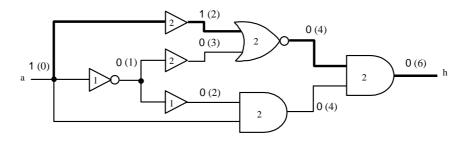

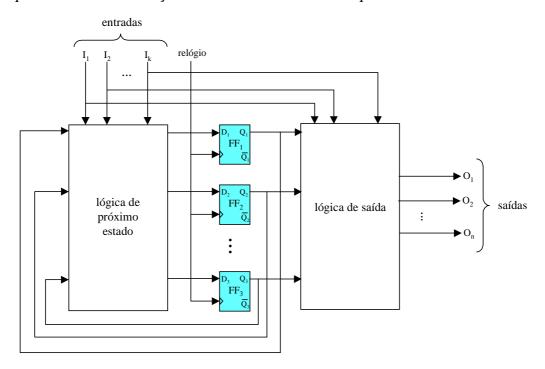

Consider Hrapcenko's circuit [HRA78] shown in figure 2.3. Assume that all gates have delay equal 1 and wires have zero delay. Its topologically longest paths are  $P_1$ =( $i_1$ ,  $G_1$ ,  $G_2$ ,  $G_3$ ,  $G_4$ ,  $G_6$ ,  $G_7$ ,  $G_8$ , h) and  $P_2$ =( $i_2$ ,  $G_1$ ,  $G_2$ ,  $G_3$ ,  $G_4$ ,  $G_6$ ,  $G_7$ ,  $G_8$ , h), both with delay 7. However, while  $i_3$ =0, no signal transition can propagate from a to b. Similarly, while  $i_3$ =1, no signal transition can propagate from d to f. As long as a signal cannot assume two logic values at the same time, the only possibility to sensitize  $P_1$  and  $P_2$  is allowing a sequence of vectors to be applied at circuit's inputs such that  $i_3$ =1 at time 1 and  $i_3$ =0 at time 4. However, if only pairs of vectors are allowed, then the previous case is not possible. Then, paths  $P_1$  and  $P_2$  are false and the circuit delay is less than 7.

FIGURE 2.3 - First example of false path: Hrapcenko's circuit.

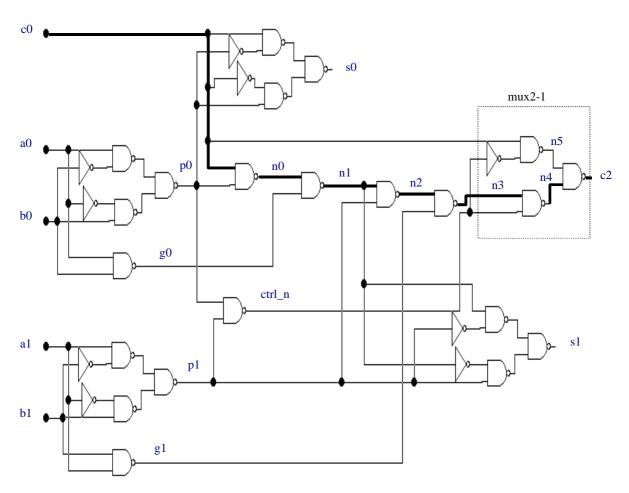

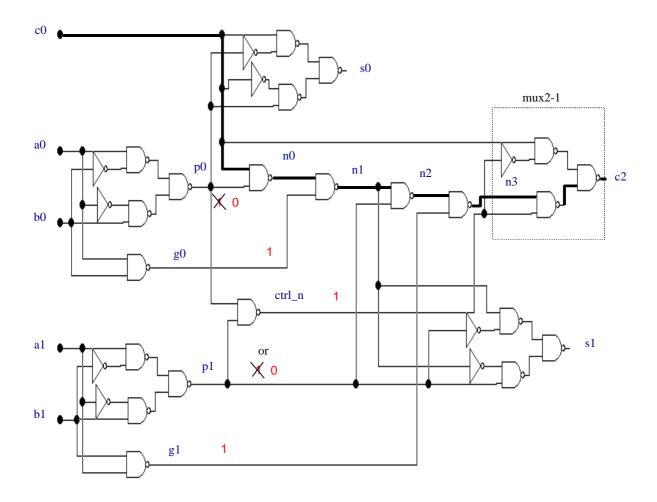

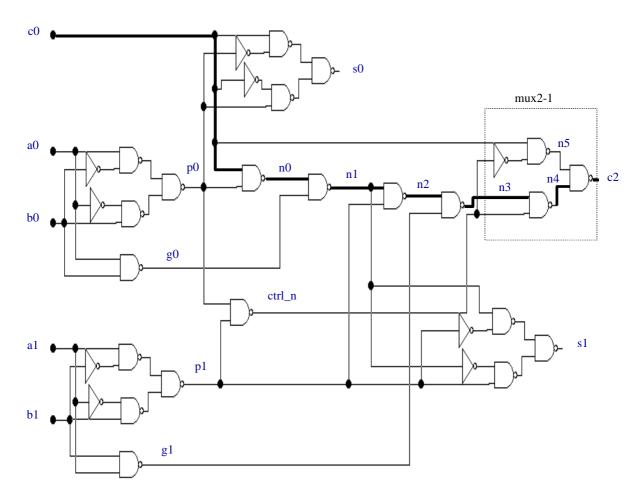

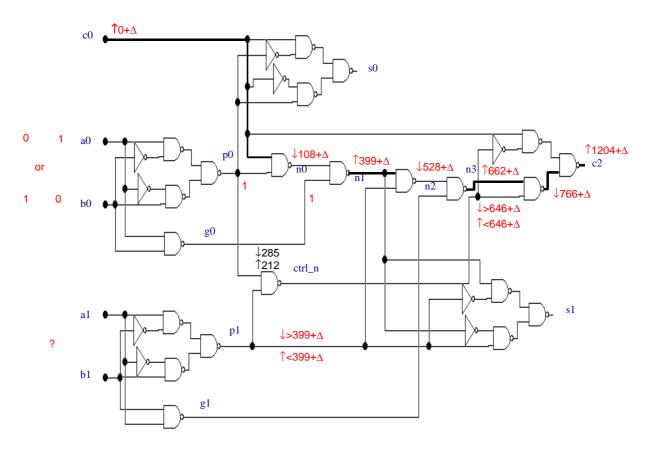

Some classes of circuits are designed to purposely make the topologically longest paths false, as a strategy for reducing its critical delay. One such a class is composed of carry-skip adders [KEU91][DEV94][LAM94]. Figure 2.4 shows a 2-bit carry skip adder (csa2). Higher order adders may be obtained by connecting together csa2s through the carry chain. In this case the topologically longest path will include the carry chain, which in a single csa2 as the one showed by figure 2.4 corresponds to path P=(c0, n0, n1, n2, n3, n4, c2), in bold. Thus, to determine the critical delay of a higher order csa adder, one must begin by analyzing the sensitizability of such path.

Suppose all gates of the csa2 of figure 2.4 have unit delay and wires have zero delay. Assuming only pairs of vectors at the circuit's inputs, in order to sensitize path P, p0, g0, p1, g1, ctrl\_n and n5 must be 1 at times 0, 1, 2, 3, 4 and 5, respectively. However, if p0, g0, p1 and g1 are made fixed at 1, ctrl\_n will be fixed at 0 and no transition will reach n4. On the other hand, no input pair of vectors satisfies p0=1 at time 0, p1=1 at time 2 and ctrl\_n=1 at time 4. Thus, path P is false.

Moreover, late transitions at c0 (i.e., transitions arriving after time t=0) do not change the sensitizability of path P. This means that in any higher order adder made up from this csa2 the topologically longest path is false. Appendix 1 presents a detailed *ad hoc* analysis of csas, using fixed non-unit delay and assuming different fall and rise gate delays.

FIGURE 2.4 - Second example of false path: a 2-bit carry-skip adder.

#### 2.3 Functional Timing Analysis and Circuit Delay Computation Models

As mentioned in chapter 1, the accuracy of any timing verification tool is completely dependent on the accuracy of the adopted circuit models. Furthermore, in the specific case of timing analysis tools, some assumptions on circuit operation are also required to improve critical delay estimation, what will become clear in the following paragraphs.

The topological timing analysis procedure presented in section 2.1 may lead to significant overestimation of critical delay because it ignores the logical behavior of circuit gates. Considering different fall and rise gate delays in that procedure is easily accomplished and may result in significant improvement of the estimation accuracy [GÜN98][GÜN98a]. In a certain manner, the use of different fall and rise gate delays may be seen as a very crude model for circuit operation, which, however, does not take false paths into account.

Due to the false path phenomenon, the critical delay of a circuit may be less than the delay of its topologically longest path. The difference between the topological delay and the actual critical delay cannot be neglected in the context of an automated design process since the designer does not have total control on the resulting generated structure. Further, even for some hand-made designs the delay estimated by a topological analysis may be too pessimistic and more accurate estimations would be highly desirable. (That is the case of carry-skip adders [KEU91][LAM94][DEV94] and some multipliers.)

In order to take false paths into account, it is necessary to revise the concept of critical delay of a (combinational) circuit. A path-based definition would state that "the **critical delay** of a circuit is the delay (or length) of its longest sensitizable path", also mentioning that "there may exist more than one critical path" [CHE93]. Although correct, this definition is quite limited since not all of the false path-aware timing analysis algorithms work on a per-path basis.

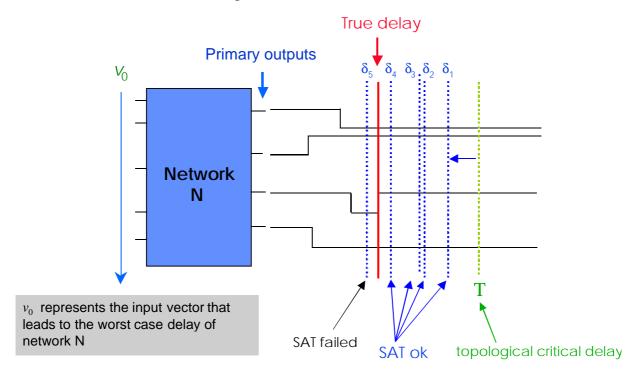

A more general definition can be found by examining the circuit operation model and realizing that the essence of timing analysis should be the capture of the exact instant at which the slowest circuit output(s) settle to its (their) steady-state value(s). Of course, one possible solution relies on testing the sensitizability of each circuit path, beginning by the longest one. However, this is not the only possible solution. Indeed, state-of-art timing analysis techniques (or algorithms) operate on sets of paths at a time, what generally results in less computation time. Timing analysis algorithms that considers false paths fall into the **functional timing analysis** (FTA) category, and will be discussed in chapter 5.

Having posed the FTA problem from a new point of view, it is possible to redefine the delay of a circuit. The **delay of a circuit** under a given input pattern is the minimum amount of time after which all of its outputs are settled to their steady-state values. By extension, the circuit's **critical delay** corresponds to its greatest delay, considering all possible input patterns. For the sake of simplicity, we may refer to the critical delay of a circuit just as **delay of the circuit** (or **circuit delay**), since this is the parameter of interest in this thesis.

Note that the previously stated definitions implicitly consider path sensitizability. However, what exactly constitutes an input pattern is not clear. This point was intentionally left open in order to make the definition of critical delay independent of the circuit operation model. In reality, the definition of what constitutes a valid input pattern depends on how the circuit is assumed to operate and will be considered within the **circuit delay computation model**.

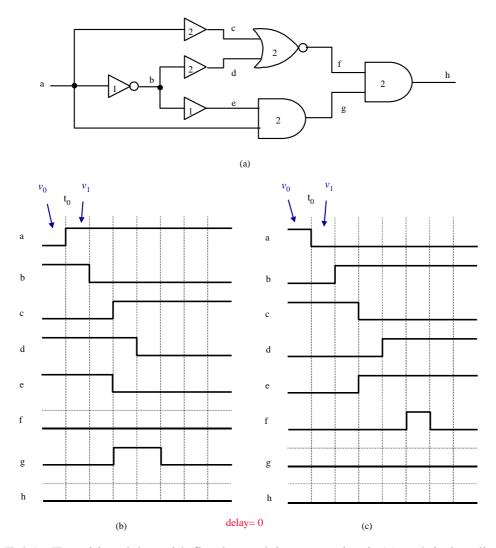

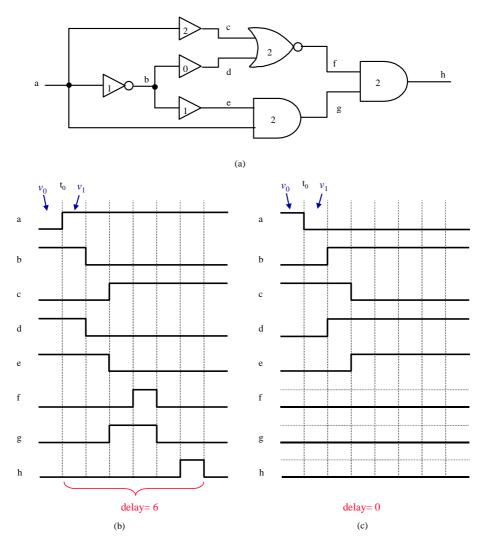

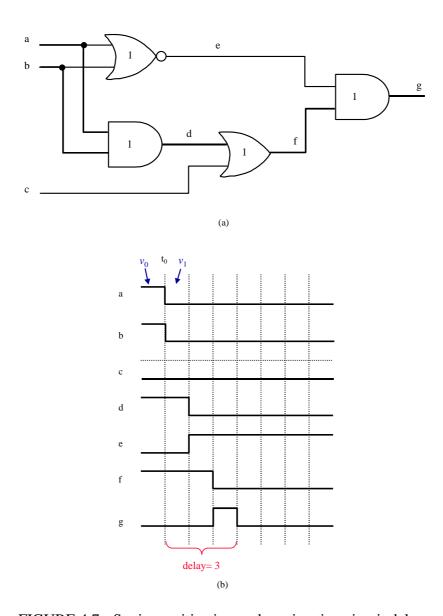

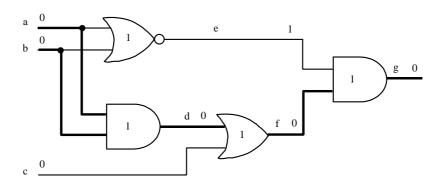

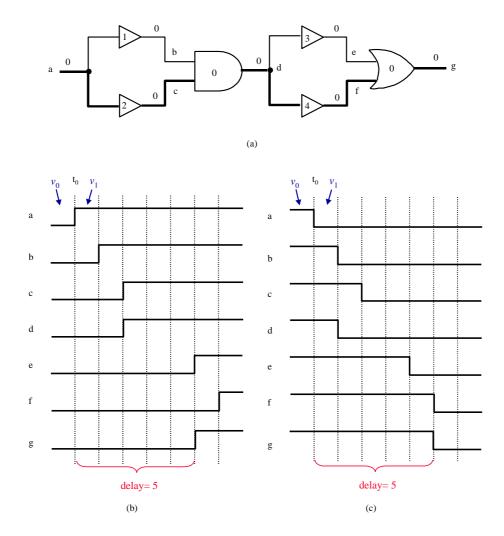

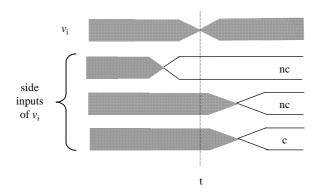

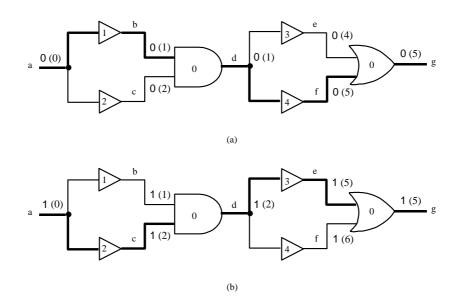

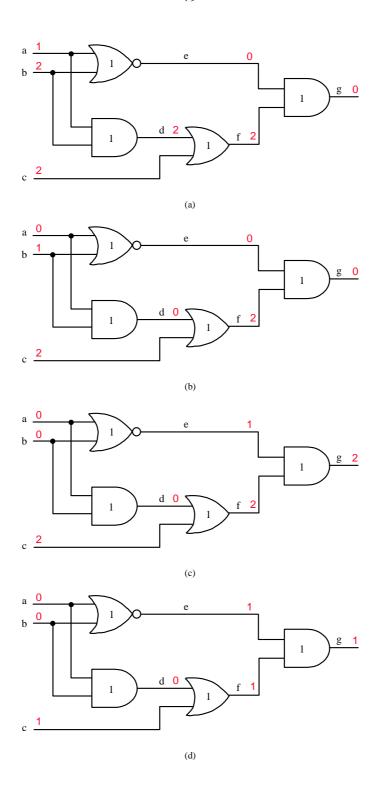

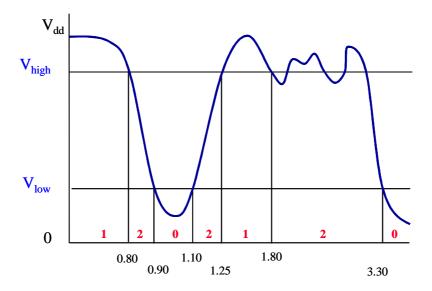

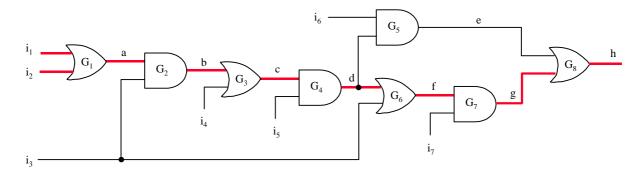

The concept of circuit delay computation model was motivated by the observation that the delay of a circuit depends on the nature of its inputs, that is, whether the inputs are assumed to be made of **pairs of vectors** or **sequences of vectors**. To illustrate this, consider the test circuit of figure 2.5a (borrowed from [LAM94]), with gate delays as assigned inside each gate. The longest path of this circuit is (a, c, f, y), with delay 5. If the inputs are considered to be made of pairs of vectors, then the latest output transition occurs at t=1. A possible input combination that generates a latest output transition is shown in figure 2.5b. On the other hand, if the inputs are considered to be made of sequences of vectors, then the latest output transition occurs at t=3. A possible input vector sequence that leads to this late output transition is shown in figure 2.5c. These results confirm that circuit delay may differ according to the type of applied inputs.

FIGURE 2.5 - The delay of circuits depends upon the type of inputs considered.

In order to compute the delay by a pair of vectors, it is assumed that a vector  $v_1$  is applied at  $t=-\infty$  and a second vector  $v_2$  is applied at t=0. The delay of a circuit is then defined as the maximum arrival time of the last output transition over all possible pairs of vectors. From the definition it becomes clear that all circuit nodes are assumed to be settle to their stable values with respect to  $v_1$  by the time vector  $v_2$  arrives.

Using the delay by pairs of vectors to estimate the circuit's critical delay is equivalent to assuming that the circuit operates in a fully synchronous manner. This type of operation has been referred to as the **transition mode** and the critical delay thus obtained is called **transition delay** of the circuit [DEV92].

It has been conjectured that the transition delay is the exact delay of a circuit [SIL99]. Indeed, this would be true if one could always guarantee a fully synchronous operation of combinational blocks within synchronous circuits. However, memory elements may present different propagation times that can lead to the misalignment of inputs. Also, a supposed benefit of the transition delay method is that, besides the delay estimation, it generates the pair of vectors responsible for this delay, thus allowing the certification of this delay through circuit simulation.

An implementation of transition delay calculation is proposed in [DEV92] and [DEV94a]. It uses symbolic simulation along with some sophisticated delay computation model. Further improvements concerning event suppression were proposed in an attempt to reduce the time complexity of this symbolic simulation based implementation [DEV94b]. The transition delay method presents severe disadvantages that have prevented its use in practical FTA tools, however. Firstly, the search space for determining the critical input vector pair situation is  $2^{2n}$ , with n being the number of primary inputs to the circuit. Secondly, the delay computation model used, the bounded model (see section 2.4), makes the symbolic simulation extremely expensive from the computation's point of view.

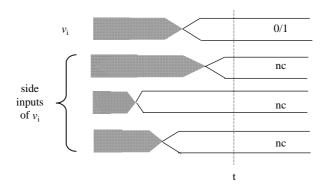

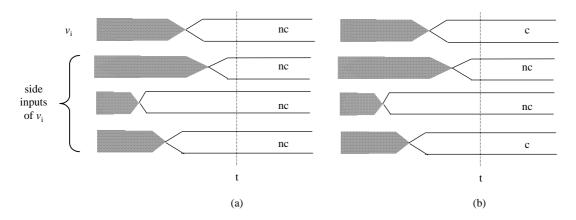

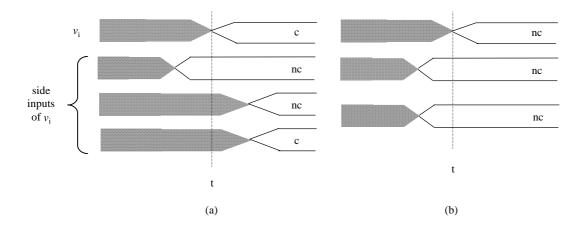

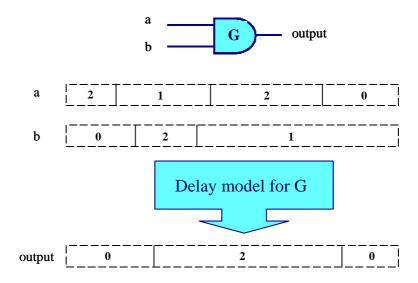

The problems with delay by pairs of vectors (transition mode) have motivated the massive use of the **single vector** approach. The single vector approach is an approximation of the delay by sequences of vectors. It conservatively assumes the nodes of a circuit to be arbitrary, i.e. "floating", before they are settle by a single input vector v. The delay of the circuit is the latest settling time over all possible single vectors  $v_i$ . The assumption of floating nodes comes from the fact that the circuit may be still propagating the input vectors applied before v, what would cause the circuit nodes to be floating. In the literature, the assumption of the single vector approach is incarnated by the designation of "floating mode of operation" [CHE91] and the delay thus obtained is referred to as the **floating delay** of the circuit.

The only known implementation of delay by sequence of vectors is presented in [LAM93] and [LAM94]. It is based on a sophisticated formalism called **timed Boolean functions** (TBFs), which is claimed to unify the Boolean and the timing behavior of circuits. The problem with this implementation is that due to the complex formulation, it demands significant computation effort, mainly if mode detailed delay models are to be used.

Although delay by sequences of vectors would be desirable, the majority of existing FTA algorithms adopts the single-vector (floating) delay computation model due to its ease of implementation and smaller computational cost. Moreover, it has been reported in [LAM94] that for most practical circuits made of simple gates the delay by sequences of vectors and the single vector delay are coincident. And for the cases where they are not coincident, single vector delay is an upper bound on the actual circuit delay, while the delay by sequences of vectors is the exact delay. Also, single-vector techniques may use many of already existing test generation algorithms.

#### 2.4 Component Delay Models

Component delay models refers to the **physical model** (also called circuit-level model) used to estimate the delay of each circuit component, thus obtaining individual delay information that will be used to determine the delay of the circuit as a whole. This information is generally expressed in terms of equations that use parameters derived from extensive transistor-level and/or device-level simulation of circuit components.

Logic synthesis tools as SIS [SEN92] generally use the linear delay model, which is the simplest physical model. In the linear delay model of SIS, for instance, the delay across a pin i, d(i), of a gate is given by:

$$d(\mathbf{i}) = A(\mathbf{i}) + B(\mathbf{i}) \times C_L(\mathbf{i}) \qquad (2.3)$$

where A(i) is called **transport delay** for the gate at pin i, B(i) is the inverse of the drive capability of the gate and  $C_L(i)$  is the total capacitive load of the net represented by i, lumped at the output of the gate. Although this simple model does not take into account some important features of CMOS technology (e.g., short channel devices, slow input ramps and body effect), it is still used by the majority of logic synthesis tools because it does not require too expensive computations.

However, the study of more sophisticated delay models appears as a major subject of the work done in the timing verification field during the first half of the 80's. Probably, this is due to the fact that these works were directly related to the development of new microprocessors. This was the case of Ousterhout's **Crystal** [OUS85] and Jouppi's **TV** [JOU87], which were used in the timing validation of the RISC II and MIPS microprocessors, respectively.

Crystal divides the circuit into stages to evaluate the delay. A stage is defined as a chain of transistors and nodes between a signal source and a place where the signal is used. Hence, a stage may represent not only the MOS transistor chain up to the gate output but also any pass transistor chain being driven by the gate. A natural consequence of this switch-level modeling of MOS circuits is that the delay of connections would be implicitly considered within stages. Crystal has three physical delay models: the lumped RC model, the lumped **slope** model and the **distributed slope** model. In the lumped RC model each transistor type is characterized by two resistance values, being one for the case when the transistor is transmitting a logic 0 and another when it is transmitting a logic 1. These values are given in Ohms per square and are multiplied by the transistor's W/L to obtain the effective resistance. The delay through a stage is computed by lumping all resistances and capacitances. The lumped slope model incorporates information about waveform. Each waveform is represented by its inversion time and its rise time. This tries to model the effect of the load being driven by the stage on the effective resistance, leading to a more accurate delay estimation. The lumped model is too pessimistic in estimating the delay of distributed capacitances. The distributed slope model is similar to the slope model except that, instead of assuming all RC lumped, it uses the results of Penfield and Rubinstein [RUB83] for the delay of RC trees.

TV uses also the Penfield-Rubinstein model but with two simplifications: only the waveform estimate is computed, instead of the bounds, and only one path is assumed open through a tree of pass transistors. This reduces the accuracy of the model because the influence of the input ramp slope is only roughly considered.

The formerly cited physical models use linear elements to approximate the behavior of transistors which is non-linear in its essence. Thus, it is not a surprise that a significant error may occur. Looking for more accurate delay estimations, Horowitz has proposed the use of non-linear elements for dealing with both transistors and interconnection networks [HOR84]. In his formulation the input ramp slope is modeled by a hyperbolic function while the transistor is modeled by a simple quadratic function.

A third possibility for delay modeling is to use explicit formulation. According to this approach the delay is estimated by using a closed formulation that includes parameters for technology characterization. Some of these parameters may be obtained from device extraction while others may come from exhaustive electrical simulation. But once the target technology is appropriately characterized, the delay of circuit components is estimated only by

using the formulae, without any other supporting means as, for instance, electrical simulation. Examples of explicit analytical formulations are the alpha-power model [SAK88] and the explicit formulation of [DES88].

In the explicit formulation of [DES88] the delay of an inverter with minimum W and L is used as a standard measure for a given technology. To this delay quantity various correction terms may be applied in order to generalize the delay estimation to nor and nand gates, possibly with Wn/Wp≠1. To consider the effect of slow input ramp a correction term was added latter to the formulation [AUV90]. Recently, the formulation was revised in order to account for the effects of submicronic technologies [DAG99].

Recent advances in CMOS technology have shrinked device dimensions to nanometers. Many electrical effects that were formerly disregarded in micronic technologies became very important in current submicronic (or nanometric) technologies and constitute sources of errors that may compromise the correct operation of complex designs. A practical example of such phenomenon is the effect of circuit interconnections. In submicronic technologies the delay of interconnections is considerable and frequently dominates the delay of circuit gates themselves. Hence, physical delay models for interconnections begin to play a very important role in the delay estimation. The basic models for interconnection analysis are those that evaluates RC networks as the Elmore's [ELM48], Sakurai's [SAK83], Penfield-Rubinstein [RUB83], Horowitz [HOR84] and also the models of Crystal. With the advent of submicronic technologies interconnection analysis has come into focus again and several works that simultaneously consider gate and connection delays have been published. A referential work was the interconnection analysis program called RICE [RAT94], that uses a technique known as AWE (Asymptotic Waveform Evaluation), which is based on the moments of the impulse response. Currently, several other works are being developed for modeling the delay of gates and connections for submicronic technologies (e.g., [FOR97][HIR98]).

A more detailed discussion on physical models for component delay calculation is beyond the scope of this work. A good review on this issue may be found in [UEB95], which also presents an analytical semi-empirical delay model that uses a latency time and an effective linear resistance to model the exponential region of the output curve of a stage.

### 2.5 Gate Delay Computation Models

The simplest gate delay computation model is known as the **fixed delay model** [DEV94]. It assumes that the delay of a gate is a fixed value d. A natural extension to this model is to assign a fixed delay value  $d_i$  to each input i of a gate. Another variation is to consider separate falling and rising delays by either assigning a single pair of delays [df,dr] to the gate or assigning a pair of delays  $[df_i,dr_i]$  to each input i. The assignment of a fixed delay or a pair of fixed delays per input is also referred to as **pin-to-pin** delay.

One important issue that arrives in timing analysis is that it is not intended to provide the critical delay of a single manufactured instance but the delay of the entire family of manufactured circuits of the same design. In this sense, the use of TTA along with maximal individual gate delays leads just to an upper bound on circuit delay. However, current submicronic designs demand more accurate delay estimations (at least tighter upper bounds), what, from the computational's point of view, can be accomplished by using the FTA approach. On the other hand, the use of maximal gate delays in FTA is not sufficient to assure that the estimated circuit delay really represents an upper bound over the entire family of

manufactured circuit instances: due to the sensitization phenomenon, maximal individual gate delays may result in an underestimation of circuit delay, what would be an unacceptable erroneous prediction. This phenomenon is known as the **monotone speedup failure** [MCG91] and will be commented in more detail in the next section.

35

In order to assure that FTA will not underestimate circuit delay, gate delays must be specified within a bounded interval  $[d^{min}, d^{max}]$ , where  $d^{min}$  and  $d^{max}$  represent the minimum and the maximum delay of the gate, respectively. This is the so-called **bounded delay model** and is the model underlying the transition delay computation. The bounded delay may also be assigned in pin-to-pin format. A modification on the bounded delay model consists of considering  $d^{min} = 0$ , which is commonly referred to as **unbounded delay model** (meaning unbounded bellow)<sup>4</sup>. As it will be shown in the next section, this is the model used for computing the floating delay under the monotone speed up property.

The previously described gate delay models implicitly divide signal magnitude into two values, either 0 or 1. Obviously, a more detailed analysis could be performed if signals were represented with a multi-valued logic. In the case of a ternary logic, for instance, a signal may assume one among the values (0,1,X) at a time, where X represents signal magnitudes between the 0-threshold and the 1-threshold. Ternary logic has been used for hazard detection and logic simulation [SEG89]. In [MCG93], ternary logic was formalized to be used in the FTA context, with the addition of the third state (X) to both bounded and unbounded models, originating the **extended bounded delay model** (XBD) and the **extended bounded-zero delay model** (XBD0), respectively.

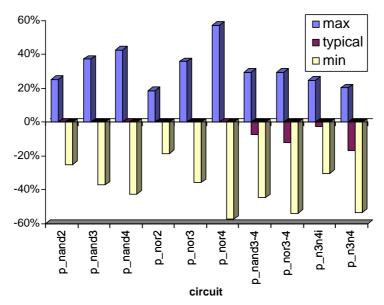

#### 2.6 Robustness and Correctness of FTA algorithms