# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

## FELIPE DOS SANTOS MARRANGHELLO

# Logic synthesis for sequential material implication logic based on resistance switching devices

Thesis presented in partial fulfillment of the requirements for the degree of Doctor in Microelectronics

Advisor: Prof. Dr. Renato Perez Ribas Co-advisor: Prof. Dr. André Inácio Reis

# CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Marranghello, Felipe dos Santos

Logic synthesis for sequential material implication logic based on resistance switching devices / Felipe dos Santos Marranghello. – 2017. 120 f.:il.

Orientador: Renato Perez Ribas; Co-orientador: André Inácio Reis. Tese (Doutorado) — Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica. Porto Alegre, BR — RS, 2017.

1. Síntese lógica. 2. Implicação material 3. Dispositivos memristivos. I. Ribas, Renato Perez. II. Reis, André Inácio. III. Logic synthesis for sequential material implication logic based on resistance switching devices.

## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof. Carla Maria Dal Sasso Freitas Coordenadora do PGMICRO: Prof. Fernanda Gusmão de Lima Kastensmidt Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

# **AGRADECIMENTOS**

Agradeço ao meu pai Carlos Roberto Marranghello, à minha mãe Eunice dos Santos Marranghello e à minha irmã Letícia dos Santos Marranghello.

Agradeço aos meus orientadores Renato Perez Ribas e André Inacio Reis. Aos colegas de laboratório e a todos que me apoiaram durante o caminho.

Agradeço ao CNPq pelo financiamento durante o doutorado.

# Síntese lógica para lógica de implicação sequencial usando dispositivos com resistência variável

Dispositivos de resistência variável (RSD) são alternativas promissoras para a criação de memórias não voláteis (NVM). Estas memórias também podem influenciar o projeto de circuitos digitais através de "lógica em memória". Dentre tais paradigmas lógicos está a lógica de implicação material (RSD-IMP). A principal diferença entre RSD-IMP e lógica convencional é que em RSD-IMP as funções Booleanas são computadas através de uma sequência de operações de implicação material (IMP). Tais operações também são chamadas de instruções. Neste sentido, o paralelismo de circuitos digitais convencionais não é observado em RSD-IMP porque uma única instrução é feita por ciclo. Esta tese propõe métodos de síntese lógica para RSD-IMP. Dada uma representação de uma função Booleana, o objetivo é obter uma sequência de operações em RSD-IMP que corresponda a esta função. As métricas para avaliar a qualidade de uma solução são o número de instruções e o número de RSD. Um ponto interessante de RSD-IMP é que, para qualquer função Booleana de n variáveis, existe uma sequência de instruções para esta função que necessita de apenas n+2RSD. A principal maneira de se obter tal sequência é através de uma forma Booleana recursiva (RBF) correspondente à função alvo. A primeira contribuição deste trabalho é a proposta de um método mais eficiente para sintetizar RBF a partir de soma-de-produtos (SOP). Então, o conceito de RBF é generalizado para soma-de-RBF (SRBF). É demonstrado que SRBF também podem ser diretamente transformadas em uma sequência de instruções que pode ser computada com n+2 RSD. Relaxando a restrição de n+2 RSD para n+k RSD, com  $k \ge 2$ , é possível explorar a classe de RBF fatorada (FRSBR). Finalmente, é discutido o projeto lógico de somadores binários baseados em RSD-IMP.

**Palavras-chave**: Síntese lógica, lógica de implicação material, memristors, dispositivos com resistância variável, circuitos digitais, funções Booleanas.

# Logic synthesis for sequential material implication logic based on resistance switching devices

Resistance switch devices (RSD) are promising alternatives to implement nonvolatile memories (NVM). These memories can also influence the design of digital circuits through logic-in-memory. Among these novel logic paradigms is the material implication (RSD-IMP) logic. The main difference between RSD-IMP logic from conventional digital circuit design is that Boolean functions are evaluated in RSD-IMP logic as a sequence of material implication (IMP) operations, known as instructions. In this sense, the parallelism observed in standard digital design is not obtained because a single IMP operation is performed per cycle. This thesis focuses on logic synthesis methods for RSD-IMP logic. Given a standard description of a Boolean function, the goal is to obtain a sequence of operations in RSD-IMP logic to evaluate the target function. The standard cost metrics are the number of instructions and the number of RSD required. An interesting aspect of RSD-IMP logic is that, for any n-input Boolean function f, there is a sequence of instructions in RSD-IMP that evaluates f using n+2RSD. The main method to obtain such a sequence of instructions is to synthesize a recursive Boolean form (RBF) for f. The first contribution of this thesis is a more efficient method to synthesize RBF from a sum-of-products (SOP). Moreover, the concept of RBF is generalized to obtain a broader class of expressions that can be transformed into sequence of operations requiring only n+2 RSD. This new class of expressions is named sum-of-RBF (SRBF). Furthermore, the constraint of n+2 RSD is relaxed to allow n+k RSD, where  $k \ge 2$  is an arbitrary integer. By relaxing this constraint, the class of factored SRBF (FSRBF) is obtained. The number of additional RSD can be controlled by considering the logic depth of FSRBF during the logic synthesis process. Finally, the logic design of binary adders in RSD-IMP logic is discussed.

**Keywords**: Logic synthesis, material implication logic, memristors, resistance switching devices, digital circuits, Boolean functions.

# LIST OF FIGURES

| Figure 1.1 – Symbol of a RSD. The output terminal is marked by a thick black line. A positive volt                           | age |

|------------------------------------------------------------------------------------------------------------------------------|-----|

| bias reduces the resistance value, whereas a negative voltage bias increases the resistance value                            |     |

| Figure 1.2 – Basic crossbar structure, a RSD is placed at each intersection.                                                 |     |

| Figure 1.3 – Basic reading scheme in a RSD crossbar.                                                                         |     |

| Figure 1.4 – Sneak path problem in RSD crossbar.                                                                             |     |

| Figure 1.5 – High fanin NOR gate using a hybrid RSD/CMOS structure.                                                          |     |

| Figure 1.6 – Hybrid RSD/CMOS threshold logic gate.                                                                           |     |

| Figure 1.7 – Switch network like implementation for $f = ab + cd$ in RSD crossbar (the missing R                             |     |

| is tied to the HRS).                                                                                                         |     |

| Figure 1.8 – Basic structure for RSD-IMP logic: (a) basic structure and (b) corresponding truth table                        |     |

| Tigure 1.0 Busic structure for 1655 fivil fogie. (a) custo structure and (b) corresponding trust tab.                        |     |

| Figure 1.9 – RSD based majority logic: (a) basic structure and (b) corresponding truth table                                 |     |

| Figure 1.10 – Example of a hybrid approach for logic-in-memory using RSD: (a) first cycle to                                 | 17  |

| compute intermediate values, and (b) final cycle to evaluate the final value of the function                                 | 18  |

| Figure 1.11 – Basic RSD-IMP logic block with two inputs and two auxiliary RSD.                                               |     |

| Figure 2.1 – Different coverings $f *= x0 x2 + x1x2 + x0 x1$ : (a) initial, (b) after reduction of cult                      |     |

| x0x1 to $x0x1$ $x2$ , (c) after expanding $x0x1x2$ to $x1x2$ , and (d) final minimum covering                                |     |

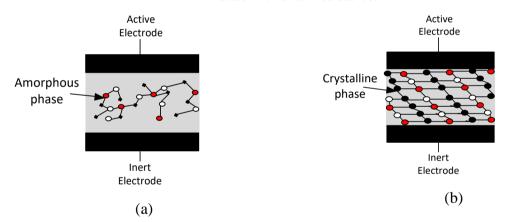

| Figure 3.1 – Ideal I-V curves for different types of RSD: (a) unipolar and (b) bipolar                                       |     |

| Figure 3.2 – Electrochemical memristive device: (a) RSD in LRS with a CF, and (b) RSD in HRS                                 |     |

|                                                                                                                              |     |

| ruptured CF                                                                                                                  |     |

|                                                                                                                              |     |

| state with small resistance.  Figure 3.4 – Basic structure of STT-MTJ.                                                       |     |

|                                                                                                                              |     |

| Figure 3.5 – Spin-transfer-torque effect in a magnetic tunnel junction: (a) from anti-parallel to para                       |     |

| and (b) from parallel to anti-parallel.                                                                                      |     |

| Figure 3.6 – Basic topology for RSD-IMP logic structure                                                                      |     |

| Figure 3.7 – Equivalent resistive circuit for IMP operation.                                                                 | 45  |

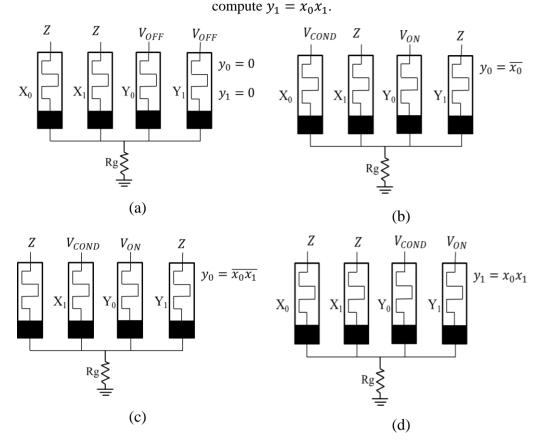

| Figure 3.8 – Voltages for each instruction to evaluate the AND2 function: (a) reset cycle; (b)                               |     |

| instructions to compute $y0 = x0$ ; (c) instructions to compute $y0 = x0x1$ ; (d) last instructions to compute $y1 = x0x1$ . | 40  |

|                                                                                                                              |     |

| Figure 3.9 – Schematic of the architecture for RSD-IMP logic structure.                                                      | 49  |

| Figure 3.10: Synthesis process for the XOR2 function: (a) original function representation, (b)                              | 1   |

| complemented function, (c) resulting function $FI$ after selecting the cube $x0x1$ , (d) function $F1$ , and                 |     |

| (e) final map after selecting the cubes $x0$ and $x_1$                                                                       |     |

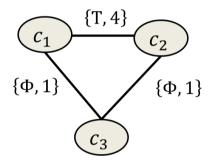

| Figure 3.11 – Graph for function $f = x0 x1$ .                                                                               |     |

| Figure 3.12 – Parallel structure for RSD-IMP logic structure                                                                 |     |

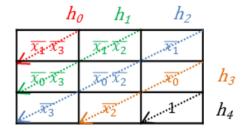

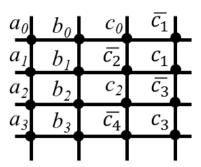

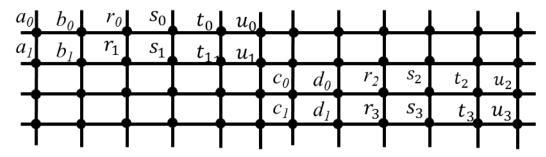

| Figure 4.1 – Example of matrix for AND decomposition.                                                                        |     |

| Figure 4.2 – Matrix view for <i>Example 4.2.2</i> .                                                                          |     |

| Figure 4.3 – Matrix view for XNOR decompositions.                                                                            |     |

| Figure 4.4 – Matrix view for Example 4.2.3.                                                                                  |     |

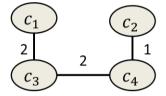

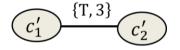

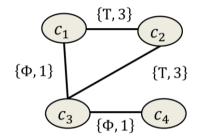

| Figure 5.1 - Graph for Example 5.1.1.                                                                                        |     |

| Figure 5.2 – Graph for Example 5.1.3                                                                                         |     |

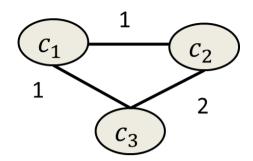

| Figure 5.3 – Graph corresponding to Example 5.2.2.                                                                           |     |

| Figure 5.4 – Graph corresponding to (5.2.6).                                                                                 |     |

| Figure 5.5 – Graph for Example 5.2.3                                                                                         |     |

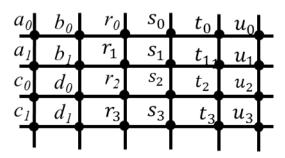

| Figure 6.1 – Carry-in configuration for the multiple-lines RCA                                                               |     |

| Figure 6.2 – Crossbar structure to implement sums A+B and C+D in parallel using the multiple-lin                             |     |

| RCA                                                                                                                          | 111 |

| Figure 6.3 – Alternative crossbar structure to implement sums A+B and C+D in parallel using the                              |     |

| multiple-lines RCA.                                                                                                          | 112 |

# LIST OF TABLES

| Table 1.2.1 – Evaluation of AND2 in RSD-IMP logic.                                             | 20  |

|------------------------------------------------------------------------------------------------|-----|

| Table 1.2.2 – Evaluation of OR2 in 6 cycles using 4 RSD.                                       |     |

| Table 1.2.3 – Evaluation of OR2 in 5 cycles using 5 RSD.                                       | 21  |

| Table 1.2.4 – Evaluation of OR2 in 3 cycles using 4 RSD.                                       |     |

| Table 2.1 – Matrix for single cube divisor extraction for (2.2.12)                             | 32  |

| Table 2.2 – Matrix for multiple cube divisor extraction for (2.2.14).                          | 33  |

| Table 2.3 – Matrix to exemplify the need for redundancy.                                       | 34  |

| Table 2.4 – Truth table for $\hat{f} = x0x1 + x0x2$ .                                          |     |

| Table 2.5 – Basic functions for FC using three input variables.                                | 36  |

| Table 2.6 – Expressions with 2 literals and the respective truth table represented as integers | 37  |

| Table 3.1 – Truth table for material implication.                                              |     |

| Table 3.2 - Sequence of operations to evaluate the XNOR3 function.                             | 51  |

| Table 4.1 - Proposed sequence of instructions to evaluate the XNOR3 function                   |     |

| Table 4.2 – Proposed sequence of instructions to evaluate equation (4.1.14)                    |     |

| Table 4.3 – Proposed sequence of instructions to evaluate the XOR3 function                    | 62  |

| Table 4.4 – 2-to-1 multiplexer truth table.                                                    | 65  |

| Table 4.5 – Comparison of RBF synthesis methods for 4-input functions.                         | 80  |

| Table 4.6 - Comparison among different RBF synthesis methods for functions with at most 20 in  |     |

| taken from ESPRESSO literature (BRAYTON, 1984)                                                 | 83  |

| Table 5.1 – Sequence of operations to evaluate (5.1.6).                                        | 88  |

| Table 5.2 – Sequence of operations to evaluate (5.2.3).                                        |     |

| Table 5.3 – Sequence of operations to evaluate the SC-FSRBF given by (5.2.7)                   | 95  |

| Table 5.4 – Comparison among different algorithms proposed for SRBF synthesis                  | 98  |

| Table 5.5 – RBF and SRBF comparison for the 15 largest functions in the benchmark set          |     |

| Table 5.6 - RBF and SRBF comparison for the 15 largest functions in the benchmark set limited  |     |

| 150 cycles                                                                                     |     |

| Table 5.7 – FC-SRBF results for the 15 most complex functions                                  | 101 |

| Table 6.1 – Sequence of operations to evaluate (6.1.1) using the complemented inputs method    | 102 |

| Table 6. 2 – Sequence of operations to evaluate (6.1.1) as a RBF.                              |     |

| Table 6.3 – Sequence of operations to evaluate (6.1.3).                                        | 104 |

| Table 6.4 – Comparison of the complemented inputs approach to SC-FCSRBF                        | 106 |

| Table 6.5 – Cycles to evaluate a FA based on (6.2.2)                                           | 107 |

| Table 6.6 – Cycles to evaluate a FA in the single line RCA.                                    |     |

| Table 6.7 – Carry computation for even index.                                                  |     |

| Table 6.8 Carry computation for even index                                                     |     |

| Table 6.9 – Sum evaluation for even and odd indexes.                                           |     |

| Table 6.10 – Comparison of the proposed adders to previous work                                | 113 |

## LIST OF ABBREVIATIONS AND ACRONYMS

AIG And-inverter-graph

AP Antiparallel

BDD Binary decision diagram

FA Full-adder

FL Free layer

FLF Four-level-form

FSRBF Factored sum-of-recursive-Boolean-forms

IMP Material implication

ISOP Irredundant sum of products

LUT Look-up table

MTJ Magnetic tunnel junction

POS Product-of-sums

PP Parallel

RBF Recursive Boolean Form

RCA Ripple-carry adder

RL Reference layer

RSD Resistance switching device

RSD-IMP Material implication logic based on RSD

SC-FSRBF Single-cube factored recursive Boolean forms

SCE Short circuit evaluation

SOP Sum of products

SRBF Sum of Recursive Boolean Forms

STT Spin-transfer-torque

VO Oxygen vacancy

# **SUMMARY**

| 1. INTRODUCTION                                           | 12 |

|-----------------------------------------------------------|----|

| 1.1 Logic Styles For Resistance Switching Devices         | 14 |

| 1.3 OVERVIEW Of RSD-IMP Logic                             | 19 |

| 1.2 challenges and Motivation                             | 21 |

| 1.3 Thesis Proposal                                       | 23 |

| 1.4 Text organization                                     | 24 |

| 2 LOGIC SYNTHESIS BACKGROUND                              | 26 |

| 2.1 definitions                                           | 26 |

| 2.2 Representations of Boolean functions                  | 27 |

| 2.2.1Truth Table and Karnaugh Map                         |    |

| 2.2.2 Sum-of-products and two-level minimization          |    |

| 2.2.2.1 SOP of Unate Functions                            |    |

| 2.2.3 Binary Decision Diagram                             |    |

| 2.2.4 Factored forms, factoring, and division             | 30 |

| 2.3 Functional composition                                | 34 |

| 2.3 PROBABILITY OF BOOLEAN FUNCTIONS                      | 37 |

| 3 RESISTIVE SWITCHING DEVICES                             | 39 |

| 3.1 Electrical behavior of resistance switching devices   | 39 |

| 3.2 Material implication logic                            | 43 |

| 3.2.1 Overview                                            | 43 |

| 3.2.2 Logic and electrical behavior                       |    |

| 3.2.3 Logic synthesis for RSD-IMP logic                   |    |

| 3.2.3.1 Recursive Boolean forms                           |    |

| 3.2.4.2 Logic synthesis methods for RSD-IMP logic         |    |

|                                                           |    |

| 4 SYNTHESIS AND EVALUATION OF RECURSIVE BOOLEAN FORMS     | 58 |

| 4.1 Evaluation of recursive Boolean forms                 | 58 |

| 4.1.1 Reverse Evaluation of Recursive Boolean Forms       | 58 |

| 4.1.2 Short circuit Evaluation of Recursive Boolean Forms | 63 |

| 4.2 Synthesis of recursive boolean forms                  | 64 |

| 4.2.1 Functional Composition Based Synthesis              | 65 |

| 4.2.2 Decomposition Based Synthesis                       |    |

| 4.2.2.1 AND Decomposition                                 | 67 |

| 4.2.2.2 Sharp, NOR and OR decompositions                  | 74 |

| 4.2.2.3 XOR and XNOR decompositions                       |    |

| 4.3 Simplification of RRF                                 | 77 |

| 4.4 Experimental Results                                                                                                                                                 | 79  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5 SYNTHESIS AND EVALUATION OF SUM OF RECURSIVE FORMS                                                                                                                     |     |

| 5.1 Sum-of-recursive-Boolean-forms                                                                                                                                       | 84  |

| 5.2 Single-cube FactorED sum-of-recursive-boolean-forms                                                                                                                  | 91  |

| 5.3 Experimental Results                                                                                                                                                 | 98  |

| 6 OTHER CONTRIBUTIONS                                                                                                                                                    | 102 |

| 6.1 Complemented inputs approach                                                                                                                                         | 102 |

| 6.2 Logic design of Binary adder 6.2.1 Full adder design 6.2.2 Single-Line Ripple carry 6.2.3 Multiple lines RCA 6.2.3.1 Carry computation 6.2.3.2 Sum output evaluation |     |

| 7 CONCLUSIONS AND FUTURE WORK                                                                                                                                            | 114 |

| 7.1 Future work                                                                                                                                                          | 114 |

| REFERENCES                                                                                                                                                               | 116 |

#### 1. INTRODUCTION

Advances on nanotechnologies processes have enabled the development of novel beyond CMOS devices that may be exploited in future computing systems. Among such devices, resistance switching devices (RSD), also known as memristors or memristive devices (STRUJOV, 2008), (CHUA, 2011), have great potential to be exploited in nonvolatile memories (NVM) (AKINAGA, 2010), (KENT, 2015). Moreover, RSD can also lead to novel alternatives to perform logic. In particular, RSD is suitable to logic-in-memory paradigms where logic is performed directly at the memory bits without the need to transfer data to a processing unit (ZHU, 2013), (WONG, 2015). In this sense, logic-in-memory may contribute to reduce the memory bottleneck.

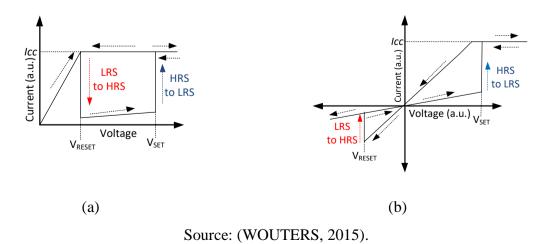

RSD have been investigated since the 1960's (HICKMOTT, 1962), (GIBBSONS,1964), (SIMMONS, 1967). The state of a RSD can be toggled between a low-resistance state (LRS) and a high-resistance state (HRS). Therefore, the resistance state can be used to encode binary information, where the LRS represents the logic level '1' whereas the HRS represents the logic level '0'.

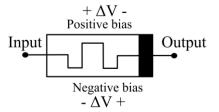

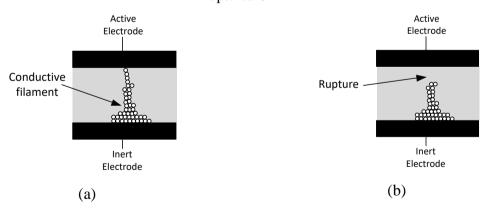

The basic structure of a RSD is a capacitor like metal-insulator-metal (MIM) structure, (KENT, 2015), (MEENA, 2014), (PAN, 2014), (VALOV, 2013), (WONG, 2012), (WOUTERS, 2015). However, by applying a voltage bias, the insulator can be modified to become a conductor. The transition between the insulator and conductor states corresponds to the transitions between the HRS and LRS. This transformation can occur due to different physical phenomena, including the creation/rupture of a conductive filament connecting the metallic terminals and a phase change from a highly resistive amorphous phase to a conductive crystalline phase. Since these transformations require a minimum electrical field to occur, it is possible to apply small voltage bias without modifying the device state. Fig. 1.1 illustrates the electrical symbol of a RSD.

Figure 1.1 – Symbol of a RSD. The output terminal is marked by a thick black line. A positive voltage bias reduces the resistance value, whereas a negative voltage bias increases the resistance value.

Source: The author.

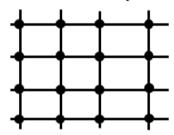

The main application of RSD is on the implementation of NVM. The basic structure of a NVM based on RSD is a matrix comprising horizontal and vertical wires, also known as crossbar. The basic structure, known as passive crossbar, is illustrated in Fig. 1.2 (MEENA, 2014). The sets of vertical and horizontal wires are at different plans. At the intersection between a row and a column, there is a RSD connecting the wires. In Fig. 1.2, the black dots represent the RSD. The passive crossbar structure is interesting due to the possible high density. Each bit requires an area of  $4L^2$ , where L is the minimum feature size.

Figure 1.2 – Basic crossbar structure, a RSD is placed at each intersection.

Source: (MEENA, 2014).

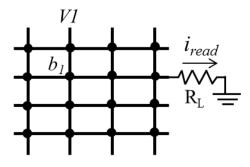

A RSD within the crossbar can be accessed by applying a voltage bias between the row and column where the device is placed and measuring the current through the RSD. The process is illustrated in Fig. 1.3, where the state of device  $b_I$  is read by applying a voltage bias VI to the device. The state of the device can be defined by sensing either the current or a voltage across a load resistor  $R_L$ . If current  $i_{read}$  across  $R_L$  is measured, then a high value of  $i_{read}$  indicates that  $b_I$  is in the LRS. Conversely, a low value of  $i_{read}$  means that  $b_I$  is in the HRS.

Figure 1.3 – Basic reading scheme in a RSD crossbar.

SOURCE: The author.

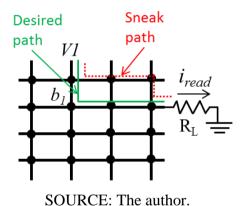

The main problem with this approach is the existence of sneak paths. A sneak path is an undesirable path for the current, as illustrated in Fig. 1.4. In Fig. 1.4, the solid green line represents the desired path for the current whereas the dotted red line represents one of many possible sneak paths. Sneak paths can make  $i_{read}$  to increase such that a device in the HRS is wrongly identified as being in the LRS. The sneak path current can be reduced by connecting the RSD to a selector which can be either a transistor or a diode, by using two RSD in an antiserial connection or by applying an intermediate voltage bias to unselected lines and rows. It has been shown that a single RSD can behave as a RSD connected to a diode or as two RSD in anti-serial connection.

Figure 1.4 – Sneak path problem in RSD crossbar.

RSDs have also been used in other applications in addition to NVM such as the design of field-programmable gate array architectures (FPGA) (GUO, 2017), neuromorphic systems (INDIVERI, 2015) and digital integrated circuit design. In the following, we focus on applications of RSD in digital design.

#### 1.1 LOGIC STYLES FOR RESISTANCE SWITCHING DEVICES

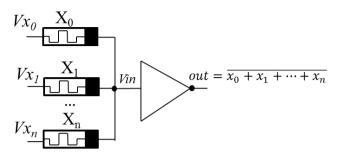

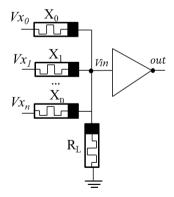

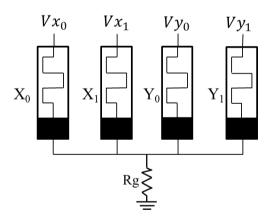

RSD can be exploited in several manners to perform logic. RSD can be combined with CMOS transistors to create high fanin NOR and NAND gates, as illustrated in Fig. 1.5 (KVATINSKY, 2012). In order to understand the behavior of the circuit, let all  $V_{x_i} = 0$  and all  $X_i$  be in the HRS. If  $V_{x_0}$  rises to the power supply voltage (Vdd), then voltage Vin remains close to 0 until  $X_0$  switches to the LRS. After this point, Vin rises to Vdd. As Vin rises, the remaining devices become negatively biased, as illustrated in Fig. 1.1 and enter the HRS. The resulting voltage divider allows Vin to reach a value near close to Vdd. The reverse current through the other RSD can be further reduced by using self-rectifying RSD.

Figure 1.5 – High fanin NOR gate using a hybrid RSD/CMOS structure.

Source: (KVATINSKY, 2012).

Hybrid RSD/CMOS gates can also be used to implement threshold logic (GAO, 2013), (FAN, 2014), (JAMES, 2014). One example of a hybrid RSD/CMOS gate is shown in Fig. 1.6 (JAMES, 2014). The basic structure is similar to the one shown in Fig. 1.5 with the inclusion of a load RSD that represents the threshold value of the function. The basic idea of this approach is that voltage *Vin* only rises to *Vdd* if there are enough inputs in *Vdd*. In order to fully benefit from these novel gates, logic synthesis methods focusing on threshold logic are important (NEUTZLING, 2014), (PALANISWAMY, 2014), (NEUTZLING, 2015), (KULKARNI, 2016). Notice that such hybrid approaches are increments on standard cell based design and are not suitable for logic-in-memory applications.

Figure 1.6 – Hybrid RSD/CMOS threshold logic gate.

Source: (JAMES, 2014).

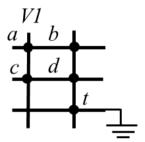

Logic circuit topologies for logic-in-memory using RSD can be broadly classified into switch based, instruction based and hybrid. In switch based approaches, the memory is configured as a switch network (LEEVY, 2014), (ALAMGIR, 2016), (PAPANDROULIDAKIS, 2017). A voltage is applied to a certain row and a target RSD is

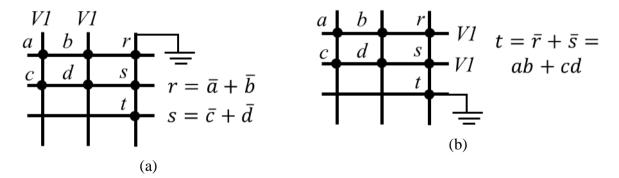

driven to the LRS only if the function represented by the given structure evaluates to 1. Fig. 1.7 shows an example of a crossbar structure configured as switch network, where RSD are placed in the intersections between the rows and columns. The missing RSD is fixed to the HRS. Voltage VI only propagates to RSD t when the following function f evaluates to true:

$$f = ab + cd (1.1.1)$$

Figure 1.7 – Switch network like implementation for f = ab + cd in RSD crossbar (the missing RSD is tied to the HRS).

Source: The author.

Switch based methods can benefit from standard algorithms for switch network generation (POSSANI, 2016), (KAGARIS, 2016), even though modifications may be required in order to consider the topology constraints of RSD-NVM. Notice that, even though the evaluation of the functions requires a single cycle, the time required to configure the crossbar in the desirable manner must be accounted for.

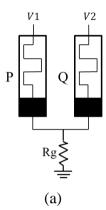

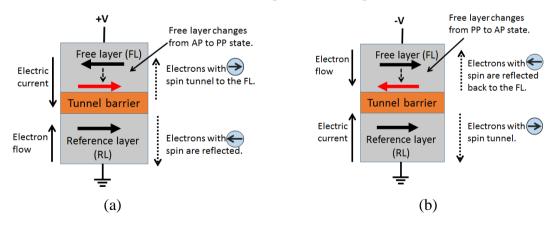

In instruction based approaches, the computation is performed as a sequence of basic instructions. The basic instruction can be either the material implication (IMP) (BORGHETTI, 2010), (ADAM, 2016), which is referred to as RSD-IMP, or the 3-input majority function (LINN, 2012), (GAILLARDON, 2016). The sequential behavior of these approaches represents a major difference to usual digital circuit design. Therefore, exploiting standard logic synthesis algorithms is not straightforward. This has motivated the development of novel logic synthesis algorithms focusing both majority logic (SHIRINZADEH, 2016), (SOEKEN, 2016) and RSD-IMP logic (LEHTONEN, 2010), 2015b), (MARRANGHELLO, 2015a), (MARRANGHELLO, (POIKONEN, (RAGHUVANSHI, 2014), (TEODOROVIC, 2013). The basic idea in IMP logic is to consider a structure as shown in Fig. 1.8(a), where two RSD P and Q are connected to a load resistor Rg through a common node. By applying appropriate voltages V1 and V2 to P and Q,

respectively, the final state of Q, denoted by q', becomes a function of the state of P, denoted by p. More specifically, the final state of Q is the LRS if the initial state of Q is the LRS or if P is in the HRS. This behavior can be translated into an IMP operation (BORGHETTI, 2010), as shown in Fig. 1.8(b). In Chapter 3, the behavior of IMP logic is detailed.

Figure 1.8 – Basic structure for RSD-IMP logic: (a) basic structure and (b) corresponding truth table.

| p | q   | q |

|---|-----|---|

| 0 | 0   | 1 |

| 0 | 1   | 1 |

| 1 | 0   | 0 |

| 1 | 1   | 1 |

|   | (b) |   |

Source: (BORGHETTI, 2010).

The idea for the RSD majority logic is to consider a single RSD P with voltages VI and V2 applied to its terminal, as shown in Fig. 1.9(a). Let p and p' denote the initial and final states of P, respectively. Fig. 1.9(b) shows the value of p' as function of p, VI and V2. The logic behavior corresponds to the following expression: (LINN, 2012):

$$p' = \overline{V2}(p + V1) + pV1 \tag{1.1.1}$$

Figure 1.9 – RSD based majority logic: (a) basic structure and (b) corresponding truth table.

(a)

| p | 1   | V2 | p' |

|---|-----|----|----|

| 0 | 0   | 0  | 0  |

| 0 | 0   | 1  | 0  |

| 0 | 1   | 0  | 1  |

| 0 | 1   | 1  | 0  |

| 1 | 0   | 0  | 1  |

| 1 | 0   | 1  | 0  |

| 1 | 1   | 0  | 1  |

| 1 | 1   | 1  | 1  |

|   | (b) | •  | •  |

Source: (LINN, 2012).

Hybrid approaches configure the crossbar as a switch network but control the data flow through instructions (KVATINSKY, 2014), (XIE, 2017). Fig. 1.10 presents an example of such hybrid methods based on the work described in (KVATINSKY, 2014), where a, b, c and d are the inputs while r, s and t are auxiliary RSD. Missing RSD are tied to the HRS. By applying an adequate voltage VI to the columns where the inputs are placed, r can be programmed to store  $\bar{a} + \bar{b}$  while s stores  $\bar{c} + \bar{d}$ , as shown in Fig. 1.10(a). Then, in a second step, t is programed to store ab + cd, as shown in Fig 1.10(b). Notice that the topology shown in Fig. 1.10 is similar to the shown in Fig. 1.8. The difference is the utilization of auxiliary RSD r and s to store intermediate values.

Overall, all approaches suffer from the need of a control block to either configure the crossbar, as in the case of switch based approaches, or to provide the correct control signals, as in the case of instruction based approaches. Hybrid approaches may fit into both cases. In this sense, reducing the number of RSD and the number of instructions should also reduce the size of the control block.

Figure 1.10 – Example of a hybrid approach for logic-in-memory using RSD: (a) first cycle to compute intermediate values, and (b) final cycle to evaluate the final value of the function.

Source: The author.

This thesis focuses on RSD-IMP logic. RSD-IMP appears to provide a good trade-off between the number of cycles and the number of RSD. However, it is not the goal to determine the best approach. It is worth noticing that, even though we have the RSD-IMP logic as motivation, this thesis mostly discusses synthesis and optimizations of different types of Boolean expressions. In this sense, the discussion presented herein may be useful to different logic topologies.

#### 1.2 OVERVIEW OF RSD-IMP LOGIC

This Section presents an overview of RSD-IMP logic. A more detailed explanation is presented in Section 3.2. In RSD-IMP logic, binary values are represented through the resistance of a RSD. A RSD in the LRS represents the logic value '1', whereas a RSD in the HRS represents the logic value '0'.

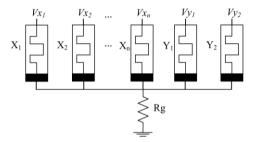

The basic structure of RSD-IMP logic comprises several RSD connected to a common node and to a load resistor Rg. There are n RSD that store the primary input variables and  $k \ge 2$  auxiliary RSD. These auxiliary RSD correspond to auxiliary variables and are used to perform computation. Fig. 1.11 presents a simple example of a RSD-IMP block with two input variables and two auxiliary RSD. Computation is performed as a sequence of instructions. Each instruction is obtained by applying a voltage bias to different RSD. Due to the common node, the voltage bias across a RSD depends on the bias applied to others RSD. This dependence allows logic to be performed.

Figure 1.11 – Basic RSD-IMP logic block with two inputs and two auxiliary RSD.

Source: The author.

When performing an operation, each RSD can either be set to a high-impedance state or be biased by one of the three different control voltages. These three control voltages are  $V_{OFF}$ ,  $V_{ON}$  and  $V_{COND}$ .  $V_{OFF}$  corresponds to a voltage value that forces the RSD to the HRS,  $V_{ON}$  sets the RSD to the LRS and  $V_{COND}$  does not change the state of the RSD.

The operations that can be performed in RSD-IMP logic are the reset, single-input implication and multi-input implication. The reset operation sets one or more RSD to the HRS. The reset operation is performed by applying  $V_{OFF}$  to the target RSD.

A single-input implication between two variables  $x_0$  and  $y_0$  ( $x_0 o y_0$ ) is performed by applying  $V_{COND}$  to  $X_0$  and  $V_{ON}$  to  $Y_0$ . If  $x_0 = 0$ , then  $V_{ON}$  sets  $Y_0$  to the LRS and  $y_0 = 1$ .

Otherwise,  $x_0 = 1$ ,  $V_{COND}$  reduces the voltage across  $Y_0$  such that  $V_{ON}$  does not suffice to cause a transition from the HRS to the LRS. In this case, the value  $y_0$  is not changed. Therefore, the final value of  $y_0$  is 1 if the initial value of  $y_0$  is 1 or if  $x_0$  is equal to 0. This behavior can be interpreted as the material implication operation (IMP), as follows:

$$y_0' \coloneqq x_0 \to y_0 = \overline{x_0} + y_0 \tag{1.2.1}$$

where  $y_0'$  is the next state of  $y_0$ . Since the result of the IMP operation is always stored at  $y_0$ , we write (1.2.1) simply as  $x_0 \to y_0$ .

To perform a multi-input implication,  $V_{COND}$  is applied to several devices  $X_1, ..., X_n$  while  $V_{ON}$  is applied to a target device  $Y_0$  (SHIN, 2011). If all devices to which  $V_{COND}$  is applied are in the HRS, then the target device switches to the LRS. Otherwise, the state of the target device does not change. Therefore, the final value of  $y_0$  is 1 if the initial value of  $y_0$  is 1 or if all  $x_1, ..., x_n$  are equal to 0. A multi-input implication can be written as follows:

$$(x_1 + \dots + x_n) \to y_0 = \overline{x_1} \dots \overline{x_n} + y_0 \tag{1.2.2}$$

Notice that the correct behavior of the circuit depends on defining adequate values for  $V_{OFF}$ ,  $V_{ON}$ ,  $V_{COND}$  and Rg. Several works have proposed methodologies to define such values. In Section 3.2, we detail how these values can be defined.

Example 1.2.1: A sequence of operations for the 2-input AND (AND2),  $x_0x_1$ , using two auxiliary variables  $y_0$  and  $y_1$ , is given in Table 1.2.1.

Table 1.2.1 – Evaluation of AND2 in RSD-IMP logic.

|    | Instruction           | Result                                                       |

|----|-----------------------|--------------------------------------------------------------|

| 1. | $y_0 = 0, y_1 = 0$    |                                                              |

| 2. | $x_0 \rightarrow y_0$ | $y_0 = \overline{x_0}$                                       |

| 3. | $x_1 \rightarrow y_0$ | $y_0 = \overline{x_0} + \overline{x_1}$                      |

| 4. | $y_0 \rightarrow y_1$ | $y_1 = \overline{\overline{x_0} + \overline{x_1}} = x_0 x_1$ |

Source: (BORGHETTI, 2010).

# 1.3 CHALLENGES AND MOTIVATION

In RSD-IMP logic, there can have different sequence of instructions for the same target function. The quality of the solution can be measured in terms of number of instructions and number of RSDs required. For instance, the solution for AND2 operation presented in Table 1.2.1 takes four instructions and four RSDs.

Example 1.2.2: In this example, we compare different solutions for the 2-input OR (OR2),  $x_0 + x_1$ . The first solution, shown in Table 1.2.2, comprises six cycles and uses five RSDs. By adding a RSD  $y_2$ , the reset operation in cycle 4 can be skipped. The resulting sequence of operations becomes as shown in Table 1.2.3.

Table 1.2.2 – Evaluation of OR2 in six cycles using four RSDs.

| <u>uere 1.2.2</u> | Diamation of Ott2 in t | an ejeles asing four table |

|-------------------|------------------------|----------------------------|

|                   | Instruction            | Result                     |

| 1.                | $y_0 = 0, y_1 = 0$     |                            |

| 2.                | $x_0 \rightarrow y_0$  | $y_0 = \overline{x_0}$     |

| 3.                | $y_0 \rightarrow y_1$  | $y_1 = x_0$                |

| 4.                | $y_0 = 0$              | $y_0 = 0$                  |

| 5.                | $x_1 \rightarrow y_0$  | $y_0 = x_1$                |

| 6.                | $y_0 \rightarrow y_1$  | $y_1 = x_0 + x_1$          |

Source: The author.

Table 1.2.3 – Evaluation of OR2 in five cycles using five RSDs.

|    | Instruction                 | Result                 |

|----|-----------------------------|------------------------|

| 1. | $y_0 = 0, y_1 = 0, y_2 = 0$ |                        |

| 2. | $x_0 \rightarrow y_0$       | $y_0 = \overline{x_0}$ |

| 3. | $y_0 \rightarrow y_1$       | $y_1 = x_0$            |

| 5. | $x_1 \rightarrow y_2$       | $y_2 = x_1$            |

| 6. | $y_2 \rightarrow y_1$       | $y_1 = x_0 + x_1$      |

Source: The author.

Both solutions, shown in Table 1.2.2 and in Table 1.2.3, use only reset and single-input operations. The solution can be improved by using multi-input implications, as shown in Table 1.2.4. The solution shown in Table 1.2.4 takes only three cycles and uses four RSDs.

Table 1.2.4 – Evaluation of OR2 in three cycles using four RSD.

|    | Instruction           | Result                                 |

|----|-----------------------|----------------------------------------|

| 1. | $y_0 = 0, y_1 = 0$    |                                        |

| 2. | $(x_0 + x_1) \to y_0$ | $y_0 = \overline{x_0}  \overline{x_1}$ |

| 3. | $y_0 \rightarrow y_1$ | $y_1 = x_0 + x_1$                      |

Source: The author.

It has been shown that for any n-input Boolean function, there is a sequence of operations that requires n + 2 RSD (LEHTONEN, 2010). In this sense, three logic synthesis challenges, regarding RSD-IMP logic, are the following:

- 1) Find the smallest sequence of operations that can be computed with n + 2 RSD.

- 2) Find the smallest sequence of operations that require at most n + k RSD, where  $k \ge 2$  is an arbitrary value.

- 3) Find the smallest sequence of operations with no upper bound on the number of RSD used.

Most works in the literature targeting RSD-IMP logic focuses on the first challenge (POIKONEN, 2012), (TEODOROVIC, 2013), (RAGHUVANSHI, 2014). In (LEHTONEN, 2010), it is proposed the use of recursive Boolean forms (RBF). A RBF can be defined as follows:

$$f = f_0 + \overline{(f_1 + \overline{(f_2 + \dots + \overline{(f_{\phi-2} + \overline{f_{\phi-1}})})})}$$

(1.2.3)

where each  $f_i$  is a negative unate SOP and  $\phi$  is the number of levels in f. The interest on RBF arises because such a kind of forms can always be directly translated to a sequence of instructions that can be evaluated with n+2 RSD. Moreover, each cube in the RBF corresponds to an instruction. Therefore, methods to optimize RBF have been proposed. The methods described in (RAGHUVANSHI, 2014) and in (POIKONEN, 2012) are based on finding a cover for the function through Karnaugh maps. In (TEODOROVIC, 2013), a graph based method, where each vertex is a minterm, is presented. Such a method is similar to the

cover based methods. All these approaches work over representations that always use  $2^n$  elements for an n-input Boolean function, being restricted to somewhat simple functions. In (WANG, 2016), a genetic algorithm to optimize RBF is proposed.

The works discussed in (CHAKRABORTI, 2014) and in (CHATTOPADHYAY, 2011), propose a BDD-based and an AIG-based method, respectively. In both cases, each node of the graph is directly transformed into a sequence of instructions. In order to evaluate only once the nodes with fanout greater than one, more than n + 2 RSD are used.

#### 1.4 THESIS PROPOSAL

This thesis focuses on defining and synthesizing classes of Boolean expressions such that: (1) the size of the expression is directly related to the number of instructions; and (2) the number of required RSD can be derived in linear time with respect to the size of the expression. From such expressions, we proposes logic synthesis methods for RSD-IMP logic considering the challenges previously described.

We consider RBF as the base form and then generalize RBF to other forms. For each new form, we investigate how this form can be transformed into a sequence of instructions, as well as the resulting number of instructions and RSD. Then, we derive algorithms to synthesize such forms while optimizing the resulting sequence of instructions.

We begin by developing algorithms related to the first challenge, *i.e.*, to find the smallest sequence of operations that can be computed with n + 2 RSDs. Our first contribution is related to the synthesis of RBF. In order to improve the scalability of RBF synthesis methods, we develop a RBF synthesis method that can be applied over different representation such as sum-of-products and BDD. Therefore, we discuss how RBF can be optimized by removing redundant cubes.

Our second contribution related to the first challenge is the proposal of sum-of-RBF (SRBF). By generalizing RBF into SRBF, we are able to reduce the number of instructions while respecting the lower bound of n + 2 RSDs. We also propose a SOP-based algorithm for the synthesis of SRBF.

In order to exploit an arbitrary number n+k of RSDs, where  $k \ge 2$ , related to the second challenge (*i.e.*, to find the smallest sequence of operations that require at most n+k RSD), we propose the use of factored SRBF (FSRBF). More specifically, we focus on single-cube FSRBF (SC-FSBRF). We show that the number of levels in the SC-FSRBF is directly related to the number of RSDs required to evaluate the resulting sequence of operations. The SOP-based algorithm for SRBF synthesis is expanded to SC-FSRBF.

Regarding the third challenge, i.e., to find the smallest sequence of operations with no upper bound on the number of RSDs applied, we propose a SOP-based approach to minimize the sequence of instructions when there is no maximum bound in the number of RSDs. This last approach takes into account the benefits of having all variables in both direct and complementary forms while considers the extra cost to obtain the complement of a variable. This problem has been addressed in (XIE, 2017), which evaluates any Boolean function in seven cycles. In this sense, we obtain a different trade-off between the number of RSDs and the number of instructions.

We finish our contributions by discussing the logic design of binary adders. In contrast to previous contributions, the design of binary adders takes into account the matrix structure of the RSD memory. The sequence of instructions to implement a full-adder (FA) circuit is obtained from a SRBF. Thus, we explore adders designs based on the proposed FA.

#### 1.5 TEXT ORGANIZATION

In Chapter 2, we provide a background on logic synthesis field. We discuss terms and definitions useful for the overall understanding of the thesis.

Chapter 3 focuses on RSD and RSD-IMP logic. Section 3.1 describes the basic physical behavior of RSD. Section 3.2 details the behavior of RSD-IMP logic, and Section 3.3 discusses existing logic synthesis methods for RSD-IMP logic.

Chapter 4 focuses on recursive Boolean forms (RBF). RBFs are the most studied forms for RSD-IMP because these ones can always be translated into a sequence of instructions computable with n + 2 RSDs in linear time with respect to the size of the RBF. We propose a more efficient method to evaluate RBF as well as two algorithms to synthesize RBF. The first algorithm provides optimal RBF that is well suited for simple functions with at most four inputs. The second algorithm aims to handle more complex functions at the cost of suboptimal solutions. The proposed methods show significant improvements over existing approaches.

In Chapter 5, we propose the concept of sum-of-RBF (SRBF). We demonstrate that SRBF can be transformed into a sequence of instructions that requires n + 2 RSDs. In Section 5.1, we present a SOP based algorithm to synthesize SRBF. In Section 5.2 we propose the use of factored SRBF (FSRBF) which can benefit from more than n + 2 RSD.

In Chapter 6, we present two other contributions. In Section 6.1, we evaluate the benefits of having the variables available in both polarities as a method to reduce the number of cycles (instructions) in RSD-IMP logic. In Section 6.2, we propose a novel logic design for

a binary adder in RSD-IMP logic. The basic full-adder block is obtained from the developed methods. Then, we propose new implementations of binary adders that take into account different trade-offs between the number of instructions and the number of RSDs. Finally, Chapter 7 presents the conclusions and future works.

#### 2 LOGIC SYNTHESIS BACKGROUND

This chapter presents some fundamentals on different concepts that are related to this work. Some helpful references for such a background are (BRAYTON, 1982), (BRAYTON, 1984) and (DE MICHELLI, 1994).

#### 2.1 DEFINITIONS

An *n*-input Boolean function F(X) defined over the variable set X with  $m \ge 1$  outputs is a relation  $F(X) = \{0,1\}^n \mapsto \{0,1,-\}^m$ , where '-' denotes *don't care*. When m = 1, the function is a single output function. For m larger than 1, the function corresponds to a multi-output function. Constant functions false and true are denoted by 0 and 1, respectively. The on-set of F is denoted by  $F_{ON}$  and consists of all input assignments  $\mathbf{x}$  such that  $F(\mathbf{x}) = 1$ . Similarly, the off-set of  $F(F_{OFF})$  and the *don't care* set of  $F(F_{DC})$  are all input assignments  $\mathbf{x}$  for which  $F(\mathbf{x}) = 0$  and  $F(\mathbf{x}) = -$ , respectively. If  $F_{DC} = \{\}$ , F corresponds to a completely specified function (CSF). Otherwise, F is an incompletely specified function (ISF). A given function F contains (or dominates) a function F if  $F_{DC} = \{\}$ , F corresponds to  $F_{DC} = \{\}$ ,  $F_{D$

A cofactor of F with respect to a variable  $x_i$  is a function obtained by assigning  $x_i$  to 1 or 0 in F. If  $x_i = 0$ , we obtain the negative cofactor. If  $x_i = 1$ , we obtain the positive cofactor. If the negative and positive cofactors of F with respect to  $x_i$  are equal, then  $x_i$  corresponds to a *don't care* variable. In other words, the value of F does not depend on  $x_i$ . The support of a given function F is the set of variables that are not *don't care* in F.

A Boolean function F is said to be positive unate on a variable  $x_i$  if  $F(x_1,...,I,...,x_n) \ge F(x_1,...,0,...,x_n)$  for all possible input assignments. In other words, switching  $x_i$  from 0 to 1 cannot make F change from 1 to 0. A Boolean function F is said to be negative unate on variable  $x_i$  if  $F(x_1,...,0,...,x_n) \ge F(x_1,...,1,...,x_n)$  for all possible input assignments. A variable in the support of F that is neither positive unate nor negative unate is a binate variable. A function F is unate if all of its variables are unate. A function F is a positive (negative) unate function if all its variables are positive (negative) unate. If there is at least one binate variable in the support of F, then F is a binate function.

In this work,  $\cdot$ , +,  $\overline{bar}$  and  $\rightarrow$  denote logical conjunction (AND), disjunction (OR), complementation (NOT) and material implication (IMP) operations. In several cases the '·' operator is just omitted for better text format so that  $(x_1 \cdot x_2) = (x_1x_2)$ .

A literal is a variable (positive literal) or a complemented variable (negative literal). The conjunction of literals is a cube. A cube comprising only positive literals is a positive cubes, whereas a cube comprising only negative literals is a negative cube and a cube

comprising both positive and negative literals is a binate cube. A minterm is a cube comprising all input variables of F. A cube c is an implicant cube (or simply implicant) of F if c=1 implies  $F \neq 0$ . An implicant c is an implicant prime (or simply a prime) of F if removing any literal from c produces a cube that is not an implicant. Equivalently, a prime is a maximal implicant. A prime is an essential prime if there is at least one minterm that is only covered by this prime.

## 2.2 BOOLEAN FUNCTION REPRESENTATION AND OPTIMIZATIONS

## 2.2.1Truth Table and Karnaugh Map

A truth table is the most straightforward way to represent a Boolean function where the values for all possible input assignments  $\mathbf{x}$  are displayed. A Karnaugh map, in turn, is similar to a truth table with the difference that the data is displayed over a matrix. The main problem of both representations is related to scalability. Both truth tables and Karnaugh map always require  $2^n$  positions, regardless of the function itself. A truth table can be represented as a hexadecimal integer where the most significant bit of such an integer is defined by minterm  $x_0x_1 \dots x_{n-1}$ .

## 2.2.2 Sum-of-products (and two-level minimization)

A disjunction of implicant cubes of F corresponds to a sum-of-products (SOP) f for F such that  $F_{ON} \subseteq f_{ON} \subseteq (F_{ON} \cup F_{DC})$ . The set of cubes in f represents a cover f for f. If removing any element from f leads to  $f_{ON} \not\subseteq f_{ON}$  then f is an irredundant cover. If all cubes in f are prime, then f is a prime cover. A prime and irredundant cover is an irredundant sum-of-products (ISOP). In other words, if any cube or literal is removed from f, then f is not a cover for f, then f is an ISOP. The cardinality of a SOP is the number of cubes in it. A minimum SOP presents the smallest cardinality among all covers for f. A minimal SOP is not a proper superset of any other SOP. Notice that a SOP always represents a CSF. If the target function f is an ISF, a SOP covering f represents a CSF f2 such that f3 implies f4 and f5 and f6 implies f6 and f7 implies f8. A function f8 can also be written in a product-of-sums (POS) form. Similarly to an ISOP, a POS is irredundant (IPOS) if any sum and any literal can be removed from the expression without modifying the target function.

A usual question is to determine which of the SOP or POS expressions is the most compact for representing a given function. Equivalently, the question could be which of F and  $\overline{F}$  have the smallest SOP representation. Notice that, if there is a POS with k sums representing a given function F, then there is a SOP representation for  $\overline{F}$  containing k cubes,

through De Morgan's theorem. The decision to represent F or  $\overline{F}$  is important because, if the optimal SOP for F has k cubes with m literals each, then the optimal SOP for  $\overline{F}$  can have up to  $m^k$  cubes (SASAO, 2001). However, given a SOP f, there is not a simple way to decide whether the SOP  $\overline{f}$  comprises more or less cubes than f.

Even though the number of cubes in the list grows theoretically as  $2^n$ , in practice this number is much smaller. For instance, an n-input AND function requires only one cube with n literals. In this sense, a SOP representation for a 50-input AND is perfectly reasonable, whereas a truth table (or Karnaugh map) representation is unfeasible.

Two-level minimization is the process of optimizing a SOP expression. The goal is to obtain a SOP comprising the smallest number of cubes (*i.e.*, a minimum SOP). There are both exact and heuristic minimization procedures. In this work, we are mostly interested in the heuristic approaches because these ones present a good trade-off between the solution quality and the execution time. A minimum solution comprises the smallest number of cubes among all possible solutions. Notice that a minimal solution is not a proper superset of any other solution. In other words, a minimal solution cannot be improved by simply removing a literal or a cube from it.

Typical tasks in heuristic two level minimization algorithms are the expansion and reduction of cubes. The goal of a cube expansion is to transform implicants into primes. Moreover, as an implicant is expanded it may cover other implicants that may be discarded. During the expansion process it is necessary to check if the expanded cube still represents an implicant. The cube reduction transforms primes into implicants. As a cube is reduced, this cube can become dominated by another cube and so be removed from the SOP. During a cube reduction, it is necessary to check if the resulting SOP still covers the target function. Typically, two-level minimizers usually perform a loop based on expansion and reduction processes. The loop execution stops when the solution cannot be no more improved.

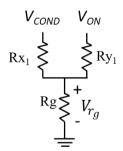

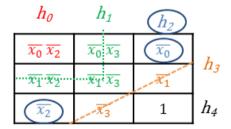

To illustrate the process of two-level minimization, consider a function F described by the Karnaugh map shown in Fig. 2.1(a). Assume an initial cover for the function corresponding to the highlighted cubes being written as follows:

$$f^* = \overline{x_0} \, \overline{x_2} + \overline{x_0} \, x_1 + x_0 x_2 + x_0 \, \overline{x_1} \tag{2.2.1}$$

Notice that (2.2.1) comprises only primes because no cube from it can be expanded without modifying the described function. Moreover, no prime can be removed from (2.2.1)

without modifying the function. One can obtain another solution by reducing cube  $\overline{x_0}x_1$  to  $\overline{x_0}x_1x_2$ , as illustrate in Fig. 2.1(b). Furthermore, it can be verified that replacing  $\overline{x_0}x_1$  by  $\overline{x_0}x_1x_2$  leads to a valid solution because  $\overline{x_0}x_1\overline{x_2}$  is dominated by  $\overline{x_0}$   $\overline{x_2}$ . The new cover can be written as follows:

$$f^* = \overline{x_0} \, \overline{x_2} + \overline{x_0} \, x_1 x_2 + x_0 x_2 + x_0 \, \overline{x_1}$$

(2.2.2)

Even though (2.2.2) comprises one more literal than (2.2.1), the cardinality of both coverings is the same. The next step is to expand cube  $\overline{x_0}x_1 x_2$  to cube  $x_1 x_2$ , as illustrate in Fig. 2.1(c), giving the following expression:

$$f^* = \overline{x_0} \, \overline{x_2} + x_1 x_2 + x_0 x_2 + x_0 \, \overline{x_1} \tag{2.2.3}$$

In (2.2.3), the cube  $x_0x_2$  is redundant and so can be removed. After this removal, the covering comprises one less cube than the original solution (2.2.1). The final covering is illustrated in Fig. 2.1(d), and is written as follows:

$$f^* = \overline{x_0} \, \overline{x_2} + x_1 x_2 + x_0 \, \overline{x_1} \tag{2.2.4}$$

Figure 2.1 – Different coverings  $f^* = \overline{x_0} \ \overline{x_2} + x_1 x_2 + x_0 \ \overline{x_1}$ : (a) initial, (b) after reduction of cube  $\overline{x_0} x_1$  to  $\overline{x_0} x_1 x_2$ , (c) after expanding  $\overline{x_0} x_1 x_2$  to  $x_1 x_2$ , and (d) final minimum covering.

| $x_2x_3$ | 00  | 01 | 11 | 10 | $x_0x_1$ $x_2x_3$    | 00  | 01 | 11      |   |

|----------|-----|----|----|----|----------------------|-----|----|---------|---|

|          | 1   | 1  | 0  | 0  | 00                   | 1   | 1  | 0       | I |

|          | 1   | 1  | 1  | 1  | 01                   | 1   | 1  | 1       |   |

|          | 0   | 0  | 1  | 1  | 11                   | 0   | 0  | 1       |   |

| )        | 1   | 1  | 1  | 1  | 10                   | 1   | 1  | 1       |   |

|          | (a) |    |    |    |                      | (b) |    |         |   |

| $x_2x_3$ |     |    |    |    | <b>16.16</b>         |     |    |         |   |

| -11      | 00  | 01 | 11 | 10 | $x_0x_1$ $x_2x_3$    | 00  | 01 | 11      |   |

|          | 00  | 01 | 0  | 0  | $x_0x_1$ $x_2x_3$ 00 | 00  | 01 | 11<br>0 |   |

| 00       |     |    |    |    | $x_0x_1$             |     |    |         |   |

| 00       | 1   | 1  | 0  | 0  | 00                   | 1   | 1  | 0       |   |

| 00       | 1   | 1  | 0  | 0  | 00 01                | 1   | 1  | 0       |   |

Source: The author.

## 2.2.2.1 SOP of Unate Functions

Unate functions are very interesting for two level minimizations because if F is a unate function, then all primes are essential and the ISOP is unique. In other words, the ISOP comprises all primes of F and only the primes of F. Therefore, given a unate covering for a unate function F, the ISOP for F can be obtained by simply removing cubes that are not prime. This process is known as single cube containment. For instance, consider a function defined by the following expression:

$$f^* = x_1 x_2 + \overline{x_3} x_4 + x_1 x_2 \overline{x_3}$$

(2.2.5)

In (2.2.5),  $x_1$  and  $x_2$  are positive unate variables whereas  $x_3$  and  $x_4$  are negative unate variables. It follows that F is a unate function. To verify if (2.2.5) is an ISOP, we check for cubes that are redundant. In this case, cube  $x_1x_2\overline{x_3}$  is redundant because it is covered by  $x_1x_2$ . Therefore,  $x_1x_2\overline{x_3}$  can be removed, leading to the following unique ISOP:

$$f^* = x_1 x_2 + \overline{x_3} x_4 \tag{2.2.6}$$

#### 2.2.3 Binary Decision Diagram

Boolean functions can also be represented through binary decision diagram (BDD) (LEE,1959), (AKERS, 1978). A BDD is a rooted, directed, acyclic graph. A node of a BDD can be either a decision node or a terminal node. Each decision node represents a Boolean variable and each terminal node is either 1 or 0. Each non-terminal node has a high and a low child. A BDD node is redundant if the low and high children are the same or if there is another node that represents the same function. Moreover, a BDD is reduced (RBDD) if there are no redundant nodes. Furthermore, a BDD is ordered (OBDD) if, for all pairs of variables  $x_i$  and  $x_j$ ,  $x_i$  and  $x_j$  appear in the same order for any path comprising both  $x_i$  and  $x_j$ . A reduced and ordered BDD (ROBDD) is a canonical representation of the corresponding Boolean function (BRYANT, 1986).

#### 2.2.4 Factored forms, factoring and division

A factored form can be recursively defined as a literal (*i.e.*,  $x_i$  or  $\overline{x_i}$ ), as well as a conjunction of factored forms or a disjunction of factored forms (BRAYTON, 1982). In other words, a factored form is a Boolean expression where only literals can be complemented.

Hence,  $x_1(\overline{x_2} + x_3)$  is a factored form whereas  $x_1(\overline{x_2} + x_3)$  is not. Similarly,  $(\overline{x_1} + \overline{x_2})$  is a factored form whereas  $\overline{x_1x_2}$  is not, both representing the 2-input NAND.

Factoring is the process of obtaining a factored form representing a Boolean function. The main goal of factoring algorithms is to reduce the number of literals in the resulting factored form. Factoring algorithms can be classified as algebraic or Boolean. An algebraic factoring algorithm considers Boolean variables as integers and applies standard algebra. The main limitation of algebraic factoring is that the notion of complement does not exist. Therefore, literals  $x_0$  and  $\overline{x_0}$  are treated as independent variables. Boolean factoring uses properties that are specific to Boolean algebra. Such properties include the following relations:  $x_0\overline{x_0} = 0$ ,  $x_0 + \overline{x_0} = 1$  and  $x_0 + x_0x_1 = x_0$ .

Boolean methods tend to yield better results but are usually more complex than algebraic methods. To illustrate the differences between these methods, we take a function F written as follows:

$$f^* = x_1 x_2 + x_2 x_3 + \overline{x_1} x_3 \tag{2.2.7}$$

An algebraic factoring method can obtain one of the following expressions:

$$f^* = x_2(x_1 + x_3) + \overline{x_1}x_3 \tag{2.2.8}$$

$$f^* = x_1 x_2 + x_3 (x_2 + \overline{x_1}) \tag{2.2.9}$$

Both (2.2.8) and (2.2.9) comprise five literals. A Boolean factoring method, on the other hand, may return the following expression:

$$f^* = (x_1 + x_3)(x_2 + \overline{x_1}) \tag{2.2.10}$$

which comprises four literals. Notice that, in order to obtain (2.2.10), the property  $x_0\overline{x_0} = 0$  is applied. Therefore, an algebraic method is not able to obtain (2.2.10) as solution.

The factoring process can also be understood as a division operation over a given SOP f. If f is divided by a SOP d, then f is written as follows:

$$f = qd + r \tag{2.2.11}$$

where q, d and r are SOP. q is the quotient, d is the divider and r is the remainder. If d is a cube, then d is a single cube divisor. Otherwise, d is a multiple cubes divisor. If d is a cube and r is empty, then d is a factor of f. If f has no factors, then f is a cube-free expression. If d is a cube and q is a cube-free expression, then d is a co-kernel of f and f is a kernel of f (BRAYTON, 1982).

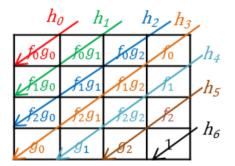

Obtaining single cube divisors can be done using a matrix structure where each column is a literal, and each row is a cube in the input SOP. If cube  $c_i$  comprises the literal  $x_j$ , a '1' is placed on the corresponding matrix position. A rectangle in the matrix is a set of columns and rows such that all matrix entries corresponding to the intersections of these columns and rows contain a '1'. Neither the columns nor the rows have to be continuous. The weight of a rectangle is the improvement obtained (usually measured in terms of reduction on the number of literals) by selecting that rectangle to perform the division operation. A prime rectangle is a rectangle for which the weight can be increased by adding a row or a column. It has been shown that the good divisors for an expression can be identified from the prime rectangles (RUDELL, 1989). For instance, consider an expression f, as follows:

$$f = x_0 x_1 x_2 x_3 + x_0 x_1 x_4 + x_3 x_6 x_7 + x_3 x_6 x_8$$

(2.2.12)

The resulting matrix is shown in Table 2.1. There are two prime rectangles in the Table 2.1. The first is given by the intersections of columns  $\{x_0, x_1\}$  and lines  $\{x_0x_1x_2x_3, x_0x_1x_4\}$ . The second is given by the intersection of  $\{x_3, x_6\}$  and lines  $\{x_3x_6x_7, x_3x_6x_8\}$ . Hence, the single cube divisors for (2.2.12) are  $x_0x_1$  and  $x_3x_6$ . The resulting expression is as follows:

$$f = x_0 x_1 (x_2 x_3 + x_4) + x_3 x_6 (x_7 + x_8)$$

(2.2.13)

Table 2.1 – Matrix for single cube divisor extraction for (2.2.12).

|                | $x_0$ | $x_1$ | $x_2$ | $x_3$ | $x_4$ | $x_5$ | <i>x</i> <sub>6</sub> | <i>x</i> <sub>7</sub> | <i>x</i> <sub>8</sub> |

|----------------|-------|-------|-------|-------|-------|-------|-----------------------|-----------------------|-----------------------|

| $x_0x_1x_2x_3$ | 1     | 1     | 1     | 1     |       |       |                       |                       |                       |

| $x_0x_1x_4$    | 1     | 1     |       |       | 1     | 1     |                       |                       |                       |

| $x_3 x_6 x_7$  |       |       |       | 1     |       |       | 1                     | 1                     |                       |

| $x_3 x_6 x_8$  |       |       |       | 1     |       |       | 1                     |                       | 1                     |

Source: The author.

Identifying good divisors using this matrix structure resembles a covering algorithm over a Karnaugh map in the sense that prime rectangles are analogous to prime implicants. However, the prime rectangle size does not need to be a power of 2 and the matrix positions do not need to be adjacent.

The process for identifying good multiple cubes divisors uses the same matrix structure. However, the columns and rows have different meanings. Each column is a cube in a kernel of f while each row is a co-kernel of f. The candidates co-kernels to be adopted in the division process can be obtained from the intersection of the pairs of cubes in f. This process is illustrated in the following:

$$f = x_0 x_1 x_2 x_3 + x_0 x_1 x_4 + x_0 x_1 x_5 + x_2 x_3 x_7 + x_4 x_7$$

(2.2.14)

The first pair of cubes  $\{x_0x_1x_2x_3, x_0x_1x_4\}$  leads to the co-kernel  $x_0x_1$  and the kernel  $x_2x_3 + x_4$ . Hence, there is a line  $x_0x_1$  and two columns  $x_2x_3$  and  $x_4$  in the matrix. On the other hand, there is no intersection of literals regarding cubes  $x_0x_1x_2x_3$  and  $x_4x_7$ . Therefore, this pair does not generate any candidate divisors. The resulting matrix is shown in Table 2.2. A prime rectangle consists of the intersection of columns  $\{x_2x_3, x_4\}$  and rows  $\{x_0x_1, x_7\}$ . When f is divided by  $x_2x_3 + x_4$ , we obtain the following expression:

$$f = (x_2 x_3 + x_4)(x_0 x_1 + x_7) + x_0 x_1 x_5$$

(2.2.15)

Table 2.2 – Matrix for multiple cubes divisor extraction for (2.2.14).

|          | $x_2x_3$ | $x_4$ | <i>x</i> <sub>5</sub> | $x_0x_1$ | <i>x</i> <sub>7</sub> |

|----------|----------|-------|-----------------------|----------|-----------------------|

| $x_0x_1$ | 1        | 1     | 1                     |          |                       |

| $x_2x_3$ |          |       |                       | 1        | 1                     |

| $x_4$    |          |       |                       | 1        | 1                     |

| $x_7$    | 1        | 1     |                       |          |                       |

Source: The author.

Notice that, even though there are two prime rectangles presented in Table 2.2, only one of them is selected because both rectangles lead to the same cubes. The rectangles are transpositions of each other. However, if rectangles overlay, there are cases where it can be useful to allow redundancies. In order to illustrate possible benefits of redundancy, consider the matrix shown in Table 2.3.

Table 2.3 – Matrix to exemplify the need for redundancy.

|       | <i>x</i> <sub>3</sub> | $x_4$ | $x_5$ | <i>x</i> <sub>6</sub> |

|-------|-----------------------|-------|-------|-----------------------|

| $x_0$ | 1                     | 1     | 1     | 1                     |

| $x_1$ | 1                     | 1     | 1     |                       |

| $x_2$ | 1                     |       |       | 1                     |

Source: The author.

The first prime rectangle is given by the intersection of lines  $\{x_0, x_1\}$  and columns  $\{x_3, x_4, x_5\}$ . The second prime rectangle is given by the intersection of lines  $\{x_0, x_2\}$  and columns  $\{x_3, x_6\}$ . Hence, the rectangles overlap. If redundancy is not allowed, then only one of the rectangles can be selected. Let the first rectangle be selected, then the resulting expression contains 10 literals, as follows:

$$f = (x_0 + x_1)(x_3 + x_4 + x_5) + x_6(x_0 + x_2) + x_2x_6$$

(2.2.16)

On the other hand, if redundancy is allowed, we obtain an expression with nine literals, as follows:

$$f = (x_0 + x_1)(x_3 + x_4 + x_5) + (x_3 + x_6)(x_0 + x_2)$$

(2.2.17)

Even though cube  $x_0x_3$  appears in both terms of (2.2.17), the resulting factored form comprises one less literal than one represented by (2.2.16).

One limitation of such matrix based method is that the number of rows and columns in the matrix are quadratic functions on the number of cubes. Different works have proposed methods to reduce the set of candidate divisors. One criteria applied is to set a maximum bound on the number of literals that a divisor can have (MODI, 2004).

#### 2.3 FUNCTIONAL COMPOSITION

Functional composition (FC) is a bottom-up approach to logic synthesis (MARTINS, 2012). The main idea of FC is to obtain expressions for complex functions by combining known solutions for simpler functions. For this reason, a set of basic functions for which optimal solutions are known must be defined. FC was proposed to perform factoring of Boolean functions and has also been applied to different emerging logic paradigms that are not necessarily based on AND and OR operations (MARTINS, 2014), (MARTINS, 2015), (NEUTZLING, 2014).

When FC is used to perform factoring, the basic functions correspond to the literals and complemented ones. These basic functions are combined through AND and OR operators, yielding functions for which the optimal factored form comprises two literals. Since expressions with m literals are created before expressions with m+1 literals, the first expression found for a function is also the optimal solution. In order to check whether an expression in the first solution for a function, a functional representation, such as a truth table, is stored together with each created expression. To illustrate the idea of FC, we consider the synthesis of a three input function given by the following SOP:

$$f = x_0 x_1 + x_0 x_2 \tag{2.3.1}$$

The truth table for (2.3.1) is shown in Table 2.4. The equivalent integer is E0.

Table 2.4 – Truth table for  $f = x_0x_1 + x_0x_2$ . f  $x_0$  $x_1$  $x_2$

Source: The author.

Since F is a three input function, the set of basic functions is as shown in Table 2.5. None of the expressions in Table 2.5 is a solution to (2.3.1). Therefore, we associate all pairs of expressions in Table 2.5 through AND and OR operators. The resulting expressions are shown in Table 2.6 together with the respective integer representation of the truth table.

Since none of the expressions in Table 2.6 represents the target function, expressions with three literals have to be generated. For this, each expression in Table 2.5 is combined with an expression in Table 2.6 through AND and OR operations. When expressions  $x_0$  and  $(x_1 + x_2)$  are combined through an AND operation, we obtain the following expression:

$$f = x_0(x_1 + x_2) \tag{2.3.2}$$

The truth table of (2.3.2) is E0. Therefore, (2.3.2) is an expression for the target function. Since (2.3.2) is the first solution found, it is also an optimal solution.

The FC process can be improved by considering properties of Boolean functions. In particular, let  $F_1$  and  $F_2$  be two functions such that  $F_1 \subseteq F$  and  $F_2 \subseteq F$ , then  $(F_1F_2) \subseteq F$ . Therefore, performing an AND operation between two functions that are dominated by F does not help the FC to approach to a solution. A similar argument is valid for OR operation. In the previous example, function  $x_0$  dominates the target function. Hence, only AND operations using  $x_0$  are useful.

Table 2.5 – Basic functions for FC using three input variables.

| $\overline{x_0}$   | $x_1$ | $x_2$ | <i>f</i> 1       | f2    | f2               | <i>f</i> 3 | f4               | <i>f</i> 5 |

|--------------------|-------|-------|------------------|-------|------------------|------------|------------------|------------|

| 0                  | 0     | 0     | 0                | 1     | 0                | 1          | 0                | 1          |

| 0                  | 0     | 1     | 0                | 1     | 0                | 1          | 1                | 0          |

| 0                  | 1     | 0     | 0                | 1     | 1                | 0          | 0                | 1          |

| 0                  | 1     | 1     | 0                | 1     | 1                | 0          | 1                | 0          |

| 1                  | 0     | 0     | 1                | 0     | 0                | 1          | 0                | 1          |

| 1                  | 0     | 1     | 1                | 0     | 0                | 1          | 1                | 0          |

| 1                  | 1     | 0     | 1                | 0     | 1                | 0          | 0                | 1          |

| 1                  | 1     | 1     | 1                | 0     | 1                | 0          | 1                | 0          |

| Integer            |       | F0    | 0F               | CC    | 33               | AA         | 55               |            |

| Boolean expression |       | $x_0$ | $\overline{x_0}$ | $x_1$ | $\overline{x_1}$ | $x_2$      | $\overline{x_2}$ |            |

Source: The author.

| Table $2.6 - Ex$ | pressions with | two literals ar | nd the respect | tive truth table re | epresented as integer. |

|------------------|----------------|-----------------|----------------|---------------------|------------------------|

|                  |                |                 |                |                     |                        |

| Expression                        | Truth table | Expression                        | Truth table |

|-----------------------------------|-------------|-----------------------------------|-------------|

| $x_0 + x_1$                       | FC          | $x_0x_2$                          | A0          |

| $\overline{x_0 + \overline{x_1}}$ | F3          | $x_0\overline{x_2}$               | 50          |

| $\overline{x_0} + x_1$            | CF          | $\overline{x_0}x_2$               | 0A          |

| $\overline{x_0} + \overline{x_1}$ | F3          | $\overline{x_0} \overline{x_2}$   | 05          |

| $x_0x_1$                          | C0          | $x_1 + x_2$                       | EE          |

| $\overline{x_0}\overline{x_1}$    | 30          | $x_1 + \overline{x_2}$            | DD          |

| $\overline{x_0}x_1$               | 0C          | $\overline{x_1} + x_2$            | BB          |

| $\overline{x_0} \overline{x_1}$   | 03          | $\overline{x_1} + \overline{x_2}$ | 77          |

| $x_0 + x_2$                       | FA          | $x_1x_2$                          | 88          |

| $x_0 + \overline{x_2}$            | F5          | $x_1\overline{x_2}$               | 44          |

| $\overline{x_0} + x_2$            | AF          | $\overline{x_1}x_2$               | 22          |

| $\overline{x_0} + \overline{x_2}$ | 5F          | $\overline{x_1} \overline{x_2}$   | 11          |

| ·                                 |             | <br>                              |             |

### 2.4 PROBABILITY OF BOOLEAN FUNCTIONS