# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

# ALAN CARLOS JUNIOR ROSSETTO

# Modeling and Simulation of Self-heating Effects in *p*-type MOS Transistors

Thesis presented in partial fulfillment of the requirements for the degree of PhD in Microelectronics

Advisor: Prof. Dr.-Ing. Gilson Inacio Wirth

Porto Alegre November 2018

# CIP — CATALOGING-IN-PUBLICATION

Rossetto, Alan Carlos Junior

Modeling and Simulation of Self-heating Effects in *p*-type MOS Transistors / Alan Carlos Junior Rossetto. – Porto Alegre: PGMICRO da UFRGS, 2018.

149 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR-RS, 2018. Advisor: Gilson Inacio Wirth.

1. CMOS. 2. Charge Traps. 3. Monte Carlo. 4. MOSFET. 5. Reliability. 6. Self-heating. I. Inacio Wirth, Gilson. II. Título.

# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenador do PGMICRO: Prof. Fernanda Gusmão de Lima Kastensmidt Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

### ACKNOWLEDGMENTS

At the completion of such a long journey, it may sometimes be difficult to identify each person who has contributed, either directly or indirectly, to the quality and content of my doctoral work. I will attempt to detail my gratitude herein, and apologize for any omissions.

First and foremost, I would like to thank my two thesis advisors and friends, Prof. Dr.-Ing. Gilson I. Wirth and Prof. Dr. Dragica Vasileska. As a CMOS reliability specialist, Prof. Gilson provided the necessary guidance and background I needed to go forward in a totally new research field to myself. Here, I also acknowledge him for supervising my research activities over the last 7 years, starting when I was an undergraduate student, through the master's degree and the completion of the current thesis.

The notorious expertise of Prof. Vasileska in the field of computational electronics also represented a remarkable improvement in the research reported here. Her guidance, patience, hospitality, friendship, and continuous support during the year I spent with her research group at Arizona State University are certainly something I will never ever forget. I also acknowledge the assistance and support of Dr. Gokul Kannan, M.Sc. Pradyumna Muralidharan, M.Sc. Robin Daugherty, and M.Sc. Suleman Qazi during my stay in Tempe, AZ.

I am also deeply in debt to my colleagues at Laprot/UFRGS. Dr. Vinicius Camargo provided the isothermal version of the Monte Carlo code for holes, as well as valuable discussions pertaining the simulation dynamic and flow. Dr. Fabio Vidor and Dr. Thiago Both substantially contributed with ideas and insights. The companionship of M.Sc. Pablo Vaz, M.Sc. Paulo Aguirre, Dr. Raphael Brum, M.Sc. Thales Becker, and M.Sc. Thiago Copetti is also acknowledged, as well as the fruitful discussions with B.Sc. Caroline Soares and M.Sc. Gabriela Furtado, for whom I am passing the torch.

At the conclusion of writing this Ph.D. thesis, I realize how much I owe to my family. I am very grateful to my parents, Nelci and Cleusa, and to my siblings, Jean and Janaina, for their unconditional support and love. I am also exceedingly thankful to my beloved wife Monique, my safe harbor and companion for both good and *not that good* times.

Finally, I would like to thank the Universidade Federal do Rio Grande do Sul for providing public and high-quality education, as well as the CAPES Funding Agency for the financial support that made this work possible.

### **ABSTRACT**

The complementary metal-oxide-semiconductor (CMOS) scaling process of the recent decades, coupled with new device structures and materials, has aggravated thermal problems and turned them into major reliability issues for deeply-scaled devices. As a consequence, the thermal transport dynamic and its impact on the device performance at submicron dimensions is established as a contemporary theme. In this context, a new selfconsistent electro-thermal particle-based device simulator for the study of self-heating effects in p-type metal-oxide-semiconductor field-effect transistors (MOSFETs) based in silicon is developed and presented. The electrical module of the tool utilizes the Ensemble Monte Carlo method to perform the charge transport, whereas the thermal module evaluates the non-isothermal temperature profiles by solving the phonon energy balance equations for both acoustic and optical phonon baths. These temperature profiles are fed back into the electrical module, which adjusts the carriers' scattering rate accordingly, thus, properly accounting for the device current capability degradation. The developed tool proved to be suitable for sub-100 nm device simulations, and it was used to perform relevant case study simulations of 24-nm channel length bulk and fully-depleted siliconon-insulator (FD-SOI) MOSFETs. General device parameters extracted from the simulations are qualitatively in agreement with the expected behavior, as well as data from the literature, ensuring the proper operation of the tool. Electro-thermal simulations of bulk and FD-SOI devices provided both acoustic and optical phonon temperature profiles across the transistor structure, as well as the heat generation map and the device power dissipation. Some results were also extracted via Joule heating thermal model, and they are presented for comparison. The current degradation due to self-heating was found to be significant for FD-SOI devices, but very modest for bulk ones. At a fixed bias point of  $V_D = V_G = -1.5$  V, for instance, bulk devices presented a current variation of as much as -0.75%, whereas for FD-SOI devices it reached up to -8.82% for  $T_{\text{gate}} = 400$  K. Hot spot acoustic (lattice) and optical phonon temperatures were extracted as a function of the applied bias for both topologies. The lattice temperature rise, for instance, exceeded 10 K and 150 K over the heat sink temperature for bulk and FD-SOI transistors, respectively, observing the same bias point and gate temperature presented earlier. The particle-based nature of the tool is also suitable for the study of the impact of trap activity in MOS-FETs and its interplay with self-heating effects. Simulations of charge traps were used to analyze the statistical distribution of the current deviations in 25-nm bulk MOSFETs

due to traps. The simulations showed that these deviations are exponentially-distributed, as experimentally observed and reported in the literature. Electro-thermal simulations of charge traps in bulk and FD-SOI transistors revealed that the largest degradation on the device current occurs when the effects of self-heating and trap activity take place simultaneously. At lower biases, the impact of charge traps dominates the current degradation, whereas the self-heating component prevails for larger biases.

Keywords: CMOS. Charge Traps. Monte Carlo. MOSFET. Reliability. Self-heating.

# Modelagem e Simulação dos Efeitos de Auto Aquecimento em Transistores MOS do Tipo P

## **RESUMO**

Nas últimas décadas, o processo de constante redução das dimensões de dispositivos semicondutores — aliado a novas estruturas de dispositivos e novos materiais —, tem agravado os problemas térmicos em tais estruturas, tornando-os importantes limitadores na confiabilidade destes dispositivos. Como consequência, a dinâmica do transporte térmico, e o impacto desta no desempenho de dispositivos semicondutores de escala nanométrica, se estabelece como um tema bastante atual. Neste contexto, esta tese desenvolve e apresenta um novo simulador eletrotérmico de dispositivos do tipo particle-based voltado ao estudo dos efeitos de auto aquecimento (self-heating) em transistores de efeito de campo de metal-óxido-semicondutor (MOSFETs) do tipo p baseados em silício. A ferramenta possui duas partes principais: um módulo elétrico — que realiza o transporte de carga baseado no método de Monte Carlo —, e um módulo térmico — que determina os perfis não-isotérmicos de temperatura dentro do dispositivo através da resolução das equações do balanço energético entre fônons óticos e acústicos. Tais perfis de temperatura são fornecidos ao módulo elétrico que, por sua vez, ajusta a frequência de espalhamento dos portadores com base na temperatura na vizinhança destes, permitindo ao simulador capturar a degradação na capacidade de corrente dos transistores devido aos efeitos de auto aquecimento. A ferramenta se mostrou adequada para a simulação de dispositivos de até 100 nm de comprimento de canal, e foi utilizada para realizar simulações estudo de caso de transistores MOS nas tecnologias bulk e fully-depleted silicon-on-insulator (FD-SOI) com 24 nm de comprimento de canal. Parâmetros elétricos de tais dispositivos extraídos via simulação se mostraram coerentes com o comportamento esperado e com dados da literatura, o que assegura o correto funcionamento do simulador. A partir de simulações eletrotérmicas, foram extraídos os perfis de temperatura ao longo da estrutura dos transistores, além do mapeamento da geração de calor dentro do dispositivo e a potência por este dissipada. Para comparação, alguns resultados também foram extraídos a partir do modelo de aquecimento Joule. A degradação na corrente do dispositivo devido ao efeito de auto aquecimento se mostrou muito mais significativa para transistores de tecnologia FD-SOI do que para transistores de tecnologia bulk. Para uma polarização de  $V_{\rm D}=V_{\rm G}=-1.5$  V, por exemplo, transistores bulk apresentaram uma variação média na corrente de -0.75%, enquanto que a corrente dos transistores FD-SOI variou, em média, -8.82%, considerando  $T_{\text{gate}} = 400 \text{ K}$ . A temperatura de pico dos fônons acústicos (rede cristalina) e óticos foi extraída em função da polarização aplicada para ambas as topologias. Para a rede cristalina, por exemplo, o aumento da temperatura em relação à temperatura do dissipador foi de 10 K e 150 K para dispositivos bulk e FD-SOI, respectivamente, observando as mesmas condições apresentadas anteriormente. A característica particle-based da ferramenta também se mostrou adequada para o estudo da atividade de armadilhas (traps) em MOSFETs, bem como a interação desta com os efeitos de auto aquecimento. A simulação de armadilhas foi utilizada para analisar a distribuição estatística de impacto destas na corrente de dispositivos bulk com 25 nm de comprimento de canal. Tais simulações mostraram que as variações na corrente dos transistores devido à ação de armadilhas são exponencialmente distribuídas, em concordância com observações experimentais reportadas na literatura. Simulações eletrotérmicas de armadilhas de carga em transistores bulk e FD-SOI revelaram que a maior degradação na corrente do dispositivo ocorre quando os efeitos de auto aquecimento e atividade de armadilhas ocorrem simultaneamente. Para tensões de polarização mais baixas, o impacto das armadilhas de carga domina a degradação de corrente, enquanto que a degradação devido ao auto aquecimento prevalece para tensões mais elevadas.

**Palavras-chave:** Auto-aquecimento, Armadilhas de carga, CMOS, Confiabilidade, Monte Carlo, MOSFET.

# LIST OF ABBREVIATIONS AND ACRONYMS

1D One-dimensional

2D Two-dimensional

3D Three-dimensional

ASU Arizona State University

BTE Boltzmann Transport Equation

BTI Bias Temperature Instability

CMOS Complementary Metal-oxide-semiconductor

EMC Ensemble Monte Carlo

FinFET Fin Field-effect transistor

FD-SOI Fully-depleted Silicon-on-insulator

LHS Left-hand Side

LU Lower-upper

MOS Metal-oxide-semiconductor

MOSFET Metal-oxide-semiconductor Field-effect Transistor

PEB Phonon Energy Balance

RDF Random Dopant Fluctuations

RHS Right-hand Side

SHE Self-heating Effects

SIP Strong Implicit Procedure

SOI Silicon-on-insulator

SOR Successive-over-relaxation

### LIST OF SYMBOLS

A Inverse valence-band parameter

$a_{1,2}$  Energy dependent parameters

$C_{\rm A}$  Volumetric heat capacity of acoustic phonons

$C_{\rm OP}$  Volumetric heat capacity of optical phonons

dt Differential time

$d_{\rm t}$  Trap depth within the gate oxide

$D_{\rm J}$  Junction depth

$D_{\rm op}$  Optical phonon deformation potential

D<sub>T</sub> Total silicon depth

$D_tK$  Deformation potential constant for optical and intervalley-phonon scat-

tering with carriers

E Electric field

Energy

E' Carrier final energy

$E_{\rm ac}$  Acoustic deformation potential

$E_{\text{avg}}$  Average carrier energy

$E_{\text{avg}}(x)$  Average carrier energy along the transistor length

$E_{\text{avg}}(x, y, z)$  Average carrier energy for each position within the transistor

$E_{\rm c}$  Energy at the edge of the conduction band

$E_{\rm g}$  Band gap energy

$E_{\rm i}$  Particle initial energy

$E_{\mathbf{k}}$  Particle energy at the state  $\mathbf{k}$

$E_{\mathbf{k}'}$  Particle energy at the state  $\mathbf{k}'$

$E_{\rm v}$  Energy at the edge of the valence band

| f(Y)                                                             | Attenuation of the trap impact as a function of its depth into the gate oxide                                                |

|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| $f(Y_i)$                                                         | Attenuation of the impact of a trap at the position $Y_i$                                                                    |

| $g(oldsymbol{	heta}, oldsymbol{\phi})$                           | Warping of the bands as a function of the angles $\theta$ and $\phi$                                                         |

| $\hbar$                                                          | Reduced Planck constant                                                                                                      |

| H                                                                | Volumetric heat generation rate                                                                                              |

| H(x)                                                             | Heat generation along the transistor length                                                                                  |

| H(x, y, z)                                                       | Heat generation for each position within the transistor                                                                      |

| $H_{	ext{J}\cdot	ext{E}}$                                        | Volumetric heat generation evaluated via Joule heating model                                                                 |

| $H_{ m PEBs}$                                                    | Volumetric heat generation evaluated via phonon energy balance equations model                                               |

| $i_{ m max}$                                                     | Maximum number of mesh points along the <i>x</i> -axis                                                                       |

|                                                                  | Largest mesh point index along the <i>x</i> -axis                                                                            |

| $i_{ m min}$                                                     | Lowest mesh point index along the <i>x</i> -axis                                                                             |

| $I_{\mathrm{D}}$                                                 | Distribution of device drain currents                                                                                        |

| $\overline{I_{ m D}}$                                            | Average drain current for an ensemble of devices                                                                             |

| $I_{\mathrm{D0}}$                                                | Reference distribution of device drain currents                                                                              |

| $\overline{I_{ m D0}}$                                           | Average reference drain current for an ensemble of devices                                                                   |

| $I_{\mathrm{D0,i}}$                                              | Reference drain current for a given transistor $i$                                                                           |

| $I_{\mathrm{D}}(x_{\mathrm{t}},d_{\mathrm{t}},z_{\mathrm{t}})$   | Drain current distribution for an ensemble of devices with a trap in the position $p_{\rm t}(x_{\rm t},d_{\rm t},z_{\rm t})$ |

| $I_{\mathrm{D,i}}(x_{\mathrm{t}},d_{\mathrm{t}},z_{\mathrm{t}})$ | Drain current for a transistor $i$ with a trap in the position $p_t(x_t, d_t, z_t)$                                          |

| J                                                                | Electric current density                                                                                                     |

| $J_{\mathrm{n}}$                                                 | Electric current density due to electrons                                                                                    |

| $\dot{J}_{	ext{max}}$                                            | Maximum number of mesh points along the y-axis                                                                               |

|                                                                  | Largest mesh point index along the y-axis                                                                                    |

|                                                                  |                                                                                                                              |

Lowest mesh point index along the y-axis

$j_{\min}$

$j_{\text{OX}}$  Mesh points in the gate oxide

$J_{\rm p}$  Electric current density due to holes

**k** wave vector of a carrier

**k**' wave vector of a carrier after scattering

*k*<sub>B</sub> Boltzmann constant

$k_{\text{max}}$  Maximum number of mesh points along the z-axis

Largest mesh point index along the z-axis

$k_{\min}$  Lowest mesh point index along the *z*-axis

L Transistor channel length

*L*<sub>C</sub> Contact length

$L_{\rm D}$  Drain region length

*L*<sub>G</sub> Gate length

$L_{\rm S}$  Source region length

$L_{\rm T}$  Total device length

$L_{\rm tr}$  Square root of the trap impact area  $L_{\rm tr}^2$

$L_{\rm tr}^2$  Trap impact area

*m* Final band

*m*\* Carrier effective mass

$m_0$  Electron rest mass

M Number of thermal Gummel Cycles

*n* Initial band

Carrier concentration (in cm<sup>-2</sup>)

Number of Monte Carlo iterations

Number of particles in the system

Number of transistors in the ensemble

*N*<sub>A</sub> Source/drain doping concentration

$N_{\rm car}$  Maximum number of carriers

$N_{\rm D}$  Substrate doping concentration

*N*<sub>i</sub> Intrinsic doping concentration

$N_{\rm OP}$  Thermal equilibrium number of optical phonons

$N_{\rm q}$  Thermal equilibrium number of phonon with wave vector q

$N_{\rm sub}$  Substrate doping concentration

$p_t(x_t, d_t, z_t)$  Trap position within the device

P Power dissipated as heat

P(t) Probability that a carrier will suffer its next scattering event during a time

dt around t

$P_{h,ac}(E)$  Acoustic phonon scattering probability per unit time as a function of the

energy

$P_{h,op}(E)$  Non-polar optical phonon scattering probability per unit time as a func-

tion of the energy

$P_{\text{J-E}}$  Power dissipated as heat evaluated via Joule heating model

$P_{\text{PEBs}}$  Power dissipated as heat evaluated via phonon energy balance equations

model

q Elementary charge (with its sign)

r Position in real space

r Uniformly distributed random number

R Carrier generation/recombination rate

$SE_{\overline{\nu}_{\rm D}}$  Standard error of the drift velocity

*t* Time

$t_{\rm BOX}$  Buried oxide thickness

$t_{\rm dep}$  Depletion region thickness (or depth)

$t_{\text{max}}$  Maximum simulation time

t<sub>OX</sub> Gate oxide thickness

$t_{\rm r}$  Random free flight time

$t_{\text{sat}}$  Amount of time required to a carrier to cross the device channel traveling

at the velocity saturation limit

$t_{Si}$  Silicon layer thickness

$t_{\rm tran}$  Simulation transient time

$t_{

m w}$  Length of the simulation time window

T Temperature

*T*<sub>A</sub> Acoustic phonon temperature

$T_{\rm A}(i,j,k)$  Acoustic phonon temperature at a given position p(i,j,k) within the mesh

*T*<sub>c</sub> Carrier temperature

$T_{\rm gate}$  Gate electrode temperature

$T_{i_{\max}}$  Temperature at the surface with  $i = i_{\max}$

$T_{i_{\min}}$  Temperature at the surface with  $i = i_{\min}$

$T_{\rm ini}$  Initial temperature

$T_{j_{\text{max}}}$  Temperature at the surface with  $j = j_{\text{max}}$

$T_{j_{\min}}$  Temperature at the surface with  $j = j_{\min}$

$T_{\text{J-E}}$  Acoustic phonon temperature (lattice) evaluated via Joule heating model

*T*<sub>L</sub> Lattice temperature

$T_{\rm OP}$  Optical phonon temperature

$T_{\rm OP}(i,j,k)$  Optical phonon temperature at a given position p(i,j,k) within the mesh

T<sub>PEB</sub> Acoustic phonon temperature evaluated via PEB model

$T_{\rm ph}$  Generic phonon temperature

$T_{\rm sink}$  Heat sink temperature

$V_{\rm D}$  Voltage applied at the drain electrode

$V_{\rm DS}$  Voltage applied between the drain and source electrodes

$V_{\rm G}$  Voltage applied at the gate electrode

$V_{GS}$  Voltage applied between the gate and source electrodes

$V_i$  Scattering potential of a given process j

$V_{\rm TH}$  Transistor's threshold voltage

W Device width

$W_{\rm A}$  Energy density for the acoustic phonon bath

W<sub>c</sub> Carrier energy density

$W_{\rm OP}$  Energy density for the optical phonon bath

$x_{\rm D}$  Position along the transistor length of the metallurgical junction between

the channel and the drain region

$x_{\text{max}}$  Maximum extension of the transistor along the transistor length

$x_{\rm S}$  Position along the transistor length of the metallurgical junction between

the source and the channel region

$x_{\rm t}$  Trap position along the transistor channel length

X<sub>i</sub> Random trap position along the transistor channel length

$y_{\text{max}}$  Maximum extension of the transistor along the transistor depth

y<sub>OX</sub> Maximum extension of the gate oxide above the Si/SiO<sub>2</sub> interface

$y_{SD}$  Position along the transistor depth of the metallurgical junction between

the source/drain and the substrate region

Y<sub>i</sub> Random trap depth into the gate oxide

$z_{\rm t}$  Trap position along the transistor width

$\beta(E')$  Non-parabolicity factor as a function of the energy E'

$\Gamma$  Total scattering rate including self-scattering

$\Gamma_i$  Scattering rate of a given process j

$\Gamma_{\text{self}}$  Self-scattering rate

$\delta I_{\rm D}$  Current deviation distribution for an ensemble of devices

$\delta I_{\rm D,calc}$  Current deviation calculated via uniform channel theory

$\delta I_{D,i}$  Extrapolated current deviation due to a trap for a given transistor i

| $\delta I_{\mathrm{D}}(\mathrm{X})$                                     | Current deviation distribution for an ensemble of devices as a function of the trap position along the transistor length |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| $\delta I_{\mathrm{D}}(\mathrm{X_{i}})$                                 | Drain current deviation due to a trap at the position $X_i$                                                              |

| $\delta I_{\mathrm{D}}(x_{\mathrm{t}},d_{\mathrm{t}},z_{\mathrm{t}})$   | Current deviation distribution for an ensemble of devices with a trap at the position $p_t(x_t, d_t, z_t)$               |

| $\delta I_{\mathrm{D,i}}(x_{\mathrm{t}},d_{\mathrm{t}},z_{\mathrm{t}})$ | Current deviation due to a trap at $p_t(x_t, d_t, z_t)$ for a given transistor $i$                                       |

| Δ                                                                       | Mesh spacing                                                                                                             |

| $\Delta E_{ m ij}$                                                      | Energy gap between band $i$ and band $j$                                                                                 |

| $\Delta n$                                                              | Carrier concentration variation (in cm <sup>-2</sup> )                                                                   |

| $\Delta t$                                                              | Time step                                                                                                                |

| $\Delta \overline{I_{ m D}}$                                            | Average current deviation for an ensemble of devices                                                                     |

| ε                                                                       | Material electrical permittivity                                                                                         |

| $arepsilon_{	ext{Si}}$                                                  | Silicon electrical permittivity                                                                                          |

| $\theta$                                                                | Azimuthal angle between the states $\mathbf{k}$ and $\mathbf{k}'$                                                        |

| κ                                                                       | Lattice thermal conductivity for silicon                                                                                 |

| $\kappa_{ m A}$                                                         | Acoustic phonon thermal conductivity for silicon                                                                         |

| $\kappa_{\mathrm{Si}}$                                                  | Thermal conductivity of silicon                                                                                          |

| $\lambda_{ m D}$                                                        | Debye length                                                                                                             |

| μ                                                                       | Carrier mobility                                                                                                         |

| ρ                                                                       | Carrier concentration                                                                                                    |

| $ ho_{ m m}$                                                            | Material mass density                                                                                                    |

| σ                                                                       | Transistor channel conductance                                                                                           |

| $\sigma_{\overline{v}_{ m D}}$                                          | Standard deviation of the drift velocity                                                                                 |

| τ                                                                       | Energy transfer time scale                                                                                               |

| $	au_{\mathrm{c-A}}$                                                    | Carrier-acoustic phonon relaxation time                                                                                  |

|                                                                         |                                                                                                                          |

Carrier-lattice scattering time constant

$au_{\mathrm{c-L}}$

$\tau_{c-OP}$  Carrier-optical phonon relaxation time

$\tau_{c-ph}$  Carrier-phonon relaxation time

$\tau_{\rm OP-A}$  Optical phonon-acoustic phonon relaxation time

$v_{\rm c}$  Single carrier drift velocity

$v_{\rm D}$  Carrier drift velocity

$\overline{v}_{\rm D}$  Average drift velocity

$v_{\rm D}^n$  Drift velocity for the  $n^{\rm th}$  particle

$v_D(x)$  Carrier drift velocity along the transistor length

$\overline{v}_D(m\Delta t)$  Average drift velocity at the  $m^{th}$  time step

$v_D^n(m\Delta t)$  Drift velocity for the  $n^{th}$  particle at the  $m^{th}$  time step

$v_{\mathrm{Dsat}}$  Carrier saturation drift velocity

$v_{\mathrm{D}t}$  Absolute (ot total) carrier drift velocity

$v_{\mathrm{D}x}$  Carrier drift velocity along the x-axis

$v_{\rm Dy}$  Carrier drift velocity along the y-axis

$v_{\mathrm{D}z}$  Carrier drift velocity along the z-axis

$v_{\rm s}$  Sound velocity in the material

$v_{\rm T}$  Carrier thermal velocity

$\phi$  Polar angle between the states **k** and **k**'

$\phi_{\rm f}$  Fermi potential

$\phi_n$  Quasi-fermi level for electrons

$\phi_{\rm p}$  Quasi-fermi level for holes

$\omega$  Phonon angular frequency

$\Omega$  Crystal volume

$\omega_0$  Initial phonon angular frequency

$\omega_{\rm op}$  Optical phonon angular frequency

$\omega_{\rm p}$  Plasma frequency

# LIST OF FIGURES

| Figure 2.1 | Flowchart of a typical ensemble Monte Carlo device simulation                                       | 34   |

|------------|-----------------------------------------------------------------------------------------------------|------|

| Figure 2.2 | Selection of the type of scattering terminating a free flight in the                                |      |

|            | e Carlo algorithm                                                                                   | 40   |

|            | Ensemble Monte Carlo simulation in which a time step $\Delta t$ is intro-                           |      |

|            | over which the motion of particles is synchronized                                                  | 41   |

| _          | Flowchart for the electric portion of the ensemble Monte Carlo                                      |      |

|            | ator developed in the work of Camargo (2016)                                                        | 43   |

| _          | Hole drift velocity as a function of the electric field and carrier                                 |      |

| mobil      | ity as a function of the acceptor density for silicon                                               | 45   |

| Figure 3.1 | Diagram and characteristics time scales of the energy transfer pro-                                 |      |

|            | in silicon                                                                                          | 50   |

|            | Self-consistent loop scheme: exchange of variables between the                                      | 50   |

|            | c and thermal kernels and choice of the proper scattering table                                     | 60   |

| ciccui     | e and thermal kernels and choice of the proper scattering table                                     | 00   |

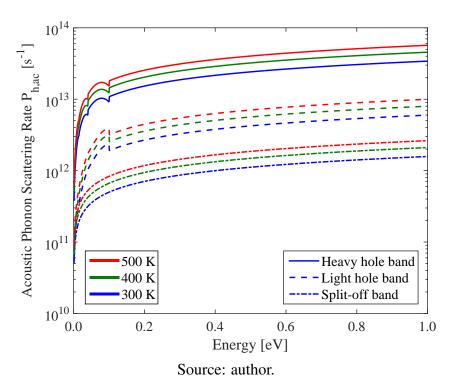

| Figure 4.1 | Acoustic phonon scattering rates for holes scattering from the heavy                                |      |

| hole, l    | ight hole, and split-off bands for temperatures of 300 K, 400 K, and                                |      |

|            |                                                                                                     | 65   |

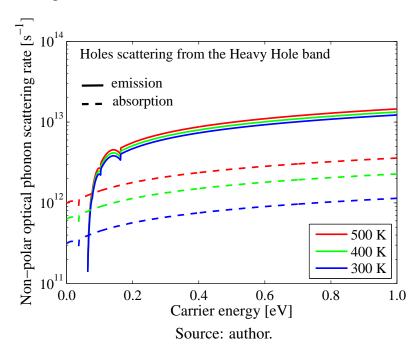

| Figure 4.2 | Non-polar optical phonon scattering rate for holes scattering from                                  |      |

| the he     | avy hole band for temperatures of 300 K, 400 K, and 500 K                                           | 66   |

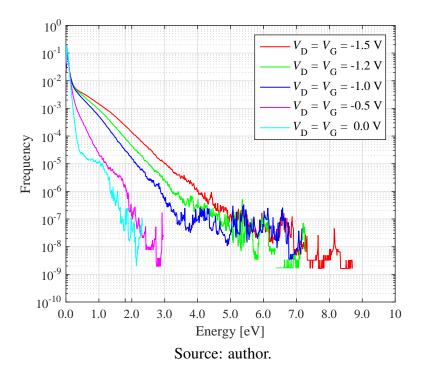

| Figure 4.3 | Histogram of the energy of the carriers during a simulation as a                                    |      |

| functi     | on of the applied bias for a bulk MOSFET                                                            | 66   |

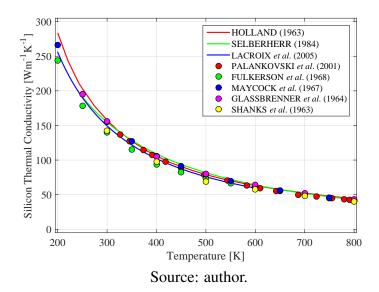

| Figure 4.4 | Silicon thermal conductivity as a function of the temperature                                       | 71   |

|            |                                                                                                     |      |

| _          | Flowchart of the electro-thermal simulator                                                          | 75   |

| Figure 5.2 | ·                                                                                                   |      |

| sistors    |                                                                                                     |      |

| Figure 5.3 | Simulation structure for bulk and FD-SOI case study transitors                                      | 78   |

| Figure 5.4 | Hot spot temperature and number of iterations needed to solve the                                   |      |

|            | quation as a function of the solver tolerance                                                       | 82   |

| Figure 5.5 |                                                                                                     |      |

|            |                                                                                                     |      |

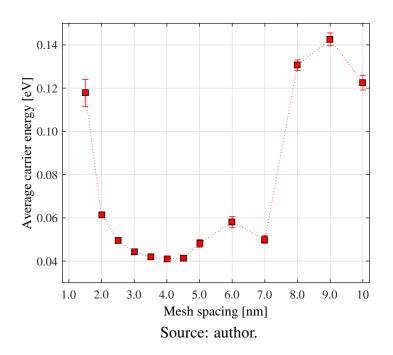

|            | Average carrier energy as a function of the mesh spacing                                            |      |

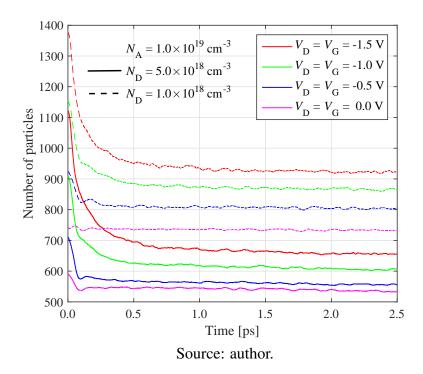

| _          | Number of particles (carriers) being used in the simulation along time                              |      |

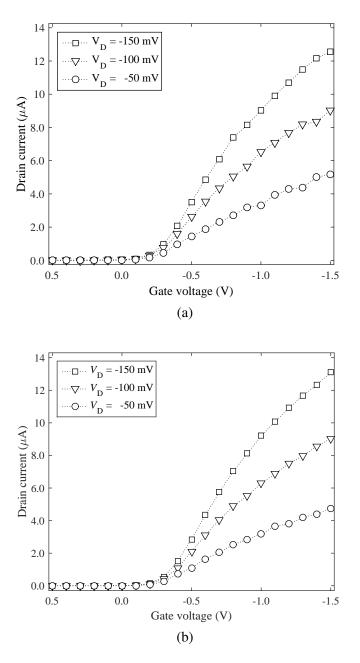

| Figure 5.8 | $I_{\rm D} \times V_{\rm G}$ characteristics of the bulk and FD-SOI case study MOSFETs              |      |

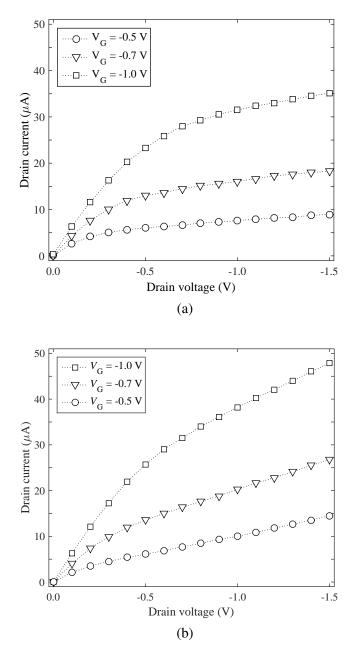

| Figure 5.9 | $I_{\rm D} \times V_{\rm D}$ characteristics of the bulk and FD-SOI case study MOSFETs              | s.88 |

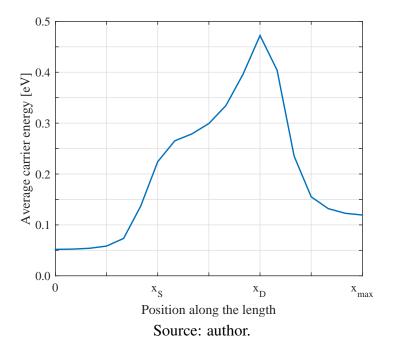

| Eigura 6 1 | Average corrier energy as a function of the position along the tran                                 |      |

|            | Average carrier energy as a function of the position along the tran-<br>length for 100 bulk MOSFETs | 01   |

|            |                                                                                                     | 91   |

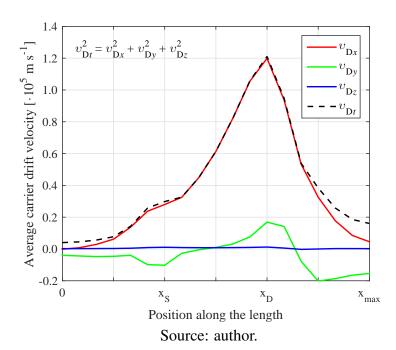

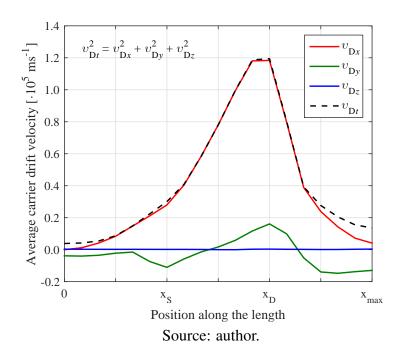

| Figure 6.2 |                                                                                                     | 01   |

|            | ansistor length for 100 bulk MOSFETs                                                                | 91   |

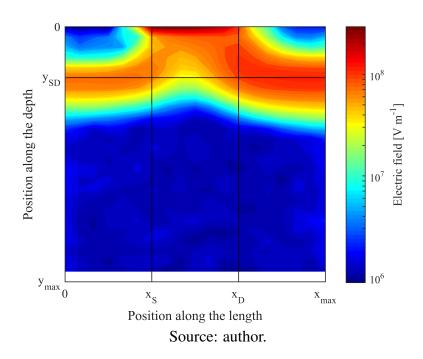

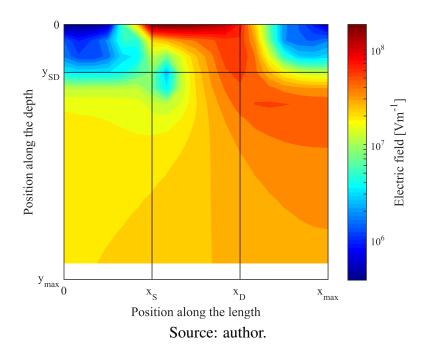

| -          | Average electric field profile as a function of the position along the                              | 02   |

|            | stor length and depth for 100 bulk MOSFETs                                                          | 92   |

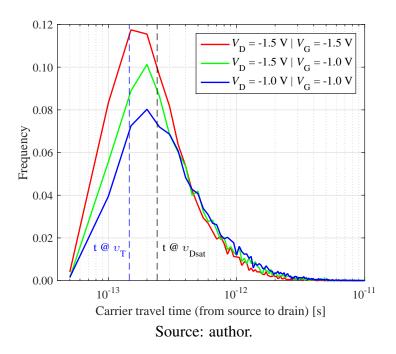

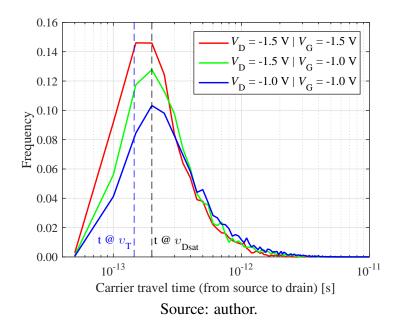

| _          | Distribution of the carrier travel time from source to drain as a                                   | 02   |

|            | on of the bias for 100 case study bulk MOSFETs                                                      | 92   |

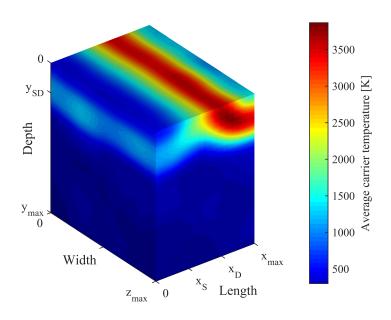

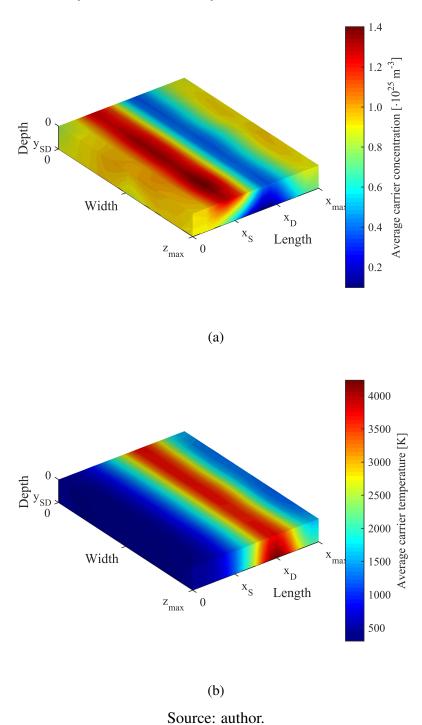

| _          | Average carrier temperature along the transistor structure for 100 tridy bulk MOSEETs               | 02   |

|            | tudy bulk MOSFETs                                                                                   | 93   |

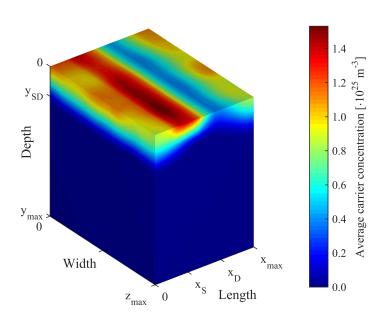

|            | Average carrier concentration along the transistor structure for 100                                | 02   |

| case s     | tudy bulk MOSFETs                                                                                   | 93   |

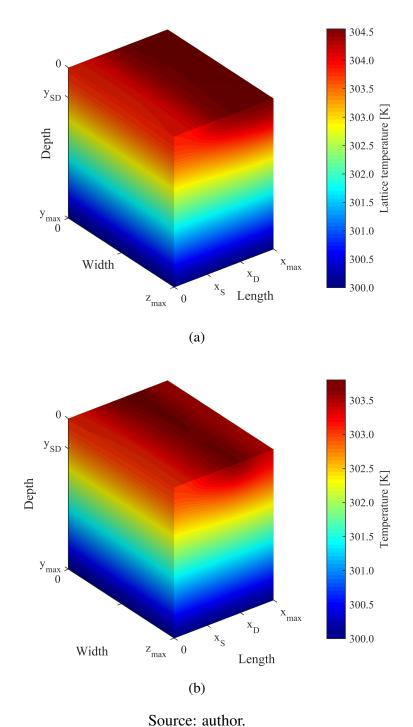

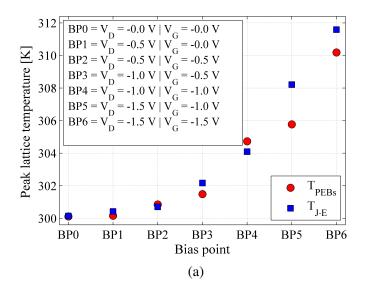

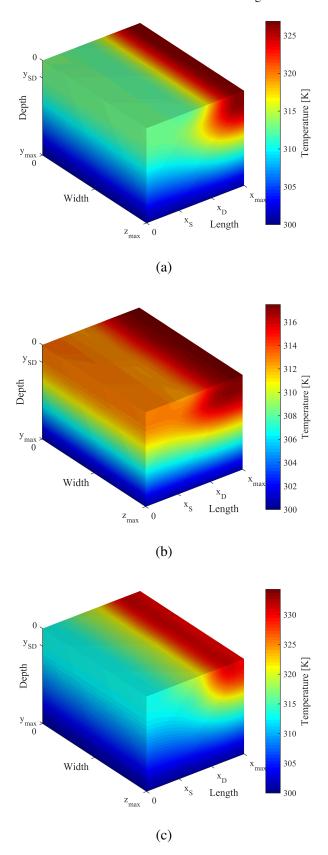

| Figure 6.7 Average acoustic phonon (lattice) temperature profile evaluated via the PEB model and Joule heating model for 100 case study bulk MOSFETs                               | .95 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

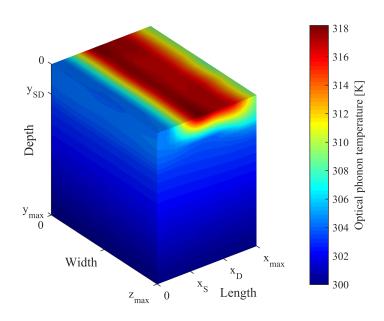

| Figure 6.8 Average optical phonon temperature profile for 100 case study bulk                                                                                                      | .96 |

| Figure 6.9 Average acoustic phonon peak temperature and optical phonon peak temperature as a function of the applied bias for 100 case study bulk                                  |     |

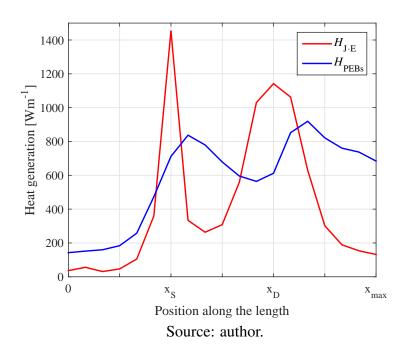

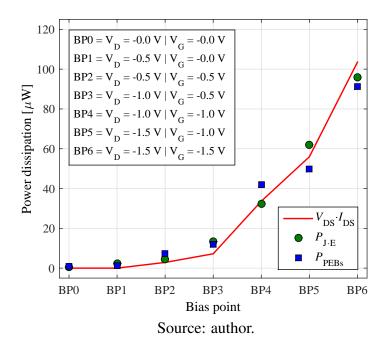

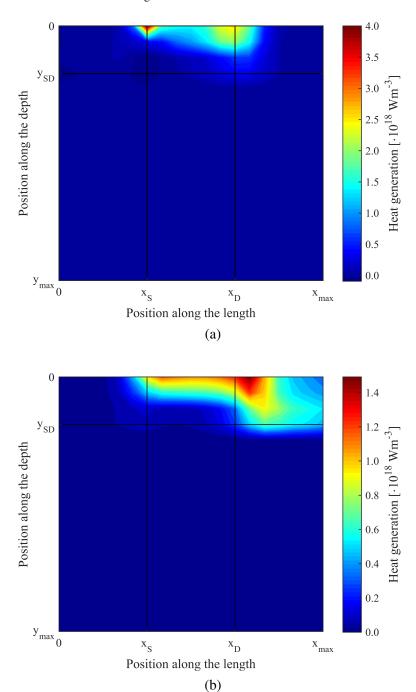

| MOSFETs.  Figure 6.10 Average volumetric heat generation within the transistor evaluated via phonon energy balance model and Joule heating model for 100 case study bulk MOSFETs.  | .97 |

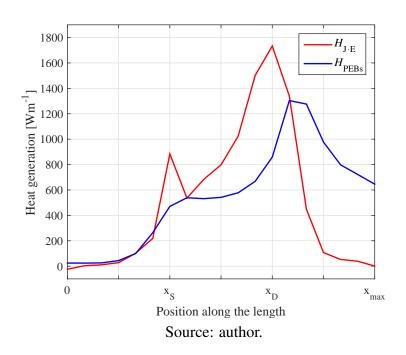

| Figure 6.11 Average heat generation along the transistor length according to the PEB model and Joule heating model for 100 case study bulk MOSFETs.1                               | 100 |

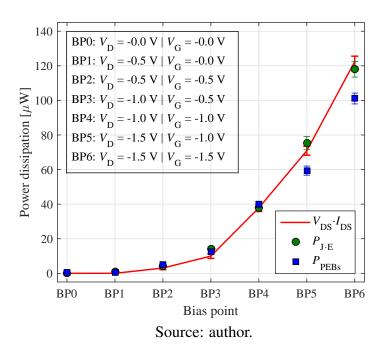

| Figure 6.12 Average power supplied to the transistor and average power dissipated as heat for each thermal model as a function of the applied bias for 100 case study bulk MOSFETs | 101 |

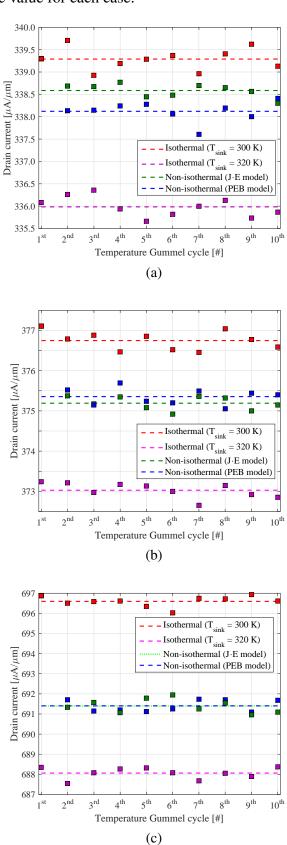

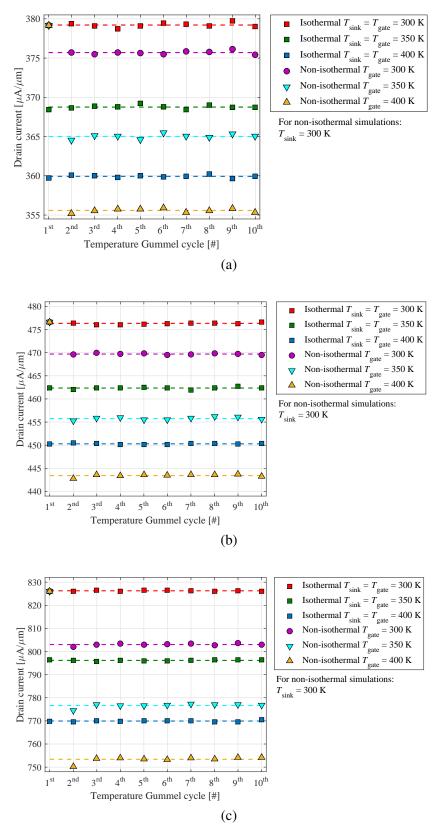

| Figure 6.13 Drain current as a function of the temperature Gummel cycle for isothermal and non-isothermal simulations.                                                             |     |

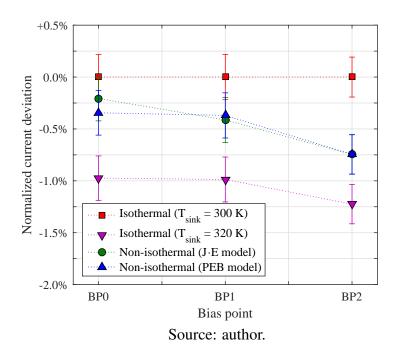

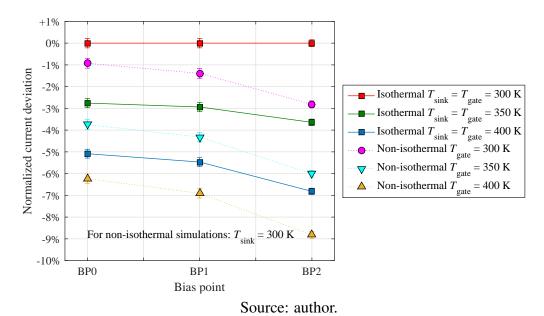

| Figure 6.14 Average drain current deviation for isothermal and non-isothermal simulations as a function of the applied bias.                                                       | 104 |

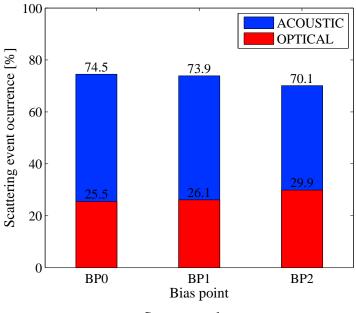

| Figure 6.15 Percentage of acoustic and optical scattering events as a function of the applied bias.                                                                                | 104 |

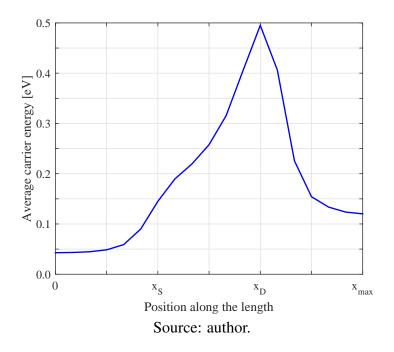

| Figure 6.16 Average carrier energy along the transistor length for 100 case study FD-SOI MOSFETs                                                                                   | 106 |

| Figure 6.17 Average carrier drift velocity along the transistor length for 100 case study FD-SOI MOSFETs                                                                           | 106 |

| Figure 6.18 Average electric field profile along the transistor length and depth for 100 case study FD-SOI MOSFETs.                                                                | 107 |

| Figure 6.19 Distribution of the carrier travel time from source to drain as a function of the applied bias for 100 case study FD-SOI MOSFETs                                       | 107 |

| Figure 6.20 Average carrier concentration and average carrier temperature along the transistor silicon layer for 100 case study FD-SOI MOSFETs                                     | 108 |

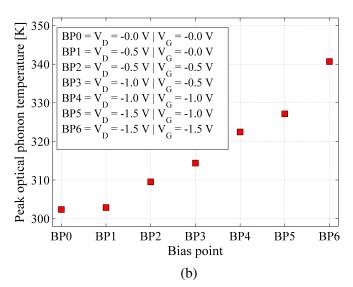

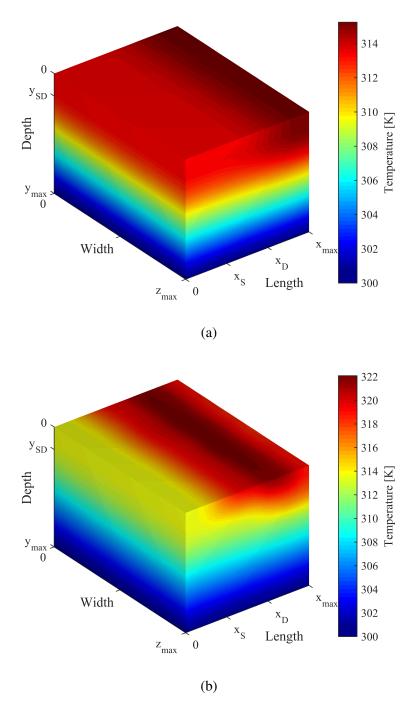

| Figure 6.21 Average acoustic phonon temperature profile evaluated via PEB model and Joule heating model, and optical phonon temperature profile for 100 case study FD-SOI MOSFETs. | 110 |

| Figure 6.22 Average acoustic phonon and optical phonon temperature profiles for 100 case study FD-SOI MOSFETs with silicon thermal conductivity depending only on the temperature  | 111 |

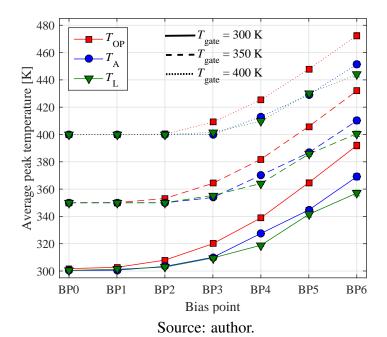

| Figure 6.23 Average optical phonon, acoustic phonon, and lattice peak temperature for 100 case study FD-SOI MOSFETs as a function of the applied bias and gate temperature         |     |

| Figure 6.24 Volumetric heat generation profile evaluated via Joule heating model and PEB model for 100 case study FD-SOI MOSFETs                                                   |     |

| Figure 6.25 Average heat generation along the transistor length for 100 case study FD-SOI MOSFETs                                                                                  | 115 |

| Figure 6.26 Electric power supplied to the device and power dissipated as heat for each thermal model according to the applied bias for 100 case study FD-SOI MOSFETs.             | 116 |

| Figure 6.27 Average drain current deviation for isothermal and non-isothermal                                                                                                      | 117 |

| Figure 6.28 Drain current as a function of the temperature Gummel cycle for       |                                                                                        |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 1                                                                                 | 110                                                                                    |

|                                                                                   | 118                                                                                    |

|                                                                                   |                                                                                        |

|                                                                                   |                                                                                        |

| for non-isothermal simulations of 100 case study FD-SOI MOSFETs                   | 119                                                                                    |

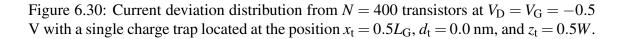

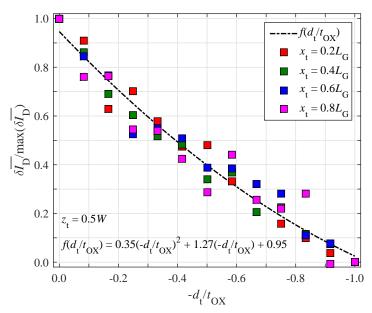

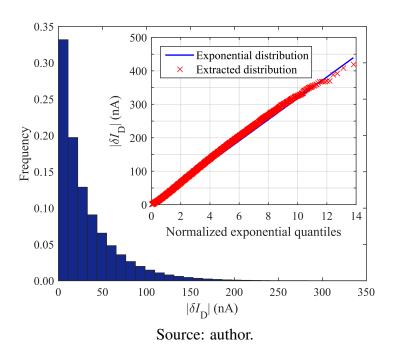

| Figure 6.30 Current deviation distribution from $N = 400$ transistors with a sin- |                                                                                        |

| gle charge trap located in the middle of the conduction channel                   | 122                                                                                    |

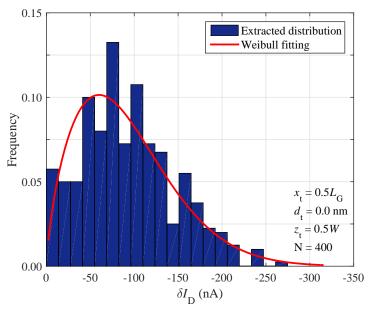

| Figure 6.31 Normalized average drain current deviation caused by a single trap    |                                                                                        |

| as a function of its position along the channel length                            | 123                                                                                    |

| Figure 6.32 Normalized average current deviation caused by a single trap as a     |                                                                                        |

| function of the its depth into the oxide.                                         | 124                                                                                    |

|                                                                                   |                                                                                        |

|                                                                                   | 126                                                                                    |

|                                                                                   |                                                                                        |

|                                                                                   | 127                                                                                    |

| *                                                                                 |                                                                                        |

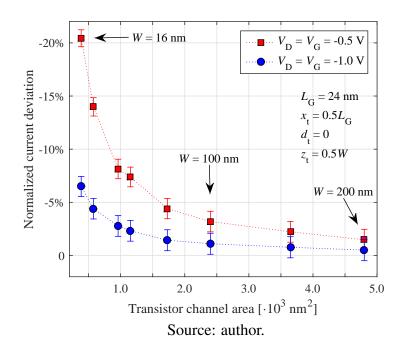

|                                                                                   | 128                                                                                    |

| interruce us a remetion of the translator channel area and approach classimini    |                                                                                        |

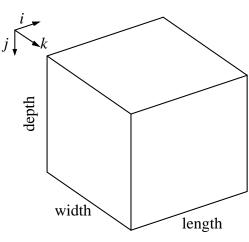

| Figure A.1 Graphical representation of the test structure                         | 145                                                                                    |

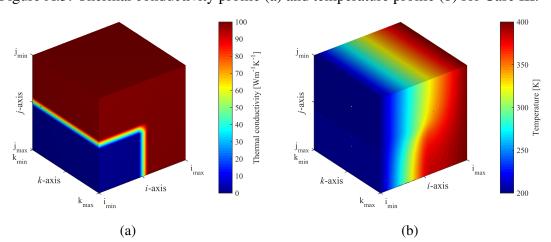

| Figure A.2 Simulated temperature profile for Case I and Case II.                  | 146                                                                                    |

|                                                                                   |                                                                                        |

|                                                                                   |                                                                                        |

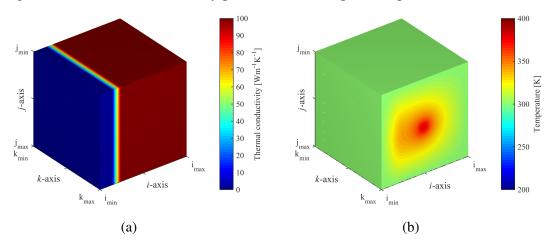

| Figure A.5 Thermal conductivity profile and temperature profile for Case V        |                                                                                        |

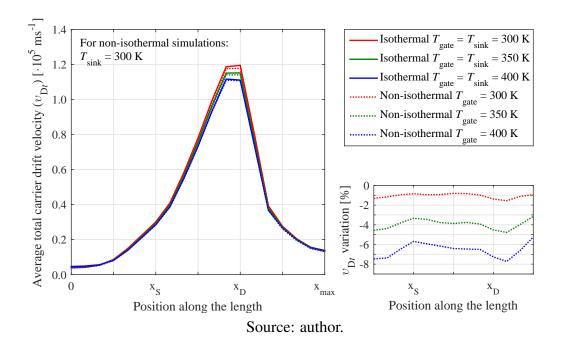

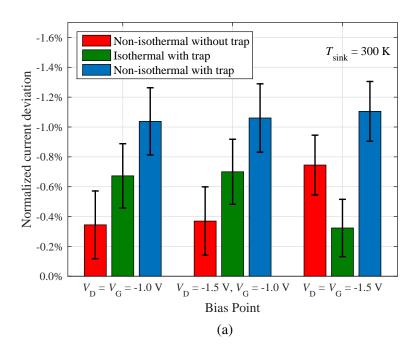

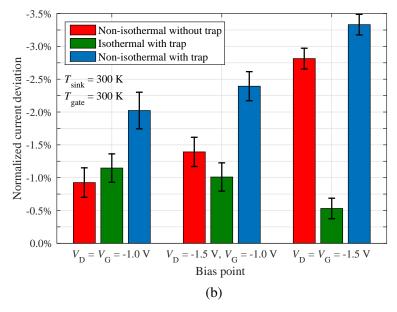

|                                                                                   | isothermal and non-isothermal simulations for multiple heat sink and gate temperatures |

# LIST OF TABLES

| Table 3.1 Comparison among the phonon models presented in Subsection 3.2.356                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 4.1 Description of the physical parameters and constants utilized for scattering rates calculation                                                                                                                                                                                  |

| Table 5.1 Physical dimensions of the bulk and FD-SOI case study MOSFETs79 Table 5.2 Main simulation parameters for bulk and FD-SOI case study MOSFETs.80                                                                                                                                  |

| Table 6.1 Average drain current for isothermal and non-isothermal simulations as a function of the applied bias for 1000 case study bulk MOSFETs. The current variation for each case is calculated over the current extracted from the isothermal simulation with $T_{\rm sink} = 300$ K |

| Table 6.2 Average drain current for isothermal and non-isothermal simulations                                                                                                                                                                                                             |

| as a function of the gate temperature and applied bias                                                                                                                                                                                                                                    |

# CONTENTS

| 1 INTI | RODUCTION                                                            | 29  |

|--------|----------------------------------------------------------------------|-----|

| 2 ENS  | EMBLE MONTE CARLO METHOD                                             | 33  |

| 2.1    | Scattering Rates                                                     | 35  |

| 2.2    | Free-Flight Time Generation                                          | 37  |

| 2.3    | Scattering Events                                                    | 39  |

| 2.4    | Ensemble Monte Carlo Simulation                                      | .40 |

| 2.5    | Device Simulation Utilizing the Ensemble Monte Carlo Method          | 42  |

| 3 THE  | LATTICE HEATING PROBLEM                                              | 47  |

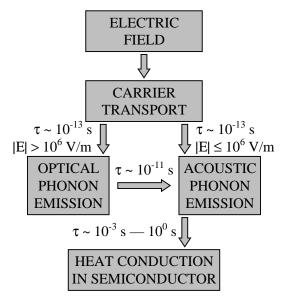

| 3.1    | Physical Mechanism                                                   | 48  |

| 3.2    | Modeling of Self-Heating                                             | 50  |

|        | 3.2.1 Joule Heating Model                                            | 51  |

|        | 3.2.2 Carrier-Lattice Scattering                                     | 52  |

|        | 3.2.3 Phonon Model                                                   | 52  |

|        | 3.2.4 Phonon Monte Carlo Simulator                                   | 55  |

| 3.3    | ASU Model Description                                                | 55  |

| 4 DEV  | ELOPMENT OF THE THERMAL MODULE                                       | 63  |

| 4.1    | Temperature Dependent Scattering Tables                              | 63  |

| 4.2    | Solving the Phonon Energy Balance Equations in 3D Coordinates        | 67  |

| 4.3    | Thermal Conductivity of Silicon Dependence on the Temperature        | 69  |

| 4.4    | Thermal Conductivity Dependence on the Silicon Doping and Thickness. | 71  |

| 5 ELE  | CTRO-THERMAL SIMULATION PROCEDURE                                    | 73  |

| 5.1    | Simulation Flow                                                      | 73  |

| 5.2    | Thermal Boundary Conditions                                          | 74  |

| 5.3    | Case Study Devices                                                   | 76  |

| 5.4    | Optimization of Simulation Parameters                                | 80  |

|        | 5.4.1 Thermal Solver Tolerance                                       | 81  |

|        | 5.4.2 Time Step                                                      | 81  |

|        | 5.4.3 Mesh Size                                                      | 84  |

|        | 5.4.4 Number of Particles in the Simulation                          | 85  |

| 5.5    | Device Characterization                                              | 86  |

| 6 RESU     | ULTS AND DISCUSSION                                              | 89   |  |  |  |

|------------|------------------------------------------------------------------|------|--|--|--|

| 6.1        | Electro-thermal Simulations of Bulk MOSFETs                      | 89   |  |  |  |

|            | 6.1.1 Carrier Profiles                                           | 89   |  |  |  |

|            | 6.1.2 Temperature Profiles                                       | 94   |  |  |  |

|            | 6.1.3 Heat Generation Profile                                    | 98   |  |  |  |

|            | 6.1.4 Impact of Self-heating on the bulk MOSFET On-Current       | 102  |  |  |  |

| 6.2        | Electro-thermal Simulations in FD-SOI MOSFETs                    | 105  |  |  |  |

|            | 6.2.1 Carrier Profiles                                           | 105  |  |  |  |

|            | 6.2.2 Temperature Profiles                                       | 109  |  |  |  |

|            | 6.2.3 Heat Generation Profile                                    | 113  |  |  |  |

|            | 6.2.4 Impact of Self-heating on the FD-SOI MOSFET On-Current     | 116  |  |  |  |

| 6.3        | Particle-based Simulations of Charge Traps in MOSFETs            | 120  |  |  |  |

|            | 6.3.1 Statistical Simulations of Charge Traps in Bulk MOSFETs    | 121  |  |  |  |

|            | 6.3.2 Electro-thermal Simulations of Charge Traps in Bulk and FD | -SOI |  |  |  |

|            | MOSFETs                                                          | 125  |  |  |  |

| 7 CON      | CLUSION                                                          | 129  |  |  |  |

| REFERENCES |                                                                  |      |  |  |  |

| APPEN      | APPENDIX A — VALIDATION OF THE THERMAL SOLVER1                   |      |  |  |  |

| APPEN      | APPENDIX B — PUBLICATIONS1                                       |      |  |  |  |

### 1 INTRODUCTION

Over the years, CMOS technology scaling has provided continuous improvements to integrated circuits performance and density, and the constant trend to reduce the transistor size has led to the emergence of nanoscale devices. On the other hand, not only advantages for the semiconductor structures have arisen from this process. Several issues that played minor roles in older technologies became major or even critical reliability limiters for modern technology nodes. Particularly noteworthy are the effects of random dopant fluctuations (RDF) (BHAVNAGARWALA; TANG; MEINDL, 2001; MAHMOODI; MUKHOPADHYAY; ROY, 2005; GERRER et al., 2012) and charge trap activity (KACZER et al., 2011; THEODOROU et al., 2015).

The shrink of device dimensions has also lead to increased power density levels generated in the channel, which can be directly translated into a temperature rise in the device active region (MAKOVEJEV; OLSEN; RASKIN, 2011). Although thermal phenomena are intrinsically related to the operation of electronic devices, they are not directly responsible for electrical functionality and performance, but adversely affect transistor reliability and yield. It is well known, for instance, that the increase in the overall device temperature may degrade its current drive capability (TAKACS; TRAGER, 1987; CAVIGLIA; ILIADIS, 1993; JENKINS; RIM, 2002). Additionally, temperature variation across a single chip may induce mismatch issues for analog applications (TENBROEK et al., 1998), while device overheating is reported to be one of the most common causes of circuit failure (MITTAL; MAZUMDER, 2010).

The heat source causing such temperature rise of a semiconductor device (or circuit) can be either external to the structure — for instance, in a situation that the circuit is operating in a high-temperature environment —, or internal — when the heat is generated by the device itself. In the latter situation, the effect is appropriately called *self-heating*. The occurrence of self-heating in semiconductor devices is known since the 70's (POPESCU, 1970) and it was firstly reported for bulk MOS (SESNIC; CRAIG, 1972) and bipolar (GAUR; NAVON, 1976) technologies.

Nevertheless, self-heating effects started to capture significant attention with the emergence of silicon-on-insulator (SOI) devices (NEEL; HAOND, 1990; BERGER; CHAI, 1991; DALLMANN; SHENAI, 1995; TENBROEK et al., 1997). In these structures, the heat flow through the substrate is restricted, since the buried oxide layer has poor thermal conductivity. In addition, the thermal conductivity of silicon significantly decreases

as the silicon layer thickness is reduced to the nanometric scale (ASHEGHI et al., 1998; ASHEGHI et al., 2002), retaining the heat even more concentrated. As a consequence, the heat generated at the active area remains almost entirely confined in the silicon layer, and much higher temperature hot spots are expected for SOI in comparison with bulk devices (RALEVA et al., 2012). Self-heating has been also reported to occur in tri-gate (PRASAD et al., 2013) as well as bulk and SOI FinFET devices (LIU et al., 2014; JIANG et al., 2015; JEON; JHON; KANG, 2017). In these non-planar and also highly confined topologies, besides the typical performance degradation, self-heating acts as a transistor lifetime limiter (LEE et al., 2017; PRASAD; RAMEY; JIANG, 2017). Moreover, its occurrence is no longer restricted to extreme scenarios, being pervasive even at nominal usage conditions (PRASAD; RAMEY; JIANG, 2017).

In the literature, self-heating effects are widely covered for *n*-type MOS devices. On the other hand, there is a lack of studies and tools addressing these effects in *p*-type structures. From the CMOS design perspective, however, it is desirable that self-heating effects are well characterized for both device types. In addition, some reliability issues, such as the bias temperature instability (BTI), mainly affects *p*-type transistors (MAK-ABE; KUBOTA; KITANO, 2000; REDDY et al., 2005; STATHIS; ZAFAR, 2006), and the interplay with self-heating might stimulate further degradation in such devices. In this context, this thesis proposes a novel self-consistent electro-thermal particle-based device simulator for the study of self-heating effects in *p*-type MOS transistors based in silicon. The version of the simulator presented here covers planar technology, but it is easily scalable to any 3D structure, such as tri-gate and FinFET devices.

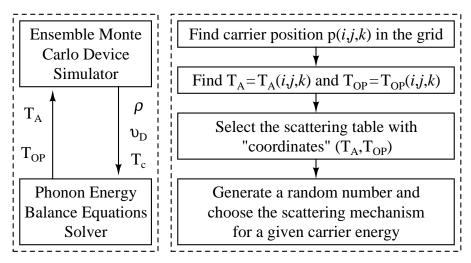

The electro-thermal tool itself is divided into two main modules. At the electrical portion of the simulator, the Ensemble Monte Carlo method is utilized to perform the charge transport by resolving the Boltzmann Transport Equation (BTE) self-consistently coupled with a Poisson equation solver. At the thermal portion of the simulator, the phonon energy balance equations are self-consistently solved for both acoustic and optical phonon baths utilizing data arising from the electrical module, providing the temperature profile for both acoustic and optical phonons at each point of the device. These temperatures are fed back into the electrical module, which adjusts the carriers' scattering rate accordingly, thus, properly accounting for the device current capability degradation. The developed tool proved to be suitable for sub-100 nm device simulations, and it was used to perform relevant case study simulations of 24-nm channel length bulk and fully-depleted silicon-on-insulator (FD-SOI) transistors.

The particle-based character of the tool is also suitable for the simulation of the impact of trap activity on the performance of *p*-type MOSFETs. The real-space treatment of the Coulomb interactions provided by the simulator allows one to account for the particle-like nature of carriers and dopants. In addition, the 3D-placement of the impurity atoms properly reproduces the RDF effect and allows the generation of unique random dopant profiles. The aforementioned features are key for the analysis of the impact of charge traps on the performance of MOS devices via computational simulations.

This work is organized as follows: first, a general and introductory overview of particle-based simulation and charge transport via the Ensemble Monte Carlo method is presented in Chapter 2. Still in the context of device simulation, Chapter 3 addresses the lattice heating problem in details; its physical mechanism and impact on the device performance, as well as the most commonly used modeling techniques. The development of the simulator thermal module is the subject of Chapter 4, which also addresses its coupling with the electrical module, turning the tool into an electro-thermal simulator. Next, the simulation procedure and the typical flowchart of an electro-thermal simulation are presented in Chapter 5, along with the optimization of some simulation parameters and the case study devices used in the scope of this work. Finally, Chapter 6 presents the results extracted for the case study structures via isothermal, electro-thermal, and charge trap simulations; and Chapter 7 gives the final remarks.

### 2 ENSEMBLE MONTE CARLO METHOD

The Monte Carlo<sup>1</sup> method can be considered as a very general and established mathematical tool for the solution of a large variety of problems, being essentially based on the selection of random numbers (JACOBONI; LUGLI, 1989). The technique has been subject of numerous books and reviews (CASHWELL; EVERETT, 1959; RUBIN-STEIN, 1981; JACOBONI; REGGIANI, 1983; JACOBONI; LUGLI, 1989; HESS, 1991; KALOS; WHITLOCK, 2008), and it is widely employed in many scientific fields, such as chemistry (DOLL; FREEMAN, 1994), physics (BINDER, 1995), biology (MANLY, 2007), finances (GLASSERMAN, 2003), etc.

With respect to the modeling and simulation of electronic devices, the application of the Monte Carlo method was firstly introduced by Kurosawa (1966), aiming to study high-field charge transport in semiconductors. Alike typical transport applications, the idea behind the simulation of charge transport problems through the Monte Carlo method is to keep track of a particle for a certain amount of time and emulate its free motion within a medium. The particle random walk is then subject to instantaneous random scattering events, which may or may not change either its trajectory or properties. In this way, the algorithm basically consists of generating random free flight times for each particle, choosing the type of scattering occurring at the end of the free flight, changing the final energy and momentum of the particle after scattering, and then repeating the procedure for the next free flight (VASILESKA; GOODNICK, 2002).

By simulating a one-particle system for a long enough time, one can gather statistics about the physical quantities of interest, such as the single particle distribution function, particle average energy, and the particle average drift velocity. This approach is known as *single-particle* Monte Carlo and it is appropriated for the calculation of steady-state carrier transport under uniform electric fields, such as the characterization of the charge transport in bulk materials. On the other hand, if the simulation is extended to an ensemble of particles — and the ensemble is representative of the entire physical system —, non-stationary time-dependent evolution of the carrier distribution under the influence of a time-dependent driving force can be simulated (VASILESKA; GOODNICK, 2002). The latter approach is the so-called *ensemble* Monte Carlo method and it is more useful for device simulation, where non-uniform electric fields typically occur.

<sup>&</sup>lt;sup>1</sup>The origin of the term comes from the gambling casinos at the ward of Monte Carlo, in the city-state of Monaco. The method demands many repetitions of a random process, similar to what occurs in a casino, which wins against players on average (ROBERT, 2014).

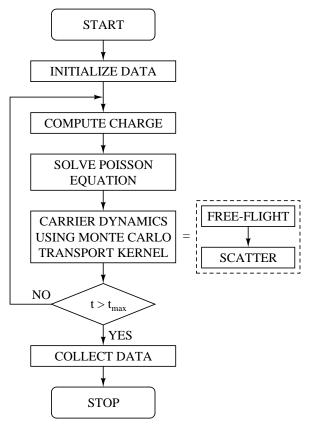

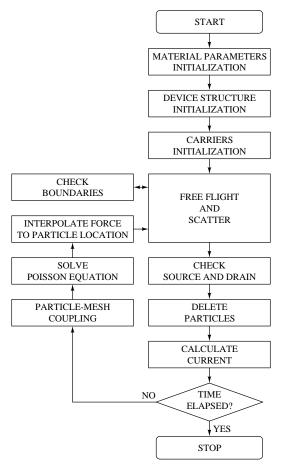

Figure 2.1: Flowchart of a typical ensemble Monte Carlo device simulation.

Source: Adapted from Vasileska, Raleva and Goodnick (2010b).

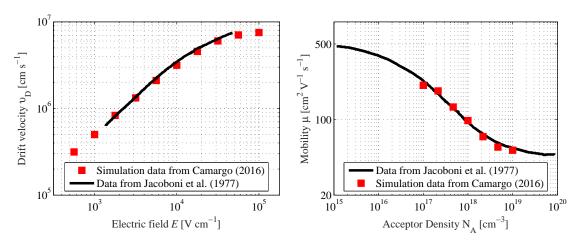

The flowchart of a typical ensemble Monte Carlo simulation is depicted in Figure 2.1. As one can note, a Monte Carlo device simulation involves supplementary steps rather than just generating free-flight times and tracking particles. Since the Monte Carlo method is presented here in a conceptual manner, an extensive analysis of these additional features is out of the scope of this thesis. Nevertheless, an alternative literature, which covers the subject, is suggested to the reader. The work of Gross (1999) presents a full description of a Monte Carlo simulator for *n*-channel MOS devices, addressing specific aspects of each stage of the simulation. Besides the free flight-scatter kernel, the author describes in details the routines for carrier and parameters' initialization, charge assignment, Poisson equation solving, as well as particle-mesh coupling. The changes in the semiconductor band structure needed to adapt the tool for the simulation of *p*-channel MOS devices is covered in the work of Camargo (2016).

In this context, the following sections aim to present the essential characteristics that compose a typical Monte Carlo simulator. Section 2.1 introduces the scattering theory, also detailing the most relevant scattering processes which affect carrier transport in silicon. Section 2.2 addresses the free-flight time generation algorithm and the role of the

self-scattering. Section 2.3, in turn, presents the dynamics of the scattering events, as well as the methodology for choosing the final state after their occurrence. Next, Section 2.4 provides an overview about the simulation flow utilizing a synchronous scheme to coordinate the particle motion over a fixed time step, which allows the Monte Carlo method to be applied for multiple particles in a system. Finally, Section 2.5 details the simulation of semiconductor devices by employing the ensemble Monte Carlo method. The simulation flow is discussed in details and some results are presented.

# 2.1 Scattering Rates

In a semiconductor, free carriers interact with the crystal and with each other through a variety of scattering processes that modify the energy and momentum of the particles (VASILESKA; GOODNICK; KLIMECK, 2010). The probability of a carrier undergo a scattering event and experience a transition from some initial state  $\mathbf{k}$  to some final state  $\mathbf{k}'$  is quantified by the scattering rate. Basically, this probability depends on the type of carrier (electron or hole), the carrier energy, and the type of scattering mechanism, also varying from material to material.

In the context of a Monte Carlo simulation, scattering rates are calculated quantum mechanically via the solution of the time-dependent Schrödinger equation, evaluated using first-order perturbation theory (HE, 2000). Thus, the transition rate per unit time from an initial state  $\mathbf{k}$  in band n to a final state  $\mathbf{k}'$  in band m for the  $j^{\text{th}}$  scattering mechanism is given by the expression (VASILESKA; GOODNICK; KLIMECK, 2010)

$$\Gamma_{j}(n,\mathbf{k};m,\mathbf{k}') = \frac{2\pi}{\hbar} \left| \left\langle m,\mathbf{k}' \middle| V_{j}(\mathbf{r}) \middle| n,\mathbf{k} \right\rangle \right|^{2} \delta(E_{\mathbf{k}'} - E_{\mathbf{k}} \pm \hbar \omega), \tag{2.1}$$

which is known as Fermi's Golden Rule. In Equation 2.1,  $V_j(\mathbf{r})$  is the scattering potential of the process, and  $E_{\mathbf{k}}$  and  $E_{\mathbf{k}'}$  are the initial and final state energies of the particle, respectively (VASILESKA; GOODNICK; KLIMECK, 2010). The matrix element  $|\langle m, \mathbf{k}'|V_j(\mathbf{r})|n, \mathbf{k}\rangle|^2$  incorporates the momentum conservation, while the delta function  $\delta$  accounts for the energy conservation during the scattering process (HE, 2000). The total scattering rate out of state  $\mathbf{k}$  is found by summing over all the final states  $\mathbf{k}'$  for a given

band, which results in (VASILESKA; GOODNICK; KLIMECK, 2010)

$$\Gamma_{j}(n,\mathbf{k}) = \frac{2\pi}{\hbar} \sum_{m,\mathbf{k}'} \left| \left\langle m,\mathbf{k}' \middle| V_{j}(\mathbf{r}) \middle| n,\mathbf{k} \right\rangle \right|^{2} \delta(E_{\mathbf{k}'} - E_{\mathbf{k}} \pm \hbar \omega), \tag{2.2}$$

or in the integral form (HATHWAR, 2011),

$$\Gamma_{\mathbf{j}}(n,\mathbf{k}) = \frac{\Omega}{(2\pi)^3} \int_0^{2\pi} d\phi \int_0^{\pi} \theta d\theta \int_0^{\infty} \Gamma_{\mathbf{j}}(n,\mathbf{k};m,\mathbf{k}') \mathbf{k}'^2 d\mathbf{k}'. \tag{2.3}$$

Here,  $\Omega$  is the crystal volume,  $\phi$  is the polar angle, and  $\theta$  is the azimuthal angle between  $\mathbf{k}$  and  $\mathbf{k}'$ .

The result obtained from Equation 2.3 is utilized to calculate the carrier scattering rate due to transitions induced by the different scattering sources present in the crystal. In silicon, the most important ones are phonons, impurities, and other carriers (JACOBONI; REGGIANI, 1983), where the former dominates the charge transport at room temperature and high electric fields (HE, 2000).

The interaction between carriers and phonons arises from lattice vibrations, which introduce small shifts in the semiconductor energy bands. Deviations of the bands from the static lattice position due to these small shifts lead to an additional potential that is responsible for the scattering process (FERRY, 2000). Such interactions can be divided into two types: acoustic phonon scattering and optical phonon scattering. Since the scattering potential  $V_j(\mathbf{r})$  is characteristic of each scattering mechanism, the matrix element for acoustic and optical phonon scattering is distinct from each other.

For acoustic phonon scattering, the matrix element is given by (FERRY, 2000)

$$\left| \left\langle m, \mathbf{k}' \middle| V_{j}(\mathbf{r}) \middle| n, \mathbf{k} \right\rangle \right|^{2} = \frac{E_{ac} k_{B} T}{\rho_{m} \Omega v_{s}^{2}}, \tag{2.4}$$

where  $E_{ac}$  is the acoustic deformation potential,  $k_B$  is the Boltzmann constant, T is the temperature,  $\rho_m$  is the mass density, and  $v_s$  is the sound velocity.

For the non-polar<sup>2</sup> optical phonon scattering, in turn, the matrix element can be written as (FERRY, 1976)

$$\left| \left\langle m, \mathbf{k}' \middle| V_{j}(\mathbf{r}) \middle| n, \mathbf{k} \right\rangle \right|^{2} = \frac{\hbar (D_{t}K)^{2}}{2\rho_{m}\Omega\omega_{0}} \left( N_{q} + \frac{1}{2} \pm \frac{1}{2} \right), \tag{2.5}$$

<sup>&</sup>lt;sup>2</sup>Optical phonon scattering can be either polar or non-polar, depending on the material characteristic. In polar materials (e.g. gallium arsenide, indium phosphide, zinc sulfide, etc.), this mechanism is called *polar* optical phonon scattering.

where  $(D_t K)^2$  is a optical coupling constant, which depends on the optical deformation potential and the phonon wave vector (JACOBONI; REGGIANI, 1983),  $\omega_0$  is the phonon frequency, and  $N_q$  is the phonon occupation factor, represented by the Bose-Einstein distribution as

$$N_{\rm q} = \left[ \exp\left(\frac{\hbar\omega_{\rm q}}{k_{\rm B}T}\right) - 1 \right]^{-1}.$$

(2.6)

In Equation 2.5, the upper sign is for the emission of phonons and the lower sign is for the absorption of phonons by the carriers.

The total scattering rate for both acoustic and non-polar optical phonon scattering mechanisms can be obtained by substituting Equation 2.4 and Equation 2.5, respectively, into Equation 2.1 and then evaluate the integral. This step will not be discussed here but it is presented in details in the work of Hathwar (2011) and Camargo (2016) for electrons and holes, respectively. In addition, an extensive description of the scattering mechanisms which affect charge transport in semiconductor materials can be found in Jacoboni and Lugli (1989, chapter 2).

## 2.2 Free-Flight Time Generation

As already presented, within the Monte Carlo technique the dynamics of the carrier motion is assumed to consist of free flights terminated by instantaneous scattering events, which may change the momentum and energy of the particle (VASILESKA; GOODNICK, 2002). In order to determine the free flight times and simulate this process, however, the scattering probability density for the carrier at hand must be determined. The relationship between the free flight time and the scattering probability is developed in the following.

Let  $\Gamma[\mathbf{k}(t)]dt$  be the probability that a carrier in the state  $\mathbf{k}$  undergoes a scattering event during the time dt. Thus, the probability that a carrier which experienced a scattering event at the time t=0 has not undergone another event after a time t is given by (JACOBONI; REGGIANI, 1983)

$$\exp\left\{-\int_0^t \Gamma[\mathbf{k}(t')]dt'\right\},\tag{2.7}$$

which, basically, gives the probability of the interval [0, t] does not contain a scattering. Consequently, the probability P(t) that a carrier will suffer its next scattering event during dt around t is given by the joint probability (JACOBONI; REGGIANI, 1983)

$$P(t)dt = \Gamma[\mathbf{k}(t)] \exp\left\{-\int_0^t \Gamma[\mathbf{k}(t')]dt'\right\} dt.$$

(2.8)

In this way, random free flight times  $t_r$  can be generated from the probability P(t) utilizing a direct method according to the expression (VASILESKA; GOODNICK, 2002)

$$r = \int_0^{t_{\rm r}} P(t)dt,\tag{2.9}$$

where r is a uniformly distributed random number in the range [0, 1]. By integrating Equation 2.9 with P(t) defined by Equation 2.8, one gets (VASILESKA; GOODNICK, 2002)

$$r = 1 - \exp\left[-\int_0^{t_{\rm r}} \Gamma[\mathbf{k}(t')]dt'\right]. \tag{2.10}$$

In addition, since 1 - r is statistically equivalent to r, Equation 2.10 can be rewritten to its final form

$$-\ln r = \int_0^{t_{\rm r}} \Gamma[\mathbf{k}(t')] dt'. \tag{2.11}$$

Equation 2.11 is the fundamental equation used to generate random free flight times within the Monte Carlo framework, resulting in a random walk process related to the underlying particle distribution function (VASILESKA et al., 2008).

Nevertheless, because of the complexity of the integral at hand, it is impractical to generate stochastic free flight times with the distribution of Equation 2.11 (JACOBONI; REGGIANI, 1983). Therefore, it is worthwhile the application of the so-called *self-scattering* method (REES, 1969). Self-scattering consists of a fictitious scattering mechanism whose scattering probability always adjusts itself in such a way the total scattering probability, i.e., real scattering plus self-scattering, is constant over time (VASILESKA; GOODNICK, 2002). In addition, if a carrier undergoes a self-scattering event, its state after the collision is taken to be equal to its state before the collision, causing the carrier trajectory to continue unperturbed as if no scattering had occurred (JACOBONI; REGGIANI, 1983). In this case, the total scattering probability  $\Gamma$  can be written as

$$\Gamma = \Gamma[\mathbf{k}(t)] + \Gamma_{\text{self}}[\mathbf{k}(t)]. \tag{2.12}$$

where  $\Gamma[\mathbf{k}(t)]$  is the real scattering probability, and  $\Gamma_{\text{self}}[\mathbf{k}(t)]$  is the self-scattering probability. Since now the dependency on time vanishes, Equation 2.11 can be rewritten as

$$-\ln r = \Gamma \int_0^{t_{\rm r}} dt' \tag{2.13}$$

and the integral is trivially evaluated. Thus, free flight times can be obtained directly from the resulting expression

$$t_{\rm r} = -\frac{1}{\Gamma} \ln r. \tag{2.14}$$

The self-scattering technique introduces significant simplification on the free flight time calculation, thus compensating the computer time spent taking care of such fictitious mechanism (JACOBONI; REGGIANI, 1983). One requirement to utilize the self-scattering approach is choosing the total scattering rate  $\Gamma$  so that it exceeds the maximum "real" scattering rate encountered during the simulation (VASILESKA; GOODNICK, 2002).

#### 2.3 Scattering Events

Immediately upon the free flight time generated accordingly the algorithm presented in the previous section elapses, a scattering event takes place. At this point, the scattering mechanism that terminates the free flight must be known. The choice is performed based on the generation of a uniformly distributed random number r between 0 and the total scattering rate  $\Gamma$ , where  $\Gamma$  contains the cumulative scattering rates for the N mechanisms taken into account in the simulation plus the self-scattering, i.e.,

$$\Gamma = \Gamma_{\text{self}}[n, \mathbf{k}] + \Gamma_1[n, \mathbf{k}] + \Gamma_2[n, \mathbf{k}] + \dots + \Gamma_N[n, \mathbf{k}]. \tag{2.15}$$

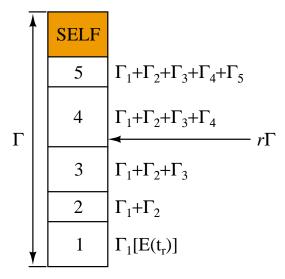

This process is graphically described in Figure 2.2.

Firstly, the product  $r\Gamma$  is compared with the maximum scattering rate for a given energy due to mechanism 1. If the product is smaller than that, mechanism 1 is selected, otherwise  $r\Gamma$  is compared again with the rate for mechanism 1 plus mechanism 2, and so on. In the case of the product  $r\Gamma$  exceeds the maximum cumulative scattering rate for the real mechanisms, then the self-scattering is selected. Since the latter has a high occurrence probability — chiefly for low energy carriers —, it is usually checked first, for the sake of efficiency (CAMARGO, 2016).

After the scattering mechanism that terminates the particle free-flight being selected, the changes in the particle energy and momentum are treated accordingly. For in-

Figure 2.2: Selection of the type of scattering terminating a free flight in the Monte Carlo algorithm. In this particular case, mechanism 4 should be selected.

Source: Adapted from Vasileska, Raleva and Goodnick (2008).

stance, if the scattering process at hand is elastic, which is the case for the acoustic phonon scattering, only the momentum is updated, since the particle energy remains unaltered. On the other hand, if the process is taken to be inelastic, both energy and momentum of the particle are modified.

#### 2.4 Ensemble Monte Carlo Simulation

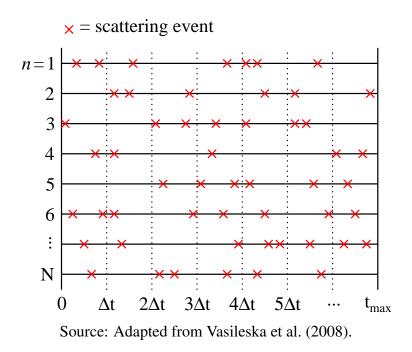

The techniques presented so far can be used for tracking either a single particle or multiple particles in a system. However, in order to get improved statistics — even with reduced simulation times —, as well as for transient simulations, the use of an ensemble of particles is preferred (VASILESKA; GOODNICK, 2002). In this case, the Monte Carlo algorithm is performed for each particle at once, and a fixed time step  $\Delta t$  is introduced in order to synchronize the motion of the particles. Basically, the time step represents the amount of time the algorithm spend keeping track of one particle before proceeding to the next one.

Figure 2.3 depicts the dynamic of a ensemble Monte Carlo simulation. In the beginning, i.e., time instant t = 0, the Poisson's equation is solved for the equilibrium condition, in order to provide initial values for the electric field and electric potential. After that, a random free flight time is generated for the first particle in the ensemble, and its motion is performed accordingly. Nevertheless, if the free flight time is larger than the

Figure 2.3: Ensemble Monte Carlo simulation in which a time step  $\Delta t$  is introduced over which the motion of particles is synchronized.

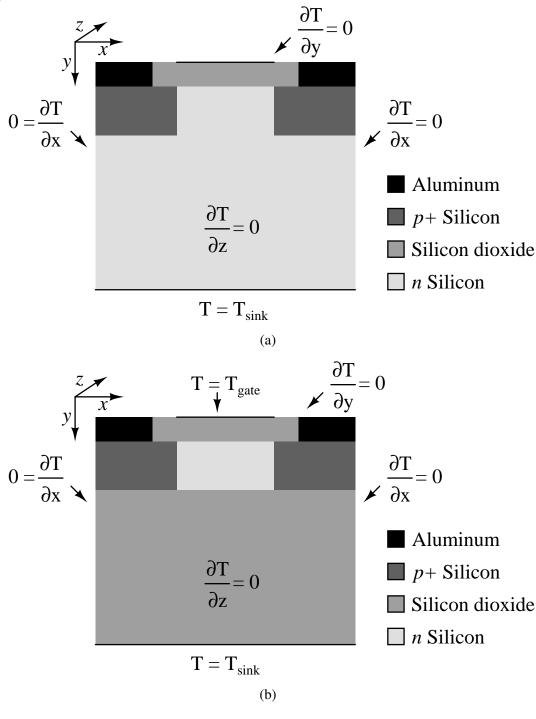

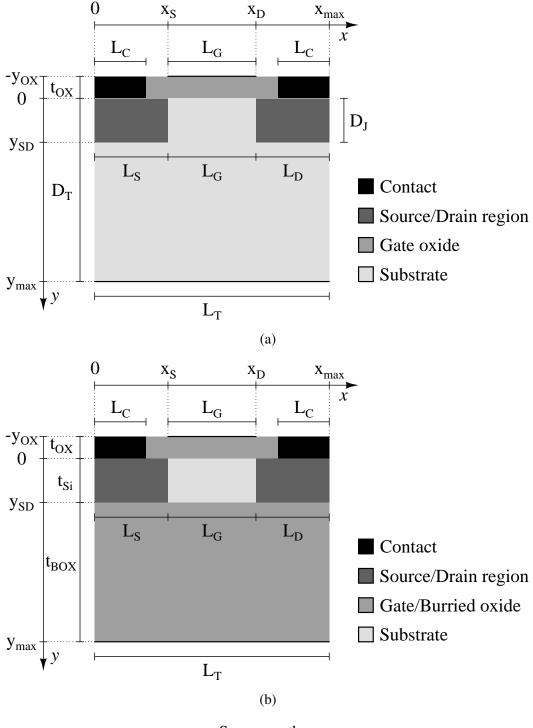

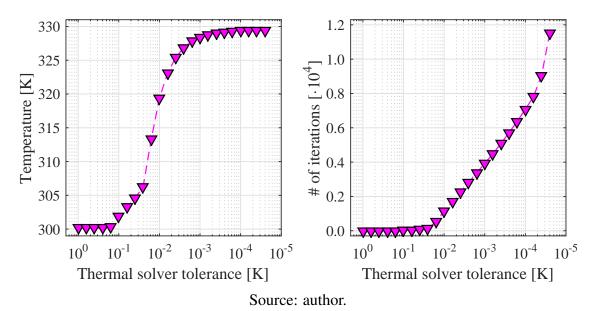

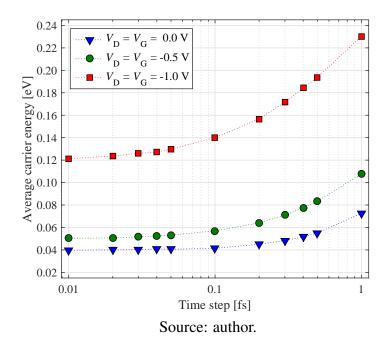

time step, the particle is treated up to the end of the time step, and the remaining free flight time is stored to be utilized by the particle at hand when the next time step is performed.