## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

## ÁDRIA BARROS DE OLIVEIRA

# Applying Dual-Core Lockstep in Embedded Processors to Mitigate Radiation-induced Soft Errors

Thesis presented in partial fulfillment of the requirements for the degree of Master of Microeletronics

Advisor: Prof<sup>a</sup>. Dr<sup>a</sup>. Fernanda Lima Kastensmidt

Porto Alegre November 2017

# CIP — CATALOGAÇÃO NA PUBLICAÇÃO

Oliveira, Ádria Barros de

Applying Dual-Core Lockstep in Embedded Processors to Mitigate Radiation-induced Soft Errors / Ádria Barros de Oliveira. – Porto Alegre: PGMICRO da UFRGS, 2017.

95 f.: il.

Dissertação (mestrado) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2017. Advisor: Fernanda Lima Kastensmidt.

1. Embedded Processors Reliability. 2. Fault Tolerance. 3. Lockstep. 4. Soft Errors. 5. Radiation Experiments. 6. Fault Injection. I. Kastensmidt, Fernanda Lima. II. Applying Dual-Core Lockstep in Embedded Processors to Mitigate Radiation-induced Soft Errors.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas

Coordenadora do PGMICRO: Prof<sup>a</sup>. Fernanda Lima Kastensmidt

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **ACKNOWLEDGMENT**

I would like to thanks my parents, Dinancy and Adons, that have always taken care of me. I am grateful for all support and learning that allowed me to be who I am. Thank you for believing in me even when I thought that I was not capable. Thank you for all unconditional love.

Jeckson, thank you for all love and support, mainly on the hard days. Thank you for being my safe harbor, for being at my side and do not give up on me. You are so much more than a boyfriend. You are my love, my partner, and my friend, and I am so thankful for that. Thank you for making me so happy. I love you.

Gennaro, Ygor, and Filipe I would like to thanks for all you have done for me. I really appreciate our friendship.

Many thanks to all my friends that even far supported me. "Friends are the family that we choose for ourselves", and I chose you all.

I would like to express my special thanks of gratitude to my advisor Fernanda who gave me the opportunity to work on this project. Thank you for trusting in me and for all your dedication and guidance. You are an inspiration for me.

A heartfelt thank you to all.

#### **ABSTRACT**

The embedded processors operating in safety- or mission-critical systems are not allowed to fail. Any failure in such applications could lead to unacceptable consequences as life risk or significant damage to property or environment. Concerning faults originated by the radiation-induced soft errors, the embedded systems operating in aerospace applications are particularly susceptible. However, the radiation effects can also be observed at ground level. Soft errors affect processors by modifying values stored in memory elements, such as registers and data memory. These faults may lead the processor to execute an application incorrectly, generating output errors or leading hangs and crashes in the system. The recent advances in embedded systems concern the integration of hard-core processors and FPGAs. Such devices, called All Programmable System-on-Chip (AP-SoC), are also susceptible to radiation effects. Aiming to address this fault tolerance problem this work presents a Dual-Core LockStep (DCLS) as a fault tolerance technique to mitigate radiation-induced faults affecting processors embedded into APSoCs. Lockstep is a method based on redundancy used to detect and correct soft errors. The proposed DCLS is implemented in a hard-core ARM Cortex-A9 embedded into a Zynq-7000 APSoC. The approach efficiency was validated not only on applications running in baremetal but also on top of FreeRTOS systems. Heavy ions experiments and fault injection emulation were performed to analyze the system susceptibility to bit-flips. The obtained results show that the approach is able to decrease the system cross section with a high rate of protection. The DCLS system successfully mitigated up to 78% of the injected faults. Software optimizations were also evaluated to understand the trade-offs between performance and reliability better. By the analysis of different software partitions, it was observed that the execution time of an application block must to be much longer than the verification time to achieve fewer performance penalties. The compiler optimizations assessment demonstrate that using O3 level increases the application vulnerability to soft errors. Because O3 handles more registers than other optimizations, the system is more susceptible to faults. On the other hand, results from radiation experiments show that O3 level provides a higher Mean Workload Between Failures (MWBF). As the application runs faster, more data are correctly computed before an error occurrence.

**Keywords:** Embedded Processors Reliability. Fault Tolerance. Lockstep. Soft Errors. Radiation Experiments. Fault Injection.

# Aplicando Dual-Core Lockstep em Processadores Embarcados para Mitigar Falhas Transientes Induzidas por Radiação

#### **RESUMO**

Os processadores embarcados operando em sistemas de segurança ou de missão crítica não podem falhar. Qualquer falha neste tipo de aplicação pode levar a consequências inaceitáveis, como risco de vida ou danos à propriedade ou ao meio ambiente. Os sistemas embarcados que operam em aplicações aeroespaciais são sucetíveis à falhas transientes induzidas por radiação. Entretanto, os efeitos de radiação também podem ser observados ao nível do solo. Falhas transientes afetam os processadores modificando os valores armazenados em elementos de memória, tais como registradores e memória de dados. Essas falhas podem levar o processador a executar incorretamente a aplicação, provocando erros na saída ou travamentos no sistema. Os avanços recentes em processadores embarcados concistem na integração de processadores hard-core e FPGAs. Tais dispositivos, comumente chamados de Sistemas-em-Chip Totalmente Programáveis (APSoCs), também são sucetíveis aos efeitos de radiação. Com objetivo de minimizar esse problema de tolerância a falhas, este trabalho apresenta um Dual-Core LockStep (DCLS) como uma técnica de tolerância para mitigar falhas induzidas por radiação que afetam processadores embarcados em APSoCs. Lockstep é um método baseado em redundância usado para detectar e corrigir falhas transientes. O DCLS proposto é implementado em um processador ARM Cortex-A9 hard-core embarcado no APSoC Zynq-7000. A eficiência da abordagem implementada foi validada tanto em aplicações executando em bare-metal como no sistema operacional FreeRTOS. Experimentos com íons pesados e emulação de falhas por injeção foram executados para analisar a sucetibilidade do sistema a inversão de bits. Os resultados obtidos mostram que a abordagem é capaz de diminuir a seção de choque do sistema com uma alta taxa de proteção. O sistema DCLS mitigou com sucesso até 78% das falhas injetadas. Otimizações de software também foram avaliadas para uma melhor compreenção dos trade-offs entre desempenho e confiabilidade. Através da análise de diferentes partições de software, observou-se que o tempo de execução de um bloco da aplicação deve ser muito maior que o tempo de verificação para que se obtenha menor impacto em desempenho. A avaliação de otimizações de compilador demonstrou que utilizar o nível O3 aumenta a vulnerabilidade da aplicação à falhas transientes. Como o O3 requer o uso de mais registradores que os otros níveis de otimização, o sistema se torna mais sucetível à falhas. Por outro lado, os resultados dos experimentos de radiação apontam que a aplicação compilada com nível O3 obtém maior Carga de Trabalho Média Entre Falhas (MWBF). Como a aplicação executa mais rápido, mais dados são computados corretamente antes da ocorrência de um erro.

**Palavras-chave:** Confiabilidade de processadores embarcados, Tolerância a falhas, Lockstep, Falhas Transientes, Experimentos de radiação, Injeção de Falhas.

## LIST OF ABBREVIATIONS AND ACRONYMS

AES Advanced Encryption Standard

APSoC All Programmable System-on-Chip

BRAM Block RAM

CPU Central Processing Unit

CRT Chip-level Redundant Threading

CRTR Chip-level Redundantly Threaded multiprocessor with Recovery

COTS Commercial Off The Shelf

CFC Control Flow Checking

DCLS\_BR\_DDR DCLS accessing BRAM and DDR memories

DCLS\_BR DCLS accessing BRAM memory only

DUT Device Under Test

DSP Digital Signal Processor

DCLS Dual-Core LockStep

DMR Dual Modular Redundancy

DWC Duplication With Comparison

DCC Dynamic Core Coupling

ESA European Space Agency

ECC Error Correction Code

EDAC Error Detection and Correction

EDC Error Detection Code

FPGA Field Programmable Gate Array

FSM Finite-State Machine

FF Flip-Flop

FPU Floating Point Unit

GPU Graphics Processing Unit

HDL Hardware Description Language

HPC High Performance Computing

HETA Hybrid Error-detection Technique using Assertions

IU Integer Unit

IP Intellectual Property

LAFN-USP Laboratório Aberto de Física Nuclear at Universidade de São Paulo

LET Linear Energy Transfer

LR Link Register

LANL Los Alamos National Laboratory

LUT Look-Up Table

MxM Matrix Multiplication

MWBF Mean Workload Between Failures

MBU Multiple Bit Upset

MPSoC Multiprocessor System-on-Chips

NMR N-modular redundancy

OCM On-Chip Memory

OS Operating Systems

PS Processing System

PC Program Counter

PL Programmable Logic

Rad-Hard Radiation Hardened

RTL Resistor-Transistor Logic

S-SETA Selective Software-only Error-detection Technique using Assertions

SDC Silent Data Corruption

SRT Simultaneous and Redundantly Threaded

SMT Simultaneous Multithreading

SRTR Simultaneously and Redundantly Threaded processors with Recovery

SBU Single Bit Upset

SEE Single Event Effect

SEFI Single Event Functional Interrupt

SEL Single Event Latch-up

SEU Single Event Upset

SET Single Event Transient

SRMT Software-based Redundant Multi-Threading

SIHFT Software-Implemented Hardware Fault Tolerance

SP Stack Pointer

SoC System-on-Chip

TLR Thread-Level Redundancy

TMR Triple Modular Redundancy

VP Verification Point

# LIST OF FIGURES

| Figure 2.1 Possible effects of soft errors in processors                                                                | 30  |

|-------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2.2 Diagram of soft errors effects in processors                                                                 |     |

| Figure 2.3 Diagram of TMR with single Voter.                                                                            |     |

| Figure 2.4 Diagram of TMR with triplicate Voters.                                                                       |     |

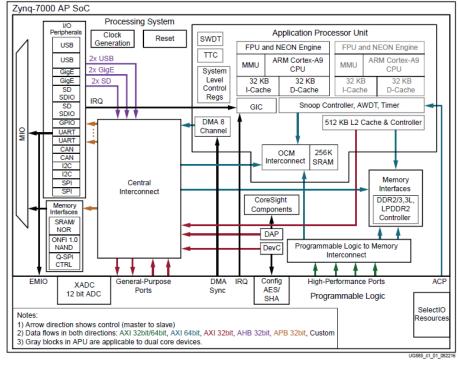

| Figure 3.1 Zynq-7000 APSoC Overview                                                                                     | 44  |

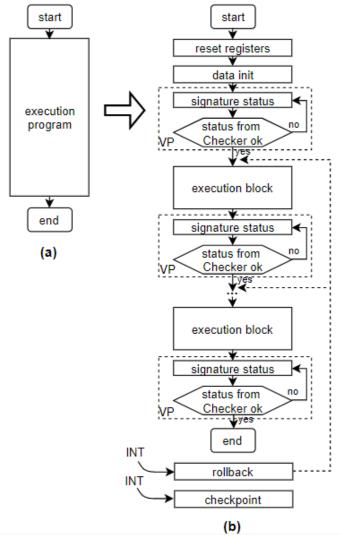

| Figure 3.2 Proposed lockstep architecture for dual-core ARM Cortex-A9 embedded into Zynq-7000 APSoC.                    | 45  |

| Figure 3.3 Lockstep Functional Flow for ARM Cortex-A9 dual-core: (a) original                                           |     |

| code, (b) code with lockstep technique running in both CPUs                                                             | 46  |

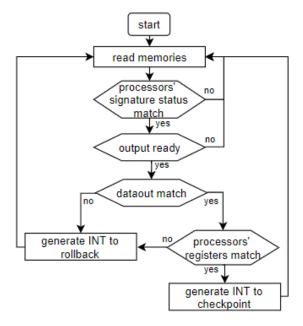

| Figure 3.4 Checker module functional flow                                                                               | 48  |

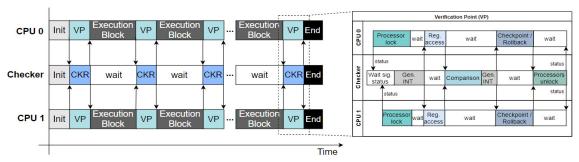

| Figure 3.5 Dual-Core Lockstep execution overview                                                                        | 51  |

| Figure 4.1 Fault injection experiment setup                                                                             | 55  |

| Figure 4.2 Fault injection procedure flow                                                                               | 55  |

| Figure 4.3 View of fault injection experiment setup                                                                     | 56  |

| Figure 4.4 Radiation experiment setup                                                                                   | 58  |

| Figure 4.5 Perspective of radiation experiment setup performed at LAFN-USP: (a)                                         |     |

| View inside of the chamber; (b) View of the laboratory                                                                  | 59  |

| Figure 5.1 Execution time in clock cycles (c.c.) for performing the AES block                                           |     |

| partitions and the Verification Points                                                                                  | 72  |

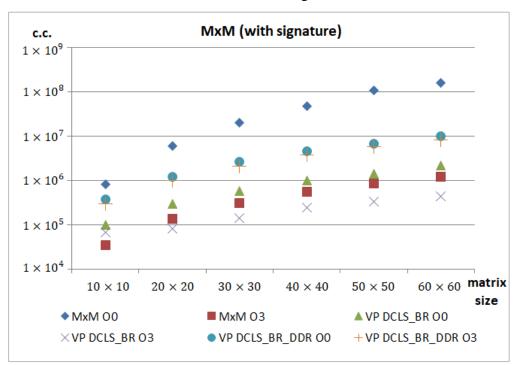

| Figure 5.2 Execution time in clock cycles (c.c.) for performing the Matrix Multi-                                       |     |

| plication in different sizes and the Verification Points                                                                | 72  |

| Figure 5.3 Execution time in clock cycles (c.c.) for performing the Matrix Multi-                                       | 72  |

| plication in different sizes and the Verification Points with signature                                                 | / 3 |

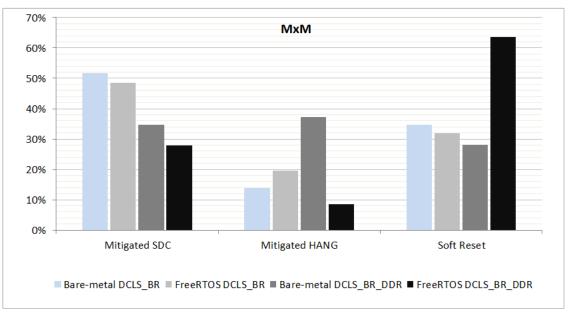

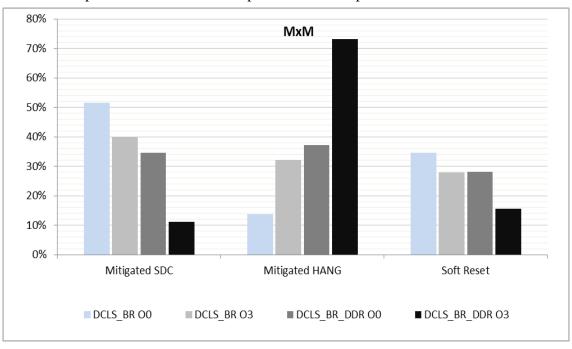

| Figure 5.4 Percentage of errors classification for Test Case II experimental designs                                    | 77  |

| with 40x40 Matrix Multiplication benchmark                                                                              | / / |

| Figure 5.5 Distribution of mitigated faults in DCLS designs for Test Case II with 40x40 Matrix Multiplication benchmark | 77  |

| Figure 5.6 Percentage of errors classification for Test Case II experimental designs                                    | / / |

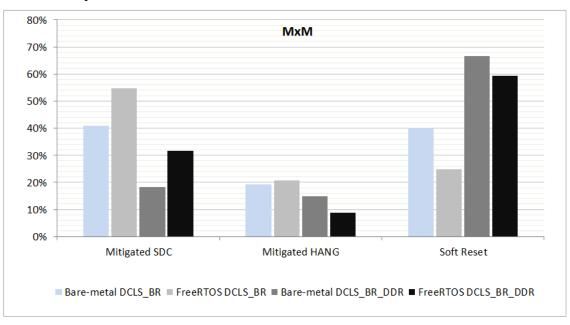

| with 60x60 Matrix Multiplication benchmark                                                                              | 78  |

| Figure 5.7 Distribution of mitigated faults in DCLS designs for Test Case II with                                       | 7 0 |

|                                                                                                                         | 78  |

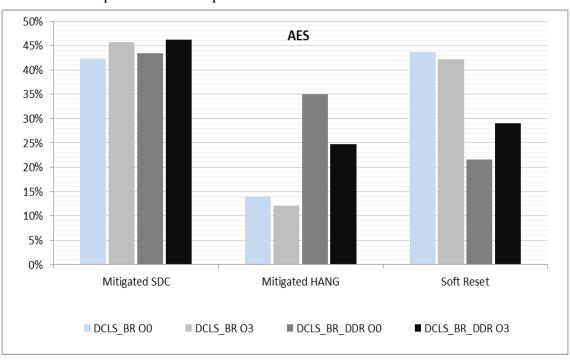

| Figure 5.8 Percentage of errors classification for Test Case III experimental designs                                   |     |

| with AES benchmark compiled with both optimizations                                                                     | 81  |

| Figure 5.9 Distribution of mitigated faults in DCLS designs for Test Case III with                                      |     |

| AES benchmark compiled with both optimizations                                                                          | 81  |

| Figure 5.10 Percentage of errors classification for Test Case III experimental de-                                      |     |

| signs with 40x40 Matrix Multiplication benchmark compiled with both opti-                                               |     |

| mizations                                                                                                               | 82  |

| Figure 5.11 Distribution of mitigated faults in DCLS designs for Test Case III with                                     |     |

| 40x40 Matrix Multiplication benchmark compiled with both optimizations                                                  | 82  |

# LIST OF TABLES

| Table 2.1 Overview of the techniques classification                                   | 39   |

|---------------------------------------------------------------------------------------|------|

| Table 4.1 Error classification description                                            | 56   |

| Table 4.2 Test Cases description                                                      | 63   |

| Table 5.1 Resource usage of each implemented design                                   | 67   |

| Table 5.2 Description of used registers for each benchmark in different compiler      |      |

| optimizations                                                                         | 67   |

| Table 5.3 Performance analysis for each design running different matrix sizes         | 68   |

| Table 5.4 Performance analysis for each design running bare-metal and on FreeRTC      | S 69 |

| Table 5.5 Performance analysis for each design performing Matrix Multiplication       |      |

| (40x40) and AES benchmarks compiled using O0 and O3 optimizations                     | 70   |

| Table 5.6 Fault injection analysis for each design running different matrix sizes for |      |

| Test Case I                                                                           | 75   |

| Table 5.7 Experimental results from the heavy ions test campaign in Zynq-7000         |      |

| device for Test Case IV with Matrix Multiplication (40x40)                            | 84   |

| 1 '                                                                                   |      |

# CONTENTS

| 1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 1.1 Main Objective and Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23                                                                                     |

| 1.2 Work Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24                                                                                     |

| 2 BACKGROUND AND STATE OF THE ART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 25                                                                                     |

| 2.1 Embedded Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25                                                                                     |

| 2.2 Software Optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 26                                                                                     |

| 2.3 Embedded Operating Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27                                                                                     |

| 2.4 Radiation Effects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27                                                                                     |

| 2.4.1 Faults, Errors and Failures Concepts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28                                                                                     |

| 2.4.2 Single Event Upsets in Embedded Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29                                                                                     |

| 2.5 All Programmable System-on-Chip Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 32                                                                                     |

| 2.6 Fault-Tolerance Techniques in Embedded Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 33                                                                                     |

| 2.6.1 Hardware-based techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33                                                                                     |

| 2.6.2 Software-based techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 34                                                                                     |

| 2.6.3 Hybrid-based techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 37                                                                                     |

| 2.6.4 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38                                                                                     |

| 2.7 Related Works about Lockstep Technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39                                                                                     |

| 3 PROPOSED DUAL-CORE LOCKSTEP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 43                                                                                     |

| 3.1 Case Study                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 43                                                                                     |

| 3.2 Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 44                                                                                     |

| 3.3 Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 45                                                                                     |

| 3.3.1 Checker Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 47                                                                                     |

| 3.3.2 Checkpoint and Rollback Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 49                                                                                     |

| 3.4 DCLS approach overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                        |

| 4 EXPERIMENTAL METHODOLOGY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53                                                                                     |

| 4 EXPERIMENTAL METHODOLOGY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 54                                                                                     |

| 4.1 Fault Injection Experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 54<br>56                                                                               |

| <ul><li>4.1 Fault Injection Experiments</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54<br>56<br>60                                                                         |

| <ul><li>4.1 Fault Injection Experiments</li><li>4.2 Radiation Experiments</li><li>4.3 Evaluated Applications</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 54<br>60<br>60                                                                         |

| <ul> <li>4.1 Fault Injection Experiments</li> <li>4.2 Radiation Experiments</li> <li>4.3 Evaluated Applications</li> <li>4.3.1 Software Optimizations</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 54<br>60<br>60                                                                         |

| <ul> <li>4.1 Fault Injection Experiments</li> <li>4.2 Radiation Experiments</li> <li>4.3 Evaluated Applications</li> <li>4.3.1 Software Optimizations</li> <li>4.3.1.1 Optimization in Software Partition</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                    | 54<br>60<br>60<br>60                                                                   |

| <ul> <li>4.1 Fault Injection Experiments</li> <li>4.2 Radiation Experiments</li> <li>4.3 Evaluated Applications</li> <li>4.3.1 Software Optimizations</li> <li>4.3.1.1 Optimization in Software Partition</li> <li>4.3.1.2 Optimization in Software Compilation</li> </ul>                                                                                                                                                                                                                                                                                                                                                              | 54<br>60<br>60<br>61                                                                   |

| 4.1 Fault Injection Experiments 4.2 Radiation Experiments 4.3 Evaluated Applications 4.3.1 Software Optimizations 4.3.1.1 Optimization in Software Partition 4.3.1.2 Optimization in Software Compilation 4.3.2 Test Cases Overview 5 RESULTS                                                                                                                                                                                                                                                                                                                                                                                           | 54<br>60<br>60<br>61<br>62                                                             |

| 4.1 Fault Injection Experiments 4.2 Radiation Experiments 4.3 Evaluated Applications 4.3.1 Software Optimizations 4.3.1.1 Optimization in Software Partition 4.3.1.2 Optimization in Software Compilation 4.3.2 Test Cases Overview                                                                                                                                                                                                                                                                                                                                                                                                     | 54<br>60<br>60<br>61<br>62<br>65                                                       |

| 4.1 Fault Injection Experiments 4.2 Radiation Experiments 4.3 Evaluated Applications 4.3.1 Software Optimizations 4.3.1.1 Optimization in Software Partition 4.3.1.2 Optimization in Software Compilation 4.3.2 Test Cases Overview 5 RESULTS 5.1 Implementation Analysis                                                                                                                                                                                                                                                                                                                                                               | 54<br>60<br>60<br>61<br>62<br>65<br>65                                                 |

| 4.1 Fault Injection Experiments 4.2 Radiation Experiments 4.3 Evaluated Applications 4.3.1 Software Optimizations 4.3.1.1 Optimization in Software Partition 4.3.1.2 Optimization in Software Compilation 4.3.2 Test Cases Overview 5 RESULTS 5.1 Implementation Analysis 5.1.1 Area assessment                                                                                                                                                                                                                                                                                                                                         | 54<br>60<br>60<br>61<br>62<br>65<br>65                                                 |

| 4.1 Fault Injection Experiments 4.2 Radiation Experiments 4.3 Evaluated Applications 4.3.1 Software Optimizations 4.3.1.1 Optimization in Software Partition 4.3.1.2 Optimization in Software Compilation 4.3.2 Test Cases Overview 5 RESULTS 5.1 Implementation Analysis 5.1.1 Area assessment 5.1.2 Performance assessment                                                                                                                                                                                                                                                                                                            | 54<br>60<br>61<br>62<br>65<br>65<br>65                                                 |

| 4.1 Fault Injection Experiments 4.2 Radiation Experiments 4.3 Evaluated Applications 4.3.1 Software Optimizations 4.3.1.1 Optimization in Software Partition 4.3.1.2 Optimization in Software Compilation 4.3.2 Test Cases Overview 5 RESULTS 5.1 Implementation Analysis 5.1.1 Area assessment 5.1.2 Performance assessment 5.1.2.1 Test Case I Analysis 5.1.2.2 Test Case II Analysis                                                                                                                                                                                                                                                 | 54<br>60<br>60<br>61<br>62<br>65<br>65<br>65                                           |

| 4.1 Fault Injection Experiments 4.2 Radiation Experiments 4.3 Evaluated Applications 4.3.1 Software Optimizations 4.3.1.1 Optimization in Software Partition 4.3.1.2 Optimization in Software Compilation 4.3.2 Test Cases Overview 5 RESULTS 5.1 Implementation Analysis 5.1.1 Area assessment 5.1.2 Performance assessment 5.1.2.1 Test Case I Analysis                                                                                                                                                                                                                                                                               | 54<br>60<br>60<br>61<br>65<br>65<br>65<br>67<br>68                                     |

| 4.1 Fault Injection Experiments 4.2 Radiation Experiments 4.3 Evaluated Applications 4.3.1 Software Optimizations 4.3.1.1 Optimization in Software Partition 4.3.1.2 Optimization in Software Compilation 4.3.2 Test Cases Overview 5 RESULTS 5.1 Implementation Analysis 5.1.1 Area assessment 5.1.2 Performance assessment 5.1.2.1 Test Case I Analysis 5.1.2.2 Test Case II Analysis 5.1.2.3 Test Case III Analysis 5.1.2.4 Software Partition Evaluation                                                                                                                                                                            | 54<br>60<br>61<br>65<br>65<br>65<br>65<br>67<br>68                                     |

| 4.1 Fault Injection Experiments 4.2 Radiation Experiments 4.3 Evaluated Applications 4.3.1 Software Optimizations 4.3.1.1 Optimization in Software Partition 4.3.1.2 Optimization in Software Compilation 4.3.2 Test Cases Overview 5 RESULTS 5.1 Implementation Analysis 5.1.1 Area assessment 5.1.2 Performance assessment 5.1.2.1 Test Case I Analysis 5.1.2.2 Test Case II Analysis 5.1.2.3 Test Case III Analysis                                                                                                                                                                                                                  | 54<br>60<br>60<br>61<br>65<br>65<br>65<br>65<br>67<br>68                               |

| 4.1 Fault Injection Experiments 4.2 Radiation Experiments 4.3 Evaluated Applications 4.3.1 Software Optimizations 4.3.1.1 Optimization in Software Partition 4.3.1.2 Optimization in Software Compilation 4.3.2 Test Cases Overview 5 RESULTS 5.1 Implementation Analysis 5.1.1 Area assessment 5.1.2 Performance assessment 5.1.2.1 Test Case I Analysis 5.1.2.2 Test Case III Analysis 5.1.2.3 Test Case III Analysis 5.1.2.4 Software Partition Evaluation 5.2 Fault Injection Experiments                                                                                                                                           | 54<br>60<br>60<br>61<br>65<br>65<br>65<br>65<br>67<br>69<br>70                         |

| 4.1 Fault Injection Experiments 4.2 Radiation Experiments 4.3 Evaluated Applications 4.3.1 Software Optimizations 4.3.1.1 Optimization in Software Partition 4.3.1.2 Optimization in Software Compilation 4.3.2 Test Cases Overview 5 RESULTS 5.1 Implementation Analysis 5.1.1 Area assessment 5.1.2 Performance assessment 5.1.2.1 Test Case I Analysis 5.1.2.2 Test Case III Analysis 5.1.2.3 Test Case III Analysis 5.1.2.4 Software Partition Evaluation 5.2 Fault Injection Experiments 5.2.1 Evaluation of Test Case I                                                                                                           | 54<br>60<br>60<br>61<br>65<br>65<br>65<br>67<br>68<br>67<br>70<br>70                   |

| 4.1 Fault Injection Experiments 4.2 Radiation Experiments 4.3 Evaluated Applications 4.3.1 Software Optimizations 4.3.1.1 Optimization in Software Partition 4.3.1.2 Optimization in Software Compilation 4.3.2 Test Cases Overview 5 RESULTS 5.1 Implementation Analysis 5.1.1 Area assessment 5.1.2 Performance assessment 5.1.2.1 Test Case I Analysis 5.1.2.2 Test Case III Analysis 5.1.2.3 Test Case III Analysis 5.1.2.4 Software Partition Evaluation 5.2 Fault Injection Experiments 5.2.1 Evaluation of Test Case II 5.2.2 Evaluation of Test Case II 5.2.3 Evaluation of Test Case II 5.2.3 Evaluation of Test Case II       | 54<br>60<br>60<br>65<br>65<br>65<br>65<br>67<br>68<br>69<br>70<br>70                   |

| 4.1 Fault Injection Experiments 4.2 Radiation Experiments 4.3 Evaluated Applications 4.3.1 Software Optimizations 4.3.1.1 Optimization in Software Partition 4.3.1.2 Optimization in Software Compilation 4.3.2 Test Cases Overview 5 RESULTS 5.1 Implementation Analysis 5.1.1 Area assessment 5.1.2 Performance assessment 5.1.2.1 Test Case I Analysis 5.1.2.2 Test Case II Analysis 5.1.2.3 Test Case III Analysis 5.1.2.4 Software Partition Evaluation 5.2 Fault Injection Experiments 5.2.1 Evaluation of Test Case II 5.2.2 Evaluation of Test Case II                                                                          | 54<br>60<br>60<br>61<br>65<br>65<br>65<br>67<br>69<br>70<br>74<br>75<br>74             |

| 4.1 Fault Injection Experiments 4.2 Radiation Experiments 4.3 Evaluated Applications 4.3.1 Software Optimizations 4.3.1.1 Optimization in Software Partition 4.3.1.2 Optimization in Software Compilation 4.3.2 Test Cases Overview 5 RESULTS 5.1 Implementation Analysis 5.1.1 Area assessment 5.1.2 Performance assessment 5.1.2.1 Test Case I Analysis 5.1.2.2 Test Case III Analysis 5.1.2.3 Test Case III Analysis 5.1.2.4 Software Partition Evaluation 5.2 Fault Injection Experiments 5.2.1 Evaluation of Test Case II 5.2.2 Evaluation of Test Case III 5.2.3 Evaluation of Test Case III 5.2.4 Software Partition Experiments | 54<br>60<br>60<br>61<br>65<br>65<br>65<br>67<br>68<br>69<br>70<br>70<br>74<br>75<br>75 |

| REFERENCES                | 89 |

|---------------------------|----|

| APPENDIX A — PUBLICATIONS | 95 |

#### 1 INTRODUCTION

State-of-the-art computing systems rely on heterogeneous architectures to achieve performance and energy consumption goals. Dependable and safety-critical systems are no exception to this rule. In the last years, new embedded Systems-on-Chips (SoC) based on heterogeneous architectures have been developed to address those requirements. These SoCs, called All Programmable System-on-Chip (APSoC), combine a Field Programmable Gate Array (FPGA) layer with embedded processors. Frequently, commercial APSoCs use SRAM-based FPGA solutions due to the high reconfiguration flexibility, competitiveness costs, and capability of integrating complex systems on the same component. Unfortunately, whilst being able to achieve high performance and energy consumption with low cost, the APSoCs devices are subject to a plethora of issues that may compromise their usage for safety-critical and dependable purposes.

The Safety- and mission-critical applications are not allowed to fail. Aerospace, nuclear, medical and automotive are examples of such systems, where any failure could lead to unacceptable consequences as life risk or significant damage to property or environment. Therefore, protection against faults that provoke errors is demanded. As mentioned, the APSoCs can be suitable for such applications, but the system must be protected with techniques to ensure high reliability.

Concerning faults originated by the radiation-induced soft errors, the embedded systems operating in aerospace applications are particularly susceptible. However, the radiation effects can also be observed at ground level due to interaction with neutron particles present in the atmosphere. Massive doses of radiation can cause several execution problems (QUINN, 2014). With the reduction of the transistor size, modern processors became more susceptible to Single Event Effects (SEE) (BAUMANN, 2005). The particles can interact with silicon, provoking transient pulses in some sensitive areas. Such episodes might lead to Single Event Upset (SEU) – or bit flips – in the sequential logic that could induce errors, generating wrong application's results and other failures in the system, like hangs and crashes (AZAMBUJA; KASTENSMIDT; BECKER, 2014). When the radiation is high enough, it may flip data bits of memory cells, registers, latches, and flip-flops that can lead to errors (DODD et al., 2003). Radiation effects also induce faults in FPGAs. The ones that use SRAM-based technologies are very susceptible to soft errors. As they are composed of millions of SRAM cells used to configure all the synthesized logic, the embedded processors, Digital Signal Processors (DSP), and memories

(SIEGLE et al., 2015). Because APSoCs are not architecturally fault tolerant, as they can be composed of multiple processors cores, Graphics Processing Units (GPU) and a programmable array that are all susceptible to radiation, safety-critical systems making use of that hardware shall present fault tolerance mechanisms.

Several methods have been described in the literature to deal with those radiation-caused errors (MAHMOOD; MCCLUSKEY, 1988; REINHARDT; MUKHERJEE, 2000; GOLOUBEVA et al., 2006; MUKHERJEE; KONTZ; REINHARDT, 2002). Most of the fault tolerance methods protect the system from Silent Data Corruptions (SDC), which are errors in memory and final application output. Single Event Functional Interrupt (SEFI), another important type of error that leads to hangs or crashes in the system, is typically not targeted by the techniques. Nevertheless, SEFI is the most severe issue, as it impacts the application execution and the user experience directly.

There are just a few techniques that are able to detect both SDC and SEFI. One of them employs the lockstep principle, which is a hybrid solution based on redundancy used to increase the dependability of embedded processors. This work makes use of Dual-core Lockstep (DCLS) as a fault tolerance method capable of detecting and correcting soft errors. The proposed DCLS runs the same application simultaneously in two identical processors and monitors the application execution outputs, checking for inconsistencies. The lockstep combines checkpoints and rollbacks (BOWEN; PRADHAM, 1993) at software level to ensure processor reliability. Checkpoints are operations that store a fault-free copy of the processor state in a safe memory. Whereas, a rollback consists of a recovery method that restores the processor to a previous safe state.

Although the literature presents a plethora of lockstep implementations (ABATE; STERPONE; VIOLANTE, 2008; VIOLANTE et al., 2011; GOMEZ-CORNEJO et al., 2013; PHAM; PILLEMENT; PIESTRAK, 2013), most of them protect soft-core processors. As these cores have an open architecture and are implemented in FPGA logic, the advantage is the designer can modify it if needed. However, the ones embedded into SRAM-based FPGAs are susceptible to persistent soft errors in the configuration bitstream, which can affect the functionality, and performance of the processor. This work focuses on protecting hard-core processors embedded into APSoCs. Therefore, the persistent errors in the processors caused by bit-flips in the programmable configurable blocks are avoided, differently as occurs with soft-core processors. Moreover, it is possible to take advantages of the high-performance hard-core processor as well as the programmable matrix.

#### 1.1 Main Objective and Contributions

This work aims to investigate a fault tolerant solution to soft-errors mitigation concerning processors embedded into APSoCs. As previously discussed, heterogeneous architectures can efficiently execute applications, achieving performance enhancement. However, these devices are very susceptible to radiation effects been necessary to implement strategies to deal with it.

The main objective of this work is implementing an approach based on Dual-Core LockStep (DCLS) as a fault tolerance technique to mitigate radiation-induced faults affecting processors embedded into APSoCs. The method should be capable of detecting and treating both SDC and SEFI errors before they can cause catastrophic issues.

The proposed DCLS architecture relies on two processors running with private embedded BRAM memories to duplicate the application execution, and a checker module to validate the processors' output and, in case of failure, recover the system. The DCLS technique is implemented to protect a dual-core ARM Cortex-A9 embedded into a Xilinx Zynq-7000 APSoC. This APSoC is capable of serving a wide range of safety-critical applications, such as avionics communications, missile control, and smart ammunition control systems. The Zynq was chosen as test case due to its high presence on the market and in the scientific literature. Although the implementation target is the ARM-A9 into Zynq, the approach can be easily portable to another hard-core processor embedded into APSoC, making just some architectural changes.

The main novelty lies in applying the DCLS to a hard-core ARM Cortex-A9 in which, for the best of our knowledge, no other work focuses on this processor. Besides, the use of an exclusive BRAM memory to each processor, in order to avoid a single point of failures in the data memory, increasing the reliability. The implemented lockstep approach does not require both processors work in the same clock, because of the verification point strategy each processor can work with distinct clock. This work applies the DCLS to applications running not only in bare-metal but also on the FreeRTOS, which is an industry-leading real-time operating system. The FreeRTOS is used in a plethora of applications, such as aerospace and safety-critical. Thus, the effectiveness evaluation of fault-tolerant techniques applied to applications running on top of this systems is essential.

A complete evaluation of the performance impact in used the proposed DCLS in the system is described. This work presents an analysis of how software optimizations can affect the DCLS approach fault coverage and performance penalties. Two types of optimization are evaluated: software partition and compiler optimizations. The former is directly related to the number of verification points, which is defined during the DCLS design. The latter is related to compilation parameters used to boost performance.

To assess the system, two types of experiments were performed: radiation exposure and fault injection. The radiation exposure consists of heavy ions experiments, conducted at Laboratório Aberto de Física Nuclear at Universidade de São Paulo (LAFN-USP), Brazil. To emulate faults in the processor a fault injection system was developed. The injection is performed by a module in the FPGA layer of the APSoC that emulates bit-flips on the processor's register file in a non-intrusive manner. Thus, the resilience of the embedded processor is evaluated.

The appendix A presents the list of publications resulting from this work efforts.

#### 1.2 Work Structure

This dissertation is organized as follows. Chapter 2 presents the background knowledge. The basics concepts of embedded processors, heterogeneous architectures and radiation effects are introduced. Besides, an overview of fault tolerant techniques used to improve the processor dependability is presented. Then, in chapter 3 is described the implementation of the proposed DCLS technique. In sequence, chapter 4 details the evaluation methodology used to assess the system. It describes the experiments performed and test case applications used for achieving the results, which are discussed in chapter 5. Finally, chapter 6 draws the final remarks and possible future works that can be done over the presented DCLS.

#### 2 BACKGROUND AND STATE OF THE ART

This chapter first discusses embedded processors and how soft errors can influence in their functionality. The system complexity and the area density increase the vulnerability to soft errors. Devices with heterogeneous architectures, which integrate embedded processors and FPGAs, are also described. These devices are extensively being used for implementing mission-critical and reliable systems. Such applications demand fault tolerant techniques capable of protecting the system against soft errors. An overview of fault tolerant techniques used to improve the processor dependability is presented, and their advantages and disadvantages are discussed. Finally, the concepts of the lockstep method and several related works are presented in the last section.

#### 2.1 Embedded Processors

Considering the evolution of the architectures, the modern processors delivers high-performance computing, power efficiency, and reduced cost, which are requirements for almost all safety-critical applications. From the first Von Neumann machines up to high-performance processors, the technology advances allowed to rise from sequential execution of instructions to a high level of parallelism.

The architectures of embedded processors can be split into three types depending on the number of Central Processing Units (CPU): single-, multi-, or many-cores. In the former, there is only one CPU, while the multi-cores are usually composed by two, four, six, or eight independent cores in the same silicon. The many-core system is defined when ten or more CPUs are integrated. In single-core processors to run multiple programs, time slices are assigned. In multi- and many-cores, multiple tasks that can be run in parallel at the same time, boosting performance (JOHNSON; DINYO, 2015).

The embedded processors can be defined as hard- or soft-cores. The hard-cores are processors designed physically in the chip, where all the components are integrated and manufactured. Thus, the processor is hardwired in the die, like Power-PC and ARM Cortex-A9. By contrast, the soft-cores are the ones implemented using reconfigurable resources of FPGAs. These processors are Intellectual Property (IP) blocks developed entirely in Hardware Description Language (HDL), like VHDL or Verilog. The MicroBlaze, PicoBlaze, and Nios are examples of soft-core processors used in many applications. Moreover, there are those proposed by the open-source community, like LEON3

and LEON4. The soft-cores main advantages concern to flexibility, simple integration, device customization, reusability, and portability. However, the soft-cores usually are slower than hard-cores. Besides, the soft-cores are not energy efficient, while hard-cores possess power saving modes (MONDRAGON, 2012).

## 2.2 Software Optimizations

Aiming to achieve performance requirements, less memory occupation and decrease the power consumption, the program executing in a processor can be optimized in some ways. Different levels can be optimization target, like assembly, compile, build, source code, algorithms and data structures, and design level (LINS, 2017). Software optimizations can be characterized as architecture-independent and architecture-dependent (DOMEIKA, 2008). The latter uses specific properties of the architecture, changing parameters depending on the underlying platform, like register allocation and instruction scheduling. On the other hand, architecture-independent optimizations are more general techniques that can be applied to different platforms, like loop-invariant code motion, dead code elimination, and common-subexpression elimination.

The optimizing compiler applies some transformations to the program aiming to get a more efficient code. The optimization must not affect the application results. However, it is allowed to change the program flow. Fundamentally, the compiler can optimize the code by control and data flow analysis (HAGEN, 2006). To assess the control flow, the compiler examines control constructs and loops to determine the paths of execution that can be taken and simplify the code. The data flow analysis concerns the program verification for the usage track of the variables, allowing to apply the optimizations.

Distinct compiler optimization levels can be applied to the code, with slightly different set of options. Depending on the selected configuration, the focus can be performance and/or code size improvement. The GCC optimization levels are described below (STALLMAN; COMMUNITY, 2014).

- -O0: This is the primary level, in which no optimization is performed. The source code is compiled without any rearrangement, and the executable instructions correspond precisely to the program. The -O0 is default level in debug mode.

- -O1: This is the optimization level one, which has restricted optimizations. This level focuses in to reduce code size and execution time, without compromise the

compilation time.

- -O2: This is the default level in release mode. Almost all the optimizations are performed by the compiler, less the space-speed tradeoff ones. The compiler attempt to improve the performance at the expense of compilation time.

- -O3: This is the highest level, in which all the optimizations are enabled. The compiler focuses on boosting performance over code size cost.

#### 2.3 Embedded Operating Systems

Several embedded computing systems use Operating Systems (OS) due to efficiency and software scalability. Differently from the OS for a desktop computer, the embedded OS typically requires resource-efficiency and reliability. Also, the embedded OSes have to be able to run with memory and processing power constraints. Due to the wide variety of embedded applications, there are a large number of available OS options, like Linux, FreeRTOS, and eCos.

For real-time systems, the FreeRTOS (BARRY, 2017) is the industry-leading operating system. FreeRTOS is a light OS that has, as main advantage, the feasibility of working with threads and pseudoparallelism on a single-core processor. Accordingly, the main application can be split into individual tasks with assigned priorities to be performed by the processor.

The main advantages in using embedded OS in the systems are the possibility to customize the OS to precise application requirements, the efficiency improvement, and the scalability. Despite these advantages, as the system complexity is increased, more critical points of failure and susceptibility to errors are observed, which becomes a concern for safety-critical applications (RODRIGUES; KASTENSMIDT, 2017). Thus, the use of embedded OS in these applications requires the implementation of fault-tolerance techniques.

#### 2.4 Radiation Effects

The progress of the semiconductor industry made possible the development of more complex systems, allowing architectures integration and increasing systems functionalities. The new technologies provide transistors with reduced dimensions, enabling to add a high number of transistors per area unit. Besides, the advances lead to tightened noise margins, and threshold voltages and node capacitances reduced. All these advances made the devices more susceptible to the radiation effects (BAUMANN, 2005).

Embedded systems operating in aerospace applications are particularly susceptible to radiation-induced soft errors caused by ionized particles originated from the spatial environment. The particles can interact with silicon, depositing enough charge that can temporarily charge or discharge the transistors drain at off-state, provoking transient pulses in the susceptible nodes. Such episodes might lead to bit-flips in the sequential logic that later on can induce to errors and failures in the system (BAUMANN, 2005). Systems in avionics and at ground level can also be affected by radiation effects due to interaction with neutrons present in the atmosphere (NORMAND, 2001). Baumann (2005) defines three primary mechanisms responsible for soft errors at terrestrial altitudes. The first is the interaction between high-energy neutrons and silicon nucleus. The second is when high concentrations of the dopant boron present in the device react with low-energy neutrons. And the last one is the emission of alpha particles, composed of two neutrons and two protons, from radioactive impurities in the materials.

The pulses of transient voltage caused by radiation disturbances are called as Single Event Effects (SEE), which can be destructive or nondestructive (BAUMANN, 2005; SIEGLE et al., 2015). Single Event Latch-up (SEL) is a destructive effect, as result of a high operating current. The nondestructive ones can be classified as Single Event Upset (SEU), Single Event Functional Interrupt (SEFI) or Single Event Transient (SET). SET is the transient pulse generated at a susceptible transistor node of design. This pulse may propagate through the logic and be captured by a flip-flop, for instance. SET can be logical, electrical, or latch window masked. A SEFI occurs when a soft error leads to malfunction of the device. The SEU is described as a radiation effect that provokes charge disturbance enough to reverse a data state of a memory element. When only one memory bit is affected by the soft error, it is called Single Bit Upset (SBU). If two or more bits are flipped in the same memory word, this event is defined as Multiple Bit Upset (MBU).

#### 2.4.1 Faults, Errors and Failures Concepts

The definition of faults, errors and failures can present small differences in the literature. This work adopts the same concepts described in (AVIZIENIS et al., 2004). The difference between the implemented hardware and its functionality is called a defect

or upset. Whereas, the logical abstraction of a physical defect, or imperfection, is defined as a fault. However, if the defect is electrically masked the fault will not be observed. The faults can be classified as permanent, transient or intermittent. The first are the ones that are continuous in time and remain until the replacement (or reparation) of the component. The second and third are temporary faults that are time limited. The transient ones occur randomly and remain during a short period. A repetitive fault is classified as intermittent.

When a fault is manifested, it can lead to an error, which is a wrong value in the output. In other words, an error is an inconsistency in the final result. If the error propagates and affects the system externally, it is said that a failure occurs. Therefore, an upset can be manifested as a fault that could lead to an error that may be propagated generating a failure. It is important to notice that not all faults result in error, and not every error produces a failure.

#### 2.4.2 Single Event Upsets in Embedded Processors

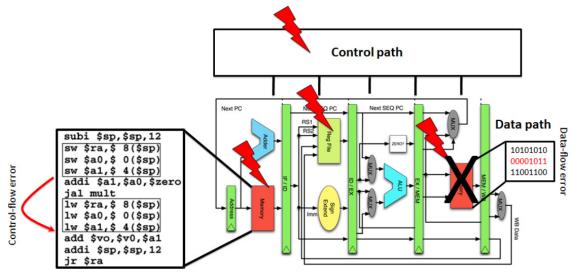

Soft errors in processors may lead to executing an application incorrectly, generating data errors or system crashes. As Fig. 2.1 shows, SEUs can affect the data flow or control flow of the processor (TAMBARA, 2017).

Upsets in the values stored in memory elements can lead to data flow errors, which can be caused by incorrect operations or wrong data. The execution of an incorrect operation occurs when a bit-flip corrupts the program code, leading to a wrong instruction. If the bit-flip affects a data used as input by an operation, the output from it certainly will be incorrect. In both data flow errors, the program output is corrupted, leading to wrong results in the final application that are classified as Silent Data Corruption (SDC).

When an SEU affects the control flow, the processor may execute the program incorrectly, leading to SEFIs. In this case, the SEFI is caused by an application crash and processor hang. Upsets in the control flow may lead to branch errors: creation or deletion of a branch, or incorrect branch decision. The erroneous creation is due to a bit-flip that set a non-branch instruction into a branch, leading the program flow to a wrong address. The erroneous deletion occurs when a branch is not taken when it should be because the branch instruction was converted into another instruction. A bit-flip in a conditional branch can result in an incorrect decision, i.e. if the branch should be taken or not. Also, an SEU can modify the register that contains the target address of a branch instruction, assigning an incorrect address to the program execution. Finally, when the Program Counter (PC)

Figure 2.1: Possible effects of soft errors in processors

Source: (TAMBARA, 2017).

register is affected by a soft error, the next instruction to be executed changes, which also leads the program flow to a wrong address.

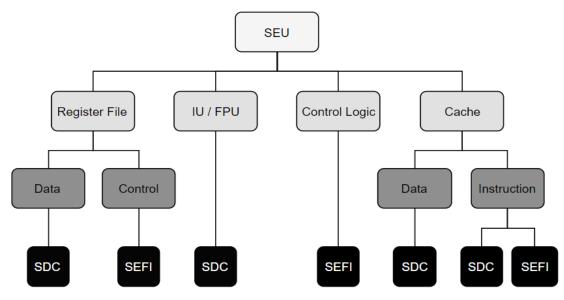

As presented, the SEUs may lead to different types of errors in the processors, depending on the memory element affected. Velazco and Faure (2007) relate the resulted error with the affected hardware unit, as described below:

- **Register File:** Upsets may corrupt data, provoking errors in the application outputs (results inconsistency). If an SEU affects a control register, this can lead to errors in the program execution flow and hangs in the system.

- Integer Unit (IU), Floating Point Unit (FPU): Due to the pipeline in the arithmetic units, SEUs may result in incorrect computations.

- **Bus Unit:** Bit-flips in the embedded registers, which latches address and data, can lead to incorrect read or write operations.

- **Control Unit:** SEUs in the circuitry, which implements complex algorithms, may provoke exception generation or losses of sequence.

- **Debug Unit:** The special execution modes can be trigged by SEUs, which will lead to errors in the execution flow of the program.

- Instruction Cache: Upsets may lead to corrupted outputs or processor hangs. The instruction caches are usually divided into SRAM array to store fetched instructions and tag array to validate or invalidate the fetched program. SEUs in the tag array can invalidate an instruction to be executed, leading to a cache miss, which introduces a

delay in the program execution as the instruction has to be fetched again. However, if an SEU validates an incorrect code, the flow of the program will be crashed. Besides, an upset can affect the SRAM array and corrupts an instruction. If the tag array validates the corrupted code, a wrong instruction will be executed, or an exception will be generated. The latter occurs when the corrupted instruction is not anymore in the processor instruction set. On the other hand, if the corrupted instruction is not validated by the tag array, the fault is masked, and no incorrect behavior will be observed.

• Data cache: These units are split in tag array and data array, like instruction caches. Bit-flips in the tag array may validate out-of-date data, leading to wrong outputs, or invalidate data, introducing a delay in the application (cache miss). If an upset affect the data array, this may lead to corrupted output. However, if the data is out-of-date, the fault is masked, and no effects will be observed.

Fig. 2.2 shows a diagram that presents an overview of the possible effects of SEUs in embedded processors. Concerning soft-core processors, they are even more vulnerable to the radiation effects. The ones embedded in SRAM-based FPGAs are susceptible to persistent soft errors in the configuration bitstream that may affect their functionality.

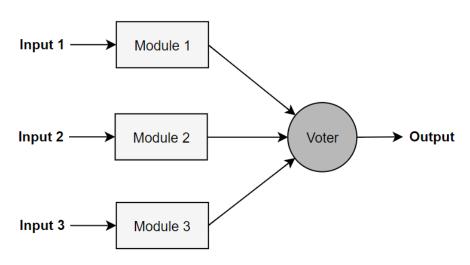

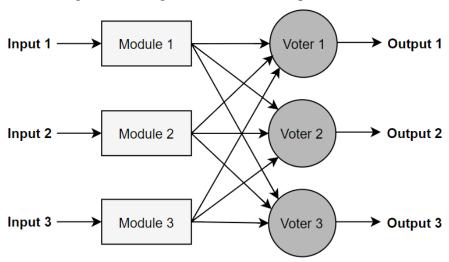

There are commercial solutions that provide Radiation Hardened (Rad-Hard) processors, which features high tolerance to radiation effects. Such is the case of Microchip (Atmel) Rad-Hard 32 bit SPARC V8 Processor (MICROCHIP, 2017) and VORAGO Rad-Hard ARM® Cortex®-M0 MCU (VORAGO, 2017). These solutions usually integrate Triple Modular Redundancy (TMR) on circuits and registers, and Error Detection and Correction (EDAC) on memories. Although the Rad-Hard architectures provide high reliability, these processors do not achieve performances as high as modern Commercial Off The Shelf (COTS) (AZAMBUJA; KASTENSMIDT; BECKER, 2014). Moreover, other drawbacks include: excessive price; limited use; not widely available - as there are only a few companies in the market; and the fabrication process uses older technologies (GINOSAR, 2012).

The Rad-Hard processors are not the only solution to systems that availability or high reliability are required. The COTS processors can be suitable for such applications if fault-tolerance methods are applied. Further in this chapter, several techniques that can be implemented to improve the dependability of embedded processors are presented.

Figure 2.2: Diagram of soft errors effects in processors

Source: From the author.

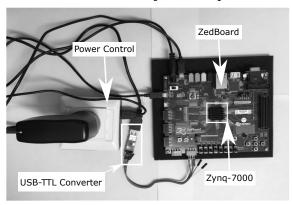

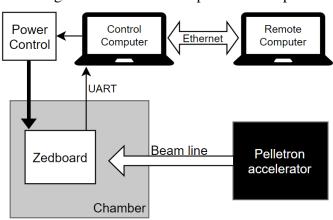

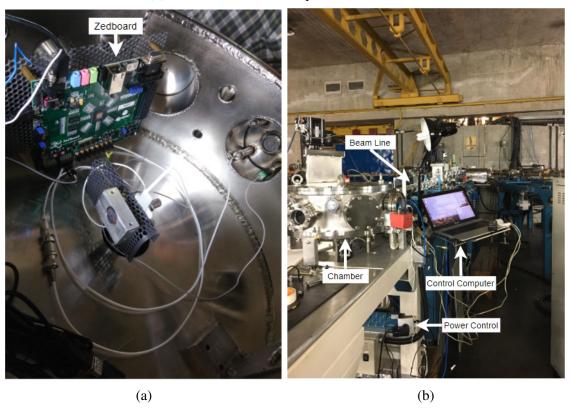

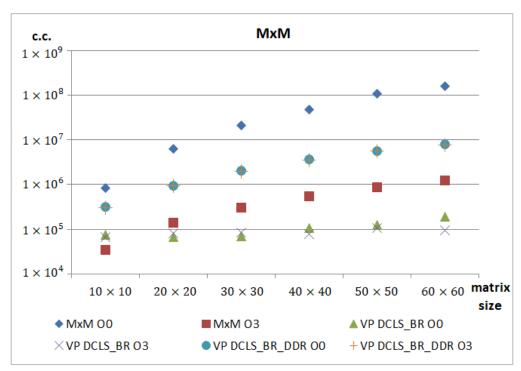

#### 2.5 All Programmable System-on-Chip Devices