## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

## TIAGO TREVISAN JOST

# SoMMA – A Software-managed Memory Architecture for Multi-issue Processors

Dissertation presented in partial fulfillment of the requirements for the degree of Master in Computer Science

Advisor: Prof. Dr. Luigi Carro

Co-advisor: Prof. Dr. Gabriel Luca Nazar

## CIP – CATALOGAÇÃO NA PUBLICAÇÃO

Jost, Tiago Trevisan

SoMMA – A Software-managed Memory Architecture for Multiissue Processors / Tiago Trevisan Jost. – 2017.

82 f.:il.

Orientador: Luigi Carro; Co-orientador: Gabriel Luca Nazar.

Dissertação (Mestrado) — Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação. Porto Alegre, BR — RS, 2017.

1. Geração de Código. 2. Limitação na Banda de Memória 3. Memória gerenciada por software. I. Carro, Luigi. II. Nazar, Gabriel Luca. III. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitor: Prof. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretor do Instituto de Informática: Profa. Carla Maria Dal Sasso Freitas

Coordenador do PPGC: Prof. João Luiz Dihl Comba

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **AGRADECIMENTOS**

This work would not have been possible without the support and comprehension on a great number of people. I would like to start by thanking my colleagues and friends from the Embedded Systems Group at INF/UFRGS with whom I spent most of my time this two-year-and-so period of my Master's. I would not dare naming them individually as some people may be forgotten.

Secondly, my most sincere gratitude to my advisors, Luigi and Gabriel, for their dedication, knowledge, comprehension and support during the whole period, and also for understanding my choice of postponing the defense in six months. I would also like to thank the people at CEA, France, where I spent my last six months as an intern, for greatly welcoming me at their company. My deepest thanks also go to all my friends outside the academic community, people from Faxinal, Porto Alegre, and everywhere, who were always there for me in times of need.

This work would have never been possible without the unconditional love and support I received from my parents, siblings and my whole family. I could never repay for all the great things you do/did/will do to me. Lastly, my heart is felt with join for sharing this dissertation with my (soon-to-be) wife, Janaina, who always gave the strength, love, and caring I needed, and for always being there for me no matter what.

## SoMMA – A Software-managed Memory Architecture for Multi-issue Processors

#### **RESUMO**

Processadores embarcados utilizam eficientemente o paralelismo a nível de instrução para atender as necessidades de desempenho e energia em aplicações atuais. Embora a melhoria de performance seja um dos principais objetivos em processadores em geral, ela pode levar a um impacto negativo no consumo de energia, uma restrição crítica para sistemas atuais. Nesta dissertação, apresentamos o SoMMA, uma arquitetura de memória gerenciada por software para processadores embarcados capaz de reduz consumo de energia e energy-delay product (EDP), enquanto ainda aumenta a banda de memória. A solução combina o uso de memórias gerenciadas por software com a cache de dados, de modo a reduzir o consumo de energia e EDP do sistema. SoMMA também melhora a performance do sistema, pois os acessos à memória podem ser realizados em paralelo, sem custo em portas de memória extra na cache de dados. Transformações de código do compilador auxiliam o programador a utilizar a arquitetura proposta. Resultados experimentais mostram que SoMMA é mais eficiente em termos de energia e desempenho tanto a nível de processador quanto a nível do sistema completo. A técnica apresenta speedups de 1.118x e 1.121x, consumindo 11% e 12.8% menos energia quando comparando processadores que utilizam e não utilizam SoMMA. Há ainda redução de até 41.5% em EDP do sistema, sempre mantendo a área dos processadores equivalentes. Por fim, SoMMA também reduz o número de cache misses quando comparado ao processador baseline.

**Palavras-chave**: geração de código, paralelismo a nível de instrução, limite na banda de memória, processador de despacho múltiplo, memória gerenciado por software.

## SoMMA – A Software-managed Memory Architecture for Multi-issue Processors

#### **ABSTRACT**

Embedded processors rely on the efficient use of instruction-level parallelism to answer the performance and energy needs of modern applications. Though improving performance is the primary goal for processors in general, it might lead to a negative impact on energy consumption, a particularly critical constraint for current systems. In this dissertation, we present SoMMA, a software-managed memory architecture for embedded multi-issue processors that can reduce energy consumption and energy-delay product (EDP), while still providing an increase in memory bandwidth. We combine the use of software-managed memories (SMM) with the data cache, and leverage the lower energy access cost of SMMs to provide a processor with reduced energy consumption and EDP. SoMMA also provides a better overall performance, as memory accesses can be performed in parallel, with no cost in extra memory ports. Compiler-automated code transformations minimize the programmer's effort to benefit from the proposed architecture. Our experimental results show that SoMMA is more energy- and performance-efficient not only for the processing cores, but also at full-system level. Comparisons were done using the pVEX processor, a VLIW reconfigurable processor. The approach shows average speedups of 1.118x and 1.121x, while consuming up to 11% and 12.8% less energy when comparing two modified processors and their baselines. SoMMA also shows reduction of up to 41.5% on full-system EDP, maintaining the same processor area as baseline processors. Lastly, even with SoMMA halving the data cache size, we still reduce the number of data cache misses in comparison to baselines.

**Keywords**: code generation process, instruction-level parallelism, memory bandwidth limitation, multi-issue processors, software-managed memory

# LIST OF FIGURES

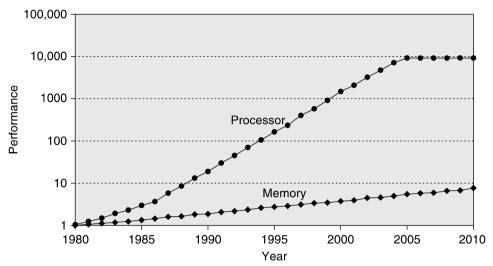

| Figure 1.1 – Processor and Memory Performance improvements over the years. The memory wall             |

|--------------------------------------------------------------------------------------------------------|

| significantly increased since 1980, as memories focused efforts on storage capacity. Since             |

| 2005, single-core processors showed no performance improvements in favor of a multi-                   |

| core approach                                                                                          |

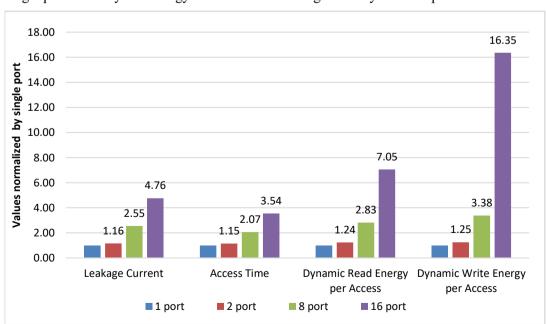

| Figure 1.2 – 32 KB cache memories with different number of ports. Values were normalized over          |

| single port. Latency and energy attributes increase significantly in multi-ported caches. 14           |

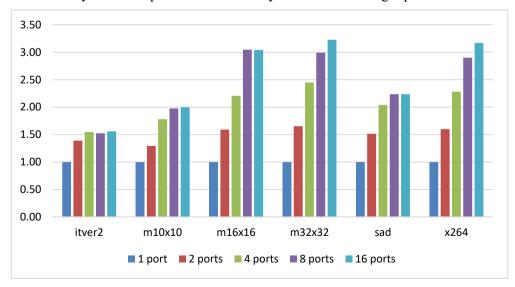

| Figure 1.3 – Normalized Speedup on a VLIW processor. Some applications struggle with limited           |

| memory bandwidth. By increasing the number of memory ports, applications on multi-                     |

| ported systems can perform considerably better than on single-ported                                   |

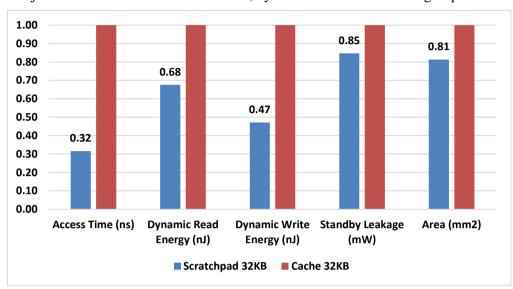

| Figure 2.1 – Constraints comparison between a 32KB Scratchpad and a 32KB Cache. We observe a           |

| major difference in terms of access time, dynamic read and write energies per access 19                |

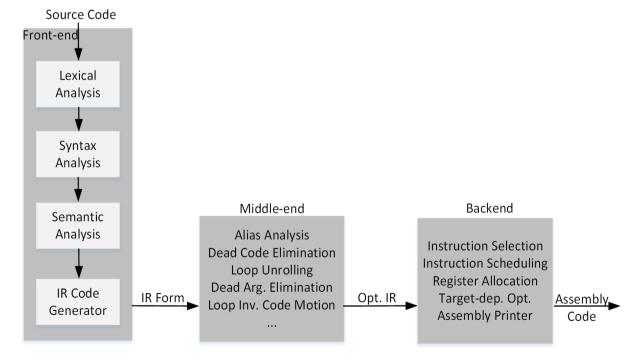

| Figure 2.2 – (a) Simplest view on the compilation Process and (b) The correct set of tools used during |

| the compilation process                                                                                |

| Figure 2.3 – A three-parted compilation process.                                                       |

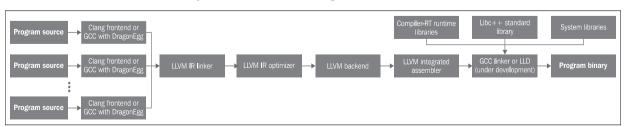

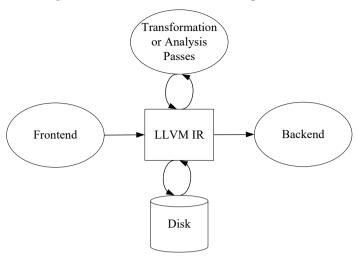

| Figure 2.4 – LLVM Compilation Overview. 23                                                             |

| Figure 2.5 – Clang diagnostic messages comparison with GCC                                             |

| Figure 2.6 – C Code transformed into SSA-form. A PHI node is used to                                   |

| Figure 2.7 – Middle-end relationship overview                                                          |

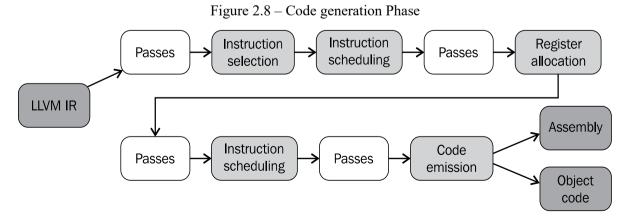

| Figure 2.8 – Code generation Phase                                                                     |

| Figure 2.9 – Code examples for two VLIW processors                                                     |

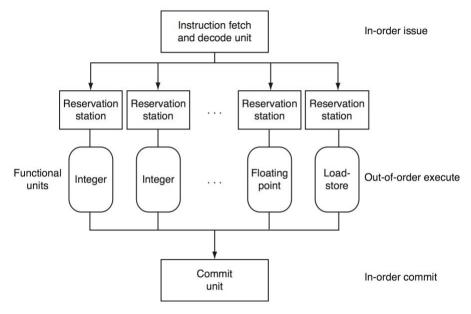

| Figure 2.10 – Three primary units of Out-Of-Order processors                                           |

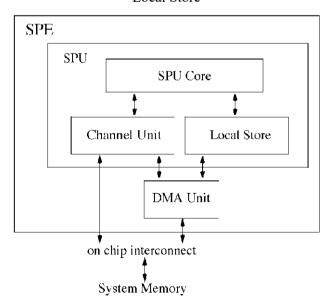

| Figure 3.1 – Synergistic processing element on the IBM cell processor. Scratchpads are referred as     |

| "Local Store"                                                                                          |

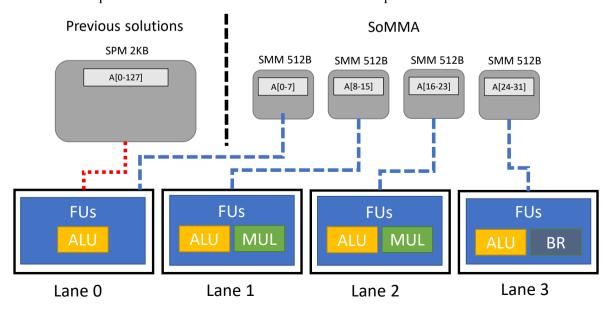

| Figure 3.2 – A 4-issue VLIW processor example. Previous solutions are represented by the red-dotted    |

| connection between lane 0 and scratchpad (SPM), while the proposed solution is                         |

| represented by the blue-dashed connection between software-managed memories                            |

| (SMMs) and lanes. Our solution uses memories in parallel in order to leverage the multi-               |

| issue characteristic of the processor. We can load and store values in multiple memories               |

| at once                                                                                                |

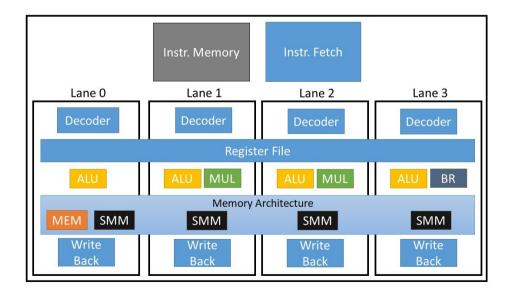

| Figure 4.1 – Location of the memory architecture in a 4-issue VLIW processor. Each lane has access     |

| to an internal memory                                                                                  |

| Figure 4.2 – Illustrative example for controlling SMMs                                                 |

| Figure 4.3 – Snippet of 7x7 matrix multiplication                                                      |

| Figure 4.4 – Snippet of assembly code                                                                  |

| Figure 4.5 – Offset address locations for a 7x7 matrix multiplication. The example shows how matrix    |

| smm a (shortened to a) and smm b (shortened to b) would be placed in the SMMs. First                   |

| scheme, on the left, shows an allocation               | n through column order, while the second, on the |

|--------------------------------------------------------|--------------------------------------------------|

| right, displays an allocation through rov              | w order 47                                       |

| Figure 4.6 – High-level algorithm for Variable Disco   | overy49                                          |

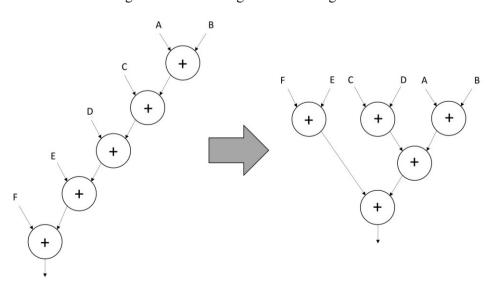

| Figure 4.7 – Tree height reduction algorithm           |                                                  |

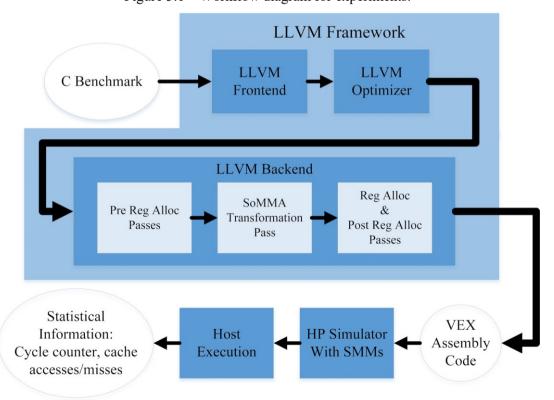

| Figure 5.1 – Workflow diagram for experiments          | 58                                               |

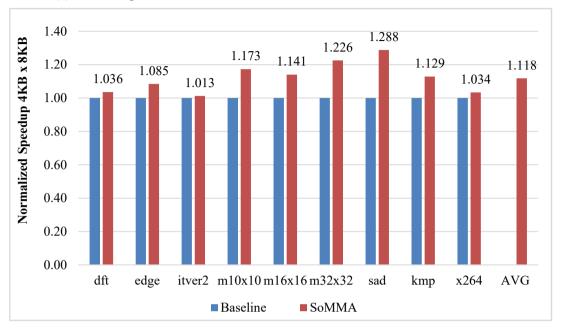

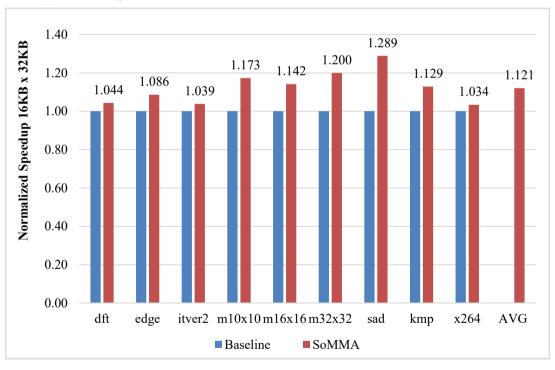

| Figure 5.2 – Normalized Speedup                        |                                                  |

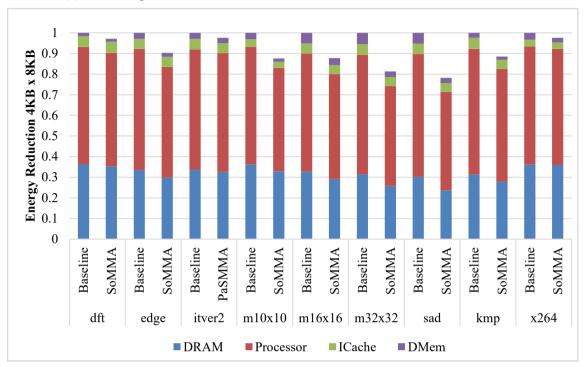

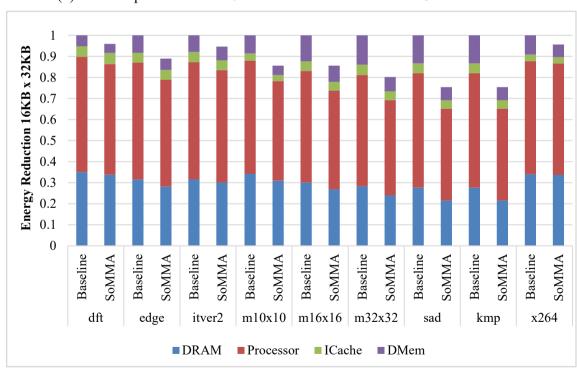

| Figure 5.3 – Normalized dynamic energy compariso       | n. Baselines have 8KB and 32KB of data cache     |

| when compared to SoMMA 4KB and S                       | SoMMA 16KB, respectively 65                      |

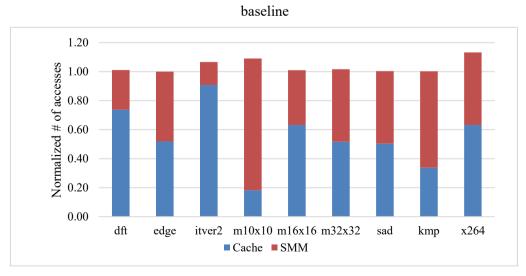

| Figure 5.4 - Normalized number of accesses for the     | SoMMA processors in comparison to the baseline   |

|                                                        |                                                  |

| Figure 5.5 – Compiler generates lane-specific nops v   | when no instruction is executed. The example     |

| show that lanes 5, 6 and 7 have a nop at               | fter nop sequence61                              |

| Figure 5.6 – Normalized Energy in a full-system cor    | nfiguration66                                    |

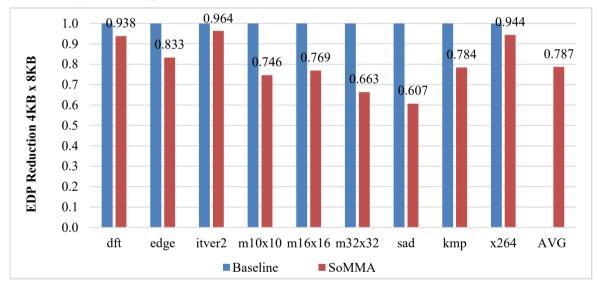

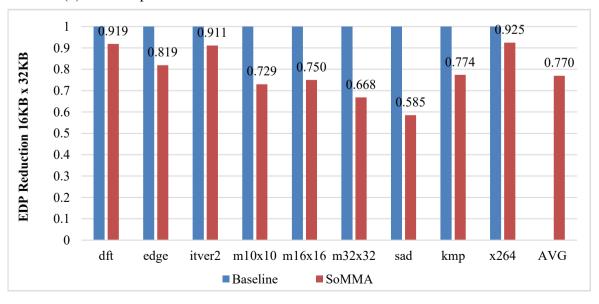

| Figure 5.7 – EDP reduction in a full-system configure  | ration 68                                        |

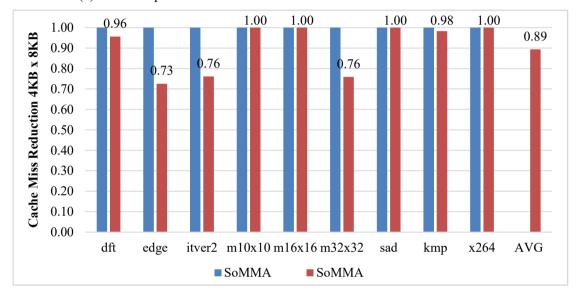

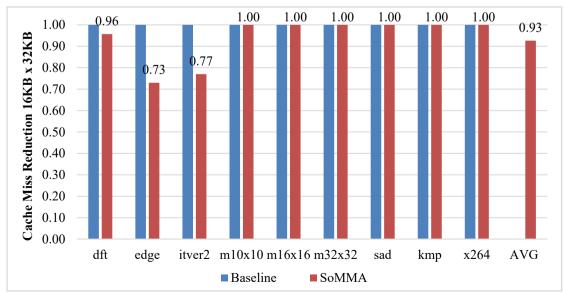

| Figure 5.8 – Data cache miss reduction                 | 69                                               |

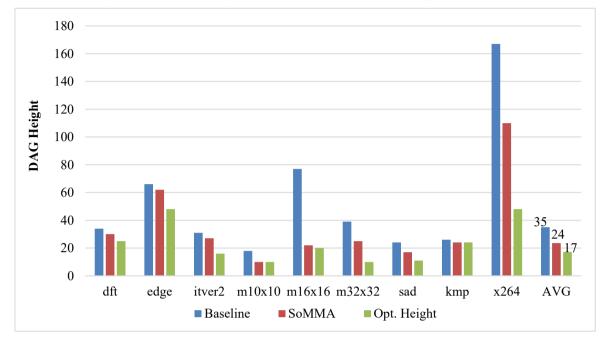

| Figure 5.9 – DAG Heights for the main BBs with the     | eir optimized values71                           |

| Figure 5.10 – Small snippet of C-code for a FIR filter | er                                               |

| Figure 5.11 – Data placement on the SMMs for FIR       |                                                  |

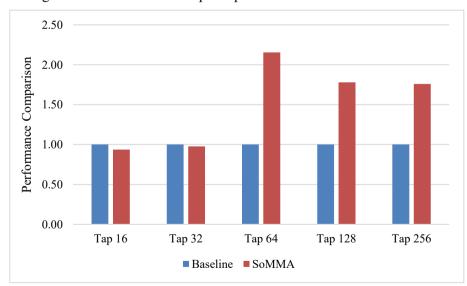

| Figure 5.12 – Performance Speedup for a handwritte     | en FIR in SoMMA74                                |

|                                                        |                                                  |

# LIST OF TABLES

| Table 2.1 – Categorization of Multi-issue Processors.         | 30 |

|---------------------------------------------------------------|----|

| Table 5.1 – Execution time increase when adding preamble code | 64 |

| Table 5.2 – Energy cost per access in Caches and SMMs         | 59 |

#### LIST OF ABBREVIATONS AND ACRONYMS

ALU Arithmetic and Logic Unit

API Application Programming Interface

ASIC Application-Specific Integrated Circuits

AVX Advanced Vector Extensions

BB Basic Block

BFS Breadth-First Search

BRAM Block RAM

CASA Cache-Aware Scratchpad Allocation

CU Compute Unit

DAG Direct Acyclic Graph

DDG Data-Dependence Graph

DFT Discrete Fourier Transform

DLP Data-Level Parallelism

DRAM Dynamic Random Accesses Memories

EDP Energy-Delay Product

FPGA Field-Programmable Gate Array

FIR Finite Impulse Response

FU Functional Unit

GPU Graphics Processing Unit

HLL High-Level Programming Language

ILP Instruction-Level Parallelism

IR Intermediate Representation

ISA Instruction Set Architecture

SRAM Static Random Access Memory

LLVM Low-Level Virtual Machine

LEAP Logic-based Environment for Application Programming

LPDDR2 Low-power DDR2

LVT Live Value Table

MIMD Multiple Instruction Multiple Data

O3 Out-Of-Order

OO Object-Oriented

RTS Real-Time Systems

SAD Sum of Absolute Differences

SIMD Single Instruction Multiple Data

SMM Software-Managed Memory

SPE Synergistic Processing Unit

SSA Static-Single Assignment

SSE Streaming SIMD Extensions

TLP Thread-Level Parallelism

VEX VLIW Example

VLIW Very-Long Instruction Word

WCET Worst-Case Execution Time

# TABLE OF CONTENTS

| 1 I           | NTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12 |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1           | Memory Wall and Memory Hierarchies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 1.2           | Memory Bandwidth Limits, Memory Ports and their Impacts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| 1.3           | Main Goals and Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| 1.4           | Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 17 |

| 2 E           | BACKGROUND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| 2.1           | Software-managed Memories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| 2.1.1         | Types of Scratchpad Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| 2.1.2         | Types of Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| 2.2           | Compilation Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| 2.2.1         | The Structure of Compiler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| 2.2.2         | LLVM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| 2.3           | Multi-issue processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| 2.3.1         | Very-long Instruction Word Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| 2.3.2         | Superscalar Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|               | RELATED WORK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| 3.1           | Scratchpads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| 3.1.1         | Academic use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| 3.1.2         | Usability in the industry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| 3.2           | Multi-ported systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| 3.3           | Our approach x Other methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|               | HARWARE AND SOFTWARE SUPPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| 4.1           | Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 4.2           | Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 4.2.1         | SMM-specific instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| 4.2.2         | Preamble Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 4.2.3         | Example Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| 4.2.4         | Code Generation Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|               | EXPERIMENTAL SETUP AND RESULTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| 5.1           | Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |