## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

## PRISCILA CAVALCANTE HOLANDA

## DHyANA: a Digital Hierarchical Neuromorphic Architecture for Liquid Computing

Thesis presented in partial fulfillment of the requirements for the degree of Master of Microeletronics

Advisor: Prof. Dr. Ricardo Reis

Coadvisor: Prof. Dr. Guilherme Bontorin

Porto Alegre December 2016

## CIP — CATALOGING-IN-PUBLICATION

Holanda, Priscila Cavalcante

DHyANA: a Digital Hierarchical Neuromorphic Architecture for Liquid Computing / Priscila Cavalcante Holanda. – Porto Alegre: PGMICRO da UFRGS, 2016.

97 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2016. Advisor: Ricardo Reis; Coadvisor: Guilherme Bontorin.

1. DHyANA. 2. Spiking neural network. 3. Hierarchical network-on-chip. 4. Biomimetic. 5. Neuromorphic. I. Reis, Ricardo. II. Bontorin, Guilherme. III. Título.

## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas

Coordenadora de Pós-Graduação em Microeletronica: Prof<sup>a</sup>. Fernanda Gusmão de Lima

Kastensmidt

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

### **ACKNOWLEDGMENTS**

This work became a reality with the kind support and help from many individuals. It was also the product of a large measure of serendipity, fortuitous encounters with people who have changed the course of my academic career and also my life. I would like to extend my sincere thanks to every single person who found a way to encourage, support and guide me throughout such a remarkable journey.

First and foremost, I offer my sincerest gratitude to my Advisor, Dr. Ricardo Reis, who believed me even when I couldn't. Without your encouragement and guidance this work would never be possible. To Dr. Guilherme Bontorin, my dear Coadvisor, who has always supported me with his patience and knowledge whilst always allowing me the room to work in my own way. To the professors Dr. Cesar Zeferino, Dr. Marco Idiart and Dr. Fernanda Kastensmidt, who kindly shared several valuable insights to this work.

To the Federal University of Rio Grande do Sul (UFRGS), for providing everything I needed to produce and complete my works, and to the National Council for Scientific and Technological Development (CNPq) for funding my studies. To the colleagues from Lab. 67/217, thank you for the fruitful conversations and for the pretty amazing food. To Vitor, whose support was vital for this work, from the thoughtful help in software, version control, and other technical issues to keeping my mind sane with some company and pretty good wine. To Cezar, who was always so available and kind to help me and so patient to explain even the most elementary questions. To Raysa, for helping the conception of the most beautiful images in this work.

To the researchers who, before me, felt fascinated by the world of the brain. Your contribution to science, to the world, and also to my humble work, is very much appreciated. To all the professors, from school, from the Federal University of Ceará, from Stevens Institute of Technology, and from the Federal University of Rio Grande do Sul, who inspired and helped me become who I am today. To Prof. Dr. Luiz Henrique Barreto, who first accepted and supervised some of my research ideas and encouraged me to follow them.

To the most caring and thoughtful friends in the world. To Neuza, Raysa, Victor, Raffaela, Adan, Caio, Laís and Halina, no matter how far, you have always been my strength and my safe harbor. To Simone, Geovana and Joana, longstanding friends who may not always be at sight, but are always in my heart. To Nayara, for sharing the hardest and craziest times of a lifetime. To Cristhine, my soulmate friend, who held my hand and

lifted me off the ground in all the ways one possibly can.

To my lucky charm, Lorrana, who showed me how to appreciate the beauty of unexpected encounters. Thank you for taking time to understand and revise this work. But mostly, thank you for having given me the courage to not only visit the basements of my own self, but mainly try to inhabit them.

To my fortress, my beautiful family, for the unconditional support. To my impossibly annoying and loved brother, for believing me. To the happiest and loudest cousins in the world, thanks for having my back. To my aunts and uncles, for providing the best care and the greatest example. To my grandparents, for being my heroes.

And lastly, to my parents, Aldemir e Ana, who deposit an unwavering faith in me. You have always provided me with the best opportunities and support a daughter could have ever hope for. For that and so much more, I am eternally grateful.

# DHyANA: a Digital Hierarchical Neuromorphic Architecture for Liquid Computing

## **ABSTRACT**

Neural Networks has been a subject of research for at least sixty years. From the effectiveness in processing information to the amazing ability of tolerating faults, there are countless processing mechanisms in the brain that fascinates us. Thereupon, it comes with no surprise that as enabling technologies have become available, scientists and engineers have raised the efforts to understand, simulate and mimic parts of it.

In a similar approach to that of the Human Genome Project, the quest for innovative technologies within the field has given birth to billion dollar projects and global efforts, what some call a global blossom of neuroscience research.

Advances in hardware have made the simulation of millions or even billions of neurons possible. However, existing approaches cannot yet provide the even more dense interconnect for the massive number of neurons and synapses required.

In this regard, this work proposes DHyANA (Digital HierArchical Neuromorphic Architecture), a new hardware architecture for a spiking neural network using hierarchical network-on-chip communication. The architecture is optimized for Liquid State Machine (LSM) implementations.

DHyANA was exhaustively tested in simulation platforms, as well as implemented in an Altera Stratix IV FPGA. Furthermore, a logic synthesis analysis using 65-nm CMOS technology was performed in order to evaluate and better compare the resulting system with similar designs, achieving an area of 0.23mm<sup>2</sup> and a power dissipation of 147mW for a 256 neurons implementation.

**Keywords:** DHyANA, spiking neural network, hierarchical network-on-chip, biomimetic, neuromorphic.

## DHyANA: uma Arquitetura Digital Neuromórfica Hierárquica para Máquinas de Estado Líquido

## **RESUMO**

Redes Neurais têm sido um tema de pesquisas por pelo menos sessenta anos. Desde a eficácia no processamento de informações à incrível capacidade de tolerar falhas, são incontáveis os mecanismos no cérebro que nos fascinam. Assim, não é nenhuma surpresa que, na medida que tecnologias facilitadoras tornam-se disponíveis, cientistas e engenheiros têm aumentado os esforços para o compreender e simular.

Em uma abordagem semelhante à do Projeto Genoma Humano, a busca por tecnologias inovadoras na área deu origem a projetos internacionais que custam bilhões de dólares, o que alguns denominam o despertar global de pesquisa da neurociência.

Avanços em hardware fizeram a simulação de milhões ou até bilhões de neurônios possível. No entanto, as abordagens existentes ainda não são capazes de fornecer a densidade de conexões necessária ao enorme número de neurônios e sinapses.

Neste sentido, este trabalho propõe DHyANA (Arquitetura Digital Neuromórfica Hierárquica), uma nova arquitetura em hardware para redes neurais pulsadas, a qual utiliza comunicação em rede-em-chip hierárquica. A arquitetura é otimizada para implementações de Máquinas de Estado Líquido.

A arquitetura DHyANA foi exaustivamente testada em plataformas de simulação, bem como implementada em uma FPGA Stratix IV da Altera. Além disso, foi realizada a síntese lógica em tecnologia 65nm, a fim de melhor avaliar e comparar o sistema resultante com projetos similares, alcançando uma área de 0,23mm² e potência de 147mW para uma implementação de 256 neurônios.

**Palavras-chave:** DHyANA, rede neural pulsada, rede em chip hierárquica, biomimético, neuromórfico.

## LIST OF ABBREVIATIONS AND ACRONYMS

AER Address Event Representation

BMI Brain-Machine Interfaces

BPDC Backpropagation Decorrelation

BRAIN Brain Research through Advancing Innovative Neurotechnologies

CAM Content-Addressable Memory

CMOS Complementary Metal-Oxide Semiconductor

DARPA Defense Advanced Research Projects Agency

DHyANA Digital HierArchical Neuromorphic Architecture

DSP Digital Signal Processing

EPFL École Polytechnique Fédérale de Lausanne

EPSP Excitatory Postsynaptic Potential

ESN Echo State Network

FIFO First In, First Out data buffer

flit flow control unit

FPGA Field-Programmable Gate Array

FSM Finite-State Machine

GSOPS Giga-Synaptic Operations Per Second

HBP Human Brain Project

HICANN High Input Count Analog Neural Network

HICIT Hierarchical Crossbar-based Interconnection Topology

HMF Hybrid Multiscale Facility

HNN Hardware Neural Networks

IBM International Business Machines Corporation

IF Integrate-and-Fire neuron model

IP Intellectual Property

IPSP Inhibitory Postsynaptic Potential

ISM Izhikevich Simple Model

LIF Leaky Integrate-and-Fire

LSM Liquid State Machine

NA Neuron Address

NETT Neural Engineering Transformative Technologies

NI Network Interface

NoC Network-on-chip

P2P Point-to-point

PCB Printed Circuit Board

phit physical unit

PSP Postsynaptic Potential

RAM Random-Access Memory

RASoC Router Architecture for Systems-on-Chip

RC Resevoir Computing

RI Routing Information

ROM Read-Only Memory

SDRAM Synchronous Dynamic Random-Access Memory

SiP System-in-Package

SNN Spiking Neural Networks

SoC System-on-chip

SRAM Static Random-Access Memory

STDP Spike-Timing Dependent Plasticity

UFRGS Universidade Federal do Rio Grande do Sul

UMC United Microelectronics Corporation

## LIST OF FIGURES

| Figure 1.1  | It Takes the World to Map the Brain.                       | 14 |

|-------------|------------------------------------------------------------|----|

| Figure 2.1  | Representation of a neuron                                 | 20 |

| Figure 2.2  | Main parts of a synapse                                    | 21 |

| Figure 2.3  | Neuro-computational properties of spiking neurons.         | 22 |

| -           | Plausibility versus Complexity.                            |    |

| _           | Example of a Spike Raster Plot.                            |    |

|             | Structure of a RNN in the Framework of Reservoir Computing |    |

| _           | Structure of a Liquid State Machine (LSM)                  |    |

|             | On-chip communication structures                           |    |

| _           | Regular Forms of Topologies                                |    |

| -           | Irregular Forms of Topologies                              |    |

|             | Generic Router Model.                                      |    |

| riguic 2.11 | Generic Router Woder.                                      |    |

| Figure 4.1  | DHyANA Global Level.                                       | 44 |

| _           | Global Link                                                |    |

| _           | Message Composition                                        |    |

| _           | Global Packet format and RI bits                           |    |

| -           | Packet Routing                                             |    |

|             | Global Level: Router components                            |    |

|             | Global Router Interface and Crosspoint Matrix.             |    |

| -           | DHyANA Cluster Level.                                      |    |

| _           | The Neuron Implementation                                  |    |

|             | The Neuron Schematic                                       |    |

| Figure 5.1  | Neurons at the Cluster Level                               | 58 |

|             | Cluster Level Packet.                                      |    |

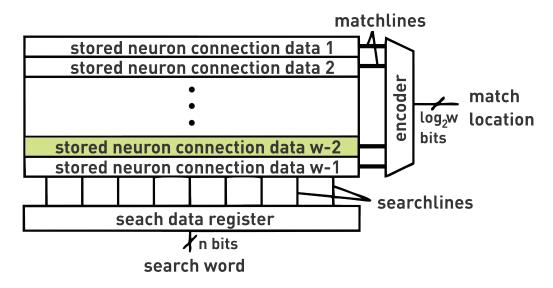

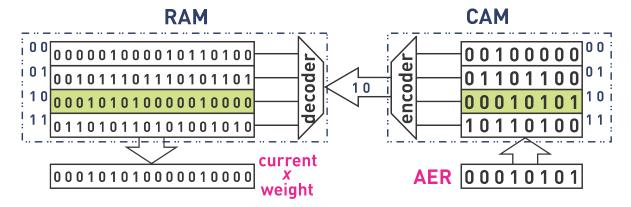

|             | Conceptual view of a Content-Addressable Memory            |    |

|             | Memories at the Neuron Module                              |    |

| Figure 5.5  | Controller Detail at the Cluster Level                     | 61 |

|             | ROM Data for one Neuron.                                   |    |

| _           | Pseudo-code for Global Packet Header assembly              |    |

|             | Cluster Controller FSM Logic                               |    |

| Figure 5.0  | Pseudo-code for Decoding the Global Packet.                | 65 |

| rigure 3.9  | rseudo-code for Decoding the Global Packet.                | 03 |

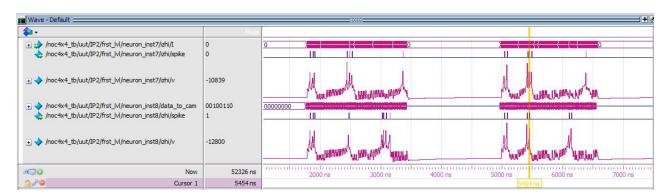

| Figure 6.1  | Two Neurons Spiking After Stimulation.                     | 67 |

|             | Afferent Datapath of the Cluster Level                     |    |

| Figure 6.3  | Routers Communication                                      | 69 |

| Figure 6.4  | Datapath of the Global Level.                              | 69 |

| Figure 6.5  | Efferent Datapath of the Cluster Level                     | 70 |

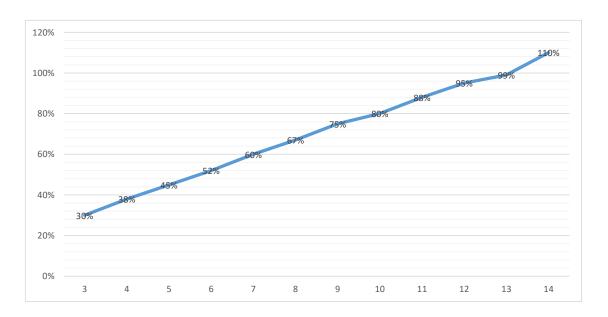

|             | Cluster Size versus FPGA Logic Utilization.                |    |

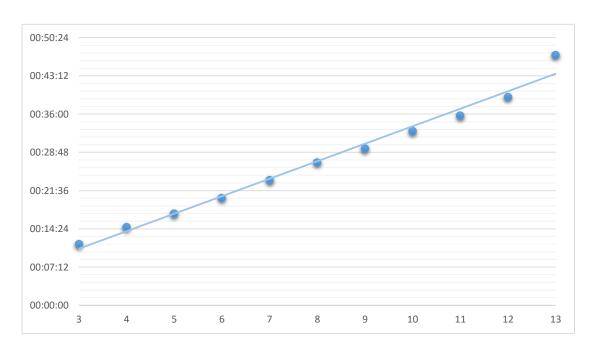

|             | Cluster Size versus FPGA Synthesis Time Elapsed            |    |

| _           | •                                                          |    |

|             | Nível Global da DHyANA                                     |    |

| Figure A.2  | Nível Local da DHvANA.                                     | 93 |

## LIST OF TABLES

| Table 2.1 | Comparison of the properties of neuron models       | 24 |

|-----------|-----------------------------------------------------|----|

|           | Parameters for a NoC Communication Infrastructure   |    |

| Table 3.1 | Related Work synthesis data                         | 42 |

| Table 4.1 | Description of RI bits                              | 47 |

|           | Parameters for neurocomputational features          |    |

| Table 6.1 | DHyANA compared to Related Works                    | 73 |

| Table A.1 | Descrição dos bits RI                               | 93 |

|           | Parâmetros para características neurocomputacionais |    |

|           | DHyANA compada a Arquiteturas Relacionadas          |    |

## **CONTENTS**

| 1 INTRODUCTION                                                | 13 |

|---------------------------------------------------------------|----|

| 1.1 Problem Formulation and Motivation                        | 15 |

| 1.2 Text Organization                                         | 17 |

| 2 BACKGROUND                                                  | 19 |

| 2.1 Spiking Neural Networks                                   | 19 |

| 2.1.1 Spiking Neurons: A Biological Perspective               | 19 |

| 2.1.2 Neuron Mathematical Models                              | 21 |

| 2.1.3 Networks and Information Coding                         | 25 |

| 2.2 Reservoir Computing                                       | 27 |

| 2.2.1 Liquid State Machine                                    | 29 |

| 2.3 Networks-on-chip                                          | 31 |

| 3 STATE-OF-THE-ART                                            | 37 |

| 3.1 Non-scalable or Special Purpose Works in FPGA             | 37 |

| 3.2 Reservoir Computing in Hardware                           | 38 |

| 3.3 Scalable and Large Scale General Purpose SNNs in Hardware | 39 |

| 4 PROPOSED NEUROMORPHIC ARCHITECTURE                          | 43 |

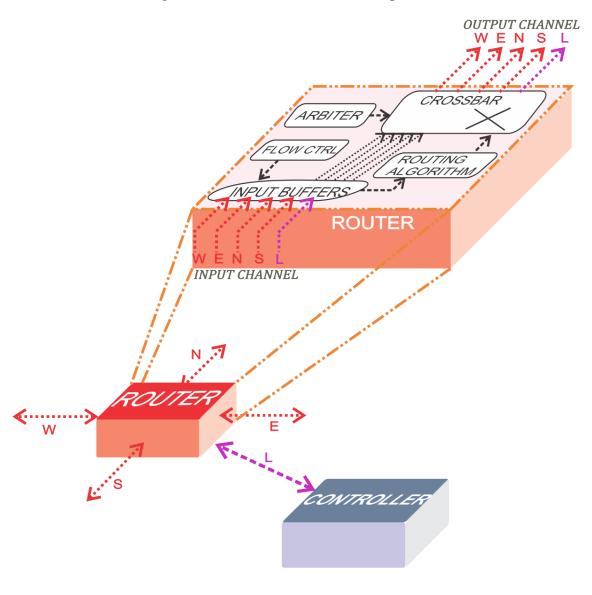

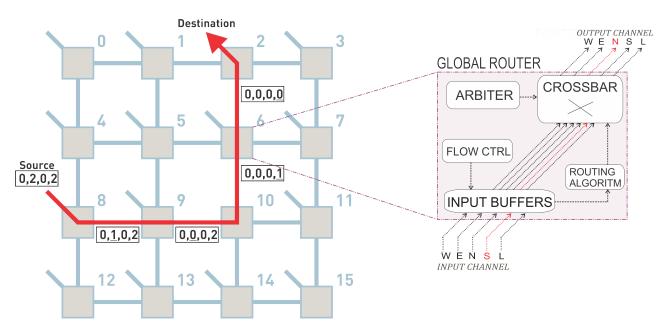

| 4.1 Global Level: The Mesh NoC Interface                      | 45 |

| 4.1.1 The Global Router                                       | 49 |

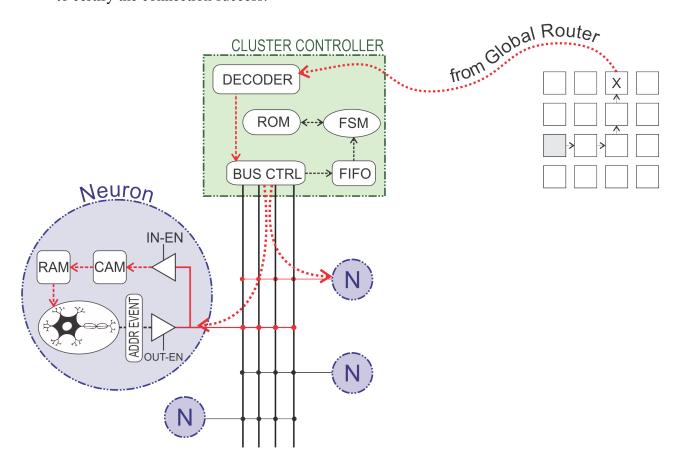

| 4.2 Cluster Level: The Bus Interface                          | 52 |

| 4.3 Processing Element: The Neuron                            | 53 |

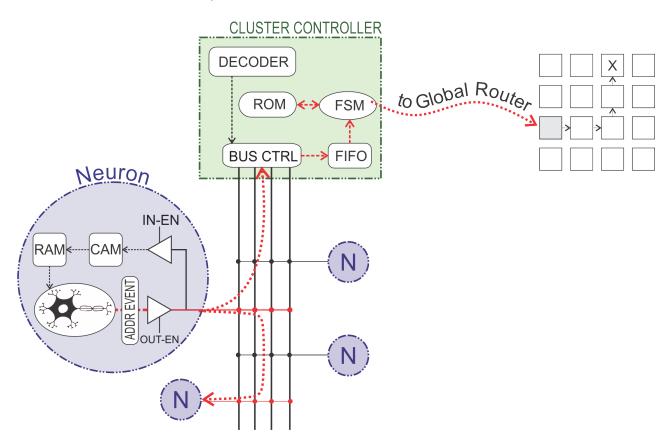

| 5 CLUSTER LEVEL                                               | 57 |

| <b>5.1</b> Neuron module                                      | 57 |

| 5.2 The Cluster Controller                                    | 61 |

| 6 RESULTS                                                     | 66 |

| 6.1 Testbench Setup                                           |    |

| 6.2 FPGA Implementation                                       | 70 |

| 6.3 Related Work Comparison and Final Remarks                 | 72 |

| 7 CONCLUSIONS AND FUTURE WORK                                 | 74 |

| APPENDIX A — RESUMO EM PORTUGUÊS                              | 87 |

| A.1 Resumo                                                    | 87 |

| A.2 Introdução                                                | 87 |

| A.2.1 Redes Neurais Pulsadas                                  | 87 |

| A.2.2 Máquinas de Estado Líquido                              | 88 |

| A.2.3 Redes em Chip                                           | 89 |

| A.2.4 Estado da Arte                                          | 90 |

| A.3 Arquitetura Proposta                                      | 91 |

| A.3.1 Nível Global                                            | 91 |

| A.3.2 Nível Local                                             |    |

| A.3.3 Núcleos de Processamento: Neurônios                     | 95 |

| A.4 Resultados                                                | 95 |

| A.5. Conclusão e Trabalhos Futuros                            | 97 |

### 1 INTRODUCTION

The brain is an amazing and highly efficient three-pound machine, and definitely one of the most complex and magnificent structures in the human body. It is formed by a network of more than 100 billion single nerve cells interconnected in systems that construct our perceptions of the world, fix our attention, and control the machinery of our actions (KANDEL et al., 2013). Understanding how complex processes in the brain give rise to complex behavior is one of the key scientific challenges in the twenty-first century, and a grown effort is rising in a global scale.

Furthermore, for the last fifty years, Moore's Law have powered tremendous advances in computing, allowing supercomputers to reach petaflop information-processing rates. Such a growth rate is by far the largest of any kind within the roughly 10,000 years of human civilization, and have revolutionized science, technology and medicine to the extent that it is now becoming feasible to simulate networks of neurons, brain regions and, eventually, the whole brain.

One of the first brain-scale models ever developed was the thalamocortical model by Izhikevich and Edelman, in which a million spiking neurons were simulated (IZHIKE-VICH; EDELMAN, 2008). Interestingly, the model exhibited behavioral phenomena similar to normal brain activity that were not previously built in, such as spontaneous activity, sensitivity to changes in individual neurons and rhythms of spiking activity.

Around the same time, Henry Markram launched the highly publicized Blue Brain Project, a partnership with IBM and the École Polytechnique Fédérale de Lausanne (EPFL). Using the massive computing power of IBM's Blue Gene supercomputer, the project aims to simulate the brains of mammals with a high level of biological accuracy (MARKRAM, 2006).

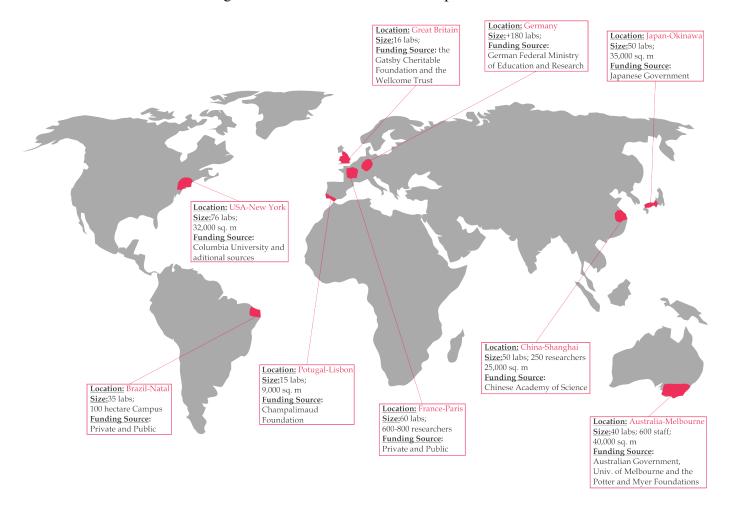

From that on, a number of large-scale projects have risen. The multi-million dollar brain research initiatives such as European Union's HBP and NETT, Unites States MindScope and BRAIN Initiative, Japan's Brain/MINDS as well as the increasing number of research facilities worldwide (See Figure 1.1) prove that we are at a historical moment for the brain.

These researches can bring several benefits to the human kind. From the ability to better understand and seek treatment for brain disorders to the expertise to model and develop intelligent systems, the motivations for implementing brain models are countless. The ability to develop Brain-Machine Interfaces (BMIs) and neuroprostheses, for instance,

Figure 1.1: It Takes the World to Map the Brain.

Source: based on (SEGEV, 2016)

would help improve the quality of life of several people affected by neurological disorders, such as Parkinsons' and Alzheimer's disease. As of 2016, cochlear implants are among the most successful ones, and in about 30 years, more than 220.000 patients worldwide now enjoy restored hearing because of such devices. Other research cases developed brain-activated upper and lower limb prostheses for amputees and paralytics, as well as retinal implants and even hippocampus emulation.

Still, to become possible, brain-scale models require yet more computational power. And as the Moore's law becomes less feasible, further computational optimizations have to be researched in order to promote exascaling computing, for it is believed to be the order of processing power of the human brain at neural level.

#### 1.1 Problem Formulation and Motivation

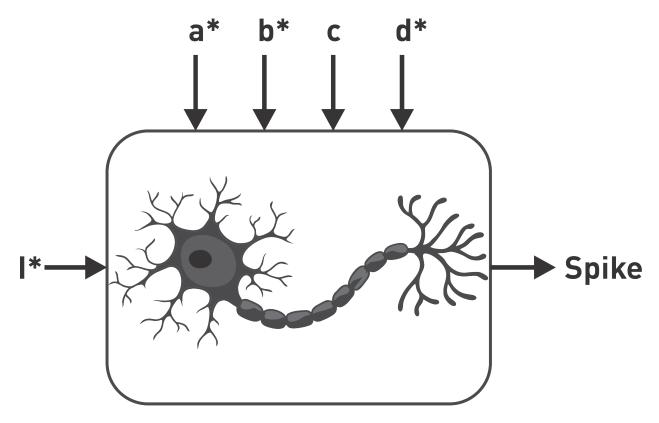

It is estimated that the brain is composed of approximately 10<sup>11</sup> processing elements, the neurons, which are extremely specialized cells. They generate electrical signals in response to chemical agents or other inputs and disseminate them through its axons to other cells (DAYAN; ABBOTT, 2005). The neuronal ionic mechanisms that generate the action potentials are known today mostly due to the pioneering work developed by Hodgkin and Huxley in 1952 (HODGKIN; HUXLEY, 1952). The neuron behavior is modeled by their approach by using four differential equations to represent the membrane dynamics and the non-linear conductances of three types of ion channels.

Since then, a lot of mathematical models were developed, such as the Integrate-and-Fire and the Izhikevich models (IZHIKEVICH, 2004), whose networks were proven to be computationally more powerful and yet consume lower power than the McCulloch–Pitts and threshold gates based ones (MAASS, 1996; MAASS, 1997; ZHANG et al., 2015). Consequently, there has been a lot of effort toward developing more biologically inspired learning algorithms, network structures, and applications of Spiking Neural Networks (SNNs).

Individual elements of information, however, are encoded in the brain by populations or clusters of interconnected neurons, rather than by single cells (POUGET; DAYAN; ZEMEL, 2000). It is also accepted that it is the type and timing of these spike trains that encodes communications between neurons within the brain. Consequently, there has been a lot of effort toward developing more biologically inspired Spiking Neural Networks and learning algorithms, thus aiming at the potential sources of cognition itself.

SNNs are essentially a population of spiking neurons, exchanging spikes to each other via weighted connections, reflecting the way real neurons project to others and interact through synapses (CAO; PIPA, 2010). Implementations of SNNs are largely used, and can be applied in various areas, such as character recognition (KULKARNI; BAGHINI, 2013; LIU; YUE, 2014), medical diagnosis and analysis (SUN et al., 2011; ROY; SCHAFFER; LARAMEE, 2013), financial predictions (REID; HUSSAIN; TAWFIK, 2013) and robotics (HULEA; CARUNTU, 2014; KERR et al., 2012; WANG et al., 2010; ALNAJJAR; MURASE, 2005), to name a few.

The development of SNNs in hardware has been a wide research area, since it benefits from the intrinsic parallel nature of hardware implementations, allowing very large speedups compared to software implementations in sequential machines. Several overview

and survey publications on digital hardware implementations of neural networks have been published (MAGUIRE et al., 2007; MISRA; SAHA, 2010; SCHÄFER et al., 2002).

Nevertheless, SNNs are difficult to train in a supervised fashion, mostly since all simple spiking neuron models have hard thresholding, which makes the calculation of gradients very prone to errors, deteriorating the learning rule's performance (SCHRAUWEN et al., 2008). One way to circumvent this drawback is by using fixed parameters, which is what is embodied by the Liquid State Machine (LSM) concept, developed by Maass, Natschläger and Markram (2002). Inspired by the fact that the neocortex processes a wide spectrum of information by stereotypical neural microcircuitry, the LSM consists of a reservoir receiving input spike trains and a group of readout neurons receiving signals from the reservoir. The concept, in which a recurrent network of spiking neurons is constructed in a way that the network parameters are fixed and randomly chosen, is similar to that of Echo State Network (ESN) (JAEGER, 2001a), being both part of a new paradigm named Reservoir Computing (RC) (VERSTRAETEN, 2009).

LSMs could benefit even more of hardware implementations, since for most of its applications, quite large networks of spiking neurons need to be simulated with hard real-time constraints (SCHRAUWEN et al., 2008). Furthermore, multiple outputs can be generated from the same reservoir, which in turn allows the implementation of a generic hardware reservoir component operating on different applications and with multiple outputs.

Nevertheless, the ever increasing size of the networks poses a huge challenge when it comes to its high inter-neuron connectivity requirements. If one would have the need to simulate the interconnection topology of, say, a mammalian neocortex, the number of synapses per neuron should be in average between  $2 \times 10^3$  and  $2 \times 10^4$  (JOHANSSON; LANSNER, 2007), which is a significant limiting factor in the suitability of its implementation in hardware. In the context of a similar connectivity problem on System-on-Chip (SoC) design, where interconnect scalability is paramount, the works from Benini and Micheli (2002), Dally and Towles (2001), Hemani et al. (2000) and Jantsch and Tenhunen (2003) introduced the concept of Network-on-Chip (NoC). Within such concept, elements from traditional computer networking are employed in order to realize the communication of the hardware structure.

There are already some efforts, both in academy and industry, in which the concept of Networks-on-Chip were utilized in order to implement highly scalable large-scale hardware neuromorphic systems. The magnitude of such projects has shown a large growth

in the number of neurons and synapses over the past years, relatively to the study in (MISRA; SAHA, 2010). Such a growth, although not yet near of reaching the human brain scale, is very encouraging since the ever-increasing ability to emulate parts of the brain makes it possible to understand its functioning. It also enables the improvement of computing tasks that involve learning and autonomous decision making capabilities such as autonomous robotics and assistive technologies.

However, there is still a huge ground to be covered, and the remaining challenges are also fundamental issues. There is still no consensus within the literature as of appropriate neuron models, interconnect and architectural issues, etc. There are also various design choices that need to be explored, such as new combinations of hierarchical topologies and the use of more complex neuron models within the systems. It is thus vitally important that such trend of research keep its growth in order to address the remaining challenges, so that the ambition to better understand the brain can be overcome.

The aim of this work is, consequently, to present DHyANA, a digital spiking neural network architecture which is optimized for liquid computing and employs the NoC concept for its inter-neuron communication. The system is intended to be as scalable, complex and biologically-realistic as possible, so it can ultimately assist in the exploration and understanding of neuroscience.

The main contributions of this work can be divided in two main parts: the development of DHyANA, an architecture which employs hierarchical topology and network-on-chip communication, intended to be used in later neuroscience and machine learning research; and the design of the hierarchical infrastructure of the DHyANA, by implementing a bus-based communication, used in the Cluster Level of the architecture, as well as the control, assemblage and decryption of the Global Network-on-Chip Packets.

### 1.2 Text Organization

Chapter 2 presents the background theory and the challenges faced when implementing each technology. Chapter 3 presents a review of the main current designs on neuromorphic hardware, divided into three categories. The sessions thus introduce the state-of-the art for non-scalable or special purpose works in FPGA, hardware implementations of LSMs and scalable and large scale general purpose SNNs in hardware (mostly using NoCs). Chapter 4 describes the proposed architecture, exploring its building blocks and design choices, as well as how they have been put together in order to become the

DHyANA architecture. Chapter 5 explores the Cluster Level, describing in deep detail its architecture and how it fits within the whole system. Chapter 6 indicates the results and comparison with the literature and industry state-of-the-art. Finally, Chapter 7 concludes the work and points some directions for future research.

### 2 BACKGROUND

In order to understand the constraints involved in neural networks modelling, the beginning of this chapter will explore some neurobiological premises. With a focus on the neurons, the first section offers a sufficient introduction to the phenomenological level of the models to be presented, even though they are a simplification of the true complexity of neurobiology. Next, the mathematical models that are used to simulate neuronal cells and their respective waveforms are covered, as well as the main trade-offs on their implementation. Then, a brief on information coding and networks of neurons will be presented, introducing the key aspects of timing and learning.

Hereafter, the key features of Reservoir Computing will be covered. The Liquid State Machines will be emphasized, for the aim of this work is to optimize the proposed architecture for this specific kind of network.

Lastly, the concepts and technologies of Networks-on-Chip will also be reviewed. Since it is a very important part of this project, NoCs will be carefully explained in the third section, as well as some of the most important design premises necessary for its implementation.

## 2.1 Spiking Neural Networks

## 2.1.1 Spiking Neurons: A Biological Perspective

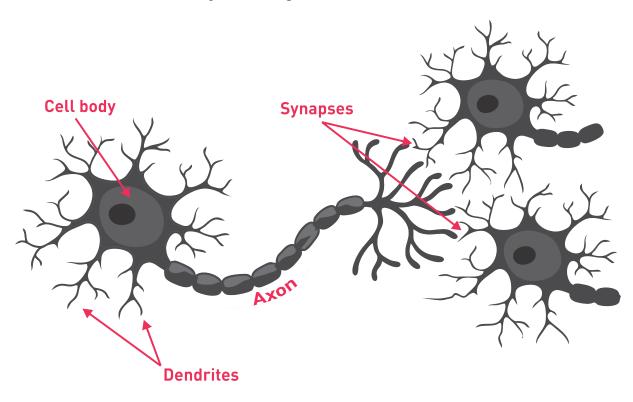

A neuron is an extremely specialized cell, which generates electrical signals in response to chemical agents or other inputs, and disseminate them through its axons to other cells (DAYAN; ABBOTT, 2005). As observable in Figure 2.1, the neuron is composed mainly by the cell body, or soma, the dendrites, and the axon, which may cross large portions of the brain or even of the entire body.

The axon may divide itself in order to connect with the dendrites of many other cells. In fact, the gray matter of the human brain contains a large amount of such axons, in the order of 4 km in every cubic millimeter (MAASS, 2002). These connections, which can be seen as some kind of chemical resistor, are called the synapses. The electrical potential between the intra- and extracellular medium of a neuron, which under resting (polarized) conditions is about -70mV, is the relevant signal to the nervous system (DAYAN; ABBOTT, 2005).

Figure 2.1: Representation of a neuron

Source: The author

A typical neuron receives more than 10,000 inputs from other neurons through their synapses (MAGUIRE et al., 2007), which produce electrical transmembrane currents that change the membrane potential of the neuron. These changes are called postsynaptic potentials (PSPs). Large currents may produce significant PSPs, which can be amplified by the voltage-sensitive channels embedded in the neuronal membrane, and that can generate an action potential or spike.

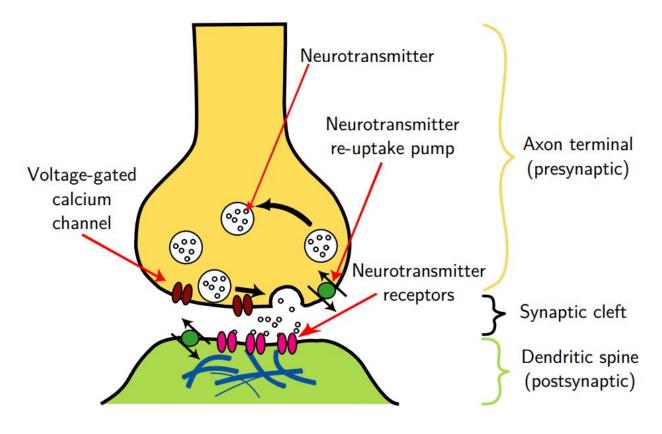

During a spike, the synapses release a neurotransmitter that quickly diffuses to the post-synaptic neuron. In the post-synaptic neuron, these neurotransmitters affect the neuron's membrane potential. Excitatory Postsynaptic Potentials (EPSPs) increase the membrane potential (depolarize), while Inhibitory Postsynaptic Potentials (IPSPs) decrease the membrane potential (hyperpolarization) (GRUNING; BOHTE, 2014).

In contrast to the spikes, which are all very similar, the size and shape of these PSPs depends on the particular synapse that causes it. Actually, it will also depend on the current "mood" and the recent "experiences" of the particular synapse, since the postsynaptic potentials have different sizes, depending on the pattern of spikes that have reached the synapse in the past, on the interaction of these spikes with the firing activity of

Figure 2.2: Main parts of a synapse

Source: Bekolay (2011)

the postsynaptic neuron, and also on other signals that reach the synapse in the form of various molecules (e.g. neurohormones) through the extracellular fluid (MAASS, 2002).

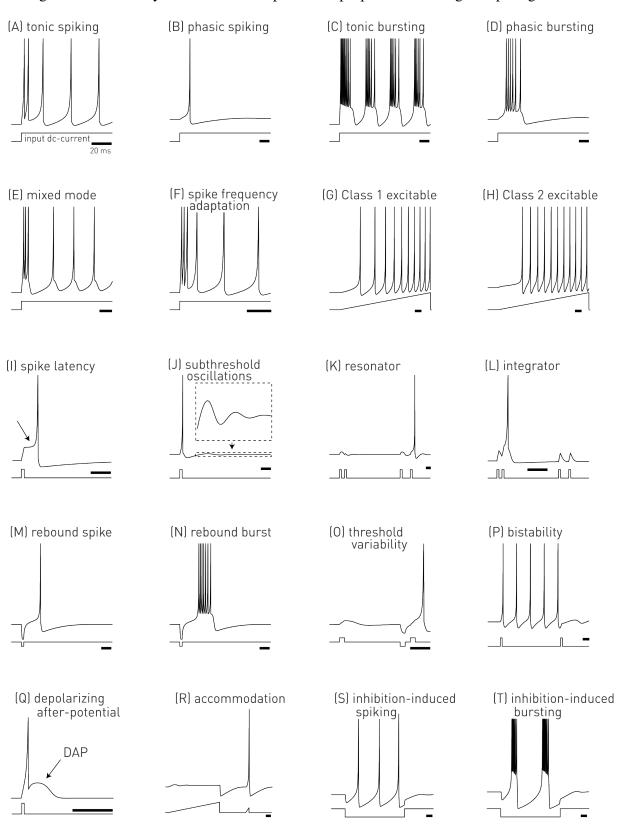

Furthermore, depending on the type or state of a neuron, or even the timing and type of inputs it just received, the characteristics of the spike train will also change. Hence, there are some different spiking modes, including but not limited to: phasic spiking, where a single isolated spike is fired; tonic spiking, where single spikes are fired at regular intervals; and tonic bursting, where small bursts of spikes are fired at regular intervals (THOMAS; LUK, 2009). They can be seen in Figure 2.3.

#### 2.1.2 Neuron Mathematical Models

There are many spiking neuron models, each varying in levels of complexity, computational intensity and biological accuracy, and a good overview of them can be seen in (IZHIKEVICH, 2004). The most biologically accurate and one of the most commonly used mathematical models of the neuron is the one developed by Hodgkin and Huxley

Figure 2.3: Summary of the neuro-computational properties of biological spiking neurons.

Source: Izhikevich (2004)

(1952). By researching the behavior of giant squid neurons (whose size is 100 to 1000 times larger than those in the human brain), they developed a mathematical model which can reproduce all kinds of neurons with a good precision in terms of shape of spikes and complex firing activities (AMBROISE et al., 2013). Nevertheless, this model also requires the estimation of a large number of parameters. Also, perhaps its major drawback is that the mathematical model is very computer intensive, as it uses up to as much as ten differential equations per neuron (FOX, 2013), which makes it even more problematic, especially in FPGA implementations, if one considers its hardware limitations.

Since the work from Hodgkin and Huxley was introduced, numerous models have been made in order to reduce its complexity. Nevertheless, none of the models is able to reach such biophysical accuracy, as well as the number of neural behaviors that the Hodgkin-Huxley model can reproduce. One of the simplest models is the Leaky Integrate-and-Fire (LIF), which uses only one differential equation to model the behavior of a neuron (FOX, 2013). It basically idealizes a neuron as having Ohmic leakage current and a number of voltage-gated currents de-activated at rest (IZHIKEVICH, 2007). The differential equation describes the voltage given by a capacitor charge, viewing the neuron as an integrator that, at a certain threshold voltage, is said to fire. Unfortunately, such simple mathematical model has flaws, in the sense that it is not as nearly biologically plausible, and may even be a waste of time for a computational neuroscientist who would want to simulate large-scale networks (IZHIKEVICH, 2007).

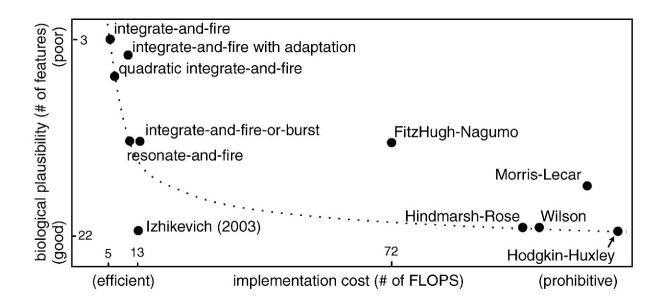

Another commonly used neuron mathematical model was proposed by Izhikevich (2003), and stands in the middle ground between complexity and biological plausibility scale, as observable in Figure 2.4. In fact, although not as simple as the integrate-and-fire, the Izhikevich model can mimic various nonlinear responses of biological neurons, making it almost as versatile as the Hodgkin-Huxley model at a fraction of its computational cost.

Note that, according to the metrics used by Izhikevich, the model proposed by him stands in an attractive position of the graphics when it comes to the trade-off between the two axes. Therefore, the model proves itself an interesting choice for digital implementations of neural networks, fact also confirmed by Table 2.1.

Figure 2.4: Biological Plausibility versus Computational Complexity of Spiking Neuron Models

Source: Izhikevich (2004)

Table 2.1: Comparison of the neuro-computational properties of spiking and bursting models. The "BIO" field means whether the model is biophysically meaningful; "FLP" is short for number of flops, an approximate number of floating point operations (addition, multiplication, etc.) needed to simulate the model during a 1 ms time span.

| Models            | BIO | (A) | (B) | (C) | (D) | (E) | (F) | (G) | (H) | (I) | (J) | (K) | (L) | (M) | (N) | (O) | (P) | (Q) | (R) | (S) | (T) | FLP  |

|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|

| IF                |     | х   |     |     |     |     |     | х   |     |     |     |     | х   |     |     |     |     |     |     |     |     | 5    |

| IF with adapt.    |     | X   |     |     |     |     | X   | X   |     |     |     |     | X   |     |     |     |     | X   |     |     |     | 10   |

| IF-or-burst       |     | x   | x   | X   | X   |     | X   | x   |     |     |     |     | x   | x   | x   |     | x   | x   |     |     |     | 13   |

| resonate-and-fire |     | X   | x   |     |     |     |     | X   | X   |     | x   | X   | X   | X   |     |     | x   | X   | X   |     |     | 10   |

| quadratic IF      |     | x   |     |     |     |     |     | x   |     | X   |     |     | x   |     |     | x   | x   |     |     |     |     | 7    |

| Izhikevich        |     | X   | X   | X   | X   | X   | X   | x   | X   | X   | x   | X   | X   | X   | X   | x   | X   | X   | x   | X   | x   | 13   |

| FitzHugh-Nagumo   |     | X   | X   |     | X   |     |     | X   |     | X   | x   | X   |     | X   |     | X   | X   |     | X   | X   |     | 72   |

| Hindmarsh-Rose    |     | X   | X   | X   | X   | X   | X   | X   | X   | X   | x   | X   | X   | X   | X   | X   | X   | X   | X   | X   | X   | 120  |

| Morris-Lecar      | x   | X   | X   |     | X   |     |     | X   | X   | X   | x   | X   | X   | X   | X   | X   | X   |     | X   | X   |     | 600  |

| Wilson            |     | X   | X   | X   | X   | X   | X   | X   | X   | X   | x   | X   | X   | X   | X   | X   | X   | X   | X   | X   | X   | 180  |

| Hodgkin-Huxley    | x   | X   | X   | X   | X   | X   | X   | X   | X   | x   | x   | X   | X   | X   | X   | x   | X   | X   | x   | X   | x   | 1200 |

Source: based on Fig 2 from Izhikevich (2004)

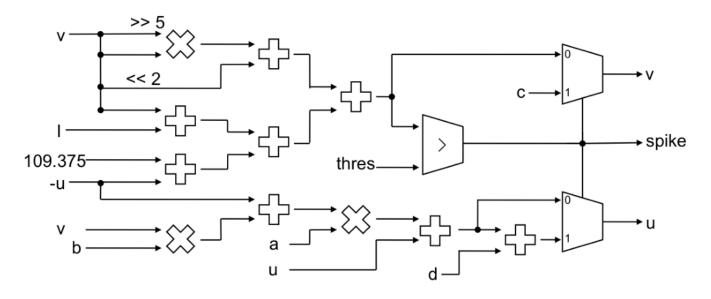

The neuron model idealized by Izhikevich is described by the following two coupled differential equations.

$$\frac{dv}{dt} = 0.04v^2 + 5v + 140 - u + I_{Izh}$$

(2.1)

$$\frac{du}{dt} = a(bu - v) \tag{2.2}$$

The variable v denotes the membrane potential, and u represents membrane recovery parameter. I is the synaptic input, and a, b are parameters controlling the dynamical behavior of the neural model. There is also a reset condition, controlled by the parameters c, d, and defined by equation (2.3).

$$v \ge 30mV \Rightarrow \begin{cases} v \leftarrow c \\ u \leftarrow u + d \end{cases} \tag{2.3}$$

## 2.1.3 Networks and Information Coding

The aim of artificial spiking neural networks is to carry out neural computation. This requires that meaning is given to neural spiking: the quantities relevant to the computation have to be expressed in terms of the spikes that neurons communicate with (GRUNING; BOHTE, 2014).

It is an accepted theory that individual elements of information are encoded in the brain by populations or clusters of interconnected neurons. Furthermore, the type and timing of these spike trains are essential for the encoding of communications between neurons within the brain.

Hence it would be appropriate to compare the output of a network of neurons with a piece of music played by an orchestra. To recognize such piece of music it is not enough to know how often each note is played by each musician. Instead one has to know how the notes of the musicians are embedded into the melody and into the pattern of notes played by other musicians (MAASS, 2002).

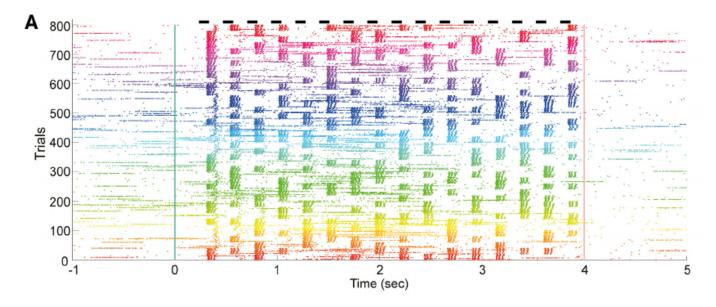

From this point of view, SNNs behave as complex systems, with "emergent macro-scopic-level properties resulting from the complex dynamic interactions between neurons, but hard to understand just looking at the microscopic-level of each neuron processing" (PAUGAM-MOISY; BOHTE, 2012). A way to visualize the temporal computation processed by an SNN is by displaying a complete representation of the network activity on a spike raster plot as in Figure 2.5, in which a small bar or dot is plotted each time that a neuron fires a spike. Variations and frequencies of neuronal activity can be observed in such diagrams, in the same way as natural neurons activities can be observed in spike

raster plots drawn from multi-electrode recordings.

Figure 2.5: Example of a Spike Raster Plot. A small dot is plotted each time (in abscissa) a neuron (numbered in ordinates) spikes.

Source: Ju et al. (2015)

Since the basic principle underlying SNNs is so radically different from McCulloch–Pitts' first generation Neural Networks, it comes with no surprise that much of the work on such networks, such as learning rules and theoretical results, had to be adapted, or even fundamentally reconsidered.

Traditionally, neural networks have been applied to pattern recognition, in various guises. For instance, multi-layer networks can perform highly accurate handwritten character recognition, financial predictions, robotics, as well as function approximation, or regression, by using classic learning rules, such as error-backpropagation, Hebbian learning or distance based variants like Kohonen self-organizing maps.

Efforts have been made in the direction of adapting traditional learning methods to spiking neural networks both by augmenting weights with delay lines and using temporal coding. Among such methods are: SpikeProp, a method similar to traditional error back-propagation proposed by Bohte, Poutre and Kok (2002); RProp a learning rate adjustment technique, first adapted to SNNs by McKennoch, Liu and Bushnell (2006); and QuickProp, where Newton's method is used for minimizing the error-gradient, first adapted to SNNs by Florian (2012); For more on the subject, the reader is referred to (BEKOLAY, 2011).

However, there has been another direction within the field, in which networks and computational algorithms are exclusively developed for spiking neural networks (PAUGAM-

MOISY; BOHTE, 2012). They use the temporal domain as well as the increased complexity of SNNs to arrive at novel methods for temporal pattern detection with Spiking Neuron Networks. Among the examples are: ReSuMe, a biologically inspired method in which the result is obtained from a spike-timing dependent plasticity rule, proposed by Potjans, Morrison and Diesmann (2009); the Spike-Timing Dependent Plasticity (STDP) (MARKRAM et al., 1997) rules; and the so-called Reservoir Computing, a new paradigm which was based on the observation that as long as a randomly generated network possess certain properties, it is not necessary to train it, and training only a recurrence-free linear readout is sufficient for many tasks (LUKOSEVICIUS; JAEGER., 2007). The Reservoir Computing paradigm, which recently triggered many practical applications of Recurrent Neural Networks and a whole new stream of research, will be overviewed in the next section.

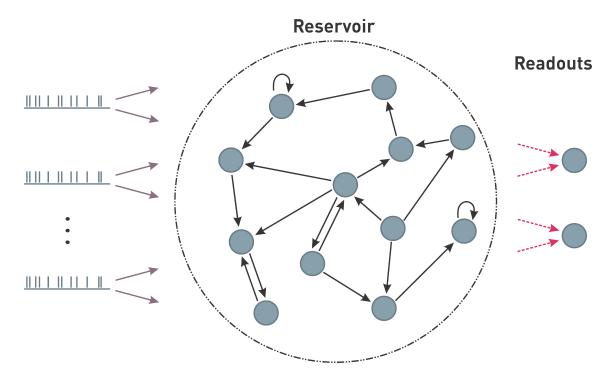

## 2.2 Reservoir Computing

The concept of Reservoir Computing was introduced by two independent publications, both of which, although using different approaches, presented the idea of a dynamic recurrent reservoir of processing units left in a transient state, while only the output layer is subject to a supervised learning. The first publication, by Jaeger (2001a), in which the Echo State Networks were introduced, explored applications of randomly connected recurrent networks of sigmoidal neurons to complex time series prediction tasks. The second one, by Maass, Natschläger and Markram (2002), which is a more biologically oriented approach, considered reservoirs of spiking neurons structured and functioning as inspired by the properties of neocortical columns in the central nervous system of mammals.

Later on, the Backpropagation Decorrelation (BPDC) learning rule was also introduced, along with a few other methods better described in (LUKOSEVICIUS; JAEGER., 2007; LUKOSEVICIUS; JAEGER, 2009; SCHRAUWEN; VERSTRAETEN; CAMPENHOUT, 2007). The fact that similar ideas were independently discovered several times underlines the importance of such concept, which is why the group of Benjamin Schrauwen proposed in (VERSTRAETEN et al., 2007) the unification of such ideas into a common research stream, which they propose to call Reservoir Computing.

The intuitive motivation behind this concept can be explained by imagining the use of a liquid (such as a glass of water) to perform computation, as explained by Cao and Pipa (2010). From a dynamical system's perspective, this does not make much sense since the only stable state to which the liquid can converge after a perturbation (e.g a drop in the

liquid) is a "dead" state where it is perfectly still. However, the idea of reservoir computing is that the transient states of the liquid at given time still holds relevant information about a perturbation that occurred at previous time. Providing that the liquid has the ability to produce significantly different transient states under two different inputs, it is then theoretically possible to extract information directly from measures on the state of the liquid since it is supposed to hold information about the past (e.g. successive pictures of the perturbed glass of water). (See Figure 2.6).

Figure 2.6: Structure of a RNN in the Framework of Reservoir Computing; Only Dotted Synaptic Connectivities are Trained.

Source: the author

In fact, the study in (FERNANDO; SOJAKKA, 2003) actually took the "reservoir" and "liquid" concepts quite literally and successfully trained a readout multilayer perceptron on several classification tasks by feeding input via mechanical actuators into a reservoir full of water and recording the state of its surface optically.

Several successful applications of reservoir computing to both synthetic data and real world engineering applications have been reported in the literature, including autonomous sine generation (JAEGER, 2001a), dynamic pattern classification (JAEGER, 2001b) and wind speed forecasting (FERREIRA et al., 2008). RC systems were used in robotics to control a simulated robot arm (JOSHI; MAASS, 2004), to model an exist-

ing robot controller (BURGSTEINER, 2005), for action prediction (BARAGLIA; NAGAI; ASADA, 2013), and for localization and event detection (HERTZBERG; JAEGER; SCHÖNHERR, 2002; ANTONELO; SCHRAUWEN; STROOBANDT, 2008). Applications in the field of Digital Signal Processing (DSP) have also been reportedly successful. Among those are speech recognition (VERSTRAETEN et al., 2005; GHANI et al., 2008), facial expression recognition (GRZYB et al., 2009), noise modeling (JAEGER; HAAS, 2004) or even classification of music styles (JU; XU; VANDONGEN, 2010).

## 2.2.1 Liquid State Machine

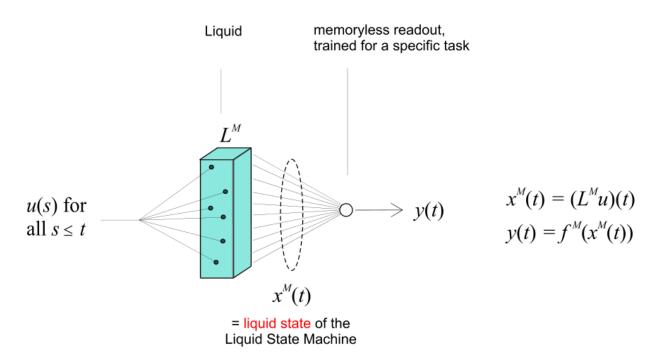

LSMs were introduced by a research lab active in robotics and neuroscience in the search for computational models that could help understanding the computations carried out in a local circuit of neurons in the neocortex (e.g. in a "cortical column"). Since it turned out to be quite successful, making it possible to carry out quite demanding computations with circuits consisting of spiking neurons and dynamical synapses, this approach will be the focus of this work.

The LSM was motivated by the hypothesis that the learning capability of an information processing device is its most delicate aspect, and that the availability of sufficiently many training examples is a primary bottleneck for goal-directed (i.e., supervised or reward-based) learning (MAASS, 2011). Thus, its architecture is composed of two layers (YAMAZAKI; TANAKA, 2007).

One layer is a reservoir of interacting spiking neurons showing recurrent topology that maps inputs into a dynamical state by generating a spatiotemporal activity pattern of neurons called a "liquid state". The network has to generate different liquid states for different input signals, because the performance of a liquid state machine mostly relies on the quality of the activity patterns. The other layer consists of neurons called "readouts", which receive the liquid state and instruction signals, compare its output to a target output in the training procedure and adapts its synaptic weights using a stateless learning rule.

Since all that needs to be trained is the readout module, instead of the recurrent neural network itself, learning is made fast and robust. The bulk of the LSM (the "Liquid") thus serves as pre-processor for such readout neuron, which amplifies the range of possible functions of the input streams u(t) that it can learn (MAASS, 2011). This also means that the same Liquid can serve a large number of different readout neurons, and each one can learn to extract a different "summary" of information from the same Liquid.

Figure 2.7: Structure of a Liquid State Machine (LSM)

Source: Maass (2011)

Formally (CAO; PIPA, 2010), the liquid of neurons is a mapping from time-dependent inputs  $\mathbf{u}(\cdot) = u\{u_i(\cdot)\}_i \in (1..k)$  lying in a subset  $U^k$  of  $(\mathbb{R}^{\mathbb{R}})^k$  onto a n-dimensional dynamical liquid state x(t) in  $(\mathbb{R}^{\mathbb{R}})^n$ :

$$L^M: U^k \to (\mathbb{R}^{\mathbb{R}})^n \tag{2.4}$$

$$u \mapsto x(t) \tag{2.5}$$

The second operation one needs to define is the readout function, mapping the liquid state into an output at every time t:

$$f^M: (\mathbb{R}^{\mathbb{R}})^n \to \mathbb{R}^{\mathbb{R}} \tag{2.6}$$

$$x(t) \mapsto y(t) \tag{2.7}$$

Thus, the liquid state machine is an operator, mapping time-varying functions onto one or many functions of time. Readout maps are generally chosen memory-less because

the liquid state x(t) should contain all the information about past inputs u(s), with  $s \ge t$ , that is required to construct the output y(t). Therefore, the readout function  $f^M$  at time t does not have to map previous liquid state x(s).

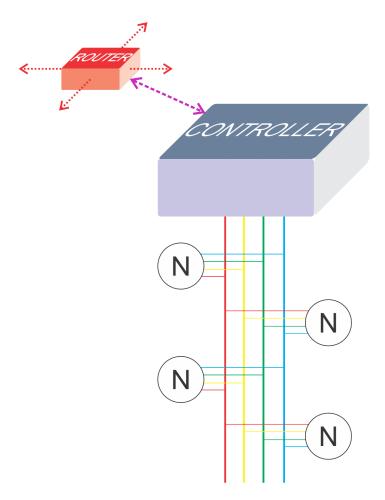

## 2.3 Networks-on-chip

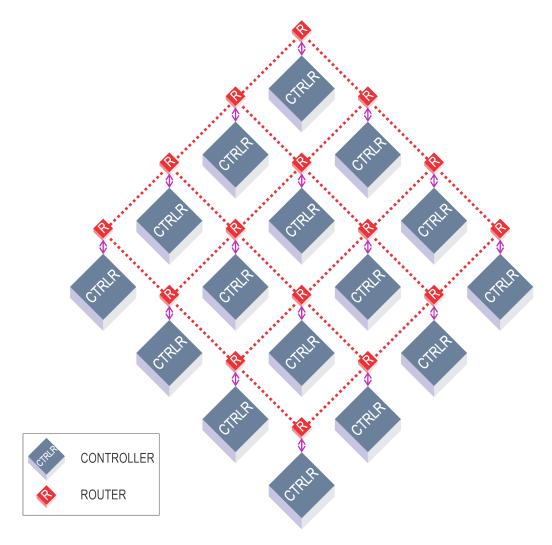

The ever increasing complexity and transistor count of nanoscale devices, where hundreds of IP cores are required to run multiple concurrent processes in a single chip, has put tremendous pressure on the communication architecture of SoCs, changing its entire design methodology to communication-based ones.

Two types of on-chip communication schemes have been traditionally used, namely, point-to-point (P2P) and bus-based communication architectures (LEE et al., 2008). P2P communication architectures can provide the utmost in communication performance at the expense of dedicated channels among all the communicating IP pairs, while they suffer from lack of scalability in terms of high complexity, cost, and design effort. On the other hand, bus-based architectures can connect a few tens of IP cores in a cost-efficient manner by reducing the design complexity and eliminating the dedicated wires required by P2P communication architectures, although they still fail to provide scalability enough when it comes to energy and performance.

The NoC-based approach represents a promising solution to the on-chip communication problems, scaling very well in terms of area, performance, power/energy consumption, and overall design effort. For this reason, scalability is said to be the utmost benefit from using NoCs. Figure 4 shows the three mentioned communication structures in a mobile phone.

Within its architecture, routing nodes are interconnected by P2P links, thus describing a network topology (NEDJAH; MOURELLE, 2014). The routing nodes are also connected to the processing elements that constitute the system, via a network interface (NI). Therefore, the information generated by a processing element, which may be divided into smaller parts, or packets, is sent over the network through the router attached to it via the NI (OGRAS; MARCULESCU, 2013). Then, the packet is stored at the input channels and the router starts servicing it. After that, the packet moves to the next router on its path and the process repeats until the packet arrives at its final destination. As a result, the communication among various cores is achieved by generating, processing and forwarding packets through the network infrastructure, rather than by routing global wires.

Memory

Memory

RF

Keypad

DSP

Keypad

DSP

Keypad

DSP

Keypad

DSP

Keypad

C) network

Figure 2.8: On-chip communication structures

Source: Bjerregaard and Mahadevan (2006)

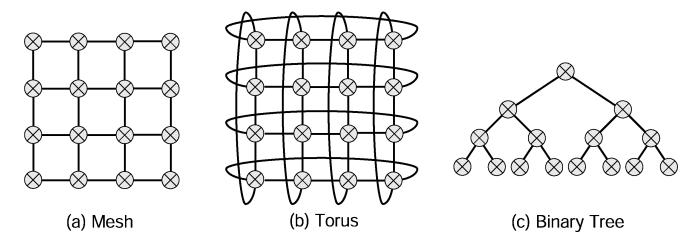

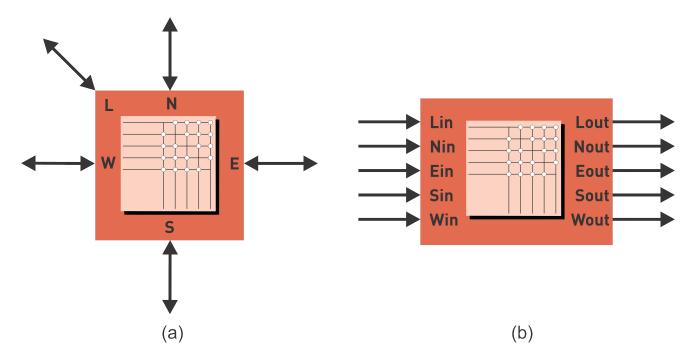

The ability of the network to efficiently disseminate information depends largely on its topology, which have a paramount effect on the network bandwidth, latency, throughput, overall area, fault-tolerance and power consumption, as well as an important role in designing the routing strategy and mapping the IP cores to the network (OGRAS; MAR-CULESCU, 2013). There have been various topologies for NoC architecture, including, but not limited to, mesh, torus, ring, butterfly, octagon and irregular interconnection networks (AGARWAL; SHANKAR, 2009). Figures 2.9 and 2.10 show examples of, respectively, regular and irregular forms of topologies.

Figure 2.9: Regular Forms of Topologies Scale Predictably with Regard to Area and Power. Examples are (a) 4-ary 2-cube mesh, (b) 4-ary 2-cube torus and (c) binary (2-ary) tree.

Source: Bjerregaard and Mahadevan (2006)

Figure 2.10: Irregular Forms of Topologies are Derived by Altering the Connectivity of a Regular Structure such as shown in (a) Where certain links from a mesh have been removed or by mixing different topologies such as in (b) where a ring coexists with a mesh.

Source: Bjerregaard and Mahadevan (2006)

Due to its simplicity and regularity structure, the mesh topologies are very attractive when it comes to timing closure improvement, reduction of dependency on interconnect scalability and facility to use high performance circuits. Thus, regular topologies, both one-dimensional (e.g. ring) and two-dimensional (e.g. mesh and torus) are the default choices for NoC designers (OGRAS; MARCULESCU, 2013).

For some implementations, customization might be desirable. For instance, when the size or shape of the cores varies widely, in which case regular topologies may waste area. The communication requirements of the components can also vary widely for real applications. Thus, designing the network to meet the requirements of highly communicating cores results in underutilization of other components, while designing it for the average case results in performance bottlenecks. Furthermore, a priori understanding of the communication workload can be exploited to fully customize the network topology, in case of application-specific implementations.

Generally speaking, the problem of optimal topology synthesis for a given application does not have a known theoretical solution. Although the synthesis of customized architectures is desirable, distorting the regular grid structure leads to various implementation issues such as complex floorplanning, uneven wire lengths, etc.

The design of the router is also a complex task in the implementation of a NoC, since it has significant impact in terms of performance, power consumption and area (OGRAS; MARCULESCU, 2013). The design involves determining the flow control

techniques, number of virtual channels, buffer organization, switch design, pipelining strategy while adhering to target clock frequency and power budgets.

The main focus in designing a router is to minimize the latency through it, while meeting bandwidth requirements. The router protocol concerns the strategy of moving data though the NoC (BJERREGAARD; MAHADEVAN, 2006). Figure 2.11 presents the major components of any routing node that is, buffers, switch, routing and arbitration unit, and link controller.

Injection Channel

Channel

LC

LC

LC

LC

Switch

LC

Routing and Arbitration

Figure 2.11: Generic Router Model. LC = link controller

Source: Bjerregaard and Mahadevan (2006)

The switch connects the input buffers to the output buffers, while the routing and arbitration unit implements the algorithm that dictates these connections. Thus, switching can be thought of as the mere transport of data, while routing can be defined as the intelligence behind it, in which the path of the data transport is determined (BJERREGAARD; MAHADEVAN, 2006).

The Routing algorithm determine the path between source and target switches for a

given packet (MELLO et al., 2004). It must prevent three situations: deadlock, livelock and starvation. The first can be defined as a cyclic dependency among nodes requiring access to a set of resources so that no forward progress can be made (MORAES et al., 2004). A livelock refers to packets circulating the network without ever making any progress towards their destination. And starvation is a condition in which a packet in a buffer requesting an output channel is blocked because the output channel is always allocated to another packet.

There is a vast parameter space when it comes to the communication infrastructure of the NoC. There may be concepts such as line and packet switching. Routing algorithms can be divided into static and adaptive algorithms as well as minimal-path and non-minimal-path ones (BLUME et al., 2008). Each of such choices might impact on all network metrics, thus being a key task of modern NoC design to efficiently explore the design space regarding all such aspects. Table 2.2 summarizes the most important parameters for a NoC communication infrastructure.

Table 2.2: Parameters for a NoC Communication Infrastructure

| Parameter    | Definition/Function                                                   |  |  |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------|--|--|--|--|--|--|--|

| Topology     | Defines the arrangement of routers and links in the form of a graph.  |  |  |  |  |  |  |  |

| Routing      | Determines how a message chooses a path in the graph.                 |  |  |  |  |  |  |  |

| Switching    | Defines how and when a router input channel is connected to an        |  |  |  |  |  |  |  |

| Switching    | output channel selected by the routing algorithm.                     |  |  |  |  |  |  |  |

| Flux Control | Deals with the allocation of channels and buffers for a message that  |  |  |  |  |  |  |  |

| Tiux Control | traverses the graph.                                                  |  |  |  |  |  |  |  |

| Arbitration  | Determines which input channel router can use a given output channel. |  |  |  |  |  |  |  |

| Memorization | Defines how and where messages blocked on a router will be stored.    |  |  |  |  |  |  |  |

Source: adapted from Zeferino (2003)

For detailed explanation of all the parameters, refer to the surveys in (BJERRE-GAARD; MAHADEVAN, 2006) and (OGRAS; MARCULESCU, 2013). This work will also present an exploration for all of its design choices in later sections.

The work in (NEDJAH; MOURELLE, 2014) suggests that, in general, NoCs are developed to perform a specific application. There is a variety of examples of such systems in the literature, and surveys such as (BJERREGAARD; MAHADEVAN, 2006), (MORAES et al., 2004) and (SALMINEN; KULMALA; HAMALAINEN, 2007) offer

comparison between their different design choices. Furthermore, some real CMOS application implementations reported to date are worth mentioning (HOWARD et al., 2010; VANGAL et al., 2007; CHEN et al., 2014).

#### 3 STATE-OF-THE-ART

There is a wide range of SNNs found in the literature. Several of them were developed using hardware, as the surveys from Maguire et al. (2007), Misra and Saha (2010) and Cassidy, Georgiou and Andreou (2013) demonstrate. The next sections will present a review of some specific types of SNNs, including their main aspects, results and applications.

### 3.1 Non-scalable or Special Purpose Works in FPGA

The work made by Ambroise et al. (2013), for instance, developed a neural network of 117 biorealistic neurons with one single computation core, which calculates each cell in turns. Their work, which was one main point of the Brainbow European project, was different in that it took into account biological real time. They implemented a Izhikevich neuron model using very few resources of a Xilinx Virtex 4 SX55.

Another spiking neural network implementation was made by Imperial College London (THOMAS; LUK, 2009). In their work, a 1024 neuron fully-connected network was implemented using the Virtex-5 XC5VLX330T device. Their architecture was based on re-usable interconnection for storing synapse weights and calculating thalamic input, making use of the large number of available FPGA's block-RAMs and fine-grain parallelism. Having Izhikevich as the model of choice as well, their work was able to run at a clock frequency of 133MHz, 16 times faster than a 3GHz Core2 CPU, and 1.1 times faster than a single-precision 1.2GHz 30-core GPU.

The work realized by Cassidy and Andreou (2008), from the Johns Hopkins University, developed an array of dynamical digital silicon neurons implementing the Izhikevich neuron model, as an extension of their previous works, which implemented a leaky integrate-and-fire neural array. The neural array, which was implemented in a Xilinx Spartan XC3S1500 FPGA, was composed of 32 physical neurons, each with 8 virtual neurons in a single FPGA, for a total of 256 independent neurons in the system operating at 80MHz. Recently, Cassidy, Georgiou and Andreou (2013) have very much incremented their work. While the work was derived from the aforementioned implementation, the synaptic weight RAM and the re-mapper RAM were both implemented in external SRAM in order to have higher RAM capacity.

While all of the works previously analyzed implemented the Izhikevich neuron

model, there are some worth mentioning neural networks that used the Hodgkin-Huxley model. The work from Smaragdos et al. (2014), for example, chose to implement an extended HH accelerator model, since their intention was to design a biophysically-meaningful model of the Inferior Olive, a part of the olivocerebellar subsystem in the brain responsible for motor coordination and learning. Using a Virtex 7 XC7VX485T FPGA, their design was able to simulate a network of 96 neurons in real-time, a performance with sufficient speedup for use in neuroscience experiments, which was more than x700 faster than their original Matlab model and x12.5 faster than their C implementation.

Another one is the work from Bonabi et al. (2014), where the authors developed a set of techniques for efficient implementation of the HH model in FPGA. In order to accomplish such optimizations, they used computational techniques such as CORDIC (Coordinate Rotation Digital Computer) algorithm and step-by-step integration in the implementation of arithmetic circuits, whose equations were described using VHDL as the hardware description language. They also used shared resources in order to preserve details of the model, to increase the network size and to keep the network execution speed close to real time while having high precision.

Perhaps the most relevant related work for this section is the one by Zamarreno-Ramos et al. (2013). The publication, from the Instituto de Microelectrónica de Sevilla, presented a modular, scalable method for assembling hierarchically structured neuromorphic AER systems. The approach, which can be accomplished by arranging modules in a 2D mesh, was tested on single and multiple Virtex-6 FPGAs. Among the applications tested are AER-based vision processing and character recognition based on convolutional type neural networks.

# 3.2 Reservoir Computing in Hardware

In spite of all the advantages that a Liquid State Machine can bring to hardware implementations, to the best of the author's knowledge, there are few SNN architectures with a focus on the subject to date. Perhaps this is due to the fact that this is a relatively new field of research.

There are, however, some very interesting and worth mentioning projects, such as the work in (SCHRAUWEN et al., 2008). The authors, from the Ghent University, are very engaged researchers in Reservoir Computer, with a great number of publications in the field. In the publication, they proposed an application oriented real-time, isolated digit speech

recognition in FPGA using a Liquid State Machine. The neurons were designed using the Leaky Integrate and Fire neuron model, but compensated their undeniable simplicity by combining then with both Dirac and exponential synapse models. The results are very promising, showing that real-time speech recognition is possible on very limited or even faulty FPGAs using an LSM.

The work in (WANG; JIN; LI, 2015), from Texas A&M University, developed a general-purpose Liquid State Machine based neuromorphic processor. It was shown that the resulting implementation, which is composed by a generic pre-processor and one or multiple task processors, efficiently reuses an optimized reservoir for different tasks. Such an encouraging result was made possible by an efficient reservoir re-use by power gating, in which a certain number of neurons are powered off to operate the reservoir with the desired size.

# 3.3 Scalable and Large Scale General Purpose SNNs in Hardware

Among the wide range of SNNs found in the literature, the most relevant proposed architectures for this work will be presented in this section. The focus of the strategic studies was on recent highly scalable hardware neuromorphic efforts. Most of them have implemented custom large-scale computing platforms and utilize network-on-chip strategies as the main communication structure.

The Neurogrid (see the website in (NEUGRID, 2006)) is a mixed signal neuromorphic multi-chip system developed at Stanford University. It uses analog computation to emulate neural dynamics, and a digital communication scheme to support synaptic connections. The main building block is the Neurocore, a 162mm² chip in a 180nm process (BENJAMIN et al., 2014), which is composed of an array of 65,536 analog quadratic integrate-and-fire neurons (CHOUDHARY et al., 2012). Altogether, a Neurogrid neuron has 61 graded and 18 binary programmable parameters—common to all the neurons in that Neurocore (for example, modeling a specific cell type in a layer of cortex). The system is formed by a total of 16 chips, organized in a tree routing network, in which the long-range connections are implemented using an FPGA daughterboard and a bank of SRAMs. The neurons on any chip send messages asynchronously to synapses on other chips via multicast communication (MEROLLA et al., 2014). In total, Neurogrid simulates one million neurons in real-time for approximately 3.1W.

The BrainScaleS project (see the website in (BRAINSCALES, 2011)) at the Uni-

versity of Heidelberg (which is the follow-on of the FACETS project (FACETS, 2005)) proposes a wafer-scale system called the Hybrid Multiscale Facility (HMF), composed of analog neurons and a digital multi-layer bus communication scheme. Their main processing building block is the High Input Count Analog Neural Network (HICANN) chip, containing up to 512 adaptive exponential integrate-and-fire neuron models and 112.000 synapses in total. 352 HICANN chips are located on a single wafer, organized in reticles of eight chips each, which makes a total of 4\*10<sup>7</sup> synapses and up to 180k neurons in a 20cm wafer. (SCHEMMEL et al., 2010). Furthermore, the wafer is not cut into separate chips, but left uncut, and a communication layer connecting the chips is added via post-processing (SCHMIDT, 2014). Larger systems can be built by interconnecting several wafer modules, being the communication based on a 2D-torus topology, implemented on a FPGA. The resulting system is said to operate at approximately up to 105 times faster than biological neurons real-time, however, this comes at the expense of an estimated power consumption of 1 kW per wafer in a 180nm technology.

The SpiNNaker is a project at University of Manchester (see the website in (SPINNAKER, 2005)) whose goal is to provide a platform for high-performance massively parallel processing appropriate for the simulation of large-scale neural networks in real-time. For that, a microprocessor-based system was developed, each node being a System-in-Package (SiP) fabricated by UMC on a 130nm CMOS process, containing 18 ARM968 processor cores plus a 128Mbyte off-die SDRAM stacked on top of it (FURBER et al., 2013). The nodes are packaged and mounted in a 48-node hexagonal array on a PCB (Printed Circuit Board), the full system requiring 1,200 such boards. The interconnection between each node is handled by an NoC using six links wrapped into a triangular lattice; this lattice is then folded onto the surface of a toroid. In operation, the engine consumes at most 90kW of electrical power for emulating 109 neurons and 1012 synapses, being 1W per node.

The EMBRACE (HARKIN et al., 2009) is another ongoing project that aims to enable future investigation of embedded neural network applications. The project from the University of Ulster and the National University of Ireland is a mixed-signal approach to NoC-based-embedded neural information hardware. The proposed architecture proposes a scalable SNN based on a hierarchical array of NoC routers, based on a hybrid star-mesh topology (CARRILLO et al., 2013). By doing so, the project exploits data locality by creating clusters of neurons located at the bottom of the hierarchy. Unlike the SpiNNaker, the EMBRACE architecture does not consider the use of multiprocessors to emulate

the neurons but instead uses an analogue, Integrate-and-Fire neuron cell on hardware to model spiking neurons. The synthesis results for the EMBRACE, based on 65-nm CMOS technology, demonstrates a low-cost area utilization of 0.587mm<sup>2</sup> and power consumption of 13.16mW for a single cluster facility of 400 neurons (CARRILLO et al., 2012). The project also offers a hardware acceleration relatively to the biological real-time, being able to accommodate firing frequencies of up to 174kHz.

The TrueNorth, which is the achievement of the Defense Advanced Research Projects Agency (DARPA) SyNAPSE project, is a chip from IBM and its university partners composed of 4096 neurosynaptic cores tiled in a 2-D array, containing an aggregate of 1 million digital neurons and 256 million synapses (AKOPYAN et al., 2015). The TrueNorth architecture uses hierarchical communication, with a high-fanout crossbar for local communication and a network-on-chip for long-distance communication, and global system synchronization to ensure real-time operation. The chip, fabricated using Samsung's 28-nanometer process technology, operates at real-time with an impressive low typical power consumption of 56mW. It also attains a peak computational performance of 58 giga-synaptic operations per second (GSOPS) and computational energy efficiency of 400 GSOPS per Watt (GSOPS/W).

The Reconfigurable On-line Learning Spiking Neuromorphic Processor (ROLLS neuromorphic processor) is a full-custom mixed-signal VLSI device with learning circuits that emulate the biophysics of real spiking neurons and dynamic synapses (QIAO et al., 2015). Idealized by the Professor Giacomo Indiveri's group at the Institute of Neuroinformatics, University of Zurich and ETH Zurich, the chip was developed for exploring the properties of computational neuroscience models and for building brain-inspired computing systems. Having approximately 12.2 million transistors, the chip was fabricated using standard 180 nm Complementary Metal-Oxide-Semiconductor (CMOS) 1P6M process occupies an area of 51.4 mm<sup>2</sup>.

By comparing all the above projects, the reader is able to identify some similarities and major differences among them. The BrainScaleS, Neurogrid and EMBRACE projects all implemented different adaptations of integrate-and-fire analog neuron models, while both the TrueNorth and SpiNNaker preferred to work with digital neurons. All the designs implemented some kinds of on and off-chip networks, although the topologies greatly differ. Although those are examples of design choices that significantly affect the final results, the similarities among some designs were not enough to produce similar design specs, with even the quantity of neurons and synapses per chip being very different for

expectedly similar cases. Consequently, it is not difficult to infer that several design choices have yet to be explored and combined to others in order to better understand their impacts on the systems as well as to determine the optimal cases for each project.

Table 3.1 shows a summary of some relevant data from the aforementioned neuromorphic architectures. Note that although related, most measurements are not from the same benchmark nor use the same technology, so they cannot be compared directly.

Table 3.1: Related Work synthesis data

| Project     | Neuron     | A/D | Neurons     | Power      | Power/   | Size         | Area/    | CMOS    | Synapses per | Topology                   |  |

|-------------|------------|-----|-------------|------------|----------|--------------|----------|---------|--------------|----------------------------|--|

| Name        | Model      |     |             |            | Neuron   | ${\rm mm^2}$ | Neuron   | Process | Neuron       | Topology                   |  |

| SpiNNaker   | IF or IZHI | DS  | $16x10^{3}$ | 1 <b>W</b> | 6,25E-05 | 102          | 6,38E-03 | 130nm   | $1x10^{3}$   | Triangular Lattice*        |  |

| Neurogrid   | Quad. IF   | A   | 983,040     | 5W         | 5,08E-06 | 168          | 1,71E-04 | 180nm   | $6x10^9$     | Star                       |  |

| BrainScaleS | Exp. IF    | A   | 512         | 1kW        | 1,95     | 430          | 8,40E-01 | 180nm   | $112x10^{3}$ | Hierarchical Buses**       |  |

| EMBRACE     | IF         | A   | 400         | 13.16mW    | 3,29E-05 | 0.587        | 1,47E-03 | 65nm    | 400          | Hybrid (star-mesh)         |  |

| TrueNorth   | -          | -   | $1x10^{6}$  | 65mW       | 5,60E-08 | 430          | 4,30E-04 | 28nm    | 256          | Mesh                       |  |

| ROLLS       | Exp. IF    | A   | 256         | 4mW        | 1,56E-05 | 51.4         | 2,01E-01 | 180nm   | 256          | Programmable Switch-matrix |  |

A = Analog, D = Digital, DS = Digital (Software), IF = Integrate-and-Fire, IZHI = Izhikevich. \*folded into a toroid surface. \*\*2D Torus (wafer). SpiNNaker, BrainScaleS, TrueNorth data per chip; EMBRACE data per cluster.

Source: The author

#### 4 PROPOSED NEUROMORPHIC ARCHITECTURE

In common with most engineering projects, the development of the proposed neuromorphic architecture required a careful consideration of many trade-offs and compromises. This chapter presents an overview of the Digital HierArchical Neuromorphic Architecture (DHyANA), including the description of its main building blocks, a careful explanation of the system's behavior and a discussion about the main trade-offs and design choices that made possible the realization of this project.

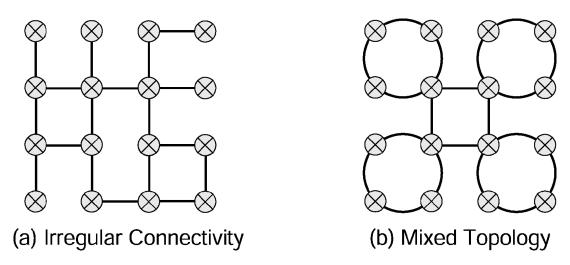

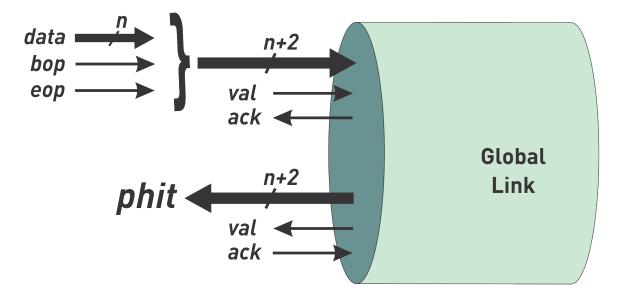

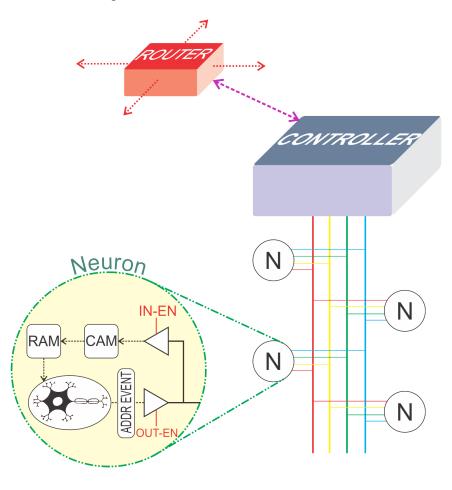

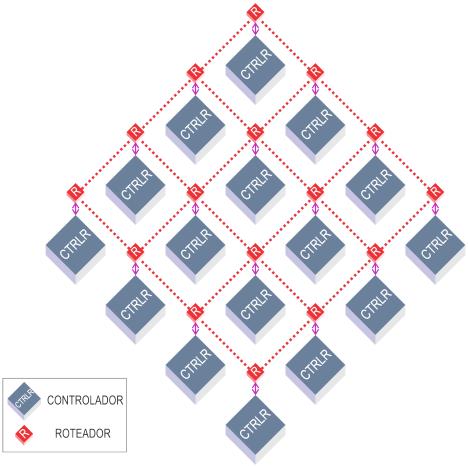

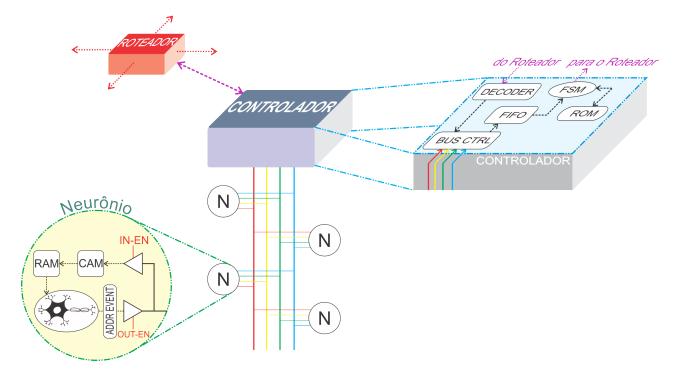

DHyANA is a Neural Network composed of a two-level hierarchical network-onchip. The processing elements, digital Izhikevich neuron models, as well as a Controller are locally connected through a shared bus at the Cluster Level. The interface between the two levels is achieved through a connection between the Controller and its corresponding Router. Finally, at the Global level, a 2D Mesh NoC performs the connection between clusters of neurons. A system's view at the Global Level is available at Figure 4.1. It shows the system prototype size for the global communication, a 4x4 mesh topology.

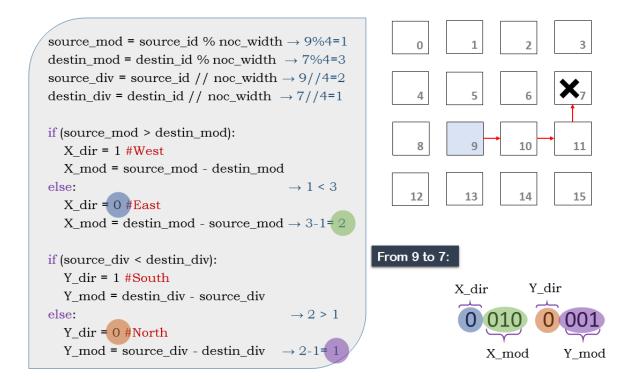

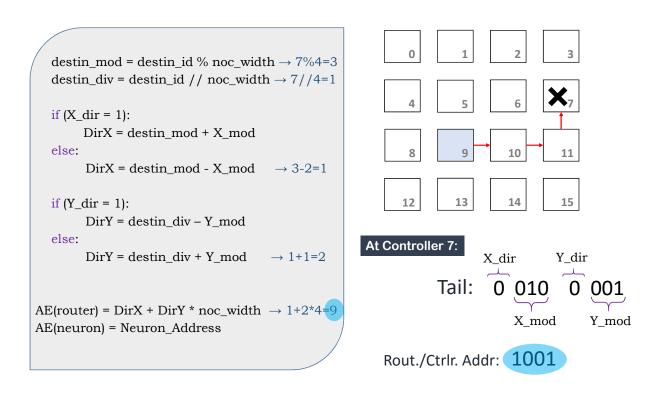

The motivation for choosing bus and mesh, two well-known topologies, as communication levels of the hierarchy was driven by practicality, performance and energy optimizations. Bus-based designs have been well architected for small multichip processors, within the order of very few tens of IP cores, being quite simple and power efficient. Nevertheless, as mentioned in section 2.3, such topology does not scale for larger configurations. Thus, a bus-based topology was considered very well suited to support local communication, while the choice for a planar, low complexity mesh topology was considered appropriate for the global network.