# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

## FILIPE MACIEL LINS

# The Effects of the Compiler Optimizations in Embedded Processors Reliability

Thesis presented in partial fulfillment of the requirements for the degree of Master of Microeletronics

Advisor: Prof. Dr. Paolo Rech

Porto Alegre September 2017

# CIP — CATALOGAÇÃO NA PUBLICAÇÃO

Lins, Filipe Maciel

The Effects of the Compiler Optimizations in Embedded Processors Reliability / Filipe Maciel Lins. – Porto Alegre: PGMI-CRO da UFRGS, 2017.

95 f.: il.

Dissertação (Mestrado) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2017. Advisor: Paolo Rech.

1. Fault Injector. 2. Compiler Optimization. 3. Embedded Processors. 4. Soft Errors. 5. COTS. I. Rech, Paolo. II. The Effects of the ComThe Effects of the Compiler Optimizations in Embedded Processors Reliability.

## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves

Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb Coordenadora do PGMICRO: Prof<sup>a</sup>. Fernanda Lima Kastensmidt

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

| "If I have seen farther than others,               |

|----------------------------------------------------|

| it is because I stood on the shoulders of giants." |

| — SIR ISAAC NEWTON                                 |

## **ACKNOWLEDGMENTS**

To UFRGS, Institute of Informatics, PGMICRO, and the Brazilian research agencies CNPq for the financial support and for putting their facilities at my disposal so I could develop my research.

To my advisor, Paolo Rech, for the confidence, lessons, and patience. Thank you for pushing me forward and encouraging me in my academic and personal decisions.

To all my colleagues from laboratories 230 from UFRGS and others that are already in other rooms, cities, or countries.

To all of you, my sincere thanks.

#### **ABSTRACT**

The recent advances in the embedded processors increase the compilers complexity, and the usage of heterogeneous resources such as Field Programmable Gate Array (FPGA) and Graphics Processing Unit (GPU) integrated with the processors. Additionally, the increase in the usage of Commercial off-the-shelf (COTS) instead of radiation hardened chips in safety critical applications occurs because the COTS can be more flexible, inexpensive, have a fast time-to market and a lower power consumption. However, even with these advantages, it is still necessary to guarantee a high reliability in a system that uses a COTS for safety critical applications because they are susceptible to failures. Additionally, in the case of real time applications, the time requirements also need to be respected. As a case of study, this work uses the Zynq which is a COTS device classified as an All Programmable System-on-Chip (APSOC) and has an ARM Cortex-A9 as the embedded processor. In this research, the impact of faults that affect the register file in the embedded processors reliability was investigated. For that, fault-injection and heavy-ion radiation experiments were performed. Moreover, an evaluation of how the different levels of compiler optimization modify the usage and the failure probability of a processor register file. A set of six representative benchmarks, each one compiled with three different levels of compiler optimization. Exhaustive fault injection campaigns were performed to measure the registers Architectural Vulnerability Factor (AVF) of each code and configuration, identifying the registers that are more likely to generate Silent Data Corruption (SDC) or Single Event Functional Interruption (SEFI). Moreover, the observed reliability variations with register file utilization were correlated. Finally, two of the selected benchmarks, each one compiled with two different levels of optimization were irradiated in the heavy ions experiments. The results show that the best performance, the minor register file usage, or the lowest AVF does not always bring the highest Mean Workload Between Failures (MWBF). As an example, in the Matrix Multiplication (MxM) application, the best performance is achieved in the highest compiler optimization. However, in the fault injection, the higher reliability is obtained in the lower compiler optimization which has, the lower AVFs and the lower register file usage. Results also show that the impact of optimizations is strongly related to the executed algorithm and how the compiler optimizes them.

Keywords: Fault Injector. Optimization. Processor. Reliability. Soft Errors. COTS.

# APSoC. MWBF. AVF.

#### **RESUMO**

O recente avanço tecnológico dos processadores embarcados aumentou a complexidade dos compiladores e o uso de recursos heterogêneos, como Arranjo de Portas Programáveis em Campo (Field Programmable Gate Array - FPGA) e Unidade de Processamento Gráfico (Graphics Processing Unit - GPU), integrado aos processadores. Além disso, aumentou-se o uso de componentes de prateleira (Commercial off-the-shelf - COTS) em aplicações críticas, ao invés de chips tolerantes a radiação, pois os COTS podem ser mais baratos, flexíveis, terem uma rápida colocação no mercado e um menor consumo de energia. No entanto, mesmo com essas vantagens, os COTS são suscetíveis a falha sendo necessário garantir uma alta confiabilidade nos sistemas utilizados. Assim como, no caso de aplicações em tempo real, também se precisa respeitar os requisitos determinísticos. Como caso de estudo, este trabalho utiliza a Zynq que é um dispositivo COTS do tipo Sistema em Chip Totalmente Programável (All Programmable System on Chip -APSoC) no qual possui um processador ARM Cortex-A9 embarcado. Nesta pesquisa, investigou-se o impacto das falhas que afetam o arquivo de registradores na confiabilidade dos processadores embarcados. Para tanto, experimentos de injeção de falhas e de radiação de íons pesados foram realizados. Além do mais, avaliou-se como os diferentes níveis de otimização do compilador modificam o uso e a probabilidade de falha do arquivo de registradores do processador. Selecionou-se seis benchmarks representativos, cada um compilado com três níveis diferentes de otimização. Realizamos campanhas exaustivas de injeção de falhas para medir o Fator de Vulnerabilidade Arquitetural (Architectural Vulnerability Factor - AVF) de cada código e configuração, identificando os registradores que são mais propensos a gerar uma corrupção de dados silenciosos (Silent Data Corruption - SDC) ou uma interrupção funcional de evento único (Single Event Functional Interruption - SEFI). Também foram correlacionadas as variações de confiabilidade observadas com a utilização do arquivo de registradores. Finalmente, irradiamos com íons pesados dois dos benchmarks selecionados compilados com dois níveis de otimização. Os resultados mostram que mesmo com o melhor desempenho, o menor uso do arquivo de registradores ou o menor AVF não é garantido que as aplicações irão alcançar a maior Carga de Trabalho Média Entre Falhas (Mean Workload Between Failure - MWBF). Por exemplo, os resultados mostram que o melhor desempenho da aplicação Multiplicação

de Matrizes (Matrix Multiplication - MxM) é alcançado no nível de otimização mais alta. No entanto, nos resultados dos experimentos de injeção de falhas, a maior confiabilidade é alcançada no menor nível de otimização que possuem os menores AVFs e o menor uso do arquivo de registradores. Os resultados também mostram que o impacto das otimizações está fortemente relacionado com o algoritmo executado e como o compilador faz esta otimização.

**Palavras-chave:** Injetor de Falhas, Otimizações, Confiabilidade, Processadores, COTS, APSoC, MWBF, AVF.

## LIST OF ABBREVIATIONS AND ACRONYMS

ACP Accelerator Coherency Port

ADC Analogue-to-digital Converter

AES Advanced Encryption Standard

AMBA ARM Advanced Microcontroller Bus Architecture

APSoC All Programmable System on Chip

APU Application Processing Unit

ARM Advanced Risc Machine

ASIC Application Specific Integrated Circuit

AXI Advanced eXtensible Interface

CAN Controller Area Network

CISC Complex Instruction Set Computing

CLB Configure Logic Block

COLE Compiler Optimization Level Exploration

COTS Commercial off-the-shelf

CPU Central Processing Unit

DAC Digital-to-analogue Converter

DCE Dead Code Elimination

DSP Digital Signal Processor

DUT Design Under Test

ECC Error Correcting Coding

EMIO Extended Multiplexed Input/Output

FF Flip Flop

FFT Fast Fourier Transform

FIFO First In First Out

FPGA Field Programmable Gate Array

FPU Floating Point Unit

GCC GNU Compiler Collection

GDB GNU Debugger

GPIO General Purpose Input/Output

IOBs Input/Output Blocks

IPC Instructions Per Cycle

JPEG Joint Photographic Experts Group

LUT Lookup Table

MIO Multiplexed Input/Output

MMU Memory Management Unit

MMU Memory Management Unit

MPE Media Processing Engine

MWTF Mean Work Time to Failure

MxM Matrix Multiplication

OCM On Chip Memory

PC Program Counter

PL Programmable Logic

PS Processing System

PSoC Programmable System on Chip

RAM Random Access Memory

RISC Reduced Instruction Set Computing

ROM Read Only Memory

SCU Snoop Control Unit

SIMD Single Instruction Multiple Data

SoC System on Chip

SPI Serial Peripheral Interface

TSMC Taiwan Semiconductor Manufacturing Company

UART Universal Asynchronous Receives Transmitter

USB Universal Serial Bus

# LIST OF FIGURES

| Figure 2.1                                                | Radiation Sources in Space                                          | .20 |

|-----------------------------------------------------------|---------------------------------------------------------------------|-----|

| -                                                         | Radiation effects                                                   |     |

|                                                           | SEU and SET in circuits                                             |     |

| Figure 4.1                                                | An example of APSOC: the Xilinx Zynq-7000                           | .31 |

|                                                           | Single Instruction Multiple Data processing in NEON                 |     |

|                                                           | The PL structure of Zynq-7000                                       |     |

|                                                           | The Configurable Logic Block (CLB)                                  |     |

| Figure 5.1                                                | Heavy ion experiment setup mounted at the beam line of the LAFN-USP | .47 |

| Figure 5.2                                                | View of the surface of a Zynq-7000 device                           | .47 |

| Figure 5.3                                                | Fault Injector First Setup                                          | .49 |

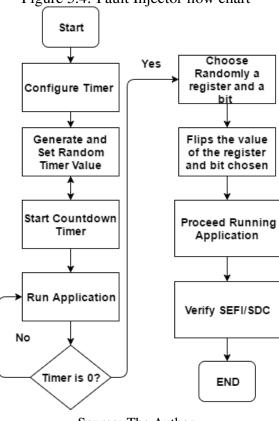

| Figure 5.4                                                | Fault Injector flow chart                                           | .50 |

| Figure 5.5                                                | Fault Injector Modifications of (OLIVEIRA; TAMBARA; KASTENS-        |     |

|                                                           | , 2017)                                                             | .51 |

| Figure 5.6                                                | Fault Injector Final Setup                                          | .52 |

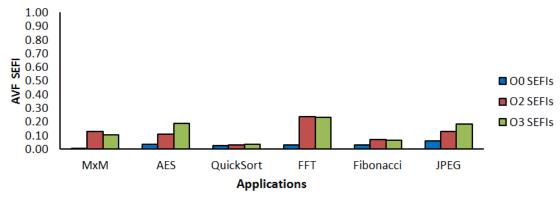

| Figure 6.1                                                | Total Architectural Vulnerability Factor SDCs                       | .58 |

| Figure 6.2 Total Architectural Vulnerability Factor SEFIs |                                                                     | .58 |

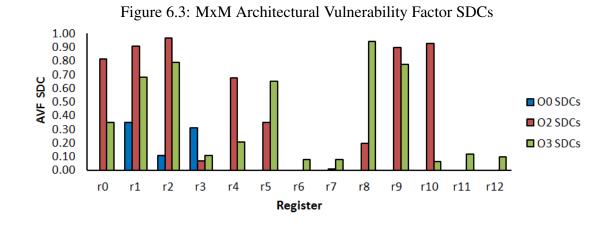

| Figure 6.3                                                | MxM Architectural Vulnerability Factor SDCs                         | .59 |

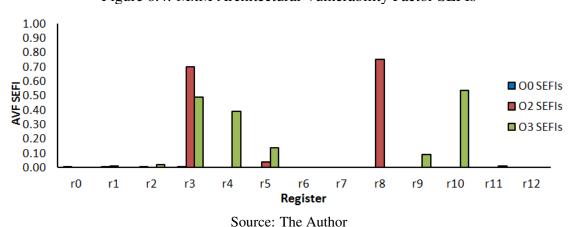

| Figure 6.4                                                | MxM Architectural Vulnerability Factor SEFIs                        | .59 |

| Figure 6.5                                                | AES Architectural Vulnerability Factor SDCs                         | .60 |

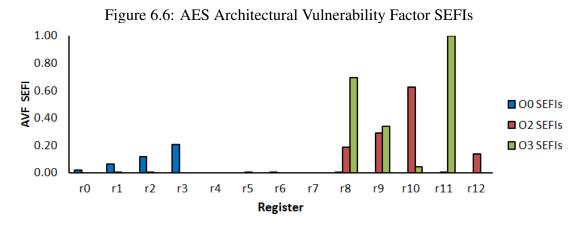

| Figure 6.6                                                | AES Architectural Vulnerability Factor SEFIs                        | .60 |

| Figure 6.7                                                | AVF SDC MxM Double O3                                               | .62 |

| Figure 6.8                                                | AVF SDC MxM Double O3                                               | .62 |

| Figure 7.1                                                | AVF and Cross Section in MxM                                        | .67 |

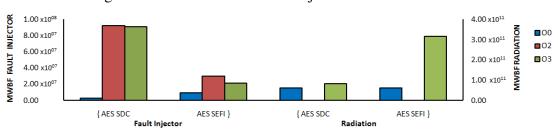

|                                                           | Radiation and Fault Injection MWBFs in MxM                          |     |

|                                                           | AVF x Cross Section in AES                                          |     |

| Figure 7.4                                                | Radiation and Fault Injector MWBFs in AES                           | .68 |

# LIST OF TABLES

| Table 3.1 The main GCC optimizations and the levels at which they are enabled     | 26 |

|-----------------------------------------------------------------------------------|----|

| Table 4.1 The Zynq Logic Fabric Resources                                         | 34 |

| Table 4.2 Compiler Optimization effects on code execution, resources utilization  | 40 |

| Table 6.1 Compiler Optimization effects on code execution, resources utilization, |    |

| and reliability                                                                   | 54 |

| Table 6.2 Fault Injection Results                                                 |    |

| Table 6.3 Heavy Ions Experiment Results                                           |    |

| Table 6.4 Number of Reads and Writes in the main memory                           |    |

| Table A.1 Results of Fault Injection MxM O0                                       | 74 |

| Table A.2 Results of Fault Injection MxM O2                                       |    |

| Table A.3 Results of Fault Injection MxM O3                                       | 76 |

| Table A.4 Results of Fault Injection AES O0                                       |    |

| Table A.5 Results of Fault Injection AES O2                                       |    |

| Table A.6 Results of Fault Injection AES O3                                       | 79 |

| Table A.7 Results of Fault Injection Quicksort O0                                 |    |

| Table A.8 Results of Fault Injection Quicksort O2                                 | 81 |

| Table A.9 Results of Fault Injection Quicksort O3                                 | 82 |

| Table A.10 Results of Fault Injection FFT O0                                      |    |

| Table A.11 Results of Fault Injection FFT O2                                      | 84 |

| Table A.12 Results of Fault Injection FFT O3                                      | 85 |

| Table A.13 Results of Fault Injection Fibonnaci O0                                | 86 |

| Table A.14 Results of Fault Injection Fibonnaci O2                                | 87 |

| Table A.15 Results of Fault Injection Fibonnaci O3                                | 88 |

| Table A.16 Results of Fault Injection JPEG O0                                     | 89 |

| Table A.17 Results of Fault Injection JPEG O2                                     | 90 |

| Table A.18 Results of Fault Injection JPEG O3                                     | 91 |

| Table A.19 Results of Fault Injection MxM Double O3                               |    |

| Table A.20 Results of Fault Injection MxM Double O3 Continuation                  |    |

| Table A.21 Results of Fault Injection MxM Double O3+                              |    |

| Table A.22 Results of Fault Injection MxM Double O3+ Continuation                 |    |

# **CONTENTS**

| 1 INTRODUCTION                                                  |    |

|-----------------------------------------------------------------|----|

| 1.1 Objectives and Contributions                                | 16 |

| 1.2 Organization                                                | 16 |

| 2 BACKGROUND                                                    | 18 |

| 2.1 RISC Architecture                                           |    |

| 2.2 Soft Errors Effects in Embedded Processors                  | 20 |

| 3 CODE OPTIMIZATION EFFECTS                                     | 24 |

| 3.1 Why optimizations?                                          | 24 |

| 3.2 What are the optimizations?                                 | 24 |

| 3.3 Optimizations effects in performance and energy consumption |    |

| 3.4 State of the art                                            |    |

| 4 CASE STUDY: THE EMBEDDED ARM A9                               | 30 |

| 4.1 All Programmable System-on-Chip                             | 30 |

| 4.1.1 Processing System                                         | 30 |

| 4.1.2 Programmable Logic                                        | 33 |

| 4.1.3 The PS - PL Interfaces                                    | 36 |

| 4.2 Algorithms                                                  |    |

| 4.3 Setups                                                      |    |

| 5 RELIABILITY EVALUATION METHODOLOGY                            | 43 |

| 5.1 Beam experiment vs fault injection                          |    |

| 5.2 Reliability Metrics                                         |    |

| 5.3 Heavy ion experiment                                        | 46 |

| 5.4 Fault injection framework                                   | 48 |

| 6 RESULTS                                                       | 53 |

| 6.1 Fault Injection Results                                     |    |

| 6.1.1 General purpose Register Setup Results                    |    |

| 6.1.2 NEON Setups Results                                       | 62 |

| 6.2 Heavy Ions Experiment Results                               |    |

| 6.3 An Analysis of the Dynamic Disassembly Code                 |    |

| 7 CONCLUDING REMARKS                                            |    |

| 7.1 Discussion                                                  |    |

| 7.2 Future Work                                                 |    |

| REFERENCES                                                      |    |

| APPENDIX A — TABLES                                             | 74 |

| A.1 MxM Tables                                                  |    |

| A.2 AES                                                         |    |

| A.3 Quicksort                                                   |    |

| A.4 FFT                                                         |    |

| A.5 Fibonnaci                                                   |    |

| A.6 JPEG                                                        |    |

| A.7 MxM Double                                                  | 92 |

#### 1 INTRODUCTION

Commercial-Off-The-Shelf (COTS) systems are becoming attractive for safety-critical applications, like biomedical implantable devices, automotive control systems, aircraft or satellite stabilizers and control circuitry. The main reason for preferring a COTS device to specifically designed rad hard chips is that the latter are typically very expensive as they require unique circuit design and lithography to meet the reliability requirements and the produced volumes are low. On the contrary, COTS components can be low-cost, flexible, have fast time-to-market, low power consumption.

The CHREC Space Processor (CSPv1) is mainly formed around a Xilinx Zynq-7020 Processor which is an example of COTS (RUDOLPH et al., 2014). Unfortunately, COTS systems are very susceptible to radiation effects, particularly Single Event Effects (SEEs). The single impinging particle can generate different types of effects on digital systems. If the particles hit a storage element, such as Static Random Access Memory (SRAM) structures, caches, and registers, it may cause a bit flip. Particles can also modify the result of operations by generating Single Event Transients (SETs) in logic gates.

Reduced Instruction Set Computing (RISC) architectures became popular thanks to the advances in compiler efficiency. In order to succeed in executing complex algorithms using few, simple, and two-inputs instructions, the compiler needs to modify the source code significantly. In recent years, compilers have allowed users to select different levels of optimization to be applied to the code. Optimization is achieved by modifying the number, the usage, and the reference of registers.

Most modern embedded processors are built with RISC architecture which allows only a few basic instructions to be executed, and inputs can come only from the register file. In other words, RISC is a load-store architecture: data in the main memory must be loaded to the register file to be digested, and the data in the register file must be stored in the main memory to be accessible to the user. Hence, the register file is a critical resource for modern computing architectures. As any data to be processed will need to pass through the register file, knowing the probability of an error in a register to propagate to the output may be sufficient to characterize the vulnerability of an application.

Register files have been identified as the most critical resources in modern computing systems (TAN et al., 2011; ISAZA-GONZÁLEZ et al., 2016). Unfortunately, registers cannot be easily protected. Unlikely Dynamic Random Access Memory (DRAM), which can be protected with Error Correcting Codes (ECC), or caches, for which parity

protection is more common than ECC, register files are integrated into the circuitry of processors, increasing the efforts and penalties of adding ECC (ASADI et al., 2005).

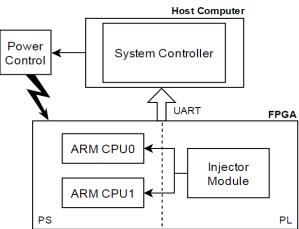

For these reasons, the focus of this research is the reliability impact of register file errors in embedded System-on-Chip (SoC) devices. For our study, it was used the Zynq-7000 device, which is equipped with dual-core ARM Cortex-A9 processors integrated with 28nm Artix-7 based programmable logic. Using a homemade fault injection platform, the criticality of each available general purpose register was identified by measuring the probability of an injected fault to generate a SDC or a SEFI. A set of six benchmarks applications were selected: MxM, Advanced Encryption Standard (AES), Quicksort, Fast Fourier Transform (FFT), Fibonacci, and Joint Photographics Experts Group (JPEG).

## 1.1 Objectives and Contributions

The RISC processors, the increase in the compiler and the optimizations complexity have made it harder to evaluate the fault tolerance of the hardware and their applications. The objective of this work is to understand better how to evaluate the reliability of the hardware and the applications.

In order to achieve this objective, it was necessary to do a radiation experiment and a fault injection in the tested benchmarks. The fault injector accesses the general purpose and NEON registers in the ARM Cortex-A9 in the Zynq-7000 architecture to inject faults. Finally, the APSoC device executing the MxM and AES applications compiled with different compiler optimizations were irradiated with heavy ion particles. Therefore, an evaluation of the effects of compiler optimization in the reliability of the device can be done.

## 1.2 Organization

This dissertation is organized as follows:

- Chapter 2 Background knowledge: introduces the RISC Architecture, and the soft errors effects in embedded processors;

- Chapter 3 Code optimization effects: presents a study about why the optimizations are used, what are the optimizations, the optimization effects in the performance and energy consumption, and the state of the art of the optimization effects in the

reliability;

- Chapter 4 Case study: The embedded ARM A9: introduces the APSoCs architecture, Xilinx Zynq-7000 as an example of APSoC and the case study device, the algorithms evaluated in this work, and the setups used in the experiments;

- Chapter 5 Reliability evaluation methodology: presents the differences between the beam experiment and the fault injection, the metrics used to evaluate the reliability, and the methodology used in the heavy ion experiment and fault injection framework;

- Chapter 6 Results: presents and analyzes the results obtained in the fault injection, and in the heavy ions experiments;

- Chapter 7 Concluding remarks: presents the concluding remarks of this dissertation, such as its a discussion about the obtained results and future works;

#### 2 BACKGROUND

This chapter introduces the background knowledge for the understanding of the dissertation. It is presented the RISC architecture and the sources of radiation and its effects on circuits and embedded processors.

#### 2.1 RISC Architecture

The Instruction Set Architecture (ISA) is an abstract model of a computer that defines the external Input/Output (I/O) model, the native data types, the instruction set, the memory architecture, the addressing modes, the registers, the interrupt modes, and the exception handling. Based on architectural complexity, ISAs are commonly divided in the Complex Instruction Set Computing (CISC) and the Reduced Instruction Set Computing (RISC).

In the design of the first processors, memory was expensive and had a small capacity (DANDAMUDI, 2005). In order to develop programs which can run using these limited resources, the designers developed the CISC instruction set, which consists of a set of complex instructions so the total size of the program could be reduced and stored in the memory.

The microprogramming in the CISC architectures facilitates the cost-effective implementation of complex instructions by using microcode. The use of small and fast memories is also required to store the microcode to reduce the memory access latency on performance. Another advantage of using these complex instructions is the close in the semantics of the high-level languages and the machine languages.

One of the reasons for first develop the CISC architecture was the fact of the complex instructions were faster than an equivalent using simple instructions. However, the measure of a single instruction is not the only measure of performance. The overall system performance should be considered.

The first RISC processors were designed from IBM, Standford, and UC-Berkeley. The Stanford MIPS, IBM 801, and Berkeley RISC 1 and RISC 2 were all designed with a similar philosophy which utilizes a small, highly optimized set of instructions (ZARGHAM, 1996).

Computing devices based on RISC architecture allow only a limited set of simple two-input operations to be executed. Additionally, data to be digested by the processor

must be loaded into registers. This load of the data in the register guarantees high performance, as simple operations can be executed in few clock cycles as registers are fast. In order to achieve the best performance, data must remain in the register files until they are no longer necessary for any instruction. In fact, loading data from the main memory or even from the cache is considered a time-consuming task that should be executed only when necessary. An anticipated result of this work is that the increasing utilization of the register file increases performance and reduces the code reliability.

RISC architectures became popular thanks to the advances in compiler efficiency. Complex and efficient compilers are the key tool to take full advantage of RISC performance successfully. The compiler rearranges the source code into a sequence of simple instructions. Moreover, the compiler defines when data must be loaded into the registers from the main memory and when data from registers can be stored in the main memory. Several iterations are typically required for the compiler to produce an efficient assembly code from the high-level source code.

The RISC design implements simple instructions that can be executed in one cycle. As a consequence of it, the processor design is simplified. In this design there is no need for microcode and operations can be hardwired.

Most of the CISC instruction set supports the register-to-memory, register-to-register, and the memory-to-memory operations. The RISC architecture allows only special load and store operations to access memory and the other operations work using the register-to-register operations. This difference in the RISC simplifies the instruction set design allowing the execution of one Instruction Per Cycle (IPC). Also, simplifies the design of the control unit. Advances in Integrated Circuits (IC) technology dimensions and the operating voltages has brought an increase in the high density, a decrease in the power, and an increase in the sensitivity of the circuits to single event effects.

The usage of simple addressing modes in the RISC processors allows a fast address computation of operands. Only the load and store instructions need a memory addressing mode. The majority of the instructions use register-to-register operations. A larger register set is needed in the RISC architecture, a consequence of it is the ample opportunities of the compiler to optimize their usage and also, a decrease in the overhead associated with procedure calls and returns.

The RISC architecture uses the fixed simple length instructions which are more efficient than the variable length instructions. As mentioned before the RISC design also use a simple instruction format allowing an efficient decoding and scheduling of instruc-

tions.

The first RISC processors had fewer instructions compared to the CISC. The new RISC processors have hundreds of instructions, and some of them are complex such as used in the CISC architecture. These new ones can be called a hybrid of the CISC and RISC.

#### 2.2 Soft Errors Effects in Embedded Processors

Advances in Integrated Circuits (IC) technology dimensions and the operating voltages has brought an increase in high density, a decrease in power, and an increase in radiation sensitivity of the circuits (BAUMANN, 2005).

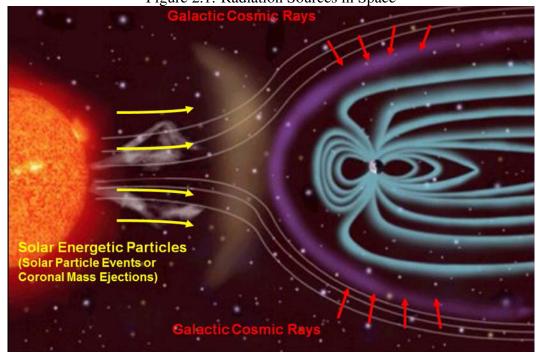

Figure 2.1: Radiation Sources in Space

Source: NASA/JPL-Caltech/SwRI

The main sources of ionizing radiation come from solar flares, solar wind and cosmic rays as showed in Figure 2.1. The Van Allen belts are a collection of charged particles, gathered in place by Earth's magnetic field and includes two electron belts and one inner proton belt. The inner belt contains electrons whose energy is less than 5MeV. The outer belt contains electrons whose energy may reach 7MeV (BOUDENOT, 2007). The belts are located in the inner region of the Earth's magnetosphere. Heavy ions may also be trapped in the magnetosphere.

Cosmic rays are high-energy particles arriving from outer space. These particles

are mainly protons, nuclei of hydrogen, nuclei of helium and heavier nuclei. When they arrive on Earth, they collide with the nuclei of atoms in the upper atmosphere producing a shower of secondary particles: x-rays, muons, protons, alpha particles, pion, electrons, and neutrons. Each kind of particle produces different effects on ICs.

Radiation Effects Total Ionization Single Event Effects (SEEs) Effects Nondestructive Destructive SEE SEE Single Event Single Event Functional Single Event Single Event Latchup (SEL) Upset (SEU) Interrupt (SEFI) Transient (SET)

Figure 2.2: Radiation effects

Source: (SIEGLE et al., 2015)

Figure 2.2 shows that the radiation effects can be divided into Total Ionization Dose (TID) Effects, and Single Event Effects (SEEs).

The TID is a cumulative effect of ionizing radiation over the exposure time. In the complementary metal oxide semiconductor transistors the exposure to high-energy ionizing radiation generates electron-hole pairs which causes a buildup of charge within the oxide. This buildup of charge will change the threshold voltage, increase the leakage current, and modify the timing of the CMOS transistor, leading to the parametric degradation and/or functional failure of the electronic device.

SEEs happens when a single ionizing particle deposits sufficient energy to disrupts the normal operation of a circuit. The SEEs can be divided in Destructive and Nondestructive. Destructive SEE is represented by Single Event Latchup (SEL), which triggers parasitic PNPN thyristor structures in a device, which can cause permanent damage or if not permanently a power cycling of the circuit is needed. Nondestructive SEE can be represented by the Single Event Upset (SEU) or Soft Error, the Single Event Functional Interrupt (SEFI), and the Single Event Transient (SET). The SEU happens when an ionizing radiation particle strikes a configuration memory cells, user memory, and regis-

ter changing the logic state of the element. The SEFI happens in complex devices like modern memories, processors, Field-programmable gate array (FPGA) or Application Specific Integrated Circuits (ASICs), and mixed-signal devices and the main effect is a component reset, lock-up, or malfunction. The SET is an electrostatic discharge caused by a single energetic particle strike whose the effect is a soft error.

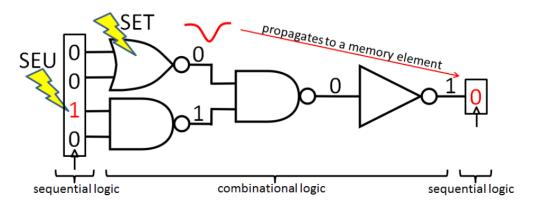

Figure 2.3: SEU and SET in circuits

Source: (CHIELLE, 2016)

In Figure 2.3 is showed an example of an SEU and a SET. A particle hits a memory element which causes an SEU and changes the stored value from 0 to 1. The SEU in the example is masked by the NAND gate because the other NAND input is 0. On the contrary, if the other NAND input is 1 the output of the NAND would be changed, and the error would propagate.

Another particle in Figure 2.3 hits a NOR gate causing a SET in which temporarily change the output from 1 to 0. The fault is not masked by any gate and propagates to the memory element. In which the wrong value can be stored if the pulse hits a memory element during a clock event.

Soft errors in embedded processors happen when a value stored in memory elements (i.e., register or data memory) is modified. This change in the memory elements values can lead to executing incorrectly an application producing a wrong output or even never finish the execution. They can affect the data-flow and the Control-flow of a running application (CHIELLE, 2016).

The data-flow errors affect the program output. When a fault affects the data-flow, the application runs normally, but the output is incorrect at the finish of the execution. The data-flow errors are usually caused by wrong operation or incorrect data.

The control-flow errors happen when the program flow is incorrectly executed.

The possible causes of this type of error is a branch creation, a branch deletion, an incorrect branch decision, an incorrect target address, or a bit flip in the Program Counter (PC) register.

#### **3 CODE OPTIMIZATION EFFECTS**

In this chapter, it will be explained the optimizations and their effects in performance, energy consumption, and reliability in the applications.

## 3.1 Why optimizations?

Since the advent of the first computer, code optimizations have been a widely used tool to perform all sort of code transformations. The objectives of the optimization depend on the constraints of the application, like time or memory requirements in real time applications in embedded systems or energy consumption in a spacial application which the power is limited.

Optimizations can be applied at different levels like design level, algorithms and data structures, source code, build, compile, and assembly. In general, the higher levels in compiler optimizations provide a greater impact but requires significant changes or even to completely rewrite the code. In some cases, the performance bottleneck is in the low level of the code, and small variations in this state have a significant impact on the program performance. In this work, a study of the effect of the global compiler optimization in the code reliability is done.

In recent years, compilers have allowed users to select different levels of optimization to be applied to the code. Optimization is achieved by modifying the number, the usage, and the reference of registers. The optimized code can hugely increase the performance of the applications but also increases the registers usage.

## 3.2 What are the optimizations?

In order to produce an optimized code, the compiler performs one or more transformation in the source code. These transformations aim at modifying the original code to a more efficient code preserving the meaning and the output of the code. The most common optimizations that compilers can perform are: the control flow analysis, the data flow analysis, the code motion, the common subexpression elimination, the constant folding, the if-conversion, the dead code elimination, the copy propagation transformations, the inlining (HAGEN, 2011).

The Data Flow analysis identifies how and when variables are used in a program and after that applies various set equations to these usage patterns to find optimization opportunities. The Code Motion is an optimization technique which reduces the number of common subexpressions relocating them to more optimal locations in an intermediate representation of the code. Loops can be optimized using this technique decreasing, for example, the number of instructions in an inner loop and increase the part of the code outside that loop. The Common Subexpression Elimination is a standard optimization mechanism, which avoids the recalculation of previously calculated values. Thus, reducing the number of instructions executed by a program to achieve the same result. The Dead Code Elimination (DCE) is the optimization technique that removes variables and statements in the code that does not do anything permanent or useful in the program. The Constant Folding technique eliminates expressions, which can be calculated when the program is compiled. The If-conversion is a technique where branch constructs are broken into separate if statements to simplify generated code and eliminate jumps and branches wherever possible. The Copy Propagation transformation is an optimization technique to reduce or eliminate redundant computations eliminating cases in which values are copied from one location or variable to another assigning their value to another variable. The Inlining is an optimization technique where code performance can improve by replacing complex constructs, and even function calls with an inline representation of the construct or function call. The Control Flow analysis examines loops and other control constructs to identify the execution paths and based on this analysis tries to make the execution path more efficient (AHO et al., 2006).

The user manual for Linaro GNU Compiler Collection (GCC) 4.9-2014 mentions that at least 160 code optimizations can be turned on or off individually. Users also can specify more than 100 different values controlling the amount of, or determine the context for, applying a particular optimization. Individually handling all these options would not be practical for regular application development. Thus, GCC provides summary optimization options named -O0, -O1, -O2, -O3, and -Os. The default level of optimization in Release mode is O2. Table 3.1 reflects the most significant optimization flags in GCC compiler that are enabled when the -O level is applied.

Higher optimization levels perform more global transformations on the program and apply more expensive analysis algorithms to generate a faster and more compact code. The price in compilation time and the resulting improvement in execution time depending on the particular application and the hardware environment.

Table 3.1: The main GCC optimizations and the levels at which they are enabled.

|                      | Included in level |    |           |    |    |

|----------------------|-------------------|----|-----------|----|----|

| Optimization         | 00                | 01 | <b>O2</b> | Os | О3 |

| defer-pop            |                   | X  | X         | X  | X  |

| tree-dce             |                   | X  | X         | X  | X  |

| cprop-registers      |                   | X  | X         | X  | X  |

| loop-optimize        |                   | X  | X         | X  | X  |

| omit-frame-pointer   |                   | X  | X         | X  | X  |

| rename-register      |                   | X  | X         | X  | X  |

| align-loops          |                   |    | X         | X  | X  |

| align-jumps          |                   |    | X         | X  | X  |

| align-labels         |                   |    | X         | X  | X  |

| align-functions      |                   |    | X         | X  | X  |

| regmove              |                   |    | X         | X  | X  |

| optmize-strlen       |                   |    | X         |    | X  |

| schedule-insns       |                   |    | X         |    | X  |

| cse-follow-jumps     |                   |    | X         | X  | X  |

| cse-skip-blocks      |                   |    | X         | X  | X  |

| peephole2            |                   |    | X         | X  | X  |

| inline-functions     |                   |    |           |    | X  |

| predictive-commoning |                   |    |           |    | X  |

| tree-partial-pre     |                   |    |           |    | X  |

Source: The Author

The GCC compiler enables a plethora of optimization to achieve better performances. Some optimizations reduce the size of the resulting machine code, while others try to create a faster code, potentially increasing its size (e.g., *loop unrolling* increases the assembly code but reduces the execution time).

O0 is the level, which GCC does not perform any optimization and compiles the source code in the most straightforward way possible. Each command in the source code is converted directly to the corresponding instructions in the executable file, without rearrangement. The compiler's goal is to reduce the cost of compilation and be able to set breakpoints, examine variables, and then continue execution.

The O1 is the first level of optimization, which the compiler tries to minimize both code size and execution time without a massive increase in the compilation time. Some optimizations are enabled at this level as shown in Table 3.1. These optimizations are described in the next paragraph.

The cprop-registers tries to reduce the number of the register copy operations.

The defer-pop accumulates function arguments on the stack. The tree-dce eliminates dead code to reduce the application size. The omit-frame-pointer avoids instructions required to set up, save, and restore frame pointers decreasing the registers usage. The loop-optimize moves constant expressions and simplifies test conditions for exit the loops in other levels of optimization this flag performs strength reduction and unrolls loops. The rename register is the GCC option that tries to use any unallocated registers to avoid false dependencies in scheduled code is frequently used on systems with a large number of registers.

The O2 level performs all O1 optimization flag and also other supported optimizations that do not involve a space-speed trade-off. Some of the main optimizations enabled in O2 level are described in the following paragraph.

The four align optimizations, which make functions, labels, jumps, and loops are aligned with the machine natural memory size boundaries avoiding no-op instructions and making the code faster. The regmove makes the GCC reassign the registers to maximize the number of registers used in the application. The optimize-strlen optimize standard C string functions using fasting alternatives. The schedule-insns reorder instructions to eliminate execution stalls when the data is unavailable.

The Os enables all O2 optimizations that do not typically increase code size. It also performs further optimizations designed to reduce code size. The Os level disables some of the O2 level optimizations like the optimize-strlen and the schedule-insns that increment the size of the final code. This level also maintains some optimizations like the cse-follow-jumps follows jumps that, which target is not unless reached. The cse-skip-blocks follows jumps that conditionally skip blocks. The peephole2 tries to replace longer set of instructions with shorter.

The O3 is the third and highest level enabled, which emphasizes speed over size. This optimization includes all optimizations enabled at O2 and some other optimizations. The inline-function integrates all functions into the routines that call them boosting performance but also can drastically increase the size of the assembly code, which can have severe effects on the code performance. Other optimizations are enabled in the O3 level like the predictive-commoning reuse memory stores and loads performed in iterations loop, and the tree-partial-pre makes an aggressive partial redundancy elimination.

Besides the level optimizations, the compiler has variously specific optimizations that can be enabled manually. Many of these optimizations involve floating point operations making significative performance improvements but changes the ISO and IEEE

specification for math functions.

It is worth noting that optimization efficiency strongly depends on the source code. Some algorithms for which the control flow is data-dependent may be hard to be optimized. In fact, the compiler can not statically predict the branches to be taken as data is not yet available. The branch prediction can not happen, for instance, in sorting algorithms which perform branch operations based on comparisons among data.

## 3.3 Optimizations effects in performance and energy consumption

One of the major effects of the compiler optimizations that affect the performance is the decrease in the memory access time. This decrease is made by eliminating redundant accesses to memory and replaces with shorter latency event like register copying and value propagation through registers. As a consequence of it, the remaining accesses in the application has a higher miss rate in the cache (DEMERTZI; ANNAVARAM; HALL, 2011).

The changes in control flow is another consequence of compiler optimizations that affect the performance. A delay in branch resolution can stall the application until the branch outcome is resolved. The branch misprediction is when a wrong branch is called, the partially processed instructions in the pipeline need to be discarded, and the pipeline has to start over at the correct branch. The optimized codes have fewer committed branches and less branch misprediction than unoptimized code. The lower number of overall branch instruction allows the processor to issue and execute long basic blocks (DEMERTZI; ANNAVARAM; HALL, 2011).

The effect of the different level of compiler optimizations in the energy consumed to execute the code is directly proportional to the number of instructions. As consequence of it, optimizations that improve performance by increasing the parallelism in the program increases the energy consumption. Optimizations that decreases the number of instructions like common sub-expression elimination, induction variable elimination and unrolling also decreases the energy consumed (VALLURI; JOHN, 2001).

The influence of the different level of compiler optimizations on power dissipation is directly proportional to the number of instructions per cycle. An example of it is the optimizations such as instruction scheduling, and loop unrolling that increase the performance but also increases the IPC has a side effect which is the increases in the power dissipation (VALLURI; JOHN, 2001).

A consequence of the compiler optimizations is the significant decrease in the number of reads and writes in the main memory with the increase of the optimization level (CHIBANI et al., 2014).

#### 3.4 State of the art

In Recent years, several studies have addressed the issue of evaluating the influence of optimizations in applications reliability.

In Sangchoolie et al. (2014) the authors evaluate the compiler optimizations injecting faults in the instruction set architecture registers and main memory locations. All the 12 benchmarks presented in the paper has an increase in the performance, but the gain varies significantly depends on the applications. The conclusion of this study is that the compiler optimization has a minor effect on the reliability of the investigated benchmark applications.

In Ferreira et al. (2013) the authors discuss how compiler optimizations influence software reliability when the applications are compiled with a technique, which detects and correct radiation control-flow errors. In order to increase the performance in the ten benchmarks selected from the Mibench embedded benchmark suite, the author uses the Compiler Optimization Level Exploration (COLE), which uses a population-based multi-objective optimization algorithm to construct a Pareto optimal set of optimizations. In the selected optimizations only 25% of the GCC optimizations appear in at most one Paretto. In this work the author implemented a software fault-injector, using GDB to perform the fault injections. The consequence of indiscriminately selecting the optimizations can decrease the software vulnerability to unacceptable levels.

In Serrano-Cases and Isaza-González (2016) the authors use the NSGA-II algorithm to choose the best optimization to reduce the code size, and execution time while improving the reliability of the final application. In the experiment, the MSP430 architecture (NAGY, 2003) has been used to inject faults in an open-sourced simulator. The method improves the fault coverage from 3% to 6% and the MWTF from 15% to 45%.

The compiler optimizations have a significant influence on the reliability of the applications. A better understanding of how to use them and how they affect the embedded processors is an essential study in the use of COTS in space applications.

#### 4 CASE STUDY: THE EMBEDDED ARM A9

This chapter introduces the All Programmable System-on-Chip (APSoC) architecture which in our case of study is the Zynq-7000. It is also presented the setups used in the fault injection and the heavy ion experiments.

## 4.1 All Programmable System-on-Chip

The Application Specific Integrated Circuits (ASIC)s, which can include digital, analog and radio-frequency components, together with mixed-signal blocks implementing Analog-to-Digital Converters (ADC) and Digital-to-Analog Converters (DAC). A System On Chip (SoC) can combine all aspects of a digital system: processing, high-speed logic, interfacing, memory, and so on. The SoC solution is lower cost, enables faster and more secure data transfers between the various system elements, has higher overall system speed, lower power consumption, smaller physical size, and better reliability. The disadvantages of ASIC-based SoCs are development time and cost, and lack of flexibility.

The Programmable System-on-Chip (PSoC) is a SoC implemented in a programmable, reconfigurable device like Field Programmable Gate Array (FPGA)s, which offers a flexible platform than ASICs for implementing SoCs. The APSoC integrates the software programmability of a processor with the hardware programmability of an FPGA (CROCK-ETT et al., 2014).

The APSoCs is formed around a Processing System (PS) and a Programmable Logic (PL). The PL section is used for high speed, arithmetic, and data flow subsystems. The PS supports operating systems and software applications. As a consequence, the system functionality can be partitioned between hardware and software.

## **4.1.1 Processing System**

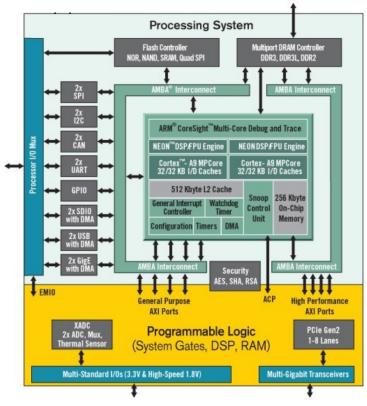

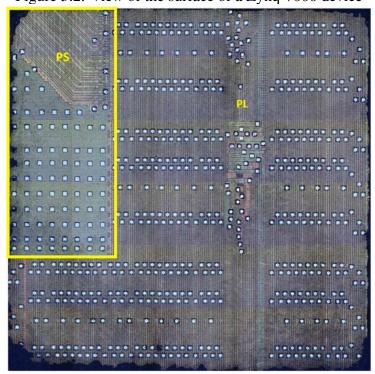

The present study is based on the COTS Zynq-7000 APSoC designed by Xilinx in Taiwan Semiconductor Manufacturing Company (TSMC) 28nm technology node. The Device Under Test (DUT), an XC7Z020-CLG484 part, is embedded in a commercially available Zed-Board Development Board. The Zynq architecture is showed in Figure 4.1.

The PS is formed around a hard-core processor the dual-core ARM Cortex-A9

Figure 4.1: An example of APSOC: the Xilinx Zynq-7000

Source: Xilinx

processor, other associated processing resources forming the Application Processing Unit (APU), and others peripheral interfaces, cache memory, memory interfaces, interconnect, and clock generation circuitry.

The APU embraces the two processors core each one with his NEON Media Processing Engine (MPE), Floating point Unit (FPU), a Memory Management Unit (MMU), and a Level 1 cache memory. The APU also has an On Chip Memory (OCM), a Level 2 cache memory, and a Snoop Control Unit (SCU).

The ARM Cortex-A9 processor is a general purpose choice for low power, cost-sensitive 32-bit devices, high-efficiency, dual-issue super scalar, out-of-order, and has a dynamic length pipeline (8 - 11 stages). The processor in Zynq-7000 operates with a clock frequency up to 667 MHz.

The ARM Cortex-A9 dual-core processor architecture has 56 physical 32-bit registers. Each core of the processor has 15 general purpose registers and one Program Counter (PC) register. Also, the processor has five banked registers, 15 banked general-purpose registers, and five status registers. In our Fault Injector, we inject faults in general purpose registers of one core using bare-metal applications, representing 25% of total registers.

input reg A input reg B operation (same for all)

Figure 4.2: Single Instruction Multiple Data processing in NEON

Source: (CROCKETT et al., 2014)

The two cores in the ARM processor has a separate Level 1 caches of 32KB for instructions and data being able to store the most used data and instructions to increase the processor performance and decrease the data access time. Additionally, the cores share a Level 2 cache of 512KB for instruction and data and also, have a 256KB OCM. The Memory Management Unit (MMU) translates the virtual address to physical addresses.

The SCU interfaces the processors and the Level 1 and 2 cache memories being responsible for maintaining memory coherency between the L1 data cache memories and the Level 2 cache memory. Additionally, manages the transactions between the PS and the PL via the Accelerator Coherency Port (ACP).

Some modern software, particularly media codecs and graphics accelerators, operate on large amounts of data that is less than word-sized. The 16-bit data is common in audio applications, and 8-bit data is standard in graphics and video. The implementation of the Advanced Single Instruction Multiple Data (SIMD) extension used in ARM processors is called NEON, and this is the standard terminology used outside architecture specifications.

The SIMD technology provides the use of a single instruction to perform the same operation in parallel on multiple data elements of the same type and size. In Figure 4.2 two registers in which each one contains a set of N individual input vector are operated using the same operation for all inputs producing a set of output vectors which are written in the output register. The NEON engine in ARMv7-A/R including ARM cortex A9 supports these data types: unsigned and signed integers, single and half precision floating point.

The NEON instructions are executed as part of the ARM or Thumb instruction

stream. The instructions provide memory accesses, data copying between NEON and general purpose registers, data type conversion, and data processing. The NEON register bank can be accessed as 64 registers in single precision or 32 registers in double precision or 16 registers in quad precision. This register bank is implemented on all current ARM Cortex-A series processors.

Developing for NEON can be done writing the code in assembly or writing the code using the intrinsics functions defined by ARM or using the compiler auto-vectorization. The intrinsics functions use the C or C++ high-level languages given direct access to NEON instructions. As a consequence, the compiler can optimize the operations for performance decreasing the work for the developer to consider the register allocation in the code. The compiler also can perform an automatic vectorization in C or C++ source code without writing assembly code or the developer using intrinsics functions. The advantage of the automatic vectorization is the fast development and the code now is portable between different tools and target platforms.

The FPU provides hardware acceleration of floating point operations following the IEEE 754 standard support single and double precision formats. Also, supports half precision and integer conversion.

The Figure 4.1 shows that the Zynq has a variety of interfaces between the PS and external components. The Multiplexed Input/Output (MIO) is the primary communication interface and provides 54 pins of flexible connectivity. A Way to extend the communication interfaces when is required it is using the Extended MIO (EMIO), which passes through and shares the I/O resources of the PL. The Available I/O peripheral interfaces are two Serial Peripheral Interface (SPI), two I2C bus, two Controller Area Network (CAN), two Universal Asynchronous Receiver Transmitter (UART), the General Purpose Input/Output (GPIO), two SD card memory, two Universal Serial Bus (USB), and two Ethernet MAC peripheral.

### 4.1.2 Programmable Logic

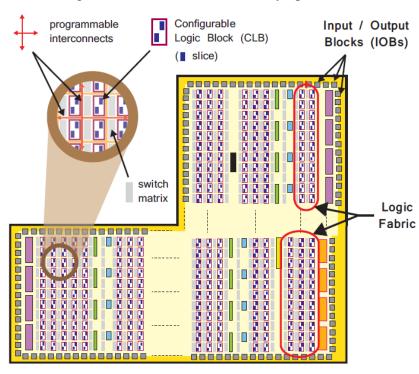

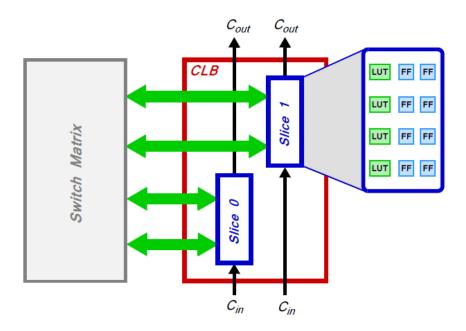

The PL is formed around an equivalent Xilinx Artix-7 FPGA logic fabric. The available resources in the logic fabric are shown in Table 4.1. The FPGA is composed of slices, Configurable Logic Blocks (CLBs), and Input/Output Blocks (IOBs) for interfacing is showed in Figure 4.3.

The CLBs are a small, regular groupings of logic elements, which are organized

Figure 4.3: The PL structure of Zynq-7000

Source:(CROCKETT et al., 2014)

Table 4.1: The Zynq Logic Fabric Resources

| Device Name                                   | Zynq-7020    |

|-----------------------------------------------|--------------|

| Xilinx 7 Series Programmable Logic Equivalent | Artix-7 FPGA |

| Programmable Logic Cells                      | 85k          |

| Look-up Tables (LUTs)                         | 53,200       |

| Flip Flops                                    | 106,400      |

| Block RAM (# 36 KB Blocks)                    | 4.9 Mb (140) |

| DSP Slices                                    | 220          |

Source: (XILINX, 2017)

in a two-dimensional array on the PL. They are connected with other resources via programmable interconnects and are positioned near a switch matrix and contains two logic slices.

Figure 4.4: The Configurable Logic Block (CLB)

Source:(CROCKETT et al., 2014)

The Figure 4.4 shows that the CLBs are composed of slices, Lookup Table (LUT), Flip Flops (FF), IOBs, and Carry Logic. The LUT is a flexible resource that can be used for implementing a small Read-Only Memory (ROM), a small Random Access Memory (RAM), a shift register, or a logic function of up to six inputs.

The Slice is a CLB sub-unit in which contain the resources for implement sequential and combinational logic circuits. They are composed of 4 Lookup Tables, 8 Flip-Flops, and other logic. The FF is a sequential circuit element with two stables states and can be used to store information. The Switch Matrix makes connections between elements within a CLB and from one CLB to other PL resources. The IOBs provides the interface between the PL logic resources and the physical device pads to the external circuit. The Carry Logic propagates the intermediate signals from the arithmetic circuits to other slices.

Two special purpose components are integrated into the logic array in a column arrangement the Block RAMs for dense memory requirements and the Digital Signal Processor (DSP) DSP48E1 slices for high-speed arithmetic. The Block RAMs can implement

RAM, ROM, and First In First Out (FIFO) buffers and supports Error Correction Coding (ECC).

The Block RAM can store up to 36Kb of information and also be configured as two independent 18Kb RAMs or one 36Kb RAM. An additional setup is the word size of the elements giving flexibility in a manner that a RAM can contain more, smaller elements or fewer, longer elements. Two or more Block RAMs can be combined to make larger capacity memories. In generally they can be clocked at the highest clock frequency by the device.

The DSP is a suited choice for a variety of applications in signal processing and other applications. The DSP uses the multiplex circuit to use the registers flexible and support dynamic alteration of the computation. Many computations can be done using one or more arithmetic operators which are selected via an OPMODE input. These inputs configure the internal multiplexers and determine the arithmetic functionality implemented. Also, the DSP is capable of doing some short SIMD processing. Another way to use the DSP is to perform logical functions like the fundamental boolean operations bit-wise, NOT, AND, OR, NAND, NOR, XOR, and XNOR. Multiple DSPs can be used in a connected way to solve complex arithmetic or to implement floating point arithmetic. The low power consumption and the high-frequency operation makes the DSP very attractive for implement arithmetic circuits.

## 4.1.3 The PS - PL Interfaces

The main link between the PS and the PL in Zynq parts are the Advanced eXtensible Interface (AXI) interconnects and interfaces. As mentioned before in subsection 4.1.2 the EMIO is also another type of connection between the PS and PL.

The AXI4 is the current version of AXI which is part of the ARM Advanced Microcontroller Bus Architecture (AMBA) 3.0 open standard. The AXI buses are very flexible and are used to connect the processor and other IP blocks in an embedded system. There are three type of buses and choose one of them depends on the desired properties of that connection. The AXI4 is used for memory-mapped links providing the highest performance and supports burst. The AXI4-Lite is also used to memory-mapped but is a simplified protocol only supporting one data transfer per connections and no burst. The AXI4-Stream is used for high-speed streaming data, supports burst transfers of unlimited size, and is suited to direct data flow between source and destination.

A set of nine interfaces with multiple channels is the primary interface between the PS and PL. An interface is a point-to-point connection used to transfer data, addresses, and handshake signals between the master and slave of the system. There are three different types of PS-PL interfaces:(1) The General Purpose AXI is a 32-bit data bus used for low and medium rate communications which have four General purpose interfaces divided in two PS and two PL masters. (2) The Accelerator Coherency Port is a single asynchronous connection between PL and the SCU with a bus width of 64 bits used to achieve coherency between the APU caches and elements in the PL. The PL is the master of the only one interface. (3) The High-Performance Ports is used to high rate communications between the PL and the memory elements in PS and includes FIFO buffers to support burst read and write behavior. The PL is master of all four interfaces.

### **4.2** Algorithms

A standardized benchmark suite for the reliability evaluation has not yet been established. However, to evaluate the reliability of the microprocessor's register file, it is required that the selected benchmarks stimulate different computational resources (QUINN et al., 2015).

The proposed software benchmark includes a collection of algorithms that are realistic software codes based on standard software benchmarks. In this work, an interruption-based fault injector and a heavy ion setup were used to evaluate the compiler optimization effects on the register file reliability in the follow applications the MxM, Advanced Encryption Standard (AES), Quicksort, Fibonacci, JPEG, and FFT.

The **MxM** is an important algorithm for several applications such as signal and control algorithm, weather forecasting, and finite element analysis (KRÜGER; WEST-ERMANN, 2003; LIEPE et al., 2010). It is memory bounded and the main operations used are the sum and multiplication. The MxM complexity to multiply two nXn matrices is  $O(n^3)$ .

The (**AES**) is a specification for the encryption of electronic data. It is a symmetric-key algorithm which means that the same key is used for encrypting and decrypting the data. The design principle of AES is based in a substitution-permutation network and has a fixed block size of 128 bits and a key size of 128, 192, or 256 bits. It is a compute-bounded application, and the main operations are bitwise. AES complexity is O(n).

The Quicksort also called partition exchange sort is an efficient algorithm that

uses a divide and conquers strategy to sort efficiently. The algorithm is a comparison sort which means that it can sort any items with a total order relation is defined. Another characteristic of the algorithm is that can be operated in-place on an array and when compared with the merge sort, and heapsort algorithms are up to three times faster than the others. It is a compute-bounded application the main operation is bitwise, and the algorithm is implemented recursively. Quicksort complexity best case performance is  $O(n \log n)$  and  $O(n^2)$  in an exceptional worst case.

The **Fibonacci** is a sequence of numbers where each subsequent number is the sum of the previous two. The Fibonacci numbers are used in various computer algorithms like the Fibonacci search technique, the Fibonacci heap data structure, and the Fibonacci cubes which are used for interconnecting parallel and distributed systems. It is a data application, the main operation is the sum, and the algorithm is implemented recursively. Fibonacci complexity is O(n).

The **JPEG** is a commonly used method of lossy compression for digital images, particularly for those images produced by digital photography. The best usage for this algorithm is for photographs and painting of realistic scenes. The JPEG has a selectable trade off between storage size and image quality. The algorithm can achieve a 10:1 compression with little loss in the quality of the image. The method for compression is based on the Discrete Cosine Transform (DCT) which converts each image from the spatial domain into the frequency domain. It is a mix of compute-bounded and memory bounded application because it uses a large amount of data. JPEG complexity is O(n).

The **FFT** is an algorithm that computes the discrete Fourier transform (DFT) of a sequence. The DFT algorithm separates a sequence of values into components of different frequencies the usage. Directly computing the Fourier transform using the FFT instead of DFT increases the performance hugely especially for long data sets. Digital signal processing, solving partial differential equations, and quick multiplication of larger integers are some of the applications where the FFT is used. It is a memory bounded application and the main operation used is bitwise. FFT complexity is O(n log n).

### 4.3 Setups

In this work to evaluate the previously described benchmarks, some metrics are used. Table 4.2 shows that the metrics are separated in performance and area. The performance metrics are the number of Instructions, the number of clock cycles, and the

execution time. The area metrics are the memory footprint and the register file usage.

$$ClockCycles = 2 \times (T_{end} - T_{start})$$

(4.1)

The clock cycle metric represents the amount of time between two pulses in an oscillator. The number of clock cycles in a bare metal environment in Zynq is calculated using the Xtime library which uses the global timer in the Zynq whose counts the number of ticks of the system. The Equation 4.1 shows how to calculate the number of the clock cycles which is done subtracting the final number ( $T_{end}$ ) by the initial number of clock cycles ( $T_{start}$ ) and the result is multiplied per two because the global timer increases every two clock cycles giving precise results.

$$ExecutionTime = \frac{(T_{end} - T_{start})}{CountsperSecond \times 10^{-6}} \quad [\mu s]$$

(4.2)

The execution time represents the time to run an application in microseconds. In the Zynq the execution time is calculated using the Equation 4.2 which is the subtraction of the final number  $(T_{end})$  by the initial number  $(T_start)$  of clock cycles. The result is divided by the number of counts per second multiplied by  $10^{-6}$  to obtain the metric in  $\mu$ s.

The Open Virtual Platform (OVP) is used to generate the dynamic disassembly of the application, which makes possible to obtain the total number of instructions.

$$RegUsage = \frac{N_{regused}}{N_{total}} \tag{4.3}$$

The register file usage is the ratio of the number of the registers used in the application divided by the number of registers in the processor core. The number of total registers considered for this calculus is the number of general purpose registers except in the MxM double whose is considered the NEON register plus the general purpose registers.

The memory footprint represents the amount of main memory used or referenced while the application is running. The main memory considered here is the code segment, data segment, heap memory, call stack, and any memory used to store additional data structures such as symbol tables, debugging data structures, and others.

The benchmarks used to evaluate the general purpose registers in this work are MxM, Quicksort, AES, Fibonacci, JPEG, and FFT. Each tested setup uses the O0, O2 and O3 compiler optimizations as shown in Table 4.2.

The first columns of Table 4.2 list, for each selected code, the performance and area usage of each of the three compiler optimizations considered. In most of the cases,

Table 4.2: Compiler Optimization effects on code execution, resources utilization

|            |      | Performance Info |                |                       | Area Usage     |                 |  |

|------------|------|------------------|----------------|-----------------------|----------------|-----------------|--|

| App.       | Opt. | # Inst.          | # Clock Cycles | Exec. Time (µs)       | Mem. Footprint | Reg. File Usage |  |

|            | O0   | 271473           | 40606          | $1.22 \times 10^{-4}$ | 94768          | 0.38            |  |

| MxM        | O2   | 73988            | 8010           | $2.40\times10^{-5}$   | 94332          | 0.85            |  |

|            | O3   | 73515            | 7550           | $2.26 \times 10^{-5}$ | 94948          | 0.85            |  |

|            | O0   | 97782            | 17958          | $5.39 \times 10^{-5}$ | 110080         | 0.38            |  |

| AES        | O2   | 33066            | 4402           | $1.32\times10^{-5}$   | 97972          | 0.31            |  |

|            | O3   | 31757            | 3823           | $1.15\times10^{-5}$   | 101056         | 0.38            |  |

|            | O0   | 330946           | 107882         | $1.62 \times 10^{-4}$ | 48504          | 0.31            |  |

| QuickSort  | O2   | 148302           | 38104          | $5.72\times10^{-5}$   | 48164          | 0.92            |  |

|            | O3   | 166582           | 40264          | $6.05 \times 10^{-5}$ | 50492          | 0.85            |  |

|            | O0   | 78931            | 14496          | $4.35 \times 10^{-4}$ | 94040          | 0.38            |  |

| FFT        | O2   | 46928            | 6782           | $2.03\times10^{-5}$   | 92604          | 1.00            |  |

|            | O3   | 46870            | 6738           | $2.02\times10^{-5}$   | 92668          | 1.00            |  |

|            | O0   | 10577461         | 1131645        | $3.40 \times 10^{-3}$ | 46516          | 0.31            |  |

| Fibonacci  | O2   | 4806704          | 705765         | $2.12\times10^{-3}$   | 46348          | 0.62            |  |

|            | O3   | 4217336          | 433657         | $1.30\times10^{-3}$   | 47352          | 0.85            |  |

|            | O0   | 5008939          | 724533         | $2.17 \times 10^{-3}$ | 112432         | 1.00            |  |

| JPEG       | O2   | 2687238          | 251634         | $7.56\times10^{-2}$   | 107764         | 1.00            |  |

|            | O3   | 2452638          | 229917         | $6.90 \times 10^{-2}$ | 121692         | 1.00            |  |

| MxM Double | О3   | 362370           | 54202          | $8.13 \times 10^{-5}$ | 46956          | 0.15            |  |

|            | O3+  | 336282           | 50300          | $7.56\times10^{-5}$   | 46956          | 0.70            |  |

Source: The Author

the execution time is improved when compiler optimizations are applied. In the best case (i.e., MxM from 00 to 02), optimization can reduce  $5\times$  the execution time. However, optimizations are not always beneficial. In fact, 03 only slightly impacts the execution time of most of the codes. Quicksort shows a very peculiar behavior, as the 03 optimization appears to be less efficient than 02. This less efficiency in the O3 optimization is not surprising, as Quicksort has a data-dependent control flow. Hence, the compiler cannot predict statically how the code will behave when executed.

In the MxM setup, the inputs used were 20x20 matrices, and the data type was an integer. A decrease of 80.72% in the number of clock cycles was observed from O0 to O2 optimization, the register file usage was increased, and the memory footprint usage was decreased from O0 to O2 optimization. Additionally, it was observed a decrease of 81.41% in the number of clock cycles from O0 to O3 optimization, the register file usage stills the same of the O2 optimization, and the memory footprint was increased above the value in the O0 optimization.

In the AES Setup uses a 128 bits block size and 16 inputs the data type is an integer. It was observed a decrease of 75.49% in the number of clock cycles and a decrease in the register file usage and the memory footprint from O0 to O2 optimizations. Additionally,

there was a decrease of 78.72% in the number of clock cycles from O0 to O3. The register file usage decreases from O0 to O2 and increases in the O3 optimization for the same of O0. The memory footprint increases from O2 to O3 optimization but is lower than the O0 optimization.

In the Quicksort setup, a vector of 400 values was used as input, and the data types were integers values. It was observed a decrease of 64.68% in the number of clock cycles from O0 to O2 optimization, the register file was increased to almost the maximum, and the memory footprint was decreased from O0 to O2 optimization. Additionally, there was a decrease of 62.68% in the number of clock cycles from O0 to O3 which is worst than O2 optimization. The register file usage was decreased from O2 to O3 optimization. The memory footprint was increased in O3 optimization above the memory footprint of O0 optimization.

In the FFT setup, a sequence of a 512 float vector was used as input. It was observed a decrease of 53.22% in the number of clock cycles from O0 to O2 optimization, the usage of the register file was increased to the maximum, and the memory footprint was decreased from O0 to O2 optimization. Additionally, there was a decrease of 53.52% in the number of clock cycles from O0 to O3, the register file usage stills the same of the O2 optimization, and the memory footprint has an insignificant increase.

In The Fibonacci setup calculates the sequence up to the twenty-fifth number and uses the integer data type. It was observed a decrease of 37.64% in the number of clock cycles from O0 to O2 optimization, the register file usage doubles, and the memory footprint was decreased. Additionally, there was a decrease of 61.68% in the number of clock cycles from O0 to O3 optimization, an increase in the register file usage above the O2 optimization, and an increase in memory footprint.

In the JPEG setup, it was used an image with 5207 pixels as input and uses the integer as the data type. It was a decrease 65.27% in the number of clock cycles from O0 to O2 optimization, the register file usage is the maximum in all optimizations, and the memory footprint decreases from O0 to O2. Additionally, there was a decrease of 68.27% in the number of clock cycles from O0 to O3 optimization, and the memory footprint was increased above the O0 optimization.

In order to evaluate the NEON register and the general-purpose registers together, it was used the MxM matrix application with a 10x10 size matrices as input and the data type used was the double. The setup was evaluated using the O3 compiler optimization, and the O3+, which is the O3 compiler optimizations plus the manual optimization option

unroll all loops. This option decreases 7.55% the number of clock cycles and the register usage increases as shown in Table 4.2 in MxM Double section. The register file usage increases specifically in NEON registers and the memory footprint stills the same.

The memory footprint, which refers to the amount of main memory that a program requires or references, is barely affected by optimizations meaning that the main modifications induced by compiler optimization regard registers and not main memory accesses.