## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

## ANTONIO FELIPE COSTA DE ALMEIDA

# Investigating Techniques to Reduce Soft Error Rate under Single-Event-induced Charge Sharing

Thesis presented in partial fulfillment of the requirements for the degree of Master of Microelectronics.

Advisor: Prof. Dr. Fernanda Lima Kastensmidt

## CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Almeida, Antonio Felipe Costa de

Investigating Techniques to Reduce Soft Error Rate under Charge Sharing / Felipe Almeida. – Porto Alegre: PGMICRO da UFRGS, 2014.

84 f.:il.

Advisor: Fernanda Lima Kastensmidt.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação. Porto Alegre, BR – RS, 2013.

1. Fault Tolerance Techniques. 2. Placement Constraints Methodology. 3. Multiple Faults Scenario. I. Kastensmidt, Fernanda Lima. II. Investigating Techniques to Reduce Soft Error Rate under Single-Event-induced Charge Sharing.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento

Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb

Coordenador do PPGC: Prof. Gilson Inácio Wirth

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **AGRADECIMENTOS**

E é dada como terminada mais uma etapa da minha vida. Demorou, mas consegui concluir, mesmo com toda a correria de tentar fazer um mestrado e trabalhar ao mesmo. Guardo boas lembranças desse período aqui, foram vários artigos aceitos, bons congressos, sem contar com as companhias para as viagens. Só tenho a agradecer a todos que me ajudaram e fizeram parte desta dissertação.

Primeiramente, queria agradecer a minha família, pois sem o suporte deles, amor e coragem não teria chegado aqui. A minha mãe, Zefinha, meu pai, Jaime e minha irmã, Fernanda. Essa educação que recebi em casa, a faculdade e ninguém poderia ter me dado melhor. Aos que ajudaram nesse processo de formação e ainda guardo seus ensinamentos, como: Irene, minha tia, Ivanilda, tia postiça, Gilva, professora e Adessandro, técnico de natação.

Aos amigos da UFRGS que estiveram comigo nas disciplinas, tirando dúvidas no laboratório e na loucura de conseguir terminar os artigos no prazo. São eles: Samuel, Eduardo Souza, Eduardo Chielli, Lucas, Anelise, Carol, Gracieli, José Rodrigo, Jimmy, Jorge e William.

A orientadora e amiga, Fernanda. Essa merece mais do que estar nos agradecimentos. Ela foi responsável por toda a concretização dos artigos aceitos em congressos e revistas. Bem como, me guiou na escolha do tema, direcionou a pesquisa e ajudou na escrita deste e outros textos. Primeira etapa concluída, agora vamos para o doutorado, que já foi iniciado e pelo menos mais 3 anos de parceria, muito obrigado por tudo.

Acredito que não se consiga fazer nada, por mais conhecimento que se tenha, se não existe o apoio dos amigos que me acompanham até hoje. Não são muitos, mas os que ficaram ao meu lado são os melhores do mundo. Quero agradecer em especial aos meus amigos de Belo Horizonte, representado aqui pelo Carlos Junior e Diego Magela, aos amigos de São Paulo, por Daniel Vita e ao pessoal do vôlei, pela Meus SAIS. Os amigos de infância que fazem tanta falta Ludmilla e Michelle, bem como o pessoal da 8º série, represetando por Handricka. Os de Porto Alegre, os quais já chamo de família: Wendyel, Guile, Luis, Tanira, Paula e Regina (Bah).

Muitos outros me deram forças em determinadas fases da minha vida, fica aqui meu agradecimento por todos esses que tiveram um papel importante por um determinado tempo. Cada um ajudou e contribuiu da sua forma. Muito obrigado!

"I want to say I live each day, until I die And all that I had something in, somebody's life The hearts I had touched will be the proof that I leave That I made a difference and this world will see"

#### **ABSTRACT**

The interaction of radiation with integrated circuits can provoke transient faults due to the deposit of charge in sensitive nodes of transistors. Because of the decrease the size in the process technology, charge sharing between transistors placed close to each other has been more and more observed. This phenomenon can lead to multiple transient faults. Therefore, it is important to analyze the effect of multiple transient faults in integrated circuits and investigate mitigation techniques able to cope with multiple faults.

This work investigates the effect known as single-event-induced charge sharing in integrated circuits. Two main techniques are analyzed to cope with this effect. First, a placement constraint methodology is proposed. This technique uses placement constraints in standard cell based circuits. The objective is to achieve a layout for which the Soft-Error Rate (SER) due charge shared at adjacent cell is reduced. A set of fault injection was performed and the results show that the SER can be minimized due to single-event-induced charge sharing in according to the layout structure. Results show that by using placement constraint, it is possible to reduce the error rate from 12.85% to 10.63% due double faults.

Second, Triple Modular Redundancy (TMR) schemes with different levels of granularities limited by majority voters are analyzed under multiple faults. The TMR versions are implemented using a standard design flow based on a traditional commercial standard cell library. An extensive fault injection campaign is then performed in order to verify the softerror rate due to single-event-induced charge sharing in multiple nodes. Results show that the proposed methodology becomes crucial to find the best trade-off in area, performance and soft-error rate when TMR designs are considered under multiple upsets. Results have been evaluated in a case-study circuit Advanced Encryption Standard (AES), synthesized to 90nm Application Specific Integrated Circuit (ASIC) library, and they show that combining the two techniques, the error rate resulted from multiple faults can be minimized or masked.

By using TMR with different granularities and placement constraint methodology, it is possible to reduce the error rate from 11.06% to 0.00% for double faults. A detailed study of triple, four and five multiple faults combining both techniques are also described.

We also tested the TMR with different granularities in SRAM-based FPGA platform. Results show that the versions with a fine grain scheme (FGTMR) were more effectiveness in masking multiple faults, similarly to results observed in the ASICs.

In summary, the main contribution of this master thesis is the investigation of charge sharing effects in ASICs and the use of a combination of techniques based on TMR redundancy and placement to improve the tolerance under multiple faults.

Keywords — Fault tolerance, Triple Modular Redundancy, Single-Event-Induced Charge Sharing, Placement Constraining

## INVESTIGANDO TÉCNICAS PARA REDUZIR A TAXA DE ERRO DE SOFT SOB EVENTO ÚNICO INDUZIDO DE CARGA COMPARTILHADA

#### **RESUMO**

A interação da radiação com circuitos integrados pode provocar falhas transitórias devido ao deposito de cargas em nós sensíveis de transistores. Por causa da diminuição das dimensões no processo tecnológico, cargas compartilhadas entre trasistores posicionados próximos uns dos outros tem sido cada vez mais observadas. Este fenômeno pode causar múltiplas falhas transientes. Por isso, é importante analisar o efeito de múltiplas falhas transitórias em circuitos integrados e investigar técnicas de mitigação.

Este trabalho investiga o efeito conhecido como evento único induzido de carga compartilhada em circuitos integrados. Duas técnicas são analisadas para lidar com este efeito. Primeiro, uma técnica que utiliza restrições de posicionamento em circuitos baseados em células padrões é proposta. O objetivo é conseguir um leiaute para que a taxa de erro de soft (SER), devido ao compartilhamento de cargas em células adjacentes, seja reduzida. Um conjunto de injeção de falhas foi realizado e os resultados mostram que o SER pode ser minimizado com o leiaute devido ao evento único induzido de carga compartilhada. Resultados mostraram que pelo uso de restrições de posicionamento é possível reduzir a taxa de erro de 12,85% para 10,63% devido a falhas duplas.

Em segundo lugar, esquemas de redundância modular tripla (TMR) com diferentes níveis de granularidade limitados pelos votadores são analisados sob múltiplas falhas. As versões de TMR são implementadas usando um fluxo de projeto padrão com base em uma biblioteca de células padrão comercial e tradicional. Uma ampla campanha de injeção de falhas é então realizada, a fim de verificar a taxa de erro de soft devido ao evento único induzido de carga compartilhada em vários nós. Os resultados mostram que a metodologia proposta é crucial para encontrar o melhor custo-benefício entre área, desempenho e a taxa de erro de software ao considerar projetos de TMR sob múltiplas falhas. Resultados tem sido avaliados em um circuito de estudo de caso do Padrão Avançado de Criptografia, sintetizado para uma biblioteca de aplicação específica de circuitos integrados de 90nm e eles mostraram que a combinação das duas técnicas, a taxa de erro resultante de múltiplas falhas pode ser minimizado ou mascarado.

Por usar TMR com diferentes granularidades e metodologia de restrição de posicionamento é possível reduzir a taxa de erro de 11,06% para 0,00% para falhas duplas. Um estudo detalhado de múltiplas falhas: triplas, quádruplas e quíntuplas combinando ambas as técnicas também são descritas.

Nós também testamos o TMR com diferentes granularidades em plataformas de FPGA baseadas em SRAM. Os resultados mostram que a versão com um esquema de granularização fina (FGTMR) foi mais eficaz no mascaramento de múltiplas falhas, que são similares nos resultados observados em ASICs.

Em resumo, a principal contribuição desta dissertação é a investigação dos efeitos de cargas compartilhadas em ASICs e o uso da combinação das técnicas baseada em redundância de TMR e posicionamento para melhorar a tolerância sob múltiplas falhas.

Palavras-Chave — Tolerância a falhas, Redundância Modular, Evento Único Induzido de Carga Compartilhada, Restrição de Posicionamento

### LIST OF ABBREVIATION AND ACRONYMS

AES Advanced Encryption Standard

AMUSE Autonomous Multilevel Emulation-Based for Soft Error Evaluation

ASCII American Standard Code for Information Interchange

ASIC Application Specific Integrated Circuit

CAD Computer Aided Design

CGTMR Coarse Grain Triple Modular Redundancy

CMOS Complementary Metal-Oxide-Semiconductor

COTS Commercial Off-The-Shelf

CPU Central Processing Unit

CTS Clock Tree Constraint

DDR Design Diverse Redundancy

DEF Design Exchange Format

DRAM Dynamic Random Access Memory

DTMR Diverse Triple Modular Redundancy

ESF Error Status Flag

FGTMR Fine Grain Triple Modular Redundancy

FIT Failures in Time

FPGA Field-Programmable Gate Array

FSM Finite State Machine

HDL Hardware Description Language

IC Integrated Circuit

IMEC Interuniversity Microelectronics Centre

LANL Los Alamos National Laboratory's

LANSCE Los Alamos National Neutron Sience Center

LEF Library Exchange Format

LET Linear Energy Transfer

LETth LET Threshold

MET Multiple Event Transient

MEU Multiple Bit Upset

MOS Metal-Oxide-Semiconductor

MSET Multiple Single Event Transient

MV Majority Voter

SEE Single-Event Effect

NASA National Aeronautic and Space Administration

NMF Non-Masked Fault

NMR N-Modular Redundancy

RAD Radiation Absorbed Dose

RISC Reduced Instruction Set Computing

SAv Self-Adapted Voter

SDC Synopsys Design Constraint

SEB Single Event Burnout

SEGR Single Event Gate Rupture

SEL Single Event Latch up

SER Soft-Error Rate

SET Single Event Transient

SEU Single Event Upset

SI International System of Units

SI Signal Integrity

SPEF Standard Parasitic Exchange Format

SRAM Static Random Access Memory

STA Static Timing Analysis

TID Total Ionization Dose

TRM Triple Modular Redundancy

VHDL Very High Speed Integrated Circuit Hardware Description Language

VHSIC Very High Speed Integrated Circuit

## **LIST OF FIGURES**

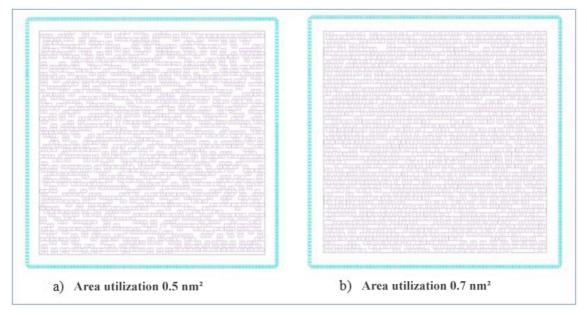

| Fig. 1 Standard cell placement showing the area utilization of the same circuit            | 14   |

|--------------------------------------------------------------------------------------------|------|

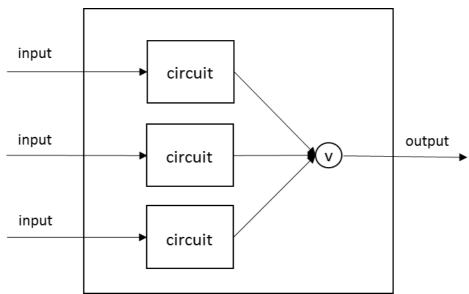

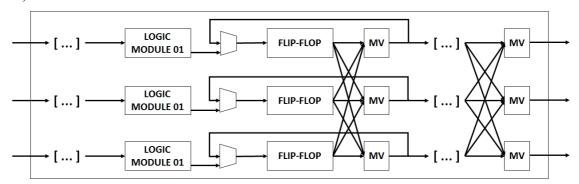

| Fig. 2 Circuit protect by CGTMR                                                            | 15   |

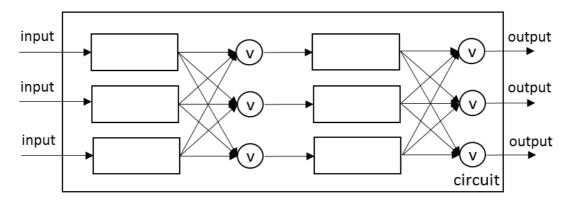

| Fig. 3 Circuit protect by FGTMR                                                            | 15   |

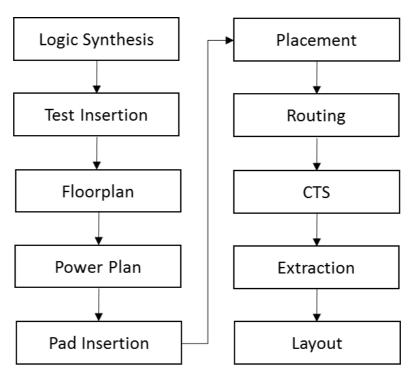

| Fig. 4 Generic ASIC flow                                                                   | 17   |

| Fig. 5 Example of SEU and SET                                                              | 21   |

| Fig. 6 Single Event Transient in transistor                                                | 23   |

| Fig. 7 Example of logical masking                                                          | 23   |

| Fig. 8 Example of electrical masking                                                       | 24   |

| Fig. 9 Example of latch window masking                                                     | 24   |

| Fig. 10 Example SEU                                                                        | 24   |

| Fig. 11 Hit memory cell                                                                    | 25   |

| Fig. 12 DICE memory cell                                                                   | 26   |

| Fig. 13 One particle, multiple effects (ROSSI, 2005)                                       | 26   |

| Fig. 14 Single-event-induced Charge Sharing                                                | 28   |

| Fig. 15 Multiple fault propagation: a) Independent propagation paths b) Convergent         |      |

| propagation paths                                                                          | 30   |

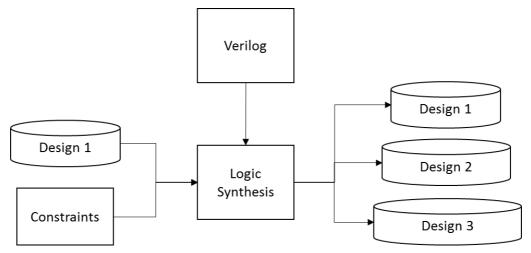

| Fig. 16 Pulse quenching effect and Multiple SET pulse (YANKANG, 2013)                      | 31   |

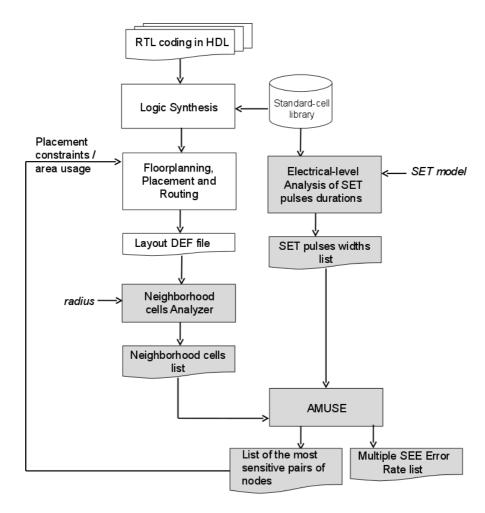

| Fig. 17 Design Flow                                                                        | 34   |

| Fig. 18 Logic synthesis flow                                                               | 35   |

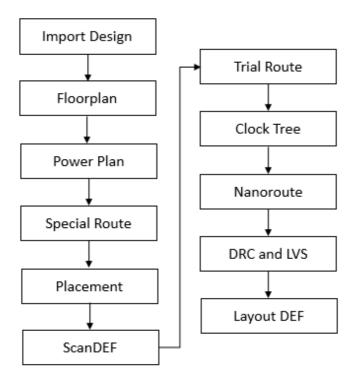

| Fig. 19 Physical Synthesis Flow                                                            | 36   |

| Fig. 20 The proposed methodology to reduce SER in multiple faults using placement          |      |

| constraints                                                                                | 39   |

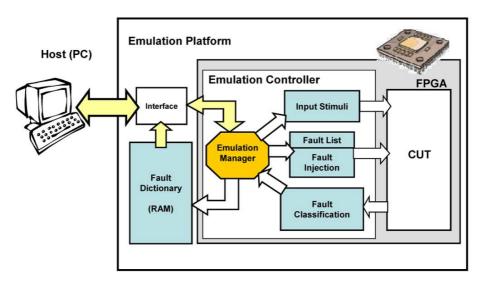

| Fig. 21 AMUSE block diagram                                                                | 40   |

| Fig. 22 AES Core block diagram                                                             | 42   |

| Fig. 23 Standard cell placement and selected pairs of nodes considering a certain radius   |      |

| distance                                                                                   | 48   |

| Fig. 24 Negative and positive charge sharing effects with respect to a single node         | 49   |

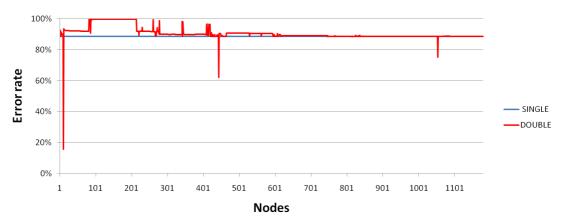

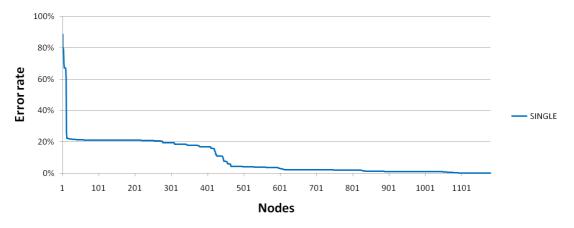

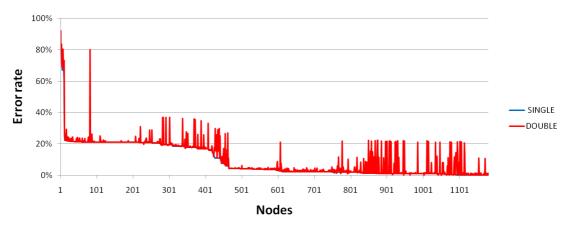

| Fig. 25 SER due to single-fault effects in each single node                                | 50   |

| Fig. 26 SER due to double-fault effects in each single node, considering the adjacent node | s in |

| the unconstrained placement                                                                | 51   |

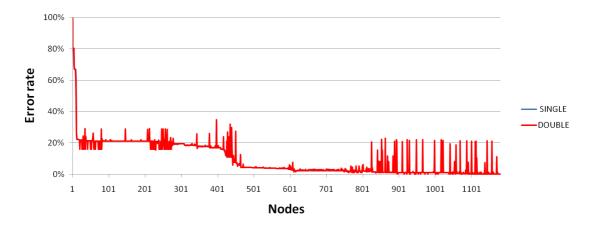

| Fig. 27 SER due to double-fault effects in each single node, considering the adjacent node | s in |

| the constrained placement                                                                  | 51   |

| Fig. 28 Theoretical optimal placement comparison                                            | 52  |

|---------------------------------------------------------------------------------------------|-----|

| Fig. 29 Example of a TMR scheme with majority voters                                        | 55  |

| Fig. 30 Example of a XTMR scheme                                                            | 55  |

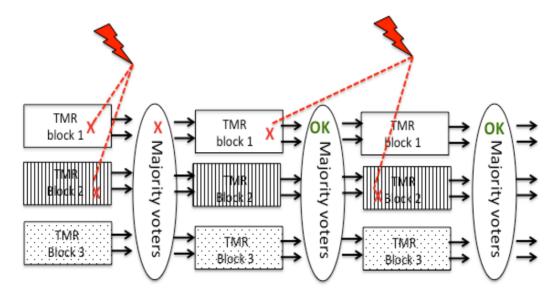

| Fig. 31 TMR block partitions with multiple faults in different partitions (ALMEIDA, 2012)   | )56 |

| Fig. 31 TMR block partitions with multiple faults in different partitions (ALMEIDA,         |     |

| 2012)                                                                                       | 57  |

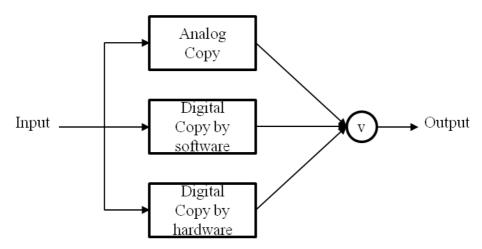

| Fig. 32 Example of the DTMR scheme (BORGES, 2010)                                           | 58  |

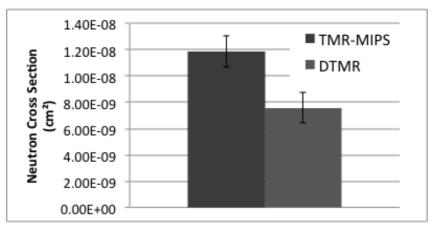

| Fig. 33 Neutron cross section of DTMR scheme and Traditional TMR-MIPS                       | 58  |

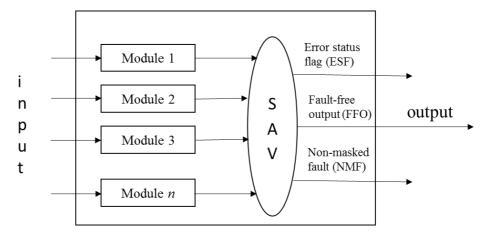

| Fig. 34 NMR-based technique for avoid multiple faults (TARRILLO, 2014)                      | 59  |

| Fig. 35 Neutron Cross-section for nMR for 37 (TARRILLO, 2014)                               | 59  |

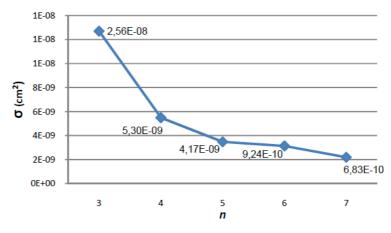

| Fig. 36 AES circuits protected by TMR with large granularity (AES_v1)                       | 61  |

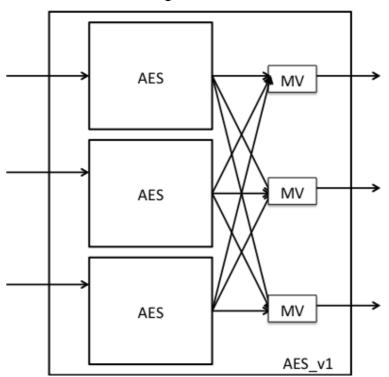

| Fig. 37 AES circuits protected by TMR with small granularity (AES_v2) (ALMEIDA,             |     |

| 2012)                                                                                       | 62  |

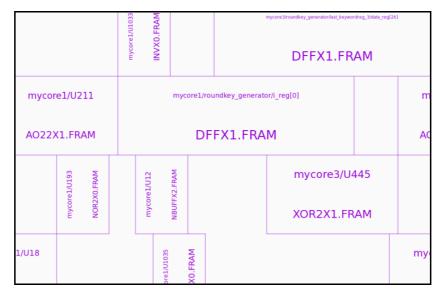

| Fig. 38 Standard cell placement in AES_v1 showing the interface between redundant block     | ς 1 |

| (mycore1) and redundant block 3 (mycore3) (ALMEIDA, 2012)                                   | 64  |

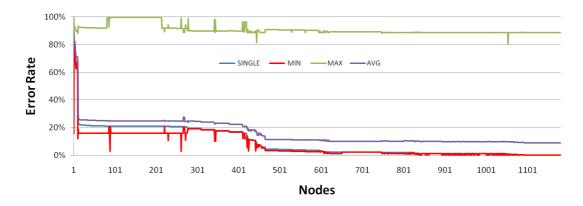

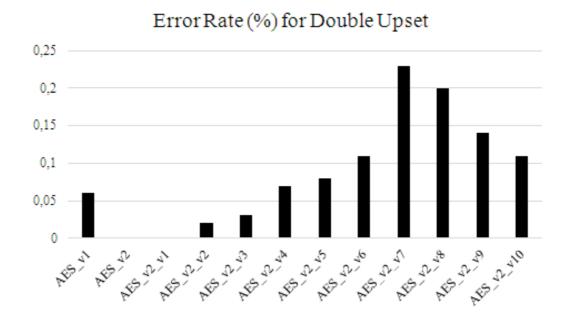

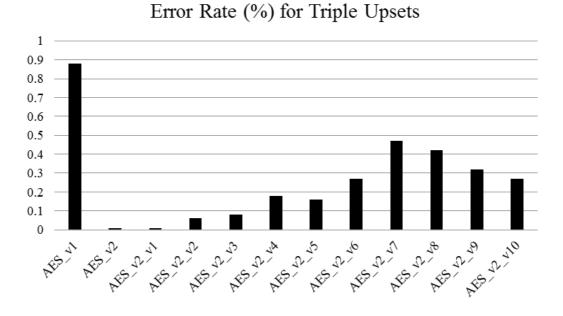

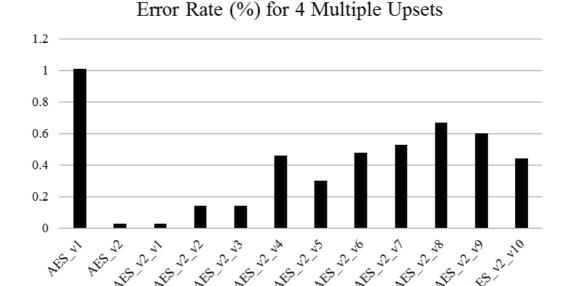

| Fig. 39 Error rate for double faults in TMR designs with different granularities            | 68  |

| Fig. 40 Error rate for triple faults in TMR designs with different granularities            | 68  |

| Fig. 41 Error rate for 4 multiple faults in TMR designs with different granularities        | 69  |

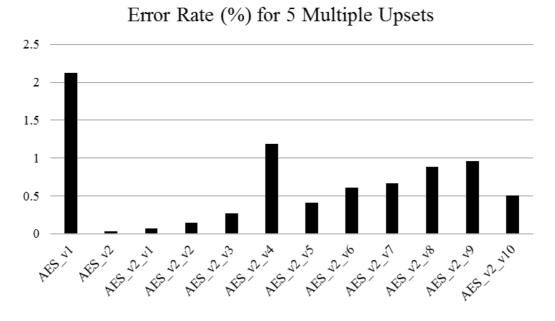

| Fig. 42 Error rate for 5 multiple faults in TMR designs with different granularities        | 69  |

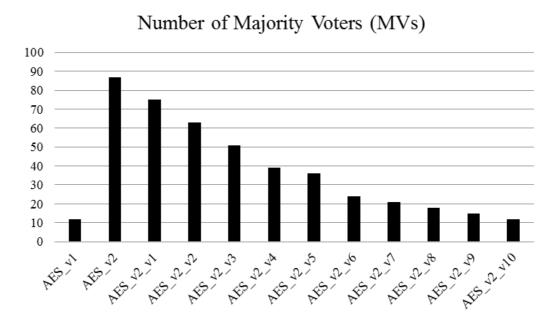

| Fig. 43 Number of Majority Voters (MVs) in TMR designs with different granularities         | 70  |

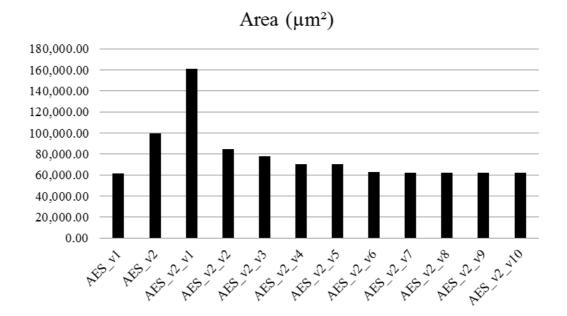

| Fig. 44 Area in TMR designs with different granularities                                    | 71  |

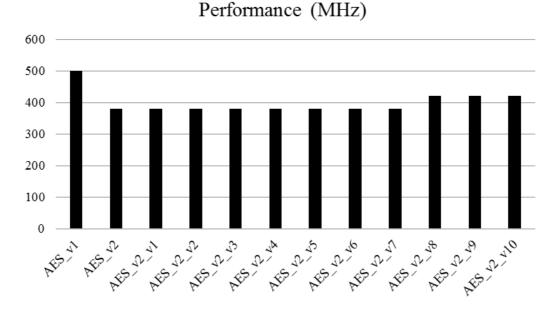

| Fig. 45 Performance in TMR designs with different granularities                             | 71  |

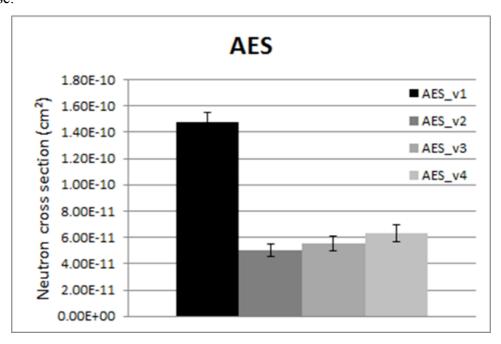

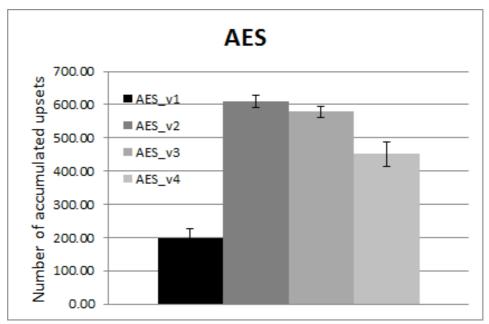

| Fig. 46 AES circuits protected by TMR with large granularity (AES_v1)                       | 74  |

| Fig. 47 AES circuits protected by TMR with small granularity (AES_v2)                       | 75  |

| Fig. 48 Calculated dynamic cross sections for each version of the AES case study during the | ne  |

| neutron experiment                                                                          | 76  |

| Fig. 49 SEU accumulated effects observed in the configuration memory bits of the AES ca     | se  |

| study during the neutron experiment                                                         | 77  |

|                                                                                             |     |

## LIST OF TABLES

| Tab. I Details of the synthesized hardware                                                | 42   |

|-------------------------------------------------------------------------------------------|------|

| Tab. II Fault injection results                                                           | 44   |

| Tab. III Increase in execution time due to additional constraining                        | 47   |

| Tab. IV SER for Single and Double faults for different placements                         | 50   |

| Tab. V Different AES circuits with the correspondent removed MV                           | 62   |

| Tab. VI Area and Performance of the TMR AES with different granularities and MVs          | 63   |

| Tab. VII Error Rate for single and double faults in standard and TMR designs with large a | and  |

| small granularities                                                                       | 65   |

| Tab. VIII Error Rate for Single, Double, Triple and Multiple 4. 5 and 6 faults in TMR des | igns |

| with Different granularities under millions of faults for each type of upset              | 65   |

| Tab. IX Different AES circuit with the correspondent removed MVs                          | 75   |

| Tab. X FPGA resources occupation and performance of the TMR-AES schemes                   | 76   |

| Tab. XI Obtained dynamic cross sections and FITs for the different AES designs            | 77   |

## **CONTENTS**

| 1 INTRODUCTION                                  | 13                               |

|-------------------------------------------------|----------------------------------|

| 2 MULTIPLE TRANSIENT FAULTS SCENA               | RIOS20                           |

| 2.1 Types of Radiation Faults                   | 20                               |

| 2.1.1 Single-Event Transient                    | 22                               |

| 2.1.2 Single-Event Upset                        | 24                               |

| 2.2 Multiple Faults                             | 26                               |

| 2.2.1 Single-Event-Induced Charge Sharing       | 27                               |

| 2.2.2 Pulse Quenching                           | 29                               |

| 2.3 Multiple Faults Scenario focused on this wo |                                  |

| 3 PROPOSED ASIC DESIGN FLOW AIMING              | G EVALUATING ASICS UNDER         |

| MULTIPLE FAULTS SCENARIOS                       | 33                               |

| 3.1 Basic Design Flow                           | 34                               |

| 3.2 Analyzing Sensitive Multiple Fault Nodes    | 38                               |

| 3.3 Case Study                                  | 42                               |

| 3.4 Fault injection Results                     | 43                               |

| 4 REDUCING SER DUE TO CHARGE SHAR               | ING BY USING PLACEMENT           |

| CONSTRAINT FOR ASICS                            | 45                               |

| 4.1 Placement Constraints Methodology           | 46                               |

| 4.2 Fault Injection Results                     | 50                               |

| 5 TECHNIQUES BASED ON MODULAR RE                | DUNDANCY TO COPE WITH CHARGE     |

| SHARING                                         | 54                               |

| 5.1 Limitations of TMR                          | 56                               |

| 6 EXPLORING DIFFERENT GRANULARITI               | IES OF FINE GRAIN TMR (FGTMR) TO |

| COPE MULTIPLE FAULTS IN ASICS                   | 61                               |

| 6.1 TMR Case Study Circuits                     | 61                               |

| 6.2 Fault Injection Results                     | 64                               |

| 7 EXPLORING DIFFERENT GRANULARITI               | IES OF FINE GRAIN TMR (FGTMR) TO |

| COPE WITH MULTIPLE FAULTS INS SRAM              | M-BASED FPGAS72                  |

| 8 CONCLUSION                                    | 79                               |

| REFERENCES                                      | 81                               |

| PUBLICATIONS                                    | FRRORI ROOKMARK NOT DEFINED      |

#### 1 INTRODUCTION

Some radiation effects on semiconductor devices have increased substantially with the decreasing of transistor size and the increasing amount of components for a given circuit area. Nowadays, it is possible to find integrated circuits fabricated in reduced dimensions such as 22 nanometers CMOS process technique operating in aerospace environments (BOHR, 2011). In this context, one of the most critical challenges in design is the amount of faults caused by cosmic ray particles. The radiation effects must be considered at the design phase to guarantee the high-reliability and safety requirements of such project (VELAZCO, 2007). Hence, it is necessary to implement techniques to avoid any interference that may cause malfunction on the system.

Integrated circuits operating in radiation environment and on Earth are susceptible to transient upsets caused by energetic particles. An upset can happen in a specific point, being called single fault, or in more than one point, called multiple faults. According to the amount of charge deposited by the energetic particle colliding with the silicon, transient pulse can have different shapes. Not all transient faults are going to provoke an error in the circuit. An error is any deviation from the expected behavior of a circuit or system. Transient upsets or faults may occur in memory elements or they may propagate through the combinational logic and if not masked by the logic or the application, these transient faults may lead to errors in the circuit.

Many of the multiple faults are due to single-induced charge sharing upsets, which means that a single energetic particle has deposited enough energy to perturb multiple transistors placed close to each other. This phenomenon is one of the most common causes of multiple upsets in nanometer technology (AMUSAN, 2006). Consequently, one of the main goals of this work is to investigate and develop a methodology to characterize integrated circuits under multiple faults by determining the most sensitive nodes and gates for fault mitigation.

In order to characterize circuits under single-induced charge sharing upsets it is mandatory to know the placement of the logic gates and transistors, because the multiple faults must be injected in transistors that are placed close to each other in the real circuit. Therefore, we have used and improved a tool, called Autonomous Multilevel Emulation-Based for Soft Error Evaluation (AMUSE) (ENTRENA, 2009). It was developed by Universidad Carlos III del Madrid (UC3M) under the guidance of the Dr. Luis Entrena. The tool is used to perform multiple fault injection and evaluate the Soft Error Rate (SER).

Once the susceptibility of a circuit under multiple faults is analyzed, some mitigation techniques can be investigated, verified and improved. A mitigation technique, which can be used to reduce charge sharing, is the placement constraint methodology (ENTRENA, 2012). Placing logic gates far away from each other, in order to reduce the error rate. This technique is based on the charge-sharing characteristics of the circuit layout.

The design flow can also be changed to introduce fault tolerance techniques that decrease the number of multiple faults. One modification is applied during the floorplan phase; it changes the utilization area, then it increases the layout space between cells as can be seen in figure 1. However, this approach has drawbacks: increase of area, routing, and circuit performance.

Fig. 1 Standard cell placement showing the area utilization of the same circuit

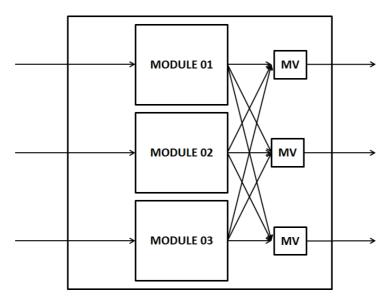

Based on redundancy, Triple Modular Redundancy (TMR) is used to mitigate single fault or error in integrated circuits. TMR is one of the most widely technique used; it has been proposed by Von Neumann (NEUMANN, 1956), which is a well know fault tolerance technique for coping with errors in integrated circuits. Normally, TMR schemes use three identical logic blocks. Each one performs the same task in tandem with the corresponding outputs being compared through Majority Voters (MVs). However, it may not be efficient to mitigate multiple faults. TMR uses majority voters to choose the correct value by selecting two out of three. The voting is usually done bit a bit. Therefore, TMR can cope sometimes with multiple faults that may affect different bits voted by distinct majority voters. However, it is important to investigate how much faults a TMR technique can tolerate. Moreover, because of that, voters can be placed among combinatorial and sequential logic blocks, where

it creates barriers to the faults. However, this approach, which uses replication of identical components, is not immune to multiple faults, for example. This work uses TMR with different granularities, this means, to insert different number of majority voters in different parts of the circuit.

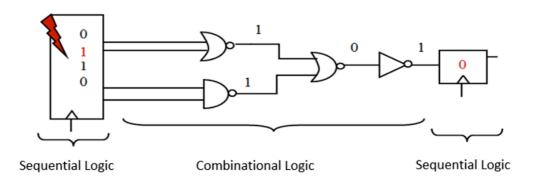

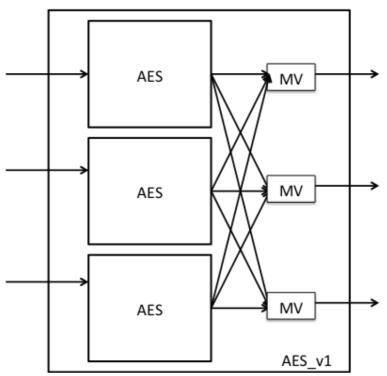

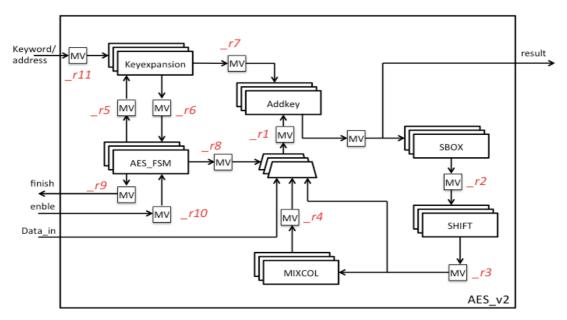

It may be implemented at Register Transfer Level (RTL) or netlist level. The tool can remove redundant logic judging unnecessary or change some parts of the circuit in order to optimize. Consequently, the TMR added on the RTL level can be interpreted by the synthesis tool as repeated logic, and thus removed. Otherwise, when the TMR is added after the synthesis, it is guaranteed that the circuit will be maintained. There are different levels of implementation using majority voter, it can be only in the final output of the circuit, Coarse Grain TMR (CGTMR), or between blocks, Fine Grain TMR (FGTMR), as can be seen in the figure 2 and figure 3, respectively.

Fig. 2 Circuit protect by CGTMR

Fig. 3 Circuit protect by FGTMR

In a multiple fault scenario, TMR may not always present an acceptable level of fault tolerance (SAMUDRALA, 2004). One of the main problems is single-event-induced charge sharing, an effect that occurs when multiple faults are created, generally at physically adjacent circuit nodes by a single particle strike. They can manifest themselves as Single-Event Effects (SEEs), affecting either combinatorial or sequential nodes (OLSON, 2005).

When considering single-event-induced charge sharing, there is one primary node that receives the primary impact, and the neighboring secondary nodes that can collect part of charge deposited by the particle that struck the primary node (MASSENGILL, 2007). The number of multiple upsets will depend on many aspects such as deposited charge, distance of the transistors in the layout, state of the transistors, charge collected by each sensitive node, fan-out of each node, logic masking, electrical masking, and the latch-window masking. In addition, there is the pulse quenching effect (AHLBIN, 2009) that must also be considered.

The problem of mitigating multiple upsets cannot be solved with the use of TMR solely because multiples upsets can occur in different modules depending on the placement. That being said, a constrained placement methodology was presented in (ENTRENA, 2012). It takes into account the information about the placement of standard cells in the circuit layout and it identifies certain standard cells that must be placed far away from each other in order to reduce the error rate. The limitation of this method relies on the placement tool that does not always honor these distance constraints that have been specified (placement tools target is usually to optimize other circuit parameters and characteristics, such as area, routability and delay). In this case, TMR with different levels of granularity can be used to improve the probability of masking multiple faults in the circuit. The placement of the cells combined with an optimal TMR partition with the majority voters are very important factors to reduce the probability of errors due to multiple faults.

The use of hardware redundancy by itself is not sufficient to avoid error by multiple faults, and it is mandatory to reload constantly the system to avoid the accumulation of faults. So, an injection methodology of multiple faults has been presented. It takes into account the real position of nodes in the Application Specific Integrated Circuit (ASIC) circuit. Moreover, a study using TMR verifies when an insertion of majority voters can be used to increase the reliability of TMR to multiple faults.

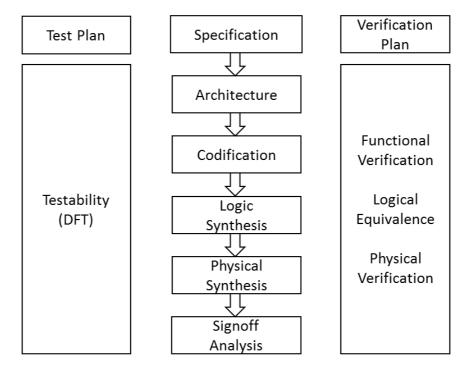

The proposed methodology uses TMR hardening under various levels of granularity. Constrained placement is also used to minimize the Soft-Error Rate (SER) due to single-event-induced charge sharing. The design flow of an ASIC is commonly performed by a set of Computer Aided Design (CAD) tools that automate the synthesis of a hardware description

language design into a netlist of standard cells. The Integrated Circuit (IC) implementation flow involves several steps and changes of one company to another, but it is very similar with other flow, to re-programmable device, such as a Field-Programmable Gate Array (FPGA) flow. Essentially a generic flow can be described as following in figure 4.

Fig. 4 Generic ASIC flow

Each one of the tasks is a transformation, which the current design goes through. We modified some of these steps in order to implement the techniques used in this work. One alternative design flow is performed to introduce the techniques implementation.

The design flow is performed once to generate a first draft layout to be analyzed by AMUSE. This tool will generate a list of SER rate and a list of the most sensitive pairs of nodes. With this information, it is possible to build a set of placement constraints and perform again the design flow. Two constraints can be setup. One is the floorplanning constraint file, which may force two or more standard cells to be placed as close as possible; the other is the area usage constraint, which defines the percentage of area usage for the standard cells available in the core surrounded by the pads. The lowest parameter is, for example, 0.5 nm, which means the highest distance between standard cells. According to the size of the circuit and the number of pads, the final area of the chip may or may not vary by changing the usage area parameter.

The goal of this work is to compare the addition of MV with the use of area utilization in order to achieve an optimal partition of the TMR logic and placement constraint methodology. The circuit must be well designed to have minimal number of voters and the best positioning of the cells. The aim is to maximize the fault tolerance without sacrificing the performance and area of the circuit.

This work investigates effects of single-event-induced charge sharing in various TMR schemes with different levels of granularities where MVs are placed in different locations in the design. The case-study circuit is an Advanced Encryption Standard (AES) algorithm (NIST, 2001) implemented in a RTL using VHDL. This analysis evaluates the SER, it uses a fault injection method (ENTRENA, 2012), and it injects millions of multiple faults in adjacent standard logic cells of the design, with the aim to analyze the robustness of the TMR versions. Finally, results show the best trade-offs between soft error rate, area and performance.

The dissertation is organized as follows:

Chapter 2 briefly introduces the problem of multiple faults and radiation effects on integrated circuits manufactured using Complementary Metal-Oxide-Semiconductor (CMOS) process, types of fault, and fault tolerance approaches to mitigate these effects in ASIC circuits.

Chapter 3 shows the proposed ASIC design flow aiming evaluating ASICs under multiple faults scenarios. The changes were made in generic flow in order to evaluate SER, as well as how is done the fault injection using the AMUSE on our case study, and the results.

Chapter 4 presents the improvements on placement constraints methodology for ASICs under multiple faults scenarios. How the methodology works and shows the results in a case study using only this mitigation technique.

Chapter 5 introduces the state of art of fault mitigation techniques based on modular redundancy. It shows the concepts of TMR and its limitation, Diverse Triple Modular Redundancy (DTMR), and n-Modular Redundancy (NMR) to cope with Charge Sharing.

Chapter 6 introduces the use of TMR in several levels of granularity to protect the circuits against multiple faults. The campaign of faults injection takes into account one main cell and a neighborhood within a given radius around this cell. The impact of a design that aims at fault tolerance for Single-Event-Induced Charge Sharing. The ASIC circuit was divided into logic blocks by functionality and it has been added majority voters gradually to decrease the number of single point of failure. Each block has different characteristics and importance on the final result. The goal is to compare several granularities of TMR using an

amount of one to twelve groups of majority voters between blocks, and based on the results, we can improve the results obtaining a lower error rate. The techniques will use a fault injection with AMUSE and the results will be compared using a golden circuit. The application of the technique will be discussed and final results will be presented.

Chapter 7 presents a fault injection in the same case study but using FPGA. The conclusions of the dissertation are addressed in the Chapter 8, followed by the references and publications.

#### 2 MULTIPLE TRANSIENT FAULTS SCENARIOS

Before introducing the developed work, this section is intended to introduce the state of the art about radiation effect and its potential effects. It will be presented the concepts about impact of radiation, which has been categorized the multiple fault scenarios.

## 2.1 Types of Radiation Faults

The types of faults are categorized according to its duration of time and storage in circuit. It can be such as Total Ionization Dose (TID), which are permanent, or SEE, which are considered transient effect faults.

The TID is over a long time, when the integrated circuit is exposed to radiation during a determined period of time. Normally, these effects are related with the intensity and time that the circuit was accumulating charge. The first satellite failure due TID was the Telstar. It was launched in July 10, 1962. Therefore, the first studies were presented in 1967. The TID, mostly due to electrons and protons, can result in device failure. In either case, TID can be measured in terms of the absorbed dose, which is a measure of energy absorbed by matter. Absorbed dose is quantified using either a unit called the rad (an acronym for radiation absorbed dose) or the International System of units (SI unit) which is the gray (Gy) = 1 Gy = 100 rads = 1 J/kg.

The trapped protons and electrons, secondary Bremsstrahlung photons (electromagnetic radiation produced by the deceleration of a charged particle when deflected by another charged particle), and solar flare protons are the main sources of TID. Some other particles from galactic cosmic ray ions are negligible in the presence of these others.

It primarily affects the oxide layers, which may trap charge or produce interface changes. In Metal-Oxide-Semiconductor (MOS) devices, trapped charges can lead to a shift in the gate threshold voltages. More generally, in semiconductors, interface states can significantly increase device leakage currents. Ultimately, TID provokes permanent functional failures of the device (LABEL, 1996) shown as degradation of the transistor devices as voltage threshold shifts and increase in leakage current.

SEE is one of main problems in space, it happen when charged particles hit the silicon transferring enough energy in order to provoke a fault in the system. SEE can have a destructive or transient effect, according to the amount of energy deposited by the charged particles and the location of the strike in the device (O'BRYAN, 1999). It can be subdivided in two main types: Single Event Transient (SET) or Single Event Upset (SEU).

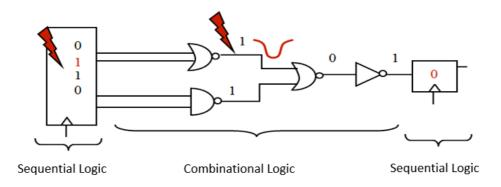

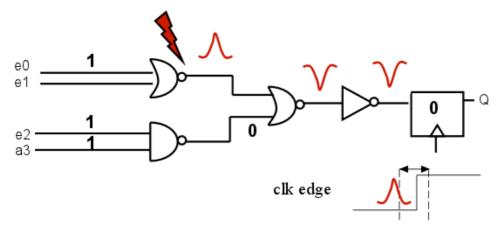

SET are caused when a particle strikes a transistor, changing the outputs logic value in the combinational logic. SEU is a wrong value in a sequential cell, which can be caused by propagated SET or a particle strike directly in a sequential cell (bit-flip). The figure 5 exemplifies SET and SEU. When a pulse or bit-flip occurs due to a radiation energy particle, it can be propagated to entire circuit arriving in a temporal barrier (flip-flop) where it is stored.

Fig. 5 Example of SEU and SET

In the space environment, spacecraft designers have to be concerned with two main causes of SEEs: cosmic rays and high-energy protons. For cosmic rays, SEEs are typically caused by its heavy ion component. These heavy ions cause a direct ionization SEE, i.e., if an ion particle hits a device that deposits sufficient charge an event such as a memory bit-flip or transient may occur. Cosmic rays may be galactic or solar in origin. (NASA, 1998)

Protons, usually trapped in the earth's radiation belts or from solar flares, may cause direct ionization SEEs in very sensitive devices. However, a proton may more typically cause a nuclear reaction near a sensitive device area, and thus, create an indirect ionization effect potentially causing an SEE (NASA, 1998).

SEE may occur due to the amount of energy of the particle that is transferred to the material, which is determined by the LET (Linear Energy Transfer). LET is a measure of the energy deposited per unit length as an ionizing particle travels through a material. The common unit is  $MeV*cm^2/mg$  of material (Si for MOS devices) (BOUDENOT, 2007). The LET threshold (LETth) is the minimum LET to cause an effect at a particle fluence of the  $1x10^7$  ions/cm<sup>2</sup>. The fluence is the number of particles passed through cm<sup>2</sup>.

Sensitive volume refers to the device volume affected by SEE-inducing radiation. The sensitive volume is, in general, much smaller than the actual device volume, its geometry is not easily known, but some information is gained from test cross section data.

Since both TID and SEE are from ionizing radiation, it is important to address the difference between the two with respect to design and analysis. TID is a long-term failure mechanism versus SEE, which is an instantaneous failure mechanism.

The error caused by radiation might be also destructive, known as single event hard errors, or the non-destructive, called soft errors. When talked about destructive errors, it is possible to observe that the object of this work does not compose, but comprehend the following species:

- Single Event Burnout (SEB) is a highly localized burnout of the drain-source in power MOSFETs. SEB is a destructive condition;

- Single Event Gate Rupture (SEGR) is the burnout of a gate insulator in a power MOSFET. SEGR is a destructive condition

- Single Event Latchup (SEL) is a potentially destructive condition involving parasitic circuit elements.

Regarding the soft errors or unique events, terms usually used like synonym by literature, commits a stored logic value or a signal that does not damage the device. The two more important soft error types for this work consist in SET and SEU.

## 2.1.1 Single-Event Transient

The well-established SET fault model is based on a single particle hitting a sensitive node in silicon, and generating a transient pulse, which changes the state of the affected node (DIEHL-NAGLE, 1984). These effects are temporary voltage glitches in combinational logic originated by the collection of charge deposited by ionizing particle strikes in the sensitive nodes of the combinational logic (BLUM, 2007).

The particle strike produces several hole-electrons under effects of the electric field. The charge generated tends to change the logic value of the struck node with a short voltage pulse, called transient pulse. However, this phenomenon can be or not captured by a memory cell or propagated throughout the circuit to the output. In other words, the SET does not always cause a failure in the system.

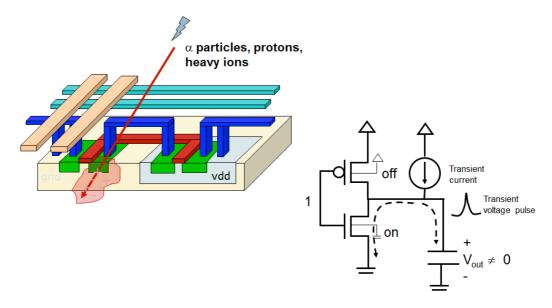

The figure 6 shows an example when a particle (normally protons and heavy ions cause SET) strikes in a transistor. Whether a transistor has "1" in its output and a transient current strike, the voltage pulse can be enough to switch the transistor to ground, changed the logic value to "0".

Fig. 6 Single Event Transient in transistor

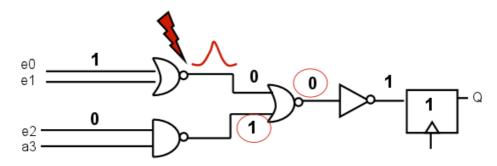

As explained before, the SET may not be captured by a memory cell or propagated, not affecting the output of the system. Some effects can be observed, they can prevent a transient pulse in combinational logic from propagating to output or being stored in a memory cell. There are three main masking effects, which can prevent a transient pulse in combinational logic from propagating and being latched by a memory element: logical masking, electrical masking, and latch window masking. The figure 7 shows logic masked. It is when a particle strike in part of the combinational logic, which has not any effect in the output (ENTRENA, 2009). The output has it logic value defined by only one of the inputs, so if glitches occur in other part of circuit, the output is not changed.

Fig. 7 Example of logical masking

Figure 8 shows the second type of masking, the electrical masking occurs when the result pulse of collision of a particle is attenuated in amplitude by whole of combinational circuit.

Fig. 8 Example of electrical masking

The third type is shown in Figure 9, latch window masking, and can occur when the glitch violates the times of setup and hold in a flip-flop, thus the wrong value is not stored.

Fig. 9 Example of latch window masking

## 2.1.2 Single-Event Upset

Some elements are capable of storing a binary value, and posteriorly recover the bit value, if necessary. Figure 10 exemplifies this in a sequential cell, which can be a flip-flop, latch or cell memory. Generally, called of memories cells, are the most susceptible to SEU as Static Random Access Memory (SRAM), Dynamic Random Access Memory (DRAM), latches and flip-flops.

Fig. 10 Example SEU

The SEUs is the main challenge to ensure the reliability in memories cells responsible for the state change induced by incidence of heavy ions or electro-magnetic radiation in a sensitive node of a circuit. This effect becomes more worrisome if these cells are exposed to high-energy particles in space.

NASA defines SEU as "radiation-induced errors in microelectronic circuits caused when charged particles (usually from the radiation belts or from cosmic rays) lose energy by ionizing the medium through, which they pass, leaving behind a wake of electron-hole pairs." (NASA, 1967) SEUs are transient soft errors, and are non-destructive. On the other hand, it is when the charge has energy enough to change the logic value or when a SET is propagated to a memory cell being stored. In this case, the charge deposited by the particle may cause malfunction of the circuit. They normally appear as transient pulses in logic or support circuitry, or as bit-flips in memory cells or registers.

The memory elements can be DRAM, SRAM or flip-flop. When the particle strike has energy enough to change the cell value, the charge is collected in form of transient current on the transistor struck.

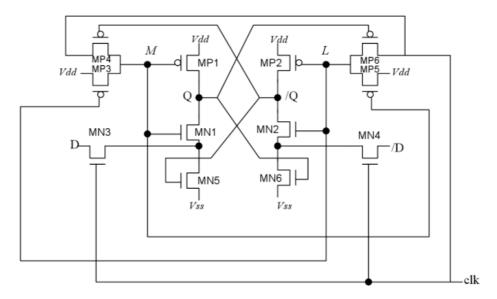

Faced with this problem, memory cells must be flexible to be tolerant SEU, therefore a set of cells that are derived from the standard static SRAM memory, as Heavy Ion Tolerant (HIT) in figure 11 and Dual Interlocked Storage Cell (DICE) in figure 12, for example.

Fig. 11 Hit memory cell

Fig. 12 DICE memory cell

These cells utilize methods to make them fault-tolerant. However, each method may use different techniques. The most widespread use feedback or duplication of information, making the data can be reversed by refeeding or by restoring the same that is storing in an isolated node, respectively.

## 2.2 Multiple Faults

With smaller device geometries in nanoscale technologies, it is very likely that a high energy particle strike affects several adjacent cells in a circuit resulting in Multiple Event Transients (MET) in combinational gates or Multiple Bit Upsets (MBU) in sequential elements. (RADAELLI, 2005)(GIOT, 2008) (MAESTRO, 2008)(HARADA, 2011).

Those multiple simultaneous faults are still due to a single particle hitting the silicon, in which case secondary particles can be emitted in several directions, as illustrated in figure 13 (ROSSI, 2005).

Fig. 13 One particle, multiple effects (ROSSI, 2005)

What has changed is that, since the devices are now closer to each other, those secondary particles may eventually affect two different nodes of a circuit, generating two simultaneous effects (NEUBERGER, 2003).

Moreover, after experimentally confirming that two simultaneous upsets affecting adjacent nodes can occur, Rossi (2005) has shown that the occurrence of bi-directional errors, i.e., two simultaneous complementary bit flips, will be possible, precluding the use of error detection codes designed to detect only unidirectional simultaneous errors.

One year later, Ferlet-Cavrois (2006) presented a detailed study on the charge collection mechanisms in SOI and bulk devices exposed to heavy radiation, using different technologies, from 0.25 µm to 70 nm. For bulk devices, that analysis shows that the shape and duration of transient pulses present significant variations, depending on the fabrication details, on the technology itself, and on the location in the device that was hit by the particle. Moreover, the comparison of the behavior of the same device exposed to different radiation sources has shown that some particles do not have enough LET to induce SEUs or SETs by direct ionization. However, those particles generate secondary ones, with much higher LETs, that can be emitted in all directions. Once again, the hypothesis of multiple transients generated by a single particle hit has been confirmed.

#### 2.2.1 Single-Event-Induced Charge Sharing

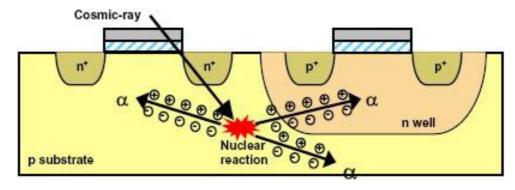

Single-event-induced charge sharing that is a typical problem when talking about deepsubmicrometer technologies due to the reduced distance between devices and their small node capacitances (VELAZCO, 1996) (OLSON, 2005) (BLACK, 2005) (AMUSAN, 2007). The separation between transistors has become far smaller, then the transistors can collect different amount of charges at the same time provoking multiple SEE, which manifest itself as a combination of SET and SEU effects, depending on whether the affected nodes are combinational or sequential, respectively. As shown in figure 14, the energy can be shared by adjacent cells, hitting one or more in a certain radius.

Fig. 14 Single-event-induced Charge Sharing

Charge sharing is a significant SEE issue because it can turn circuit-level hardening techniques ineffective. Multiple fault models must be taken into account to analyze error rate in high-density integrated circuits. When considering single-event induced charge sharing, it is common to have a primary impact device or active node, which is the struck hit node (i.e., hit node), and the adjacent devices or passive nodes, which are the neighboring nodes that can also collect some charge due to its proximity to the active node (MASSENGILL, 2007). For high-density integrated circuits, the active and passive nodes are not necessarily placed in the same combinational or memory cell.

Thus, it is important to analyze the effect of charge sharing not only inside a logic cell but also the impact of multiple faults in multiple logic cells in the circuit. Related works on charge sharing focus on determining the amount of collected charge in the passive nodes and to evaluate the effect of the charge sharing inside a single combinational logic gate and/or memory element (AMUSAN, 2006) (MASSENGILL, 2007) (LIU, 2009) (DODD, 2003) (MESSENGER, 1982). However, no previous work has considered charge sharing among logic cells and its effect in the functional behavior of an entire circuit.

With the advance of technology, it is expected that multiple passive nodes located in distinct logic cells may collect charge generating, simultaneously, multiple SET due to the reduced size of each logic cell. Therefore, in the current technologies, it is mandatory to characterize the sensitivity of the design to multiple faults in early stages of development.

The soft error characterization for single-event induced charge sharing can be done by fault injection considering the layout floorplanning and placement. The layout information as design placement and distances between devices are crucial data to define the possible combination of nodes affected by charge sharing at the same time. It is not realistic to inject multiple random faults, as the affected nodes must be placed together in a certain minimum distance for this phenomenon to actually occur. Many parameters must be analyzed. It is important to evaluate the number of nodes affected and the different transient pulses widths generated at each node.

For large and complex circuits, there are thousands or even millions of possible combinations of multiple upsets that can occur in a circuit and it is not feasible to analyze all combinations by simulation. Consequently, it is necessary to have a fast fault injection method that allows millions of faults to be injected in a short period of time but also taking into account the charge sharing information.

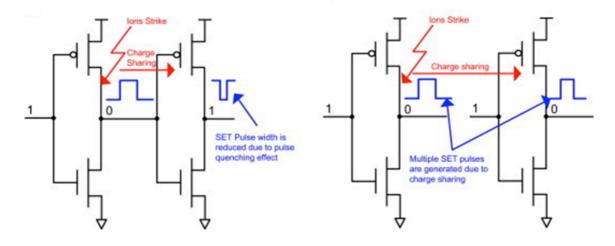

### 2.2.2 Pulse Quenching

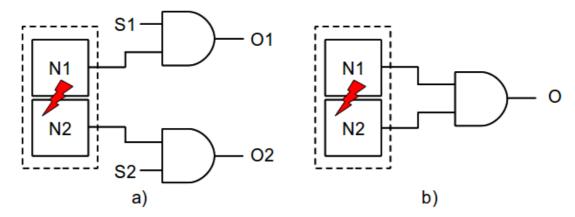

Another effect, called quenching, or pulse-quenching effect has been studied. This effect occurs with the interaction in a way as to truncate a propagated voltage transient, effectively limiting the observed SET pulse widths at high LET. It is related with multi-node charge collection due to a single ion hit (YANKANG, 2013). This approach was used initially to reduce the propagated single event transient in some works (AHLBIN, 2009) (ATKINSON, 2011). However, the layout cell is a factor to reduce SEE or to increase the number of Multiple Single Event Transient (MSET) due charge sharing in transistors without no electrical relationship. Let us consider the examples, as it can be seen in figure 15. The nodes N1 and N2 are placed close enough to suffer single-event-induced charge sharing effects. For simplicity, we neglect delays and assume that all involved signals are independent and have the same probability to be 0 or 1, p = 0.5.

Fig. 15 Multiple fault propagation: a) Independent propagation paths b) Convergent propagation paths

The example in figure 15a illustrates the case where nodes N1 and N2 have independent propagation paths. A single fault in node N1 propagates to output O1 when the side input S1 is 1. Thus, the probability that the fault in N1 propagates to the output is p1 = 0.5. Similarly, the probability that a fault in node N2 propagates to output O2 is p2 = 0.5. The joint propagation probability that a double fault in N1 and N2 propagates to any of the outputs is p12 = p1 + p2 - p1p2 = 0.75.

As expected, the joint propagation probability is higher than the single fault propagation probability. This is an example when charge sharing has a negative effect. The example in figure 15b shows the case where the paths from N1 and N2 converge to a single output. In this case, propagation conditions are not independent. Let v(X) is the logic value at node X. The state of the circuit at a particular time is represented as v(N1)v(N2)/v(O). Using this notation, there are four possible states with the same probability:

• 00/0, 01/0, 10/0 and 11/1.

A single fault in N1 changes these states into:

• 10/0, 11/1, 00/0 and 01/0.

The output O is erroneous in two cases, namely the second and the fourth. Thus, p1 = 0.5 as in the example in figure 15a. Similarly, p2 = 0.5. In the case of a double fault in N1 and N2, the faulty states are 11/1, 10/0, 01/0 and 00/0. The output is wrong in the first and fourth cases and the joint probability is p12 = 0.5. Thus, the joint propagation probability is lower than in the example in figure 15a and is the same as the single propagation probability. This is because when the logic values at N1 and N2 are different, the errors cancel each other and produce a correct output. Note that if these states are more probable than the others, the joint propagation probability can be even lower than the single propagation probabilities. For instance, if the probabilities of each state are 0.1, 0.4, 0.4 and 0.1, respectively, then p1 = p2 = 0.5.

0.5 and p12 = 0.2. This is a positive charge sharing effect. Similar results are obtained for their convergent paths with different types of gates.

These examples demonstrate that charge sharing with positive effects is possible. In a complex network, many other possible situations can contribute to reduce charge sharing effects. Although charge sharing occurs more readily between devices in the same wells (AMUSAN, 2008), for the sake of generality it will consider that any pair of adjacent cells can be upset, without making any particular assumption about the implementation that could contribute to mitigate charge sharing effects. The goal of this is to identify the pairs of cells that minimize single-event-induced charge sharing effects and use this information to guide the placement process.

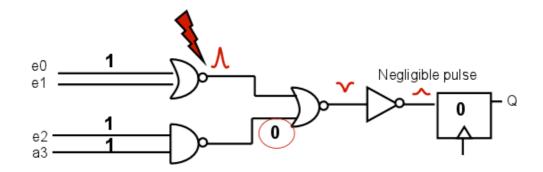

The pulse quenching can be seen in figure 16, where it has two inverters that are physically adjacent in a circuit layout. In the first case, the inverters have electrical relationship. When one ions strike in an off transistor and its charge is shared, the SET pulse width is reduced due to pulse quenching effect. In order words, the logic value of the output of first invert is inverted, so the output of the second inverter is attenuated. In the second case, the output of the both inverters is inverted. This factor generates multiple SET due charge sharing.

Fig. 16 Pulse quenching effect and Multiple SET pulse (YANKANG, 2013)

Yankang at el. studied the impact of pulse quenching effect on soft error vulnerabilities in combinational circuits based on standard cells. Their simulation indicated that the soft error vulnerabilities could be reduced by 4-16% when pulse-quenching effect is introduced. They proposed an ideal optimized method to adjust the cell orientations to enhance the pulse quenching effect. This layout methodology could decrease the soft error rate when there are electrical relationships between two inverters, for example.

The two inverters are physically adjacent in a circuit layout. When these two inverters are electrically related, pulse-quenching effect could occur due to multi-node charge collection (YANKANG, 2013). This would reduce the propagated SET pulse width, which is beneficial to reduce the circuit soft errors (AHLBIN, 2009) and (ATKINSON, 2011). However, when these two inverters have no electrical relationship, MSET pulses might appear due to charge sharing. MSET pulses could shrink or enlarge the soft error vulnerabilities, depending on the circuit topology (PAGLIARINI, 2011) and (ENTRENA, 2012). For instance, when the generated MSET pulses converge at one logic cell and partially cancel each other, the SET pulse width at the primary outputs would be reduced (ENTRENA, 2012). This could lower the soft error vulnerabilities.

## 2.3 Multiple Faults Scenario focused on this work

In this work, we proposed a SER characterization methodology for single-event-induced charge sharing in standard-cell based designs. This methodology analyzes the effect of multiple SET at logic and system level by considering the information of charge sharing from the actual design placement using emulation.

In other words, when a particle (whether charged or not) strikes a specific spot in the circuit may or may not distribute its charge among the neighborhood of standard cells, it provoking the logic value change. In such case, the insurgent multiple faults errors may propagate them to other parts of the circuit leading to several misbehavior. Consequently, if the circuit is a mission-critical system not hardened by any faults tolerance methodology, it could lead to safety issues or even money loss.

Previous studies do not take into account the placement of cells to inject faults. A campaign of fault injection was performed randomly. In our studies, we could observe that the charge sharing happens in neighboring cells. In this scenario, this work was performed to find the best trade-off between area, performance and SER.

## 3 PROPOSED ASIC DESIGN FLOW AIMING EVALUATING ASICS UNDER MULTIPLE FAULTS SCENARIOS

ASIC is a design of integrated circuit made from silicon wafer for a specific application (DI FEDERICO, 2012). There are standard product or general purpose that are not as specific as ASIC, such as a logic gate or a general-purpose microcontroller, but both of which can be used in any electronic application by anybody. Examples include, chip for a satellite, chip for a car, chip for a medical IC designed to monitor a specific human biometric parameter, chip designed as an interface between memory and Central Processing Unit (CPU) and so on. The ASICs are divided in three different classes. There are:

- Custom ASIC: For this type of ASIC, the designer designs all or some of the logic cells, layout for that one chip. The designer does not used predefined gates in the design. Every part of the design is done from scratch.

- Standard Cell ASIC: The designer uses predesigned logic cells such as AND gate, NOR gate, etc. These gates are called standard cells. The advantage of standard cell ASICs is that the designers save time, money and reduce the risk by using a predesigned and pre-tested standard cell library. In addition, each standard cell can be optimized individually. The standard cell libraries are designed using the full custom methodology, but you can use these already designed libraries in the design. This design style gives a designer the same flexibility as the full custom design, but reduces the risk.

- Gate-Array ASIC: In this type of ASIC, the transistors are predefined in the silicon wafer. The predefined pattern of transistors on the gate array is called a base array and the smallest element in the base array is called a base cell. The base cell layout is same for each logic cell, only interconnects between the cells and inside the cells is customized.

When designing a chip, it is necessary to achieve the better solution to a specific application; the following constraints are taken into account:

- Performance

- Area

- Power

- Time to market

There are several kinds of design flow for different vendor (Cadence, Synopsys, Mentor and so on). Robustness is a custom ASIC but the cost and time to manufacture is larger than the others. In this work, we use the most common and cheap, which is standard logic that will be showed in this chapter.

## 3.1 Basic Design Flow

A simple digital flow is presented in figure 17 for a digital flow. The main goal is to understand the digital flow for sequential and combinational circuits in order to explain later in more details the modifications and additions that were performed to improve robustness to multiple faults.

Fig. 17 Design Flow

Specification and architecture define the functionality and architecture. There are two types of specification: functional and structural. The functional specification is a formal document that describes all external interfaces and how the chip should behave. The structural specification describes all internal modules and your connections; this document directs the designer to choose the architecture and how to code it. For digital designer, how going to be Finite State Machine (FSM) or combinational circuit (Karnaugh Map).

After define the architecture, the next step is codification. Hardware languages as Verilog or VHDL are used to implement a behavior structure and achieve the all defined structural specification. The modules are defined within *process* (VHDL) or *always* (Verilog). It may be sensitive to clock or any input, sequential or combinational, respectively.

The Logical Synthesis is the procedure of translation between behavioral codes to structural netlist mapped on gates (Standard Cell Methodology). This is similar to use of boolean algebra for combinational circuits, where each operand is mapped a logical gate. Some tools can generate bitstreams for programmable logic devices (FPGAs), while others target the creation of ASICs. The tool needs RTL code and the cell library target for mapping in logic gates.

Physical Synthesis and Signoff is the layout phase. Procedures as floorplanner, placement, routing and physical verifications are done. This work focus in techniques to decrease the SER, mainly in the placement step. The tool import the outputs from logical synthesis, the design netlist and constraint file together with the technology libraries, to proceed the physical synthesis.

Testability is the insertion of extra logic that of circuit's functionality to test after manufacture; these steps are performed at transistor level schematics, and Functional Verification is done at simulation, where is created a verification environment to verify the functionality is according with specification.

The figure 18 shows the mapping of HDL in logic gates. The logical synthesis needs, at least, three inputs: Timing library (.lib), time constraint (.sdc) and HDL. It can generate how many designs you want just changing the input files.

Fig. 18 Logic synthesis flow

Timing library (.lib) file is an American Standard Code for Information Interchange (ASCII) representation of the timing and power parameters associated with any cell in a particular semiconductor technology. The timing and power parameters are obtained by simulating the cells under a variety of conditions, and the data is represented in the .lib format. The .lib file contains timing models and data to calculate:

- I/O delay paths

- Timing check values

- Interconnect delays

Time constraint (.sdc) is a format used to specify the design intent, including the timing, power and area constraints for a design. Synopsys Design Constraint (SDC) is tel based that is a guide for logical synthesis to choose the right gate size. The Library Exchange Format (LEF) is added to synthesis logic, and it is important because influence on susceptibility to single and multiple faults.

Command Types, normally are the operating conditions, wire load models, system interface, design rule constraints, timing constraints, timing exceptions, area constraints, multivoltage and power optimization constraints and logic assignments. It is used to help the tool estimate better these parameters.

Therefore, the tool reports the netlist that will be loaded in the next phase of project, physical synthesis. Backend loads the netlist in tool to generate all reports to manufacture design are described.

Physical Synthesis makes use physical layout and timing information of the target device in order to achieve the minimum area usage at the required speed. The figure 19 shows a kind of physical synthesis.

Fig. 19 Physical Synthesis Flow

Before starting the floorplan, it is necessary to load all information related of the netlist, libraries, LEFs, SDC and IO files.

The designer must create the SDC and IO files. In addition, to add all libraries. Finally, the designer needs to define power and ground nets to share out for whole the circuit.

The physical design begins with a floorplan, to specify the utilization to derive the core size of the design and estimate wiring lengths and wiring congestion. Floorplanning takes into account the macros used in the design, memory, other IP cores and their placement requirements, the routing possibilities, and also the area of the entire design. Floorplanning also decides the IO structure, aspect ratio of the design.

Before start, the floorplan is a good practice to do a time analysis (Pre-place) to avoid loading a design with some problems of the time, like a huge time slack negative, which is the difference between arrived time and capture time. In this step, you place pads, blocks and minimize cross route. In power plan, the designer creates rings and stripes for the blocks in the design, separating digital and analog blocks, which have different power structures. To create the core ring and add stripes to balance the distribution of power for whole circuit, avoid problems like ir-drop. The block pins, pad pins, pad rings and standard cell pins are connected on power and ground nets of the rings and stripes. In this phase, it is needed to verify if all power nets are connected.

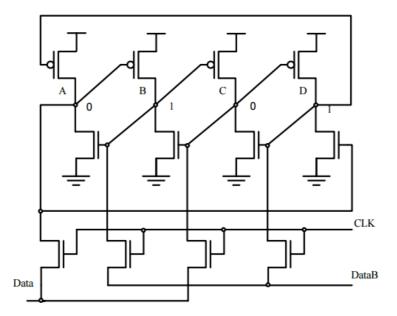

The placement distributes all the cells in the design. It can specify some options like list of spare cells, Jtag cell to test and so on. All cells are pre-determined in the libraries cell, which were loaded in tool on import design. To make the flip-flops in the design controllable and observable to do test, the scan chain is inserted. The next step is the route, the tool connect all sequential and combinational logic, and can create congestion and timing violations. Routing of nets, evaluating LEF layers for the best choice. Taken into account spacing rules, routing of pins and vias, process antenna, geometry and so on.

The clock tree synthesis is the selection of cells (buffers, inverters and gate elements) to use for clock tree synthesis and run in the tool taken into account.

Concluded all this phases, another tool performs the verification of the design according to the rules from technology files, called Design Rules Checking (DRC), as well as verifying if the layout is consistent with the schematic, Layout versus Schematic (LVS).

Some analysis can be performed to verify time and power problems in different parts of the flow. As well as verification about geometry, process antenna, connectivity, density and so on. The tools take into account information on libraries and generate reports.

The final of the flow is save some files to send to foundry to be manufactured. Those files are:

- Design Exchange Format (DEF)

- Standard Parasitic Exchange Format (SPEF)

- Netlist

- SDC

The signoff analysis provides a comprehensive timing analysis and signoff verification solution that includes automated signoff Engineering Change Order (ECO), advanced modeling for precise delay calculation, power-aware, static timing analysis, accurate Signal Integrity (SI), crosstalk delay and flitch analysis, and statistical timing and leakage analysis.

#### 3.2 Analyzing Sensitive Multiple Fault Nodes

In the literature, there are several ways to analyze the sensitivity of a device to faults. In the laboratory, it is common to use fault injection. Fault injection either at the hardware level (logical or electrical faults) or at the software level (code or data corruption) and the effects are monitored. In this work, we perform fault injection at design level in case of the ASICS case study circuit using the AMUSE platform that emulates the design in a FPGA platform to speed up the injection. The robustness measurement is analyzed in terms of SER, which means the number of injected faults able to cause an error in the output of the design.

As mentioned previously, the design flow of an ASIC is commonly performed by a set of CAD tools that automate the synthesis of a hardware description language design into a set of standard cells, performs the floorplanning, placement and routing, and finally generates a layout. In this work, we added some extra tools to the original basic CAD tool flow to analyze the neighborhood cells and to inject faults to measure the probability of error rate due to charge sharing. Figure 20 shows the flow with the added gray blocks, which is composed of the constrained placement methodology. This part was added to reduce the SER of single-event-induced charge sharing by placing the most sensitive cells far away from each other and fault injection tool to evaluate the SER.

Fig. 20 The proposed methodology to reduce SER in multiple faults using placement constraints

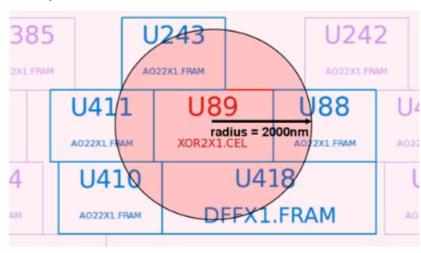

The first layout is saved in a DEF file. The file is used as the main input to the neighboring standard-cell analyzer tool, proposed in (PAGLIARINI, 2011). This tool receives as inputs the size of the radius and the number of nodes in which the charge sharing effect is considered. At the end, the tool generates a list of neighboring nodes that is composed of the primary node and others standard-cell nodes that are struck at the same time when single-event-induced charge sharing effect occurs. Therefore, the proposed methodology uses placement information to generate a fault injection list that correlates better with the actual physical behavior. Then, based on the list of the most sensitive set of nodes identified by AMUSE, it is possible to build a set of placement constraints to be hardened in order to mitigate single-event induced charge sharing effects and perform again the design flow. On the other hand, after this analysis, the circuit is resubmitted to AMUSE, which determines the actual SER of that optimized circuit.

AMUSE is a fault-injection system that supports SET and SEU fault injection and can be used for any ASIC technology. The main advantages of AMUSE are accuracy and

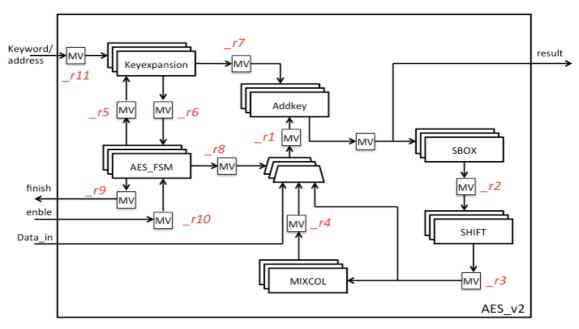

performance. AMUSE uses a quantized representation of time, voltage, and delays (ENTRENA, 2009), which allows to implement arbitrary ASIC delays by means of nonlinear counters. Time advances on a time quantum basis, performed by a time quantization clock. This approach covers all masking effects, including electrical masking effects, providing accuracy close to electrical simulation. On the other hand, the quantized model can be mapped into a field programmable gate array (FPGA) to boost performance. AMUSE fault-injection rates are typically in the order of 1 million faults per second, making multibillion fault-injection campaigns feasible in a short emulation time. The figure 21 shows AMUSE diagram.

Fig. 21 AMUSE block diagram

AMUSE has been extended to support the injection of multiple SETs and SEUs. Transients of a selected pulse width can be injected at any time and simultaneously into any combination of circuit nodes. For the affected combinational nodes, the logic value is changed while the injected pulse is active. For sequential nodes, the pulse produces a bit-flip that is kept beyond the end of the pulse until the end of the current clock cycle.

AMUSE has been used to estimate the SER for every possible set of nodes in the circuit. For each SET, several thousand pulses of selected duration were injected at random instants, and their effects after several thousand clock cycles were analyzed. The fraction of faults that produced any difference at the circuit outputs was used as an estimation of the SER due to charge sharing. The collected set of SER estimations for every possible set of nodes will be referred to as the cross-SER table. The cross-SER table is a matrix where each element contains the estimated SER for single-event-induced charge sharing of node and nodes in the case they were placed close enough. The complete cross-SER table can be computed within acceptable time for small circuits, in the order of 1000 nodes. For larger

circuits, a partial cross-SER table can be obtained by limiting the fault-injection campaign to the most critical nodes or, since circuits are organized hierarchically, by performing a partial analysis for each sub module of the design.

The optimal pairs of nodes can be identified by traversing the cross-SER table. In particular, we derived a set of placement constraints using the following approach. For every row, we first selected the four elements with the smaller SER. The resulting list of elements is then sorted according to the difference with respect to the average SER in its row. Finally, some elements are removed in order to ensure that no node appears in the list more than four times and that there are no redundant elements. The remaining elements constitute the set of placement constraints.

It is important to note that, for the example used in the experiments, the four elements selected for each row have a SER smaller or equal than the single-fault SER. In other words, for every node, it is possible to find at least four other nodes with positive charge sharing effects. This remarkable result demonstrates that charge sharing with positive effect can potentially be used to minimize the overall SER of a circuit due to multiple faults.

A SET can be modeled as a spurious voltage pulse on the output of a gate. The pulse may propagate across the circuit and eventually provoke malfunction. The purpose of fault injection is to inject SETs in a circuit and classify their effects. The resulting classification is an estimation of SET sensitivity for the circuit under test. In order to estimate the SER before the circuit is manufactured, fault injection is performed on the model of the circuit under test that results from the design process.

In emulation-based fault injection, the model of the circuit is downloaded into a FPGA. The voltage pulse induced by a SET is modeled at the logic level as an erroneous logic value (0 or 1) at the output of a logic gate that lasts for the duration of the pulse. Propagation of the pulse is then performed by executing the circuit in the FPGA and the fault effect is classified by comparing the result with a golden execution. Therefore, the emulation system must support fault injection at any gate and time instant, comparison between the golden and faulty execution, classification of fault effects, and external communication with the user. In Autonomous Emulation, all these functions are implemented inside the FPGA in order to improve emulation efficiency.

Propagation of a SET effect can be seen as a two-step process. First, the pulse is propagated throughout the combinational logic up to the memory elements (latches, flip-flops and memories). At this point, the SET effect can be seen as an SEU, if just one memory element or bit is affected, or as an MBU, in case several memory elements or bits are affected.

If the SET does not produce any change on the circuit state, it can be classified as having no effect. Otherwise, if the SET produces a SEU or MBU, then a second stage is needed. In the second stage, the SEU/MBU is propagated in subsequent clock cycles until the fault effect is finally classified.

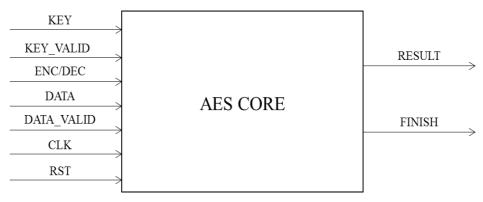

### 3.3 Case Study

The chosen case-study circuit is a crypto core that implements the AES algorithm (NIST, 2001) and supports a range of different configurations. For the purpose of this work, a key length of 128 bits has been considered during only the encryption process. The core was submitted to synthesis using Synopsys Design Compiler and a 90nm ASIC library also provided by Synopsys (SAED90nm) (SYNOPSYS, 2004). The resulting circuit has a total of 1,191 cells, from which 11 cells are memories, 156 cells are flip-flops and the remaining ones are combinational cells. The resulting area, excluding memory blocks, which are placed separately, is summarized in Table IV.