## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

## VINÍCIUS VALDUGA DE ALMEIDA CAMARGO

# **Evaluating the impact of charge traps on MOSFETs and Circuits**

Thesis presented as a partial fulfillment of the requirements for the degree of Doctorate in Microelectronics.

Advisor: Prof. Dr. Gilson Inácio Wirth

## CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Valduga de Almeida Camargo, Vinícius

Evaluating the impact of charge traps on MOSFETs and Circuits / Vinícius Valduga de Almeida Camargo. -2016.

77 f.:il.

Orientador: Gilson Inácio Wirth;

Tese (Doutorado) — Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica. Porto Alegre, BR — RS, 2016.

1.RTN. 2.BTI. 3.Ensemble Monte Carlo. 4.Simulação de circuitos. 5.TCAD. I. Wirth, Gilson. II. Evaluating the impact of charge traps on MOSFETs and Circuits.

### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Oppermann Vice-Reitora: Profa. Jane Tutikian

Pro-Reitor de Pos-Gradução: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Profa. Carla Maria Dal Sasso Freitas

Coordenador do Pós-Graduação em Microeletronica: Profa. Fernanda Gusmão de Lima

Kastensmidt

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **ACKNOWLEDGEMENTS**

I am very grateful to all my masters, specially to my advisor Gilson Wirth, to professor Dragica Vasileska and to Ben Kaczer, without the discussions with them and the knowledge they passed to me, nothing in this thesis would be possible.

I also grateful to my family and my beloved ones for all the love and support along this journey.

I am grateful my colleges in LAPROT, at ASU and at IMEC, specially to Maurício Banaszeski da Silva. Not only for making the day-to-day in the laboratory a pleasure, but also for the daily discussions in each other research. That is how many great ideas begin.

Análise do impacto de armadilhas em MOSFET's e circuitos

**RESUMO**

Nesta tese são apresentados estudos do impacto de armadilhas no desempenho elétrico

de MOSFETs em nível de circuito e um simulador Ensamble Monte Carlo (EMC) é apresentado

visando a análise do impacto de armadilhas em nível de dispositivo. O impacto de eventos de

captura e emissão de portadores por armadilhas na performance e confiabilidade de circuitos é

estudada. Para tanto, um simulador baseado em SPICE que leva em consideração a atividade

de armadilhas em simulações transientes foi desenvolvido e é apresentado seguido de estudos

de caso em células SRAM, circuitos combinacionais, ferramentas de SSTA e em osciladores

em anel. Foi também desenvolvida uma ferramenta de simulação de dispositivo (TCAD)

atomística baseada no método EMC para MOSFETs do tipo p. Este simulador é apresentado

em detalhes e seu funcionamento é testado conceitualmente e através de comparações com

ferramentas comerciais similares.

Palavras-chave: RTN. BTI. Ensemble Monte Carlo. Simulação de circuitos. TCAD.

Evaluating the impact of charge traps on MOSFETs and Circuits

**ABSTRACT**

This thesis presents studies on the impact of charge traps in MOSFETs at the circuit

level, and a Ensemble Monte Carlo (EMC) simulation tool is developed to perform analysis on

trap impact on PMOSFETs. The impact of charge trapping on the performance and reliability

of circuits is studied. A SPICE based simulator, which takes into account the trap activity in

transient simulations, was developed and used on case studies of SRAM, combinational

circuits, SSTA tools and ring oscillators. An atomistic device simulator (TCAD) for modeling

of p-type MOSFETs based on the EMC simulation method was also developed. The simulator

is explained in details and its well function is tested.

**Keywords**: Traps. RTS. BTI. Ensemble Monte Carlo. TCAD. Circuit simulations.

## LIST OF FIGURES

| Figure 2.1 - Bias point dependency of the capture and emission times for a particular trap 15                         |

|-----------------------------------------------------------------------------------------------------------------------|

| Figure 2.2- High level simulation framework (b) including the detail of the Trap kinetics on Verilog-A                |

| component (a)                                                                                                         |

| Figure 2.3- Trap activity impact on the threshold voltage of a PMOS transistor in time where both BTI                 |

| and RTN effects are present. 20                                                                                       |

| Figure 2.4- a) QQ-plot of the delay of an inverter considering the time zero variability and b)                       |

| considering also the trap activity after 1000s of stress on nominal operating voltage (0.8V) and duty                 |

| factor of 0.5                                                                                                         |

| Figure 2.5- Cumulative Density Function of 1000 periods of a (a) 3-stage ring oscillator and (b) of a 7-              |

| stage ring oscillator under the effect of trap activity                                                               |

| Figure 2.6- Threshold voltage as a function of time for the transistors M2 and M5 of the 6T-SRAM                      |

| case study cell and how these impact SRAM $V_{\text{min}}$ . The right hand side depicts the values after an          |

| elapsed time of $10^4$ s (indicated by the break of $10^4$ s shown in the time axis). During this time the cell       |

| suffered BTI, as seen in the threshold voltages and SRAM $V_{\text{min}}$                                             |

| Figure 2.8- The schematic of the analyzed paths. (a) Path1, (b) Path2 and (c) Path3                                   |

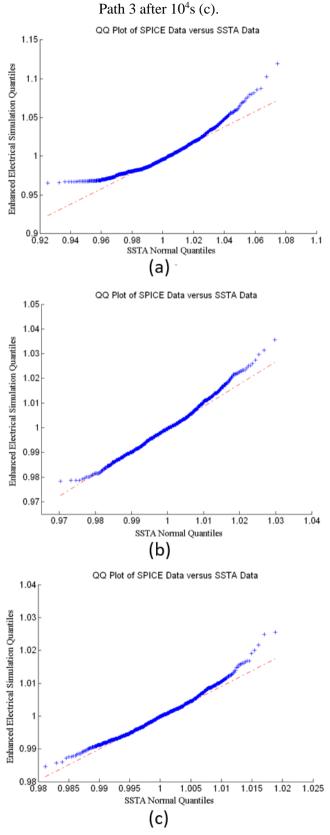

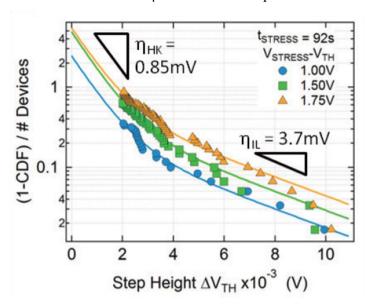

| Figure 2.9- The Q-Q plot of the normalized delay generated by the electrical simulation in comparison                 |

| with the one generated by the SSTA analysis in the Path 1after $10^4 s$ (a), in Path 2 after $10^4 s$ (b) , and in    |

| Path 3 after 10 <sup>4</sup> s (c)                                                                                    |

| Figure 2.10- Q-Q plots of the delays on paths 1 (a) and 2 (b) after 10 <sup>4</sup> s of stress considering time zero |

| variability                                                                                                           |

| Figure 2.11- Threshold voltage distribution due to NBTI considering (a), and not considering (b) time                 |

| zero variability                                                                                                      |

| Figure 3.1- (1-CDF) of step heights normalized to the number of tested nFETs after positive stress.                   |

| Data can be fitted with a bimodal distribution with $\eta_{IL}=3.7mV$ and $\eta_{HK}=0.9mV.$ Note that $\eta_{IL}$ is |

| similar to the $\eta$ value obtained in pFETs                                                                         |

| Figure 3.2- Relationship between the position of the trap along the channel length and the impact that                |

| a captured charge causes in the threshold voltage for devices with and without halo                                   |

| Figure 3.3- Device simulator Framework showing the coupling of the transport equations with the                       |

| Electromagnetic fields calculation. 37                                                                                |

| Figure 3.4- Semi-classical and quantum-mechanical transport approaches                                                |

| Figure 3.5- Bulk Monte Carlo simulation flowchart                                                                     |

| Figure 3.6 Silicon band structure including the Valence bands showing the Heavy (HH), light (LH)                      |

| and split-off (SO) bands. 45                                                                                          |

| Figure 3.7 – Iso-surfaces of energy for the (a) Heavy-hole band, (b) Light-hole band and (c) split-off                |

| band                                                                                                                  |

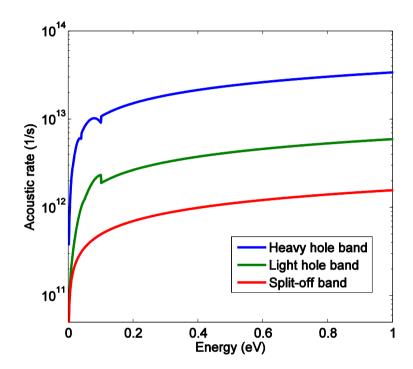

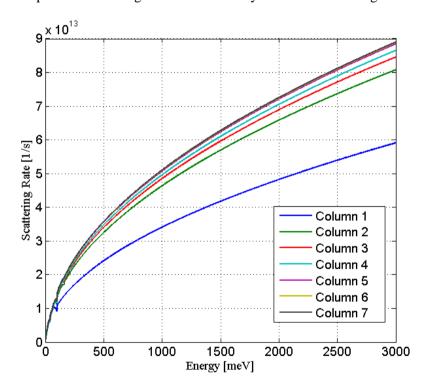

| Figure 3.8- Acoustic phonon scattering rates for holes residing in the heavy, light and split-off bands.    |

|-------------------------------------------------------------------------------------------------------------|

| This scattering process is intra-band (the initial and the final bands are the same)                        |

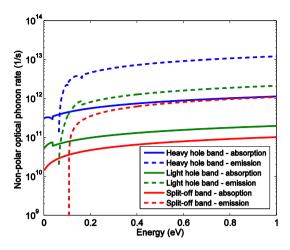

| Figure 3.9 - Non-polar optical phonon rates for holes scattering from the heavy hole band 49                |

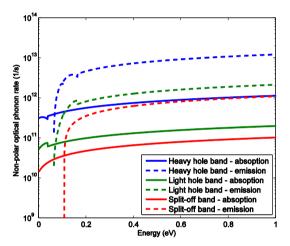

| Figure 3.10 - Non-polar optical phonon rates for holes scattering from the light hole band 49               |

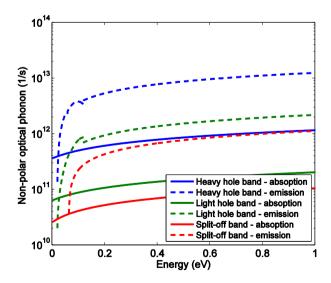

| Figure 3.11 - Non-polar optical phonon rates for holes scattering from the split-off band                   |

| Figure 3.12 - Example of a scattering table for the Heavy-hole band for energies smaller than 3eV 51        |

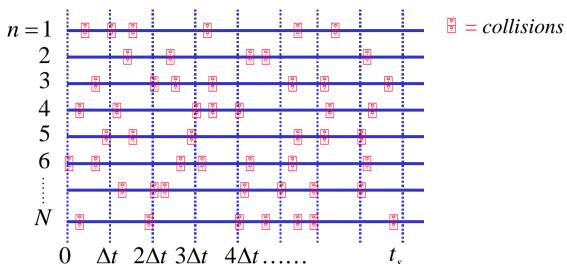

| Figure 3.13 - Ensemble Monte Carlo simulation in which an observation time, $\Delta t$ , is introduced over |

| which the motion of particles is synchronized. The squares represent random scattering events 53            |

| Figure 3.14 - Free-flight-scatter flowchart                                                                 |

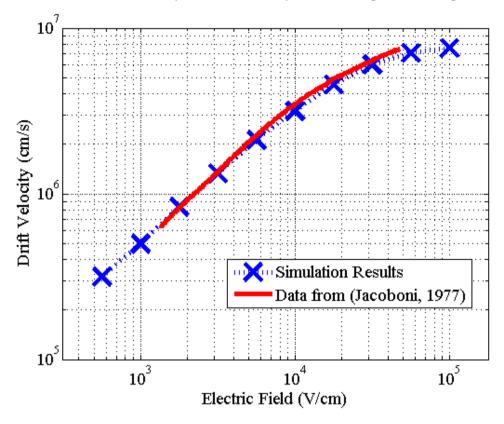

| Figure 3.15- Bulk Monte Carlo steady state drift velocity of holes compared with experimental data.56       |

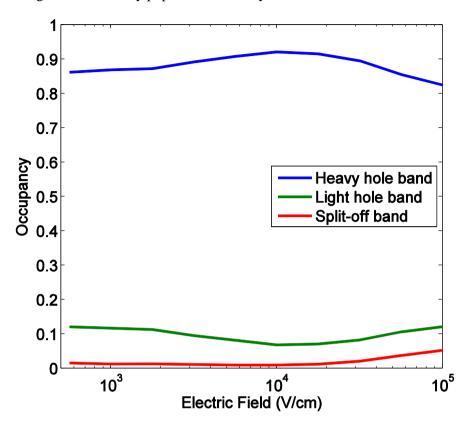

| Figure 3.16 - Valley population in steady state condition vs. Electric field                                |

| Figure 3.17 - Transient drift velocity of holes in silicon for applied fields of 15, 25, 50, 75 and         |

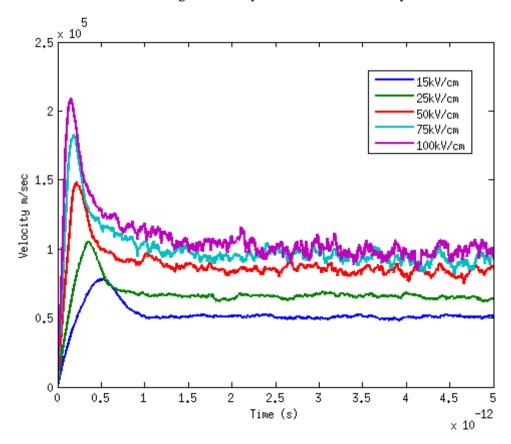

| 100kV/cm showing the velocity overshoot and the steady state                                                |

| Figure 3.18 - Transient energy of hole in silicon for applied fields of 15, 25, 50, 75 and 100kV/cm 58      |

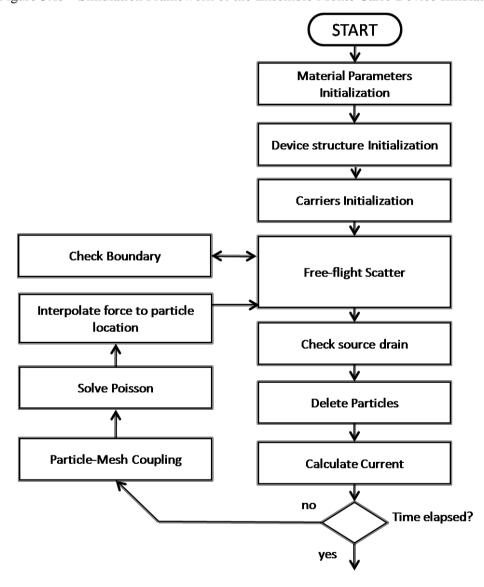

| Figure 3.19 - Simulation Framework of the Ensemble Monte Carlo Device simulator                             |

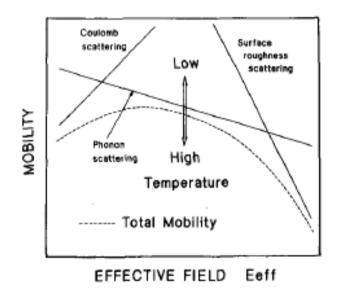

| Figure 3.20 - Mobility versus transversal electrical field in silicon                                       |

| Figure 3.21 - Charge balance in the contacts. 62                                                            |

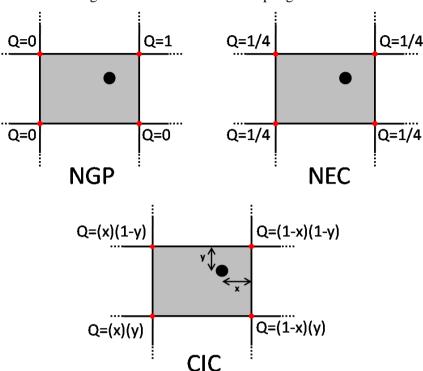

| Figure 3.22 - Particle-mesh coupling methods                                                                |

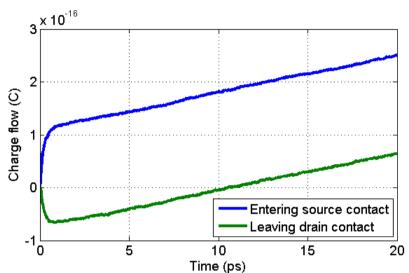

| Figure 3.23 - Simulation results for a 60nm PMOS presenting charge conservation in the device 64            |

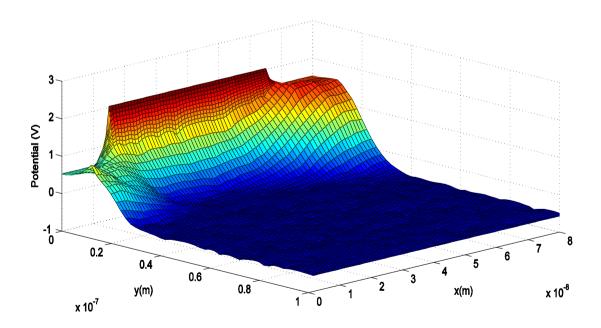

| Figure 3.24 - Potential on a xy cross section of the device                                                 |

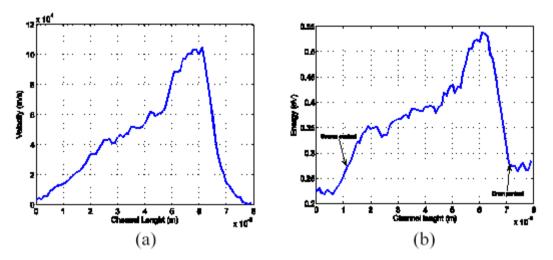

| Figure 3.25- Behavior of the carrier's velocity (a) and energy (b) along the channel length 65              |

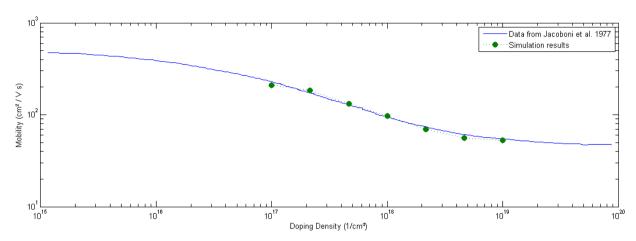

| Figure 3.26 - Comparison of the mobility between a resistor simulated with the EMC device simulator         |

| and experimental data from Jacoboni (1977)                                                                  |

| Figure 3.27 - Comparison of a PMOSFET transistor simulated with the EMC device simulator and the            |

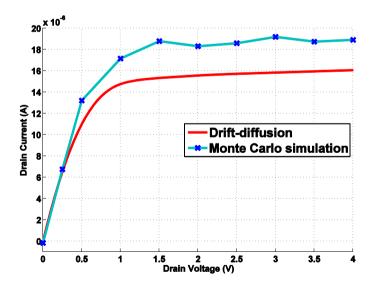

| Drift-Diffusion tool from Silvaco                                                                           |

## LIST OF TABLES

| Table 2.1- Summary of the 7 stage RO analysis.                                                       | 22 |

|------------------------------------------------------------------------------------------------------|----|

| Table 2.2-Delay distributions characteristics for the three studied Paths for different stress times | 30 |

|                                                                                                      |    |

| Table 3.1- Example of a scattering table for Heavy-hole Band                                         | 51 |

#### LIST OF ABREVIATIONS AND ACRONYMS

ASIC Application Specific Integrated Circuit

ASU Arizona State University

BSIM Berkeley Short-Channel IGFET Model

BTI Bias Temperature Instability

CAD Computed Aided Design

CDF Cumulative Distribution Function

CIC Cloud In Cell

CLT Central Limit Theorem

CMOS Complementary Metal-Oxide-Semiconductor

DC Direct Current

EMC Ensemble Monte Carlo

LER Line Edge Roughness

NBTI Negative Bias Temperature Instability

NEC Nearest Element Center

NGP Nearest Grid Point

NMOS Negative Metal Oxide Semiconductor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

PBTI Positive Bias Temperature Instability

PDF Probability Density Function

PMOS Positive Metal Oxide Semiconductor

PTM Predictive Technology Model

PVT Process, Voltage and Temperature

RDF Random Dopant Fluctuation

RO Ring Oscillator

RTN Random Telegraph Noise

RTS Random Telegraph Signal

SIP Strong Implicit Method

SPICE Simulation Program With Integrated Circuit Emphasis

SRAM Static Random Access Memory

STA Static Timing Analysis

SSTA Statistical Static Timing Analysis

TCAD Technology Computed Aided Design

# TABLE OF CONTENTS

| 1 INTRODUCTION                        | 11                 |

|---------------------------------------|--------------------|

| 2 TRAP KINETICS ON TRANSIENT CIRC     | CUIT SIMULATIONS13 |

| 2.1 Trap Kinetics Model               | 14                 |

| 2.2 Simulation Framework              | 16                 |

| 2.3 Case Studies                      | 19                 |

| 2.3.1 Ring Oscillators                | 20                 |

| 2.3.2 SRAM                            | 23                 |

| 2.3.3 Combinational Circuits and SSTA | 25                 |

| 2.4 Conclusions                       | 34                 |

| 3 MONTE CARLO SIMULATIONS ON PM       | 10SFETS35          |

| 3.1 Bulk Monte Carlo                  | 40                 |

| 3.1.1 Initial Condition               | 42                 |

| 3.1.2 Scattering Rates                | 43                 |

| 3.1.3 Scattering Tables               | 50                 |

| 3.1.4 Free flight                     | 51                 |

| 3.1.5 Scattering Events               | 55                 |

| 3.1.6 Bulk Simulation Results         | 55                 |

| 3.2 Device Simulation                 | 58                 |

| 3.2.1 Results                         | 63                 |

| 3.4 Conclusions                       | 67                 |

| 4 CONCLUSIONS                         | 68                 |

| DEEEDENCES                            | 60                 |

#### 1 INTRODUCTION

Charge trapping and de-trapping at localized states at the interface or in the gate dielectric is a significant reliability issue in state of the art CMOS applications (VAIDYANATHAN, 2012). It is known to be a source of low-frequency noise, and also considerably contributes to the Bias Temperature Instability (BTI). These localized states are known as traps. Trapping and de-trapping are stochastic events, and a trap may be either populated or empty. A trap becomes populated when capturing a charge carrier and becomes empty after emitting it. These capture and emission events dynamically impact the electrical parameters of the transistor, generating time dependent reliability issues at the circuit level (KACZER, 2010).

According to the characteristics of each trap, it may impact the MOSFET in a different way (TOLEDANO-LUQUE, 2012). If a trap is more likely to capture a carrier than to emit it, this trap will tend to remain occupied, producing an aging effect. BTI is an aging phenomenon attributed to this trap activity effect (GRASSER, 2011). On the other hand, a trap which is equally likely to capture and to emit carriers will likely change its state frequently generating a noise effect. This effect is known as Random Telegraph Signal (RTS) or Random Telegraph Noise (RTN).

In a MOSFET device, a carrier might be trapped at the Si/SiO<sub>2</sub> interface or deeper into the gate dielectric. To first order, the impact of a trapped carrier on the electrical behavior of the transistor is inversely proportional to the channel area regardless of its position. The miniaturization of the transistor's channel, hence, leads to an increase of the relevance of charge trapping and de-trapping phenomena. Furthermore, Random Dopant Fluctuations (RDF) will induce percolation paths, further increasing the impact of a single trap and leading to variability issues in circuit electrical response (GERRER, 2014). Another trend is the increase of the nominal threshold voltage and/or the decrease of the operation voltage, aiming to reduce the power consumption. When combining these effects, the increase of the impact of trap activity on transistor variability becomes evident, leading to serious circuit reliability issues. Atomistic (TCAD) simulation results show that the impact of a single trap on a 45nm channel length NMOS transistor might cause an increase as high as 16% on the device threshold voltage (ASHRAF, 2011). This kind of simulation, however, cannot be used to study the traps impact in circuits with more than a couple of transistor due to its computational cost.

Aiming to better evaluate the impact of traps in the circuit level and aid designers to cope with effects related to the trap activity, a simulation tool capable of simulating the trap

kinetics and of estimating its impact on transient electrical simulations was developed. Chapter 2 of this thesis further motivates the need of such a simulation tool comparing to others in the literature. The model used and the simulation framework are meticulously described and case studies show the wide range of applications in which it can be used. Each case study is presented providing insights on how the trap activity affects different circuit types.

Chapter 3 changes the focus from the circuit level to the device level. In this chapter it is presented an Ensemble Monte Carlo device simulation tool which was developed for PMOS transistor. Details of the implementation of the code are provided beginning from the scattering probabilities calculation and the bulk simulation to the device simulation. Results showing that it conforms to results from commercial tools are also presented. The Ensemble Monte Carlo device code is then used to evaluate the impact charges trapped in the dielectric or in the Si/SiO<sub>2</sub> cause in the behavior of the device. Chapter 4 discusses the results achieved in this thesis and presents future works that may be obtained with the two simulation tools developed and presented here.

#### 2 TRAP KINETICS ON TRANSIENT CIRCUIT SIMULATIONS

As RTN has become a critical effect for circuit reliability, its impact on circuits has been widely investigated. Traditionally RTN was evaluated only in the frequency domain, therefore the circuit analysis techniques to evaluate the RTN impact on circuits were developed based on frequency domain analysis (LEYRIS, 2007). For digital and low power applications, however, it is of most interest to make studies in the time-domain (YE, 2010), but up until now there are still no commercial SPICE tools available that allow this type of simulation.

Recently many authors presented simulation methodologies capable to simulate RTN effect on transient SPICE analysis thus allowing the investigation of its impact at the circuit level. A cyclo-stationary simulation method for RTN was first presented by Van Der Wel (2003) and further developed by Kolhatkar (2005) and Wirth (2010) and (2012). Other simulation methodologies were developed at the electrical level (SPICE level). These methodologies are based on i) equivalent electrical models for each trap (REISINGER, 2012) and (YE, 2010), where trap behavior is modeled by equivalent circuits; or ii) by evaluating the trap activity outside the electrical simulation tool in a single simulation as in (TANG, 2010) and in MUSTARD, or in multiple simulations as in SAMURAI, (AADITHYA, 2013) aiming to consider the bias dependency.

The goal of this kind of simulation is to obtain a reliable result for circuit simulations considering the trap activity on transient simulations. A cyclo-stationary simulator can be used to perform case studies on specific circuits that might give insights to designers in order to develop newer, more reliable design techniques, and also to evaluate the traps impact on small critical blocks widely used on designs such as SRAM cells, ring oscillators and analog blocks. Another possible use of this kind of simulations is to provide a golden simulation result for the development of more computing efficient CAD tools that would be used during the design of large real circuits, such SSTA tools.

The previous methodologies presented in the literature are either not accurate enough because they do not support models which depend on the bias conditions or are not computationally efficient, becoming unviable to run Monte Carlo simulations on realistic circuits under usual switching conditions. The existing methodologies also were focused on considering just RTN neglecting other effects caused by the trap activity, such as BTI.

This chapter presents in depth a circuit simulation methodology capable of performing workload dependent trap simulations in the time-domain on arbitrary circuit designs under arbitrary bias conditions. It is thus capable to evaluate the effects caused by the traps, such as

BTI and RTN, at the circuit level. As many studies on the trap kinetics and its impact on transistors are still being made, many new models and enhancements to previous models, which may be more suitable for different technology nodes, are still being developed. On this kind of simulation, the complexity of the model is tightly attached to the computational cost of the simulation. The methodology presented in this manuscript was developed so that the model used by the simulation tool can be easily changed, thus allowing the user to choose the model that best fits their needs.

This chapter first presents the model of trap kinetics which is used in the case studies, then the simulation tool developed is presented and case studies on a ring oscillator, on a SRAM cell and a comparison with commercial SSTA tools on combinational circuits are presented and discussed. Finally, a conclusion section is presented summarizing the main contributions of this work.

#### 2.1 Trap Kinetics Model

Oxide and interface traps capture and emit charge carriers responsible for the drain current of the MOSFET. When a trap captures a charge carrier, the drain current is affected due to the electrostatic effect, which leads to reduction in number of carriers in the channel and also affects mobility. This is here modeled as a V<sub>th</sub> fluctuation.

For a constant bias condition i.e., in a steady state condition, the traps whose energy level is close to the Fermi level will present larger activity. By changing the transistor's bias point, the difference between the trap's energy level and the Fermi level is also changed, thus changing the occupation probability of the trap (GRASSER, 2012). Responding to this change, the traps tend to change their states, adapting to the new occupation probability. However, this change is not instantaneous, but a function of the time constants of each trap. The same model can be used to describe the charge trapping activity, both for steady state (DC) condition as well as for arbitrary bias conditions (GRASSER, 2010).

Capture and emission of a charge carrier by a trap is modeled as a Poisson processes with rates  $\tau_c$  and  $\tau_e$ . State 1 stands for the populated trap, while state 0 stands for the empty trap.  $\tau_c$  and  $\tau_e$  are then the average residence times in states 0 and 1 in a steady state condition, respectively (MACHLUP, 1954).

Equations (2.1) and (2.2) shown the probability of a particular trap to change its state after an elapsed time  $\Delta t$  (WIRTH, 2011).

$$P_{01}(\Delta t) = \left[1 - \exp\left(\frac{-\Delta t}{\tau_{eq}}\right)\right] \cdot \frac{\tau_{e}}{(\tau_{c} + \tau_{e})}$$

(2.1)

$$P_{10}(\Delta t) = \left[1 - \exp\left(\frac{-\Delta t}{\tau_{eq}}\right)\right] \cdot \frac{\tau_c}{(\tau_c + \tau_e)}$$

(2.2)

Where  $1/\tau_{eq} = 1/\tau_c + 1/\tau_e$ .

The equations (2.1) and (2.2) can be summarized into equation (2.3). The bias point condition and the process are included in the time constant parameter. For our circuit simulation in the time domain, Eq. (2.3) is defined as the time step of the simulation, 'p' is the process, either capture ('c') or emission ('e'), 'p\*' is the complimentary process, 'v' is the bias condition on that given instant of time and is the trap time constant.

$$P_{p,v} = \frac{\tau_{p^*,v}}{\tau_{e,v} + \tau_{c,v}} \left\{ 1 - exp \left[ -\left(\frac{1}{\tau_{e,v}} + \frac{1}{\tau_{c,v}}\right) \Delta t \right] \right\}$$

(2.3)

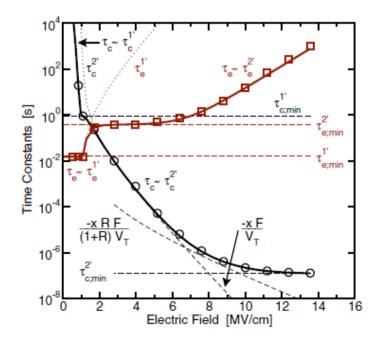

These equations apply to any bias condition. However, as depicted by Figure 2.1, the time constants are a function of the bias point. This dependency is included in the model by a numerical fitting algorithm which aims at finding the correct value of the time constants for a given bias point from known time constants defined for a known bias point.

Source: (GRASSER, 2010)

For the emission time, the simulator is fed with two parameters,  $\tau_{e;min}^{1\prime}$  and  $\tau_{e;min}^{2\prime}$ , which are defined in (GRASSER, 2010). The emission time used during the simulations is given by equation (2.4). For the capture time, the simulator is fed with the capture time for two different gate voltages in the range of operation of the device. Using a linear approximation on the log-scale, the capture time of this given trap is calculated for the other gate voltages. The linear approximation presented to be satisfactory for electric fields in the range of 1-6MV/cm as shown in Figure 2.1. For a more accurate, but more computing cost simulation, the voltage dependency model can be changed to follow the model presented in (GRASSER, 2010).

$$\tau_{e} = \begin{cases} \tau_{e;\min}^{1\prime} & V_{g} \leq V_{T} \\ \tau_{e;\min}^{2\prime} & V_{g} > V_{T} \end{cases}$$

(2.4)

#### 2.2 Simulation Framework

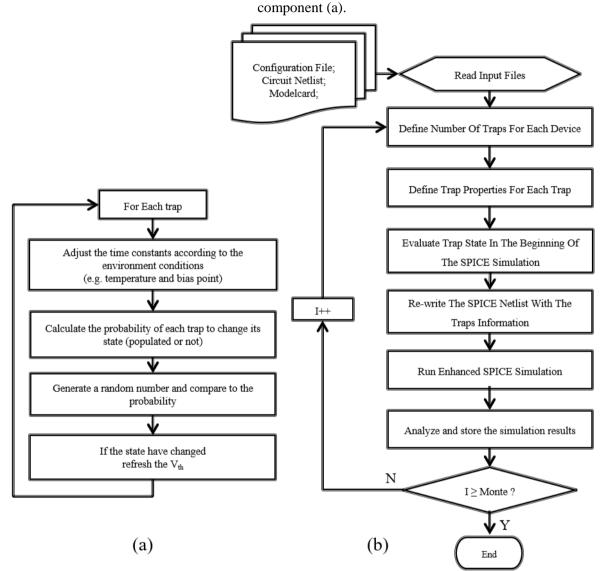

This section presents the simulator framework developed and used in this study. Because not only the charge trapping kinetics are a stochastic phenomenon, but also the number of traps and their properties are described as random variables, the simulation framework is decomposed into two different levels. One level evaluates the trap activity during the electrical simulation and the other one controls the simulation flow externally.

In order to include the impact of the trap activity into the electrical simulator, the transistor model used in the simulations was enhanced by adding the trap kinetics equations presented on section 2.1. This enhancement was performed by creating a Verilog-A component which contains the BSIM4 description. The Verilog-A standard provides a flexible way to model devices and integrate new models into electrical simulations (CHALKIADAKI, 2012).

All the information regarding the trap properties for a given technology are included in a configuration file. This file also contains the information about the running options, such as the number of runs of a Monte Carlo Simulation; and analysis options, such as if time zero variability is to be considered in the analysis.

The input parameters for each instance of the Verilog-A component are: i) number of traps for each transistor in the circuit; ii) the time constants for each trap; iii) the impact of each trap on the threshold voltage (when populated); iv) the parameters that define the dependence of capture and emission probability on temperature and bias point, for each trap; and v) the initial state of each trap. All these parameters are defined by the control script based on the configuration file information. The values of the parameters are defined for each instance prior to each electrical simulation.

Once that every instance has all of its parameters defined, the electrical simulation is performed. At each time step of the transient simulation, equation (2.3) is used to evaluate the probability of the trap to change its state. Based on this information the trap's next state is randomly defined. For each populated trap, its impact on Vth is added to the threshold voltage parameter of the transistor model.

The impact on  $V_{th}$  caused by each trap is considered to be a constant value independent of bias and temperature. Even though recent studies show that the trap's impact on  $V_{th}$  can have dependency on bias (FRANCO, 2012), this is not a strong one and has a negligible impact during the on-state conditions. There is still no conclusive study detailing this dependency nor models capable of describing it. The methodology is capable of considering this dependency by adding models in the Verilog-A model (as done to include the bias dependency of time constants).

The time constants used in equation (2.3), however, are a function of environmental variables such as the electrical field at the Si/SiO<sub>2</sub> interface as discussed for instance in (GRASSER, 2010). To include these dependencies, during each step, prior to evaluate the next state of the trap the time constants are adjusted numerically, as presented in section 2.1, based on the environmental parameters of each device and the conditions at which the trap was characterized. For a more precise consideration of these dependencies, one might also use the equations (15) and (16) presented in (GRASSER, 2010). A summary of this flow is presented on Figure 2.2(a).

By performing an electrical simulation using the Verilog-A component, it is possible to simulate a given circuit with pre-defined traps considering the trap activity during the transient simulation. Aiming to improve the simulation process, a control script was written. Based on a configuration file that contains the information about the probability density functions of the trap related parameters and on the netlist of the studied circuit, this control script writes a new netlist changing the MOSFETs devices by the Verilog-A component and adding, to each instance of this component, its parameters (number of traps, time constants, and so on).

The control script starts by reading the configuration file and the netlist of the circuit of interest. For each Monte Carlo run, the control script defines the number of traps for each Verilog-A component in the circuit. For each MOSFET, the number of traps is randomly chosen according to a Poisson distribution as shown in (KEYES, 1975). The parameters of this distribution are defined in the configuration file and are adjusted based on the design parameters of each given component, such as its channel area (WIRTH, 2012). During this stage the control

script also writes the experimental characterization information related to the traps, which is also found in the configuration file, into every instance of the Verilog-A component.

Figure 2.2- High level simulation framework (b) including the detail of the Trap kinetics on Verilog-A

Once the number of traps on each MOSFET is defined, the control script defines the impact of the trap on the threshold voltage ( $\Delta V_{th}$ ) and the time constants ( $\tau_c$  and  $\tau_e$ ). Both parameters are random variables where the first is shown to be described by an exponential distribution with average  $\eta$ , where  $\eta$  scales with the device properties as presented in (KACZER, 2010). For simplicity the time constants are described by uniform distributions in a logarithmic scale. In general, a more accurate bi-variate Gaussian distribution can be used (BINA, 2012). Studies show that there is no correlation between the step-height and the time constants of each trap (KACZER, 2010). The definitions of these parameters for each trap are randomly chosen according to the statistical distribution of each random variable. The

distributions and their properties are defined in the configuration file and are adjusted for each transistor based on its design dependent parameters, such as the channel area.

After all trap related information of each device in the design is defined, it is possible to run an electrical simulation which will consider the trap kinetics. Since all the equations were added to the transistor models and not to the simulation tool, any commercial tool that supports the Verilog-A standard is able to perform the simulation. Post simulation scripts aiming to analyze the results may be added after the electrical simulation to avoid losing information as other electrical simulations run in the same Monte Carlo loop.

The same trap kinetics mechanisms can be used to simulate BTI effects. Because BTI is an aging effect we are interested in evaluating its impact after a given time of operation, that may be in the range of years, and no longer in short time as we did for RTN. It is, however, impracticable to run transient electrical simulations in the range of years.

Aiming to allow users to simulate BTI effects, we implemented an analytical function capable of predicting the trap state after a certain period of time under a predefined stress condition. This way the user may describe the stress signal by its voltage, frequency and duty cycle, and define the duration of this stress condition. This function will, thus, evaluate the state of each trap for the stress condition defined and will feed the electrical simulator which will use these as its initial condition. The analytical solution is based on the trap kinetics equations presented on section 2.1. A method of predicting the trap state after an arbitrary stress time under known conditions is presented in (TOLEDANO-LUQUE, 2011-a).

In contrast to the method that evaluates the trap activity on a transient SPICE simulation, the analytical method presented in (TOLEDANO-LUQUE, 2011-a) is not capable to consider the impact that degraded devices have on the other devices surrounding it. A circuit with degraded devices produces slightly different waveforms which will be the stress signals for other circuits, for the case of a logic gate the rise and fall times will change, also changing how the next stage is stressed. A comparison between the two methods was performed, validating the methodology of (TOLEDANO-LUQUE, 2011-a) for long stress times where the BTI phenomena dominates, for short periods of time, where RTN dominates, the correlation between the impact of traps is more significant and thus the enhanced SPICE simulation considering the trap kinetics should be used.

#### 2.3 Case Studies

Aiming to better illustrate the behavior of the simulation tool and its capabilities as to study circuits of interest for designers, some case studies were performed and are presented here. For all case studies the test circuit was designed on a 45nm CMOS technology. A PTM 45nm model card for high-performance applications was used for the SPICE simulation (ZHAO, 2006). The trap properties used in the simulation are described in detail in (TOLEDANO-LUQUE, 2011-b). Since trap related properties (as for instance number of traps on each device) are random variables, a statistical analysis method is mandatory.

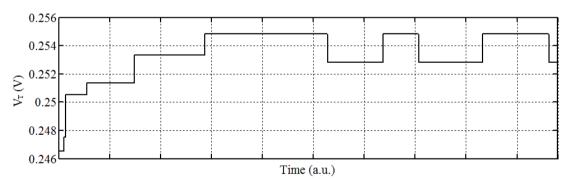

## 2.3.1 Ring Oscillators

For an initial study, a transient simulation was run and the  $V_{th}$  of a PMOS transistor was measured right after the transistor started to be stressed. The result is plotted on Figure 2.3. In this figure the trap activity and its impact on  $V_{th}$  are clearly seen. As each trap causes a particular impact on  $V_{th}$  it is possible to identify each trap and when it changed its state. The increase of  $V_{th}$  in time is caused by the BTI effect. In this figure it is possible to identify four traps responsible for causing the BTI effect. It is also possible to see one trap responsible for the RTN effect as it suffers both capture and emission events three times on this simulation.

Figure 2.3- Trap activity impact on the threshold voltage of a PMOS transistor in time where both BTI and RTN effects are present.

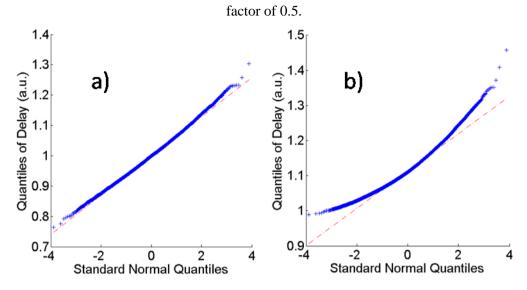

As next step towards a ring oscillator we performed a simulation on an inverter chain. The inverters used were sized with  $w_p$ =135nm and  $w_n$ =90nm and L=50nm. A Monte Carlo simulation with 10000 samples was then run and the delay of a given inverter in the center of the chain was analyzed. For this case study we considered not only the trap activity but also the time zero variability. The time zero variability in the transistors occurs due to effects such as Random Dopant Fluctuation (RDF) and Line Edge Roughness (LER) and, in this work, was modeled as a Normal distribution of the threshold voltage with the standard deviation equal to 10% of the mean (CARTHIGNOL, 2008).

Figure 2.4- a) QQ-plot of the delay of an inverter considering the time zero variability and b) considering also the trap activity after 1000s of stress on nominal operating voltage (0.8V) and duty

Figure 2.4 shows the results obtained from these simulations. In a) the delay of the inverter only considering the time zero variability is shown, while b) shows the delay considering also the trap activity in the simulation. Comparing both figures we see not only the increase of the delay of the test inverters due to BTI but also that the right side tail obtained in the simulation considering the trap activity decreases much more smoothly. It is important to notice that the tail of the delay distribution is of high importance since it is in that region where circuits that fail to meet the constraints are located.

Ring oscillators are simple digital structures traditionally used as the base structure for voltage controlled oscillators and for test structures aiming at the extraction of basic parameters of the technology. The inverters used in the ring oscillator simulated were sized with  $w_p$ =135nm and  $w_n$ =90nm and L=50nm.

The ring oscillator was submitted to a series of Monte Carlo analyses under different conditions. In each of these 1000 transient simulations were performed, using the enhanced electrical simulator presented on section 2.2. On each simulation, the period of the first 100 cycles was measured. The standard deviation of the period on each simulation was considered to be the signal cycle to cycle jitter, or just jitter.

First, we evaluated the impact RTN on the ring oscillator's jitter through a comparison between the initial impact of the RTN traps, and the impact of the RTN traps after 10<sup>4</sup>s of activity. These simulations were performed both with and without considering the time zero variability. It was then performed a new set of simulations increasing the operation voltage

(Vdd) in order to adjust the oscillation period. All the simulations were performed under the conditions described above. The results are summarized at Table 1.

Table 2.1- Summary of the 7 stage RO analysis.

|                             | Vdd  | Time     | Avg. Period | Avg. Jitter |

|-----------------------------|------|----------|-------------|-------------|

| No Time Zero<br>Variability | 0.8  | 0s       | 0.37360ns   | 4.6665ps    |

|                             | 0.8  | $10^4$ s | 0.40492ns   | 5.6084ps    |

|                             | 0.83 | $10^4$ s | 0.37692ns   | 4.6822ps    |

| Time Zero<br>Variability    | 0.8  | 0s       | 0.37608ns   | 5.0754ps    |

|                             | 0.8  | $10^4$ s | 0.40767ns   | 6.0284ps    |

|                             | 0.83 | $10^4$ s | 0.37797ns   | 4.8370ps    |

The results presented on Table 2.1 show that the jitter caused by the traps cannot be neglected with its average reaching a variation larger than 1.25% of the period of the signal. When including the long-term BTI effects caused by the traps in the simulation after 10<sup>4</sup>s of operation, we obtained an increase of 8.5% in the average period and of 18.8% in the average jitter over all the measured samples with time variability included.

The increase in the period is a natural cause of the increase of the  $V_{th}$  caused by the BTI effect. As the impact of each trap is also modeled as an increase on the  $V_{th}$  and, according to basic transistor models, it has a crescent impact on the drain current as it gets larger. The increase on the jitter is caused mainly by this increase of the impact of each trap in the transistor's drain current, which is occurs due to the increase on the  $V_{th}$  caused by the BTI. An increase of 0.3V in the operation voltage was needed to compensate the impact of the BTI on the RO. The increase in the operation voltage also reduced the jitter as it also decreased the impact of each trap in the transistor's drain current.

1.06

1.06 1.08

Period (a.u.)

1.10

1.12

1.02

1.04

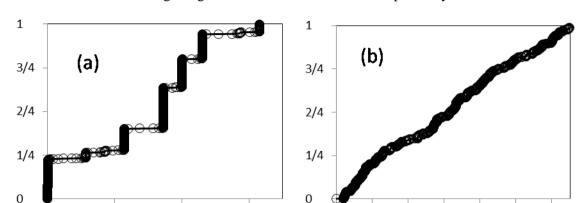

Figure 2.5- Cumulative Density Function of 1000 periods of a (a) 3-stage ring oscillator and (b) of a 7-stage ring oscillator under the effect of trap activity.

Figure 2.5(a) shows the cumulative distribution function (CDF) of oscillation period, measured in the simulation of 1000 successive cycles of a 3-stage ring oscillator with the same size as the test circuit. This simulation was performed considering that the transistors were already stressed by 10<sup>-4</sup>s in the ring oscillator with a duty factor of 0.5. In this figure it is clearly seen that a few traps dominate the behavior, with clear discrete steps in the CDF. This happens because the cause of the jitter in this simulation is the trap activity which varies between discrete levels characterizing the RTN effect. For larger ring oscillators, i.e. ring oscillators formed by larger transistors or with a higher number of stages, this step like distribution is not as clearly noticed due to the increase of the number of traps affecting the signal period as the decrease of the impact of each trap. This case is shown in Figure 2.5(b) where the studied circuit was a 7-stage ring oscillator.

### 2.3.2 SRAM

1.00

1.02

Period (a.u.)

1.04

A case study consisting of a simulation of the  $V_{min}$  in a SRAM cell during the stand by condition under the effect of trap activity was performed. Both the PMOS and NMOS core transistors were sized with (W/L)=(65nm/45nm) and the NMOS pass transistor were sized with (W/L)=(90nm/45nm). The  $V_{min}$  was considered the minimum supply voltage at which the design has a positive Read Noise Margin.

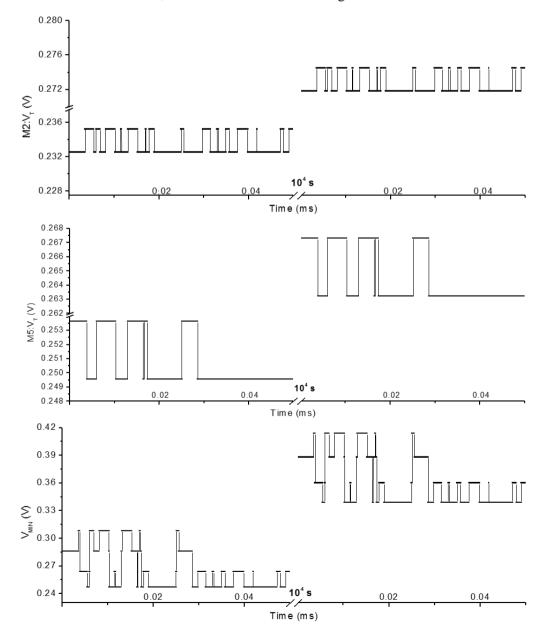

Figure 2.6 shows the  $V_{min}$  of a SRAM cell in a transient simulation. The transient simulation was run for two different BTI stress times. The first simulation is for a BTI stress of  $100\mu s$ , and the second simulation corresponds to a stress time of 10ks. Due to the small number of traps in the devices and the constant bias, RTN trap activity was detected only on a PMOS

core transistor (M2) and on a NMOS core transistor (M5) during the transient simulation, each of these transistors showing a single RTN trap. From the BTI stress time of  $100\mu s$  to 10ks, the duty cycle on the memory was 0.5, leading to a  $V_{th}$  shift due to BTI in transistor M2 of 25.7mV and of 9.96mV in M5. The duty cycle of 0.5 was chosen to avoid degrading some transistors of the cell much more than others which would generate an unbalance leading to a much larger  $V_{min}$ .

Figure 2.6- Threshold voltage as a function of time for the transistors M2 and M5 of the 6T-SRAM case study cell and how these impact SRAM  $V_{min}$ . The right hand side depicts the values after an elapsed time of  $10^4$  s (indicated by the break of  $10^4$  s shown in the time axis). During this time the cell suffered BTI, as seen in the threshold voltages and SRAM  $V_{min}$ .

To allow easy comparison between the BTI stress conditions, the same seed was chosen for the random number generator in the RTN trap simulation for both cases. In other words, RTN activity is the same in both simulations.

Comparing the  $V_{min}$  of the SRAM cell with the trap activity seen in the transistor's  $V_{th}$ , we can see that the trap activity translates its impact to the  $V_{min}$  parameter. Experimental data showing the impact of RTN on SRAM reliability is shown in (AGOSTINELLI, 2005), (TAKEUCHI, 2010), (TAKEUCHI, 2011) and (YAMAOKA, 2011). This effect is very relevant for the test of SRAM cells as it shows that a cell tested working for a given  $V_{min}$  condition might not be reliably working for the same condition after just a few instants later due to the trap activity. It is possible to see that both BTI and RTN traps have an important impact on the cell's  $V_{min}$ .

#### 2.3.3 Combinational Circuits and SSTA

The Standard cell methodology is a method widely used for designing the digital functionalities of ASICs. The Standard cell design flow consists of creating, for instance, through the full custom method, a library containing a certain number of cells with the same height so that they can be placed one next to the other in order to form a more complex circuit. Based on these cells the designer translates a high level circuit description into a logic gate level description of the circuit limited by the cells present in the library. Once the designer has the circuit described in the logic gates level, he places the cells into a predefined grid and route the connections among them. During the entire process the designer is aided by CAD tools. One of these tools is the Static Timing Analysis (STA), which is the one responsible to verify after each step if the time constraints are still being accomplished (RABAEY, 2003).

The principle of the STA tool is to sum the delay of each cell and connection in a path (usually the critical path) of the circuit according to its position in the path. To that end each cell is characterized by its delay for different input signals with different fan-outs. This is done for different PVT (Process, Voltage and Temperature) corners. As the design advances from the circuit description to the placement and to the routing, the STA result becomes progressively more precise.

The advances in device technologies lead to transistors that are faster, cheaper, and/or with less power consuming. To convert these gains to the circuit level and finally to the system level, cells containing these devices are designed, characterized and ultimately used as the base for complex high level designs.

The downscale of the transistors present in the new technologies, together with physical limitations during the process stage, leads to new challenges that must be taken in account during the design stage. Among the main challenges there are the increase of the relative variability of the transistor physical dimensions, Line Edge Roughness (LER), effects created by the discreteness of charge and matter such as Random Dopant Fluctuation (RDF). All these sources of physical variability convert to variability in the electrical characteristics of the transistor and propagate to the higher levels of the design (ASENOV, 2003).

The traditional corner analysis, which consisted of selecting the worst and the best case scenarios for characterizing the cells, is not anymore able to reproduce well the high variability generated by the process of the transistors, leading to over-pessimistic designs. As the distributions become wider, in some circumstances it may be advantageous to sacrifice yield to gain in performance. To solve this problem during the design flow the STA tools were improved so that they could be able to deal with these issues and started to be called Statistical STA tools, or just SSTA.

The SSTA tools, together with its compatible characterization tool, analyze the circuit considering the parameters variability as distributions through statistical methods, such as linear sensitivity analysis (SILICON, 2007), (SILICON, 2008). They make a prediction of the probability density function of the electrical performance of the cell.

Because aging effects were not in the past considered to be stochastic, the design of the SSTA tools was originally done to consider only process variations at the starting time. These process variations are usually described following Normal distributions in parameters such as the threshold voltage and the transcondutance. This way the linear sensitivity analysis method presents a satisfactory response.

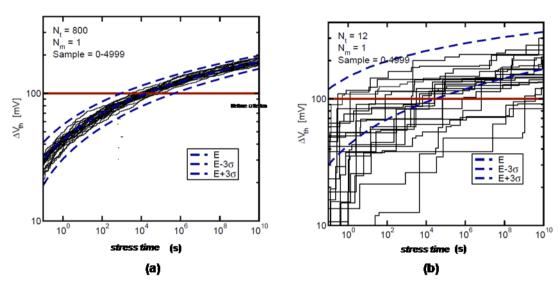

Bias Temperature Instability (BTI) is a critical reliability mechanism that affects device electrical parameters such as the threshold voltage (SCHRODER, 2003). It is caused by charging of defects in the gate oxide. In large devices of older CMOS technologies, BTI was considered to be a deterministic effect for a given circuit and stress condition. New, "atomistic" studies show that the BTI degradation (aging) in state-of-the-art technologies based on deeply-scaled transistors will lead to a huge increase in time-dependent variability (KACZER, 2010). This trend is illustrated in Figure 2.7, discussed in detail in the next section.

Figure 2.7- (a) The random properties of many defects N in large devices average out, resulting in a well-defined lifetime while (b) the stochastic nature of a handful of defects in deeply-scaled devices becomes apparent.

Source: (KACZER, 2010)

In the literature it is possible to find suggestions of how to include the Bias Temperature Instability and other aging effects in the (S)STA tools including works from (SANGWOO, 2010), (WANG, 2010), (WENPING, 2007) and (KUMAR, 2007).

We, however, could not find any commercial tool that is already using any of the approaches suggested in the literature. Due to this, in order to consider aging effects in the (S)STA tools available in the market, a 'time' corner is defined for the desired live expectancy of the circuit and the characterization is performed for each aged cell.

This case study presents a characterization method for the linear sensitivity analysis based SSTA tools and compare those with the result obtained with the simulation tool presented in this chapter. In order to compare the precision of the SSTA simulation method to evaluate the BTI phenomena on circuits we first characterized a standard cell library. The library chosen was the Nangate Open Cell Library for 45nm technology node used together with a PTM model for 45nm (ZAHO, 2006). Both the library and the modelcard were chosen because they are open, allowing anyone to reproduce the same results obtained in this case study.

The linear sensitivity analysis is a method used by the most of the commercial SSTA tools. It is based on a simulation of a circuit with their parameters all at nominal values and one new simulation for each random parameter in the circuit. In each of these simulations one of the random parameters is shifted while the others are kept the same. This way it is possible to see the impact of each parameter in the output of the cell individually (PARRAT, 1961). This

information together with the probability density function (PDF) information of the random parameters leads to an approximation of the PDF of the output. This method assumes the PDF of each parameter as a Normal distribution and a linear dependency between the parameter and the output which is a valid approximation when dealing with process variability issues because they are traditionally modeled by Normal distributions.

Once that the tool has evaluated the delay PDF of each cell it makes a sum of the delay on each stage finding the possible critical paths. Changes in the waveform and power consumption are also evaluated.

In order to characterize the cells to make them compatible to a linear sensitivity analysis based SSTA tool it is needed to obtain not only the Fan-out versus Slope table for the cell with its parameters with nominal values but it is also needed to obtain a new version of this table after changing each random nature parameter in the design. All this information is translated into a Liberty<sup>TM</sup> file which is later used by the SSTA tool.

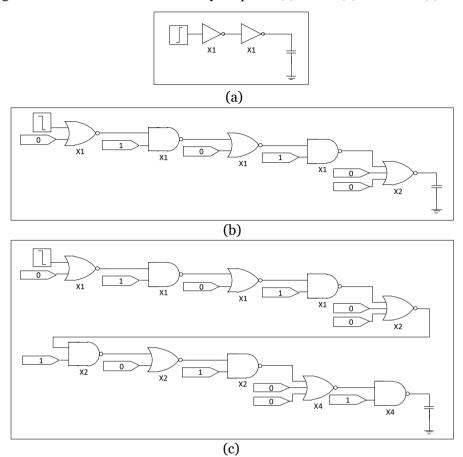

Once the library is properly characterized, we define some case study circuits on which we will compare the SSTA results with the enhanced SPICE ones. In order to study the behavior of circuits with different complexity, we selected three circuits with different logic depth, they are shown in the Figure 2.8. The first one is an inverter, a simple circuit making it easy to see the effect of each trap in the general result. The second circuit is a critical path in a circuit with five logic stages. This circuit was selected because it is a typical path used in a standard cell method and is still small enough making possible to run a Monte Carlo simulation with the enhanced SPICE tool in an acceptable amount of time. The third path is ten logic stages path. This path has the objective to show the behavior of the distributions in comparison with the complexity of the path.

The third step of the process is to obtain the random parameters distribution in a transistor after the amount of time that will be defined in the time corner of the SSTA analysis. This information is used to feed the SSTA tool. In our case we defined this amount of time to be 1s,  $10^4$ s and  $10^8$ s. For the sake of simplicity and to have a result that can be easily interpreted, the only random variable reported on each transistor will be the Vth. In the first analysis only trap dependent variability (BTI) will be considered, on further analysis the time zero variability will be also included.

Figure 2.8- The schematic of the analyzed paths. (a) Path1, (b) Path2 and (c) Path3.

Once the mean and the standard deviation of the random parameters of the circuit are known it's possible to run the linear sensitivity analysis based SSTA and the enhanced SPICE simulation for the same circuits defined previously. The electrical simulations were performed using the Monte Carlo method with 1000 runs.

Figure 2.9 compares the delay obtained by the enhanced electrical simulation to the delay obtained by the SSTA method presented before, after a stress time of 10<sup>4</sup> seconds. The delay is normalized by its mean value. The result obtained by the SSTA method is a normal distribution, and hence represented by the dashed lines (straight lines) in the Q-Q plots. It is important to pay attention to the tails of the distribution, where the failing circuits are located. The Q-Q plot format helps detailing the tails of the distributions.

Looking at the tails one can see a significant difference between both methods for the case study with less complex paths, while for the more complex paths the error is less severe.

Table 2.2 presents both the Skewness and the Kurtosis of the distributions versus the complexity (measured in logic stages) and the different stress times. The Kurtosis value was chosen because is the most representative value of the weight of the tails of a distribution, while

the Skewness is the measure of the PDF's asymmetry. This table shows a tendency of the delay's PDF to become closer to a Normal distribution as path complexity increases. The accuracy of the SSTA tool to evaluate the chance of a timing violation is correlated to the Normality of the path's delay.

Table 2.2-Delay distributions characteristics for the three studied Paths for different stress times.

|                          | Stress time       | Skewness | Kurtosis |

|--------------------------|-------------------|----------|----------|

| Path 1 (1 Logic Stage)   | 1s                | 1.5094   | 6.3276   |

|                          | $10^4$ s          | 1.1068   | 4.6823   |

|                          | 10 <sup>8</sup> s | 1.2947   | 6.1172   |

| Path 2 (5 Logic Stages)  | 1s                | 0.5641   | 3.4397   |

|                          | $10^{4}$ s        | 0.3751   | 3.3063   |

|                          | 10 <sup>8</sup> s | 0.5394   | 3.2249   |

| Path 3 (10 Logic Stages) | 1s                | 0.4501   | 3.2773   |

|                          | $10^{4}$ s        | 0.5382   | 3.7532   |

|                          | 10 <sup>8</sup> s | 0.3885   | 3.1765   |

Let us focus first on the Figure 2.9 (a), which is the one regarding to the path 1 (a single inverter). That is the case where the error of the SSTA tool is the largest. Since there is just one logic stage, the SSTA tool is given only by the linear sensitivity analysis of that given cell. The linear sensitivity analysis assumes that the input random variables are all given by Normal distributions. In the BTI case, these random variables are the threshold voltage of both the PMOS and NMOS transistors in the gate. Because these random variables are not normally distributed (RAUCH, 2007), they lead to an error in the shape of the distribution. The other important error generated by the linear sensitivity analysis is the fact that it considers the delay as a linear function of the input random variables leading to minor errors both in the mean and the variance of the result distribution. The result presented by the enhanced electrical simulator is considered to be correct since its distribution is automatically generated based on experimental data for the distributions of the trap properties and in first principles.

Figure 2.9- The Q-Q plot of the normalized delay generated by the electrical simulation in comparison with the one generated by the SSTA analysis in the Path 1after  $10^4s$  (a), in Path 2 after  $10^4s$  (b), and in

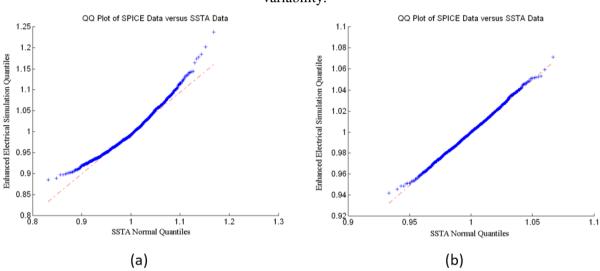

Another series of simulations were run to evaluate the impact of the time zero variability in the study. Time zero variability is usually modeled by adding to the Threshold voltage a Normal distributed variable. The mean of the distribution is zero and the standard deviation is a function of the technology and the area of the transistor. In this case the standard deviation is assumed to be 10% of the threshold voltage for a transistor with the minimal dimensions for the technology (HORSTMANN, 1998). The standard deviation was considered to be inversely proportional to the area of the channel of the transistor.

Figure 2.10- Q-Q plots of the delays on paths 1 (a) and 2 (b) after 10<sup>4</sup>s of stress considering time zero variability.

Figure 2.11- Threshold voltage distribution due to NBTI considering (a), and not considering (b) time zero variability.

The simulation of the delay on path 1 and path 2 after 10<sup>4</sup>s is presented on Figure 10. There it is possible to see a smaller difference between the results obtained by the electrical simulation and by the SSTA method. This happens because the PDF of the threshold voltage becomes the sum of two distributions, one of those is a Normal, making the threshold voltage PDF more Normal like and then more suitable for studies using the linear sensitivity analysis method. Figure 2.11 shows the distribution of the threshold voltage due to NBTI in a transistor considering (a) and not considering (b) the time zero variability.

Despite of the error for path 1, paths 2 and 3 presented a result much closer to the ones obtained by the SSTA method. It is clear an increase in the accuracy of the method with the increase of the complexity of the path being studied. This can be understood if one considers that the Central Limit Theorem (CLT) of the Statistics, which states that "that if  $S_n$  is the sum of n mutually independent random variables, then the distribution function of  $S_n$  is well-approximated by a certain type of continuous function known as a normal density function (GRINSTEAD, 1997). This theorem is applicable to the SSTA case since the total delay is given by the sum of the delays of each stage, which are considered to be mutually independent random variables.

Two other properties of this system of sum of mutually independent random variables are presented in equations (2.5) and (2.6). These properties are valid no matter the shape of the PDF of the random variables.

$$\mu_{S_n} = \sum_{i=1}^n a_i \mu_i \tag{2.5}$$

$$\sigma_{S_n}^2 = \sum_{i=1}^n a_i^2 \sigma_i^2 \tag{2.6}$$

Based on these properties we can tell that for a long path the delay will tend to be Normally distributed with its mean and variance given by the equations (2.5) and (2.6) regardless of the shape of the individual cell delays.

SSTA tools are used for two main reasons, to look for setup time violations and hold time violations. The most probable paths to do these violations are the long paths for the setup time and the short paths for the hold time. BTI effects are responsible foran increase of the threshold voltage which leads to a larger delay in the logical path, changes in the flip-flops parameters and an increase in the variability. The increase of the delay of the logic path increases the probability of a setup time violation and reduces the chance of a hold time

violation. The change in the flip-flop parameters changes with the circuit's topology so we cannot present a general case of the BTI's impact on those. For setup time violation analysis, it is important to consider the critical paths, which are the paths with the largest propagation delays, so usually are the ones with the largest number of logic stages. This way we can assume that when simulating paths to look for setup time these paths are going to fulfill the long path condition.

#### 2.4 Conclusions

A circuit simulation method capable of considering the trap activity during transient electrical simulations was presented. Because it is directly obtained from detailed defect (trap) studies and adjusted with experimental data, this approach leads to an accurate tracking of the trap states during the simulation. This allows the analysis of the impact of trap activity in arbitrary circuits. Because the trap kinetics are included in the transistor model, it is possible to use this method with any electrical simulation tool and it also allows the user to extend this methodology to include other time dependent effects. A case study on a ring oscillator demonstrates the impact of the traps on both jitter and BTI, a case study on a SRAM cell shows how critical the trap activity can be on the reliability of SRAM cells as it affects the V<sub>min</sub> of the cell, and a case study on combinational circuits and SSTA tools shows where these are adequate to use on BTI effects and where they are not reliable. Other case studies performed but not presented here includes (KACZER, 2011) and (RODOPOULUS, 2011).

The overhead in the runtime of the simulation method presented here is slightly larger than a traditional electrical simulation. Overall, this simulation methodology proves to be an efficient tool for analyzing both RTN and BTI. The models used in these simulations, however, are based only experimental data which are very scarce in the literature limiting the conditions to which the simulations can be run. An alternative to experimental data is generating the data using TCAD simulations, but also in this case there are only a few case studies for specific cases and only for n-type transistors. As a step forward to solving this lack of tools in the scientific community, an EMC device simulation tool for modeling p-type transistors was developed as part of this thesis work and is described in the next chapter.

#### 3 MONTE CARLO SIMULATIONS ON PMOSFETS

The previous chapter presented an electric simulation tool which helps to evaluate the impact that the trap activity causes in circuits through transient simulations. The relevance for translating technology characteristics related to the trap activity to circuit level variables used during the design is highlighted in chapter 2. All the simulation tools of this kind, not only the one developed in this thesis, require two inputs. They are: i) the information regarding the circuit to be evaluated and the desired output and ii) the technology information including the trap characteristics for that given technology node.

The trap related characteristics include the probability distributions of their time constants, their impact on the threshold voltage and how these correlate with themselves and with other environmental parameters of the circuit such as the temperature and the electrical field. All these characteristics are usually obtained from experimental data. However, even for simple trap models these are hard to obtain due to the statistical and time dependent nature. This issue becomes an important limitation for using the simulation tools as the ones presented in chapter 2. In the case studies presented in section 2.3, experimental data obtained from IMEC and from other sources in the literature were used, as referenced.

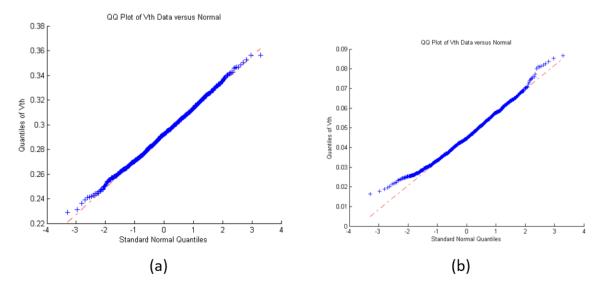

Despite of a limited number of studies, the trap characteristics dependency on the device technology is evident. Considering the trap impact on the device's threshold voltage, for instance, Toledano-Luque (2012) shows two different distributions that define the trap impact comparing the measurements made with traditional devices and with high-k as seen in figure 3.1. Ashraf (2011) shows the changes on the traps impact on the threshold voltage due to halo implantations as seen in figure 3.2. Furthermore, due to the tight relation of the impact of traps with percolation paths in the channel, one can also assume that the impact also depends strongly on the doping profile of the device near the semiconductor-dielectric interface, which is strongly affected by the doping density of the channel and V<sub>th</sub> correction mechanisms. All these dependencies limit the trap characteristics to be valid only for the technology in which it was measured. All simulation tools which have trap characteristics as an input are limited to technologies which the user has access to extract that information by measurements, by simulation or both.

Figure 3.1- (1-CDF) of step heights normalized to the number of tested nFETs after positive stress. Data can be fitted with a bimodal distribution with  $\eta_{IL}=3.7mV$  and  $\eta_{HK}=0.9mV$ . Note that  $\eta_{IL}$  is similar to the  $\eta$  value obtained in pFETs.

Source: (TOLEDANO-LUQUE, 2012)

Figure 3.2- Relationship between the position of the trap along the channel length and the impact that a captured charge causes in the threshold voltage for devices with and without halo.

TCAD tools can be used to obtain the carriers impact on the threshold voltage without the need of performing experiments. Previous works performed at University of Glasgow, including (BUKHORI, 2010), (WANG, 2012), (AMOROSO, 2012), (AMOROSO, 2013) and (AMOROSO, 2014), and works performed at ASU as the one performed by ASHRAF (2011),

show the capability of this kind of tool to evaluate the impact that a charge trapped in the

dielectric has on the device performance. Even though the computational cost of obtaining this information using TCAD tools is high, it gives the user the opportunity to obtain some of the trap characteristics for the device of interest without the need of experimental data, even before manufacturing the device. This may allow optimizing performance and reliability of future technologies. An additional upside of TCAD simulations is that they give to the user access to internal information of the device variables which one cannot access by experiments. This enables detailed studies aimed at further understanding the impact of traps. In ASHRAF study in (2011), for instance, the trap position was swept along the channel providing a better understanding on how the trap impact is as a function of its location.

A prototypical device simulation tool is, traditionally, built by the self-consistent solution of two sets of equations: the transport equations for charge flow and the Maxwell equations for the electromagnetic fields. For low frequency devices the Maxwell equations can be reduced to the Poisson equation shown in Eq. (3.1),

$$\frac{d^2\psi}{dx^2} + \frac{d^2\psi}{dy^2} + \frac{d^2\psi}{dz^2} = -\frac{\rho(x, y, z)}{K_s \varepsilon_0},$$

(3.1)

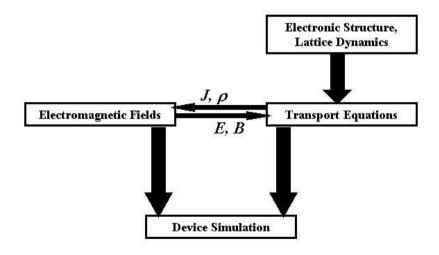

Where  $\psi$  is the electrical potential,  $\rho$  is the free charge density and  $K_s\epsilon_0$  is the material permittivity. Within the semi-classical limits, the equation which defines the carriers transport in a semiconductor is given by the Boltzmann transport equation (BTE). In a device simulation these two equations are self-consistently coupled as shown in Figure 3.3.

Figure 3.3- Device simulator Framework showing the coupling of the transport equations with the Electromagnetic fields calculation.

Source: (VASILESKA, 2010)

As shown previously, the trap impact on the device is highly dependent on the physical structure of the device, so the structure being simulated should be carefully matching the technology of interest. Among the physical characteristics of the device, one that should be highlighted is the doping profile in the active channel area as it is strongly responsible for the generation of percolation paths in the channel region. The percolation paths are generated by the random position of doping atoms in the channel generating a non-uniform potential landscape. To account for the random position of charges in the channel it is important for the TCAD tool used to be atomistic. The percolation path profile generates a randomness in the impact of a trap in a device, allowing a trap in the same channel position in two devices of the same technology to have different impact (ASENOV, 2003).

The trap impact is also known to gain relevance for the smaller devices as a consequence of having a smaller total charge in the gate capacitor. This relation also forces the TCAD tool to be suited for simulation in small devices. When dealing with small devices other effects become relevant, such as the velocity overshoot and the ballistic transport (LUNDSTROM, 2002). The TCAD tool used should be able to take those into account properly.

Figure 3.4 shows a hierarchical map of the methods used to solve the corresponding transport equation in device simulators. Shown on the left side are the semi-classical methods which include the drift-diffusion model, the hydrodynamic model and the Monte Carlo method for direct solution of the Boltzmann transport equation. For completeness, on the right side are shown quantum-mechanical methods for the analysis of ultra-nanoscale devices. It is important to highlight that corrections for quantum effects may be included in the semi-classical approaches. These include quantum mechanical tunneling and quantum-mechanical space quantization effect. When using a TCAD tool which includes a correction model, it is important to remember that in the correction the effect is not described by its physical nature, but emulated by a mathematical model fitted for that given case.

In order to be able to cope with stochastic nature of the trap impact, any analysis demands several samples to generate a reliable result. When choosing the method to solve the transport equation, it is important to weight not only the limitations of each method, but also their computational cost so that a sufficiently large number of simulations can be run. The drift-diffusion and the hydrodynamic models, despite of having a small computational cost, are not capable of taking into account the atomistic nature of the charged carriers and the impurities or the ballistic transport. Methods based on quantum mechanics, on the other hand, are for the most part unnecessarily complex. The Ensemble Monte Carlo device simulation method, in spite of having a high computational cost, is the most accurate among the semi-classical

methods and can be used for 3D device simulations with atomistic dopants on real positions that are randomly defined. The Ensemble Monte Carlo device simulation method is the method chosen for the analysis in this thesis work.

Figure 3.4- Semi-classical and quantum-mechanical transport approaches.

# Semiclassical Transport

- Drift-Diffusion Model

- Hydrodynamic Model

- Solution of the Boltzmann Transport Equation

- Direct

- Spherical Harmonics

- Monte Carlo

# Quantum-Mechanical Transport

- Quantum Monte Carlo

- Wigner Function, Density Matrix Method

- Non-Equilibrium Green's Function Formanism

- Many-Body Solution of the Schrodinger Equation

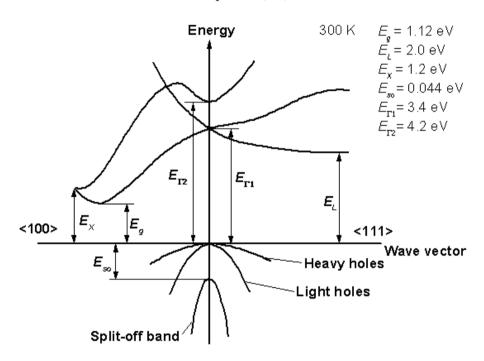

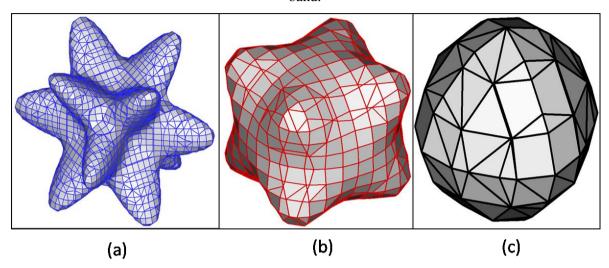

The Ensemble Monte Carlo (EMC) device simulation method nowadays is a well established tool for simulating transport in semiconductor devices. The Monte Carlo method is attributed to Fermi, Von Neumann, and Ulam, during their research in Los Alamos for the construction of the atomic bomb, even though there are indications of previous uses of the technique dating back to the beginning of the century (JACOBONI, 2002). In large semiconductor devices, the high computational cost and the large size of transistors, however, limited its use mostly to analyzing bulk material properties as alternative methods like driftdiffusion were at that time adequate and much faster. For the state-of-the-art devices the need for the EMC device simulation method was created; however, there are no commercial TCAD tools that implement the EMC device simulation method that the author is aware of. The data regarding the impact of traps in devices presented in the literature were generated by several groups that developed their own code to simulate these effects and in all cases considered they referred to n-channel devices. It is important to highlight the material and the carrier type being considered (electrons or holes), because in a simulation code based on the EMC method, the simulation depends strongly on the band characteristics. In the case of electrons, we refer to the properties of the conduction bands and in case of holes to the properties of the valence bands. The energy bands in which the carrier of interest is located affect the simulation both when defining the scattering rates of the carriers as well as when defining the relationship between the energy and the wave vector of each carrier. To the best of the knowledge of the author, there is not another work that has developed a code with the required complexity needed to simulate the impact of traps in pMOSFETs. Hence, there is a deficiency of studies on the impact of traps at device level. To target this deficiency, in this work a device simulator based on the EMC method for p-type silicon devices was developed.

In the rest of this chapter, the device simulator based on the EMC method is discussed in details. Initially, the basic algorithm for Monte Carlo simulations in a bulk material is described. At this point the equations derived from the band structure, like the ones that evaluate the scattering rates and the energy-wave vector relationship, are presented. Comparisons between the results obtained with the developed algorithm and data from the literature is given that shows the validity of the approach. Afterwards, the bulk EMC code is extended into a 3D particle-based device simulator. Once again comparisons between the simulation results obtained with the code and data from the literature and other TCAD tools were made, thus showing the correctness of the tool.

## 3.1 Bulk Monte Carlo

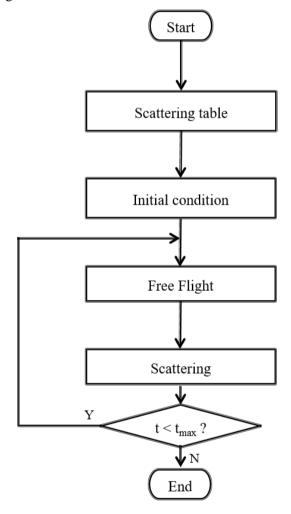

A simulation method based on the Monte Carlo algorithm consists of tracking one or more carriers for a given amount of time in which the carrier(s) go through a series of freeflight periods (where they accelerate due to the electrical field) that are followed by scattering events. For a bulk material simulation, one can track a single carrier for long enough time and obtain the characteristics of interest for that material regarding the carrier's transport (this is called single particle Monte Carlo algorithm). When a large number of carriers is tracked, the simulation may be run for a shorter time and transient effects, such as the velocity overshoot, can be observed. When several carriers are tracked simultaneously, the simulation is called Ensemble Monte Carlo (EMC). Both the single particle and the EMC simulation consist of a free-flight-scattering loop which repeats itself until the simulation time is reached. Statistics is gathered at the so-called observation times at which the ensemble is frozen and average particle velocity and average particle energy are being calculated. There is no specific physical limit on the length of the observation times for bulk simulations. Typical values are on the order of 10s of femtoseconds to get good resolution in the time domain. The duration of the simulation depends on when the system reaches steady-state and is on the order of 5-10 picoseconds. Hence, there are many observation points during the length of the simulation.

The time between scattering events, where the carrier accelerates according to the applied electric field (Newton's law), is called free-flight and has its length defined by the

maximum cumulative scattering rate of all the scatter mechanisms present in the given band. The scattering rates, in turn, are a function of the band structure, the presence of other possible bands and the energy of the carrier. In a given band or valley, for each mechanism and for different carrier energies the scattering rate is calculated and a table is generated. The process is repeated for all possible bands and valleys for that kind of carrier in that specific material thus generating a set of tables. Those are called scattering tables.

Figure 3.5- Bulk Monte Carlo simulation flowchart.

Source: (VASILESKA, 2010)

A Monte Carlo code for bulk materials has a flowchart presented in figure 3.5. In the case of a single carrier simulation the carrier is initialized with a given energy and wave vector. The initialization of the carrier is not critical as the result extracted by the simulation will be the one obtained after a long period of time. Thus, transient characteristics cannot be calculated. For an EMC bulk simulation, the flowchart becomes slightly different with the addition of an extra loop where the number of carriers is swept. As in the case of an EMC simulation one

might be interested in the transient results, such as the velocity overshoot effect, it is important to initialize the carriers properly.