# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

## MAICO CASSEL DOS SANTOS

Adaptive Low Power Receiver combining ADC Resolution and Digital Baseband for Wireless Sensors Networks based in IEEE 802.15.4 Standard

Thesis presented in partial fulfillment of the requirements for the degree of Master of Microelectronics

Advisor: Prof. Dr. Luigi Carro

#### CIP - CATALOGING-IN-PUBLICATION

Santos, Maico Cassel dos

Adaptive Low Power Receiver combining ADC Resolution and Digital Baseband for Wireless Sensors Networks based in IEEE 802.15.4 Standard / Maico Cassel dos Santos. – 2015.

83 f.:il.

Advisor: Luigi Carro.

Thesis (Master) — Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica. Porto Alegre, BR — RS, 2015.

1. Wireless Sensors Networks. 2. Transceivers 3. Adaptive Wireless Receivers 4. Digital Baseband I. Carro, Luigi. II. Adaptive Low Power Receiver combining ADC Resolution and Digital Baseband for Wireless Sensors Networks based in IEEE 802.15.4 Standard.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento

Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb

Coordenador do PGMICRO: Prof. Gilson Inácio Wirth

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **AGRADECIMENTOS**

Gostaria de agradecer primeiramente a minha família pela paciência e apoio que tiveram nos momentos em que tive que me ausentar para realizar o respectivo trabalho.

Por segundo as pessoas que tiveram maior impacto na minha capacitação em microeletrônica, sem a qual não teria o conhecimento necessário para realizar este trabalho: Fernanda Kastendsmidt, minha orientadora ainda na graduação onde iniciei meus estudos na área de circuitos digitais tolerantes a falhas por radiação; Luigi Carro, meu professor na graduação e orientador no mestrado pelos trabalhos que exigiam muito esforço mas traziam sempre conhecimentos úteis a minha carreira; Eric Fabris e equipe NSCAD Microeletrônica, por terem me apresentado grandes desafios na área de semicondutores e onde por 5 anos tive uma formação profissional diferenciada globalmente; instrutores da vendor de EDA Cadence, pelo compartilhamento de experiências na área; turmas do CI Brasil em que tive o privilégio de ensinar e também aprender nos 4 anos em que fui instrutor.

Por fim mas não menos importante, gostaria de agradecer aos amigos de bar que nunca desistiram de me convidar para as grandes discussões filosóficas, apesar das minhas negativas com a desculpa de finalizar a dissertação: Vagner Zanatta, Márcio Vasconcelos, Glauco da Rocha e Everton Ghignatti.

#### **ABSTRACT**

With the increase of Internet of Things applications and devices, many efforts to reduce power consumption in transceiver has been invested. Most of them targeted in RF frontend, converters, or in the digital baseband architecture individually. As result, there are few margins nowadays for power improvement in these blocks singly that compensates the huge hard work required.

The next optimization step leads to a system level analysis seeking design space and new possibilities expansion. It is in this field that adaptive systems approaches are conquering ground recently. The solutions combines Radio Frequency (RF) and process variation techniques, Low Pass Filters (LPF) and Analog to Digital Converters (ADCs) adjustment for better performance, digital baseband bit width adaptive according to income packet SNR, configurable ADC resolution and topology, and others.

In this scenario the current work proposes an adaptive system level architecture targeting ADC and digital receiver power reduction. It uses a robust algorithm for digital baseband receiver, a Sigma-Delta ADC, and suggests a feedback control block based on packet SNR measure. The system was designed for the IEEE 802.15.4 standard and required system modeling using Matlab tool, hardware description in Verilog language, and logic synthesis using X-FAB XC018 process for validation and power consumption estimation.

Simulations show up to 15% of system power reduction and still meeting the standard requirements. The work results were published in the International Instrumentation and Measurement Technology Conference of 2014 occurred in Montevideo - Uruguay.

**Keywords:** IEEE 802.15.4. Wireless Sensor Network. ZigBee. Sigma-delta ADC. Digital baseband transceiver.

Receptor adaptativo de baixa potencia combinando resolução de conversor analógico para digital e banda base digital para redes de sensores sem fio baseado no protocolo IEEE 802.15.4

#### **RESUMO**

Com o aumento das aplicações e dispositivos para Internet das Coisas, muitos esforços para reduzir potência dissipada nos transceptores foram investidos. A maioria deles, entretanto, focam individualmente no rádio, nos conversores analógicos para digital e viceversa, e na arquitetura de banda base digital. Como consequência, há pouca margem para melhorias na potência dissipada nestes blocos isolados que compense o enorme esforço. Portanto, este trabalho propõe uma arquitetura adaptativa a nível de sistema focando em reduzir o consumo no conversor analógico para digital e no receptor digital. Ele utiliza um algoritmo robusto para o receptor banda base digital, um conversor analógico para digital topologia Sigma-Delta e um bloco de controle realimentado conforme a relação sinal ruído medida do pacote recebido. O sistema foi projetado para o protocolo IEEE 802.15.4. Para validação do sistema e estimar a potência consumida foi feito um modelo de sistema utilizando a ferramenta Matlab, uma descrição do hardware em linguagem Verilog e uma síntese lógica utilizando o processo da X-FAB XC018. As simulações mostram uma redução na potência consumida pelo sistema de até 13% e ainda atingindo os requisitos do protocolo. Os resultados deste trabalho foram publicados na conferência internacional em tecnologia de instrumentação e medidas de 2014 realizada na cidade de Montevidéu no Uruguai.

**Palavras** Chave: IEEE 802.15.4. Redes de sensores sem fio. ZigBee. Sigma-delta conversores de analógico para digital. Transceptor banda base digital.

# LIST OF FIGURES

| Figure 2.1 - Wireless system standards                               | 21 |

|----------------------------------------------------------------------|----|

| Figure 2.2 - IEEE 802.15.4 layers                                    | 22 |

| Figure 2.3 – PPDU packet format                                      | 23 |

| Figure 2.4 - Spread spectrum signal effect.                          | 24 |

| Figure 2.5 - Half-sin O-QPSK modulation                              | 26 |

| Figure 2.6 - Transmitter internal processes                          | 26 |

| Figure 2.7 - Synchronization processes                               | 27 |

| Figure 2.8 - Receiver internal processes                             | 27 |

| Figure 2.9 - Transceiver basic blocks                                |    |

| Figure 2.10 - Transceiver architecture example                       | 29 |

| Figure 2.11 - Low IF frontend architecture                           |    |

| Figure 2.12 - Zero IF frontend architecture                          | 31 |

| Figure 2.13 - Projected power dissipation (1pJ/bit)                  | 34 |

| Figure 2.14 - Resolution requirement of the ADC for Digital Baseband |    |

| Figure 2.15 - Delay and correlate architecture                       | 38 |

| Figure 2.16 - Packet detector, timing and frequency estimation       | 41 |

| Figure 2.17 - OSR and SNR effects in ADC power consumption           |    |

| Figure 2.18 - Adaptive receiver based in signal SNR                  |    |

| Figure 3.1 - Adaptive ADC resolution architecture                    |    |

| Figure 3.2 - First order Sigma-Delta ADC modulator                   |    |

| Figure 3.3 - First order modulator model in frequency domain         |    |

| Figure 3.4 - Noise shaping and low pass decimator filter             |    |

| Figure 3.5 - Second order Sigma-Delta architecture                   |    |

| Figure 3.6 - SNR, OSR, and modulator order relationship              |    |

| Figure 3.7 - Digital baseband processor architecture                 |    |

| Figure 3.8 - Phase estimator block                                   |    |

| Figure 3.9 - Transmitter model                                       |    |

| Figure 3.10 - Channel model                                          |    |

| Figure 3.11 - Low-pass filter                                        |    |

| Figure 3.12 - Sigma-delta ADC model                                  |    |

| Figure 3.13 - Decimator filter frequency response                    |    |

| Figure 3.14 - Packet detector model                                  |    |

| Figure 3.15 - Phase estimator model                                  |    |

| Figure 3.16 - Minimum ADC resolution related to BER for a given SNR  |    |

| Figure 3.17 - Minimum ADC resolution related to PER for a given SNR  |    |

| Figure 4.1 - Top-level architecture                                  |    |

| Figure 4.2 - Sigma-delta ADC decimator filter architecture           |    |

| Figure 4.3 - Decimator sinc filter micro-architecture.               |    |

| Figure 4.4 - Digital baseband architecture                           |    |

| Figure 4.5 - Carrier recovery architecture                           |    |

| Figure 4.6 - Despreading architecture                                |    |

| Figure 4.7 - Signed packet detector                                  |    |

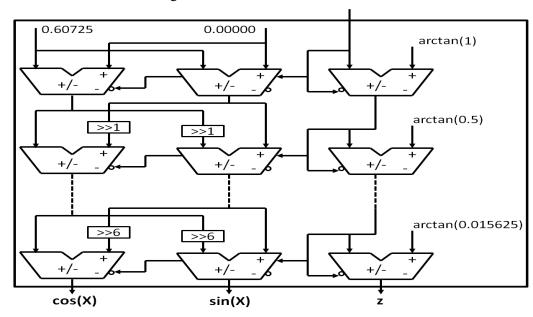

| Figure 4.8 - Cordic rotation architecture                            |    |

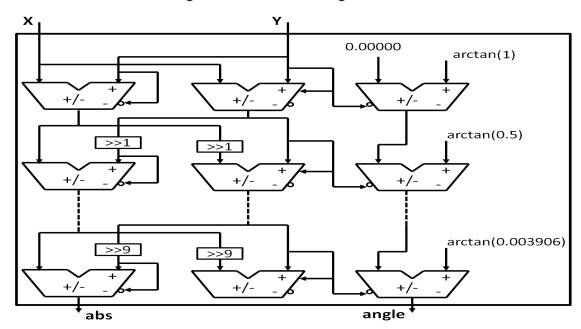

| Figure 4.9 - Cordic vectoring architecture                           |    |

| Figure 4.10 - Decision architecture                                  |    |

| Figure 4.11 - Phase estimator architecture                           |    |

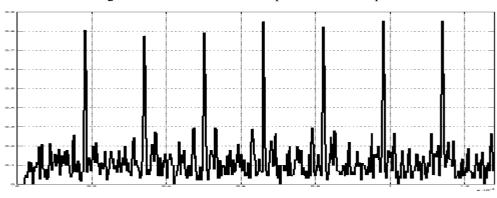

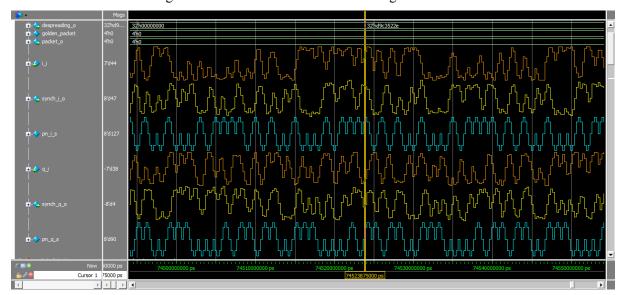

| Figure 4.12 – Model and RTL packet detection peaks                   |    |

| Figure 4.13 - Modelsim simulation of digital baseband                | 74 |

# LIST OF TABLES

| Table 2.1 - Spread spectrum encode                                          | 25 |

|-----------------------------------------------------------------------------|----|

| Table 2.2 - Rx architecture cost                                            |    |

| Table 2.3 - Advantages and disadvantages for low-power and low-cost systems | 32 |

| Table 2.4 - Performance comparison of CMOS transceivers                     | 33 |

| Table 2.5 - ADC topologies and specifications                               | 35 |

| Table 2.6 - Synchronization algorithms performance                          |    |

| Table 3.1 - Sigma-Delta ADC specification                                   |    |

| Table 3.2 - ADC model parameters                                            |    |

| Table 4.1 – Baseband synthesis result.                                      |    |

| Table 4.2 - Power consumption early estimation                              |    |

#### LIST OF ABBREVIATION AND ACRONYMS

ADC Analog to Digital Converter

AES Advanced Encryption Standard

AGC Automatic Gain Control

AWGN Additive White Gaussian Noise

BER Bit Error Rate

BPF Band Pass Filter

BW Band Width

CCA Clear Channel Assessment

CIC Cascade Integrator and Comb

CMOS Complementary Metal-Oxide Semiconductor

CORDIC Coordinate Rotation Digital Computer

CS Carrier Sense

DA Drive Amplifier

DC Direct Current

DAC Digital to Analog Converter

DCR Direct Conversion Receiver

DCT Direct Conversion Transceiver

DSSS Direct Sequence Spread Spectrum

ED Energy Detection

ENOB Effective Number Of Bits

EVM Error Vector Magnitude

FIFO First-In First-Out

IC Integrated Circuits

IDSE Interference Detector and SNR Estimator

IF Image Filter

IEEE Institute of Electrical and Electronic Engineers

IEC International Electrotechnical Commission

IoT Internet of Things

IRM Image Reject Mixer

ISO International Organization for Standardization

FIR Finite Impulse Response

FSM Finite State Machine

LO Local Oscillator

LNA Low Noise Amplifier

LPF Low Pass Filter

LQI Link Quality Indicator

LR Low Rate

LUT Look-up Table

MAC Medium Access Control Layer

MCU Memory Control Unit

MPDU MAC Protocol Data Unit

NCO Numerically Controlled Oscillator

OSI Open System Interconnect

OSR Oversampling Rate

O-QPSK Offset Quadrature Phase Shift Keying

PER Packet Error Rate

PHR PHY header

PHY Physical Layer

PLL Phase-Locked Loop

PN Pseudorandom Noise

PPDU PHY Protocol Data Unit

PSDU PHY Service Data Unit

POS Personal Operating Space

RF Radio Frequency

RSS Received Signal Strength

RTL Register Transfer Level

Rx Receiver

SAR Successive Approximation Register

SFD Start-of-Frame Delimiter

SHR Synchronization Header

SNDR Signal Noise Ration and Distortion Ratio

SNR Signal-to-Noise Ratio

TCF Toggle Count Format

TDMA Time Division Multiple Access

Tx Transmitter

VCO Voltage Controlled Oscillator

VGA Voltage Gain Control

WLAN Wireless Local Area Network

WPAN Wireless Personal Area Network

# CONTENTS

| <b>ABST</b> | FRACT                                         | 5   |

|-------------|-----------------------------------------------|-----|

| RESU        | U <b>MO</b>                                   | 7   |

| LIST        | OF FIGURES                                    | 9   |

| LIST        | OF ABBREVIATION AND ACRONYMS                  | 13  |

| 1 IN        | NTRODUCTION                                   | 19  |

| 2 W         | VIRELESS SYSTEM                               | 21  |

| 2.1         | Why IEEE 802.15.4?                            | 21  |

| 2.2         | Standard Overview                             | 22  |

| 2.2.1       | Transmission Mode                             | 23  |

| 2.2.2       | Reception Mode                                | 26  |

| 2.3         | Low Power Transceivers Architectures          | 28  |

| 2.3.1       | RF Frontend                                   | 29  |

| 2.3.2       | Converters                                    |     |

| 2.3.3       | Baseband                                      |     |

| 2.3.4       | Adaptive Architectures                        | 41  |

|             | DAPTIVE RECEIVER ARCHITECTURE                 |     |

| 3.1         | Analog-to-Digital Converter                   |     |

| 3.1.1       | Sigma-Delta ADC Architecture Overview         |     |

|             | Digital Baseband                              |     |

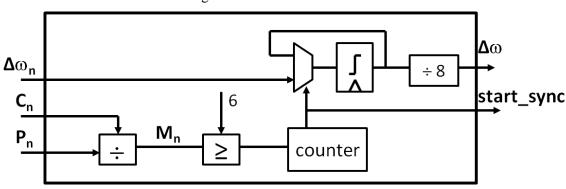

|             | Adaptive ADC power control                    |     |

|             | System Model                                  |     |

| 3.4.1       | Transmitter Model                             |     |

| 3.4.2       | Channel Model                                 |     |

| 3.4.3       | Receiver Model                                |     |

| 3.4.4       | Simulation Parameters                         |     |

| 3.4.5       | Modeling Results                              |     |

|             | ARDWARE ARCHITECTURE                          |     |

|             | Sigma-Delta ADC Decimator Filter Architecture |     |

|             | Baseband Architecture                         |     |

| 4.2.1       | Signed Packet Detector                        |     |

| 4.2.2       | Cordic Rotation and Vectoring modes           |     |

| 4.2.3       | Decision                                      |     |

| 4.2.4       | Phase Estimator                               |     |

|             | RTL Simulation                                |     |

|             | Logic Synthesis                               |     |

|             | CONCLUSION                                    |     |

|             | ERENCESENDIX DESIGN FILES                     |     |

| APP         | F/NDIX DE/SICTN FIL/E/S                       | X.1 |

#### 1 INTRODUCTION

The Internet of Things (IoT) is increasingly present in our lives and it is bringing a consequence: the world is becoming wireless. The main reasons are clear: low cost, reliability, and mobility. Tech big players companies like Cypress, Qualcomm, Atmel, Samsung, Facebook, Microchip, NXP and Google are moving sharply in this direction spending 13 billions of dollars last year in merge and acquisition.

There are many applications and respective limitations in this field. Most of them have to keep the power consumption under control to guarantee the mobility market requirement. Some have to operate years using a single battery, requiring ultra low power devices over the time (low energy). Home Automation, Smart Energy, Building Automation, Health Care, and Wireless Sensors Network are some examples in which low power devices are mandatory.

IEEE 802.15.4 standard contributes in this field by defining data rate, modulation, signal degradation, minimum distance between devices, and many other parameters targeting low power and low data rate wireless networks. In complement, IC designers have spent uncountable effort in the search for the best algorithms and architectures to push transceivers power consumption to the ground. RF front-end, converters, and digital baseband were already deeply optimized in such way that there is not too much margin to improve in the block level.

The presented work, therefore, explores a bigger picture of the transceiver architecture and, through the study of digital baseband and analog-to-digital converter characteristics, proposes an adaptive system level architecture in which reduces up to 15% the overall power with insignificant overhead. The solution uses the noise robustness of the first, the relationship between resolution and power of the second, and the income signal quality as advantage for an optimum system level relation of signal-to-noise ratio and power.

Chapter 2 presents an overview of IEEE 802.15.4 standard, the transceiver internal blocks, and low power architectures proposed in literature. Chapter 3 details the adaptive architecture including sigma-delta ADC, digital baseband processes, and adaptive control. Also, it describes the system simulation. Chapter 4 details the hardware architecture developed including micro-architecture, RTL simulation, logic synthesis, and the final results. Chapter 5 presents the conclusion and future work.

#### 2 WIRELESS SYSTEM

## 2.1 Why IEEE 802.15.4?

The concept of using wireless communication to gather information or perform certain control tasks inside a house or factory is not new. There are several standards for short-range wireless networking, including IEEE 802.11 and Bluetooth. Each of these standards has its advantages in particular applications.

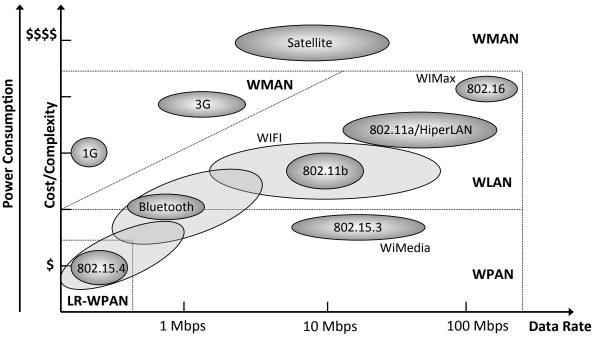

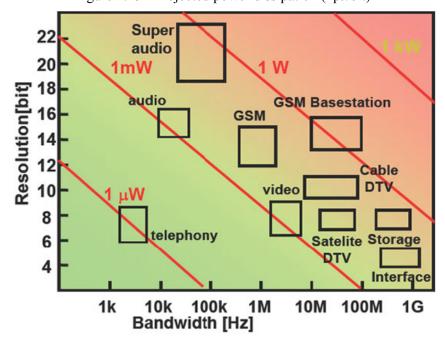

IEEE 802.11b, for instance, presents high data rate (up to 11 Mbps) and one of its typical applications is providing Internet connections (IEEE 802.11B, 2012). Bluetooth has a medium data rate (1 to 3 Mbps) and its indoor range is typically 2 to 10 meters. The most popular application is wireless headsets, where the Bluetooth is used for communication between a mobile phone and a hands-free headset (IEEE 802.15.3, 2003). IEEE 802.15.4 standard, on the other hand, targets mainly for battery-powered applications, where low data rate, low cost, and long battery life are main requirements. Its data rate of 250k bits per second is commonly adopted in wireless sensors networks (IEEE 802.15.4, 2006). Figure 2.1 summarizes the basic characteristics of the three standards and their fitness with other wireless standards. IEEE 802.11b was used in the comparison because, in the 802.11 standards family, it has the equivalent 2.4GHz band of the two above.

Figure 2.1 - Wireless system standards

Source: The author

Moreover, while the IEEE 802.11 is Wireless Local Area Network (WLAN) short-range class, the other two are Wireless Personal Network (WPAN). This means that the first is a replacement or extension of a wired Local Area Network (LANs) such as Ethernet (IEEE 802.3) and the goal is to maximize the range of data-rate. WPANs, in contrast, are not developed to replace any existing wired LAN but to provide the means for power efficient wireless communication within the personal operating space (POS) without the need of infrastructure. POS is the spherical region that surrounds a wireless device and has a radius of 10 meters (GUTIERREZ, CALLAWAY and BARRET, 2007).

IEEE 802.15.4 is classified as low rate (LR) WPAN class because of its maximum data rate of 250kbps. As a result it merges the generality, flexibility, and low cost wireless network characteristics of a WPAN with ultra low power specification, becoming a higher potential for large-scale applications.

#### 2.2 Standard Overview

Initially released in 2003, the IEEE 802.15.4 is developed by IEEE 802 standard committee and is divided in two layers based on the Open System Interconnect (ISO/IEC 7498-1, 1994) reference model and illustrated in Figure 2.2

Medium Access Control Layer (MAC)

Physical Layer (PHY)

Radio Transceiver

Figure 2.2 - IEEE 802.15.4 layers

Source: IEEE 802.15.4 (2006)

The PHY layer specification determines the physical level characteristics such as frequency of operation, data-rate, and receiver sensitivity requirements. It is responsible for activating the radio that transmits or receives packets, selects the channel frequency and makes sure any other devices on another network do not currently use it.

The MAC layer provides the interface between PHY layer and user-defined layer, usually network layer. It is responsible for generating frames (beacon, data, acknowledge, and MAC command), synchronizing the device to the network if it is configured as a synchronous network (beacon enabled), and providing device network association and disassociation services. For more details about the standard, please refer to IEEE 802.15.4 (2006)

The standard has at least three operation modes: transmitting, receiving, and idle. Therefore, it is not possible to transmit and receive data at same time.

In idle mode, the transceiver is off and waits for a request from MAC or up layers. Transmission and reception requires more detail and are presented in next two subsections.

#### 2.2.1 Transmission Mode

In a transmission mode, the transceiver is turned on and the MAC request the PHY to perform a clear channel assessment (CCA) to insure the channel is not in use by any other device. The CCA can be performed through Energy Detection (ED), Carrier Sense (CS) or both. The first estimates the signal energy level in the desired channel while the second demodulates the signal to verify whether the signal modulation and spreading are compliant with the characteristics of the PHY.

Further, if the channel is clear, MAC sends the payload to PHY, which includes the synchronization header (SHR) and the PHY header (PHR) to the packet before transmission. The SHR consists of preamble and start-of-frame delimiter (SFD). They enable the receiver to synchronize and lock into bit stream. Both are binary values of 32 zeros and 0xE5 respectively. The PHR consist of 7 bits, which represent the frame length information in octets.

PHY Service Data Unit (PSDU) is the convention name for the PHY payload sent by MAC and PHY Protocol Data Unit (PPDU) is for final packet transmitted, as it is illustrated on Figure 2.3.

4 octets 7 bits 1 bit Up to 127 octets Start-of-Frame **Preamble** Frame PSDU Reserved Delimiter (SFD) Sequence Length SHR PHR **PHY Payload** Transmitted Transmitted last

Figure 2.3 – PPDU packet format

Source: IEEE 802.15.4 (2006)

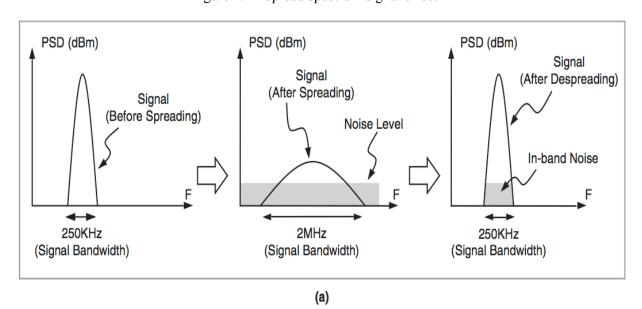

IEEE 802.15.4 uses spread spectrum methods to improve the receiver sensitivity level, increase jamming resistance, and reduce effect of the multipath. The spreading method used is the Direct Sequence Spread Spectrum (DSSS). In this sense, every 4 bits of each octet of PPDU are grouped together and referred to as symbol. Then a lookup table is used to map each symbol in a unique 32-bit sequence. This 32-bit sequence is also known as the chip sequence or the pseudorandom noise (PN) sequence. Figure 2.4 (a) shows the concept of signal spreading, Figure 2.4 (b) shows the reduced effect by interferes and Table 2.1 the lookup spreading table.

Figure 2.4 - Spread spectrum signal effect

Source: Farahani (2008, p. 146)

| <b>Data Symbol (b0,b1,b2,b3)</b> | Chip Value (c0, c1,,c31)         |

|----------------------------------|----------------------------------|

| 0 0 0 0                          | 11011001110001110101010010011110 |

| 1000                             | 111011011001110000110101000010   |

| 0 1 0 0                          | 0010111011011001110000110101010  |

| 1100                             | 00100010111011011001110000110101 |

| 0 0 1 0                          | 010100100101110110110011100011   |

| 1010                             | 00110101001001011110110110011100 |

| 0110                             | 1100001101010010010111011011011  |

| 1110                             | 10011100001101010010010111101101 |

| 0 0 0 1                          | 10001100100101100000011101111111 |

| 1001                             | 1011100011001011100000011110111  |

| 0101                             | 01111011100011001001011000000111 |

| 1101                             | 011101111011100011001011100000   |

| 0 0 1 1                          | 00000111011110111000110010010110 |

| 1011                             | 01100000011101111011100011001001 |

| 0111                             | 10010110000001110111101110001100 |

| 1111                             | 11001001011000000111011110111000 |

Table 2.1 - Spread spectrum encode

Source: IEEE 802.15.4 (2006)

The use of spread spectrum improves the signal noise ratio according to the following formula (FARAHANI, 2008):

$$Process \ Gain = 10.\log\left(\frac{2Mbps}{250kbps}\right) = 9.03 \ dB \tag{2.1}$$

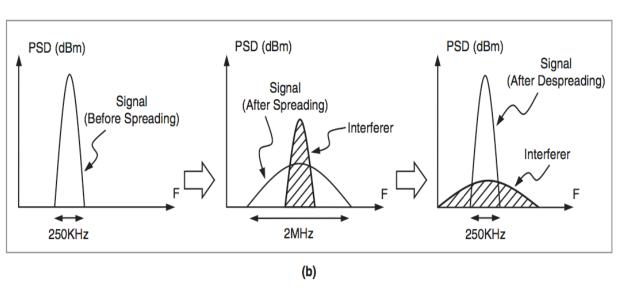

The chip sequences representing each data symbol are modulated onto the 2.4GHz carrier using Offset-Quadrature Phase Shift Key (O-QPSK) with half-sine pulse shaping. Even indexed chips are modulated onto the *in* phase "I" and the odd indexed chips onto the *quadrature* phase "Q" carrier.

To form the offset between I phase and Q phase the last shall be delayed by  $T_c$  with respect to I phase, where  $T_c$  is the inverse of the chip rate (2 Mchip/s).

Figure 2.5 illustrates the O-QPSK chip modulation.

Figure 2.5 - Half-sin O-QPSK modulation

Source: IEEE 802.15.4 (2006)

The functional block diagram in Figure 2.6 illustrates the transmitter processes discussed.

PSDU From MAC PPDU Bit to symbol Symbol to chip O-QPSK modulator Signal Transmitted

Figure 2.6 - Transmitter internal processes

Source: The author

## 2.2.2 Reception Mode

In the reception mode, the transceiver detects the transmitted packet and brings the signal from 2.4GHz frequency carrier back to the 2 MHz baseband. The signal power must be in a range of -85 dBm and -20 dBm for a proper detection and accomplishment of packet error rate (PER) less than 1%.

In addition, the reference clocks in the receiver and transmitter of two different nodes might have a difference of up to  $\pm 80$  ppm, leading into a maximum rotation speed in O-QPSK constellation of  $\pm 200$  kHz. The receiver uses the preamble sequence (PHR) and carrier recovery architecture to synchronize its clock and to lock the bit stream.

Carrier Recovery, as shown in Figure 2.7, requires timing, frequency, and phase synchronization. The first detects the beginning of preamble in a sample precision. Frequency

synchronizer estimates the carrier offset and compensates it, resulting in the stop of the constellation rotation. The last adjusts the symbol phase to expected position.

Begin of packet detection

Timing Frequency Phase

Figure 2.7 - Synchronization processes

Source: The author

In parallel with the preamble synchronization, the receiver estimates the link quality indicator (LQI) based in received signal strength (RSS), the ratio of the desired signal energy to the total in-band noise energy (SNR), or both. LQI is an indication of the quality of data packets received by the receiver. It is sent to MAC layer and is available to other layers for any type of analysis such as routing path decisions.

Demodulation uses the start of packet detected in the timing synchronizer to sample the signal closest of the peak of half-sin. Positive sample leads to bit "1" and negative, "0". Further despreading remaps the chip containing 32 bits to symbol and the symbol to set of 4 bits. They are concatenated to form the original octet base packet.

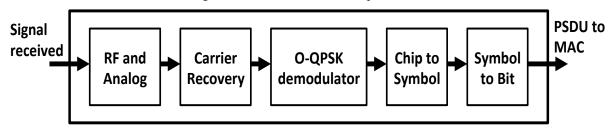

Finally, reception process is represented according to the block diagram of Figure 2.8.

Figure 2.8 - Receiver internal processes

Source: The author

Usually, MAC and up layers are performed by a processor, except for AES cryptographic block which often it is executed by a co-processor. PHY layer, on the other hand, requires a specific hardware according to standard and transmission frequency. Next section discusses some transceiver architectures found in literature and solutions presented for power reduction.

#### 2.3 Low Power Transceivers Architectures

Transceivers architectures, as shown in Figure 2.9, comprise three distinct parts: analog, mixed-signals, and digital. The first is the RF Frontend responsible for modulating and demodulating the signal. The second are the converters, which transform the analog signal to digital and vice-versa (ADC/DAC). The last one is the digital baseband, which synchronizes, encodes and decodes, and controls the PHY operation.

Transmitted

Mixer and Adder

DAC

TX

Digital

Baseband

To MAC

RX

TO MAC

Figure 2.9 - Transceiver basic blocks

Source: The author

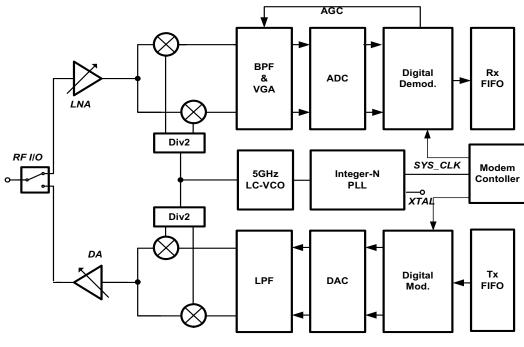

Figure 2.10 illustrates an example of a more detailed full transceiver architecture presented by Lim, Cho, *et al.* (2006). From it can be extracted the blocks that comprises the RF Fronted: Low Noise Amplifier (LNA), Mixers, Band Pass Filter (BPF), Variable Gain Amplifier (VGA), Voltage Controlled Oscillator (VCO), Phase-locked Loop (PLL), Low Pass Filter (LPF), and Drive Amplifier (DA). Also, the digital baseband contains the Digital Demodulator, Rx FIFO, Modem Controller, Tx FIFO, and Digital Modulator.

Figure 2.10 - Transceiver architecture example

Source: Lim, Cho, et al. (2006)

This architecture consumes the same current in transmission and reception modes, 25mA. It is not unusual, although, that the transmitter spends more power than the receiver. This relation will depend on architecture, design, and signal gain in the Drive Amplifier.

In fact, the gain required to transmit the signal through antenna drives most of the RF Frontend power in transmission mode. DAC and transmitter baseband blocks have low complexity, driving insignificant power.

In the reception, however, digital carrier synchronization requires complex digital processing and ADC has to oversample the signal at least in the Nyquist criteria. The result is a bigger share in power consumption of these blocks in the receiver compared to transmitter.

There are horde topologies and architectures of transceivers and to cover all of them is not the goal of this section, but to discuss some of them that are related to this work.

## 2.3.1 RF Frontend

Direct conversion transceiver (DCT) architecture is the favorite solution for singlechip radio implementations due to high level of integration and low power consumption. It does not need an image rejection filter and the IF band-pass filter is replaced by the low-pass filter. In IEEE 802.15.4 compliant devices, in contrast, it is not rare to find Low IF instead of Zero IF (direct conversion) architecture for the receiver.

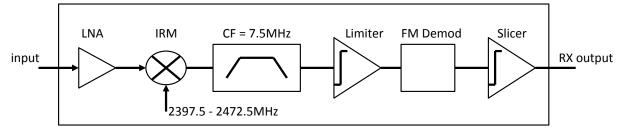

The main advantage of Low IF receiver is the absence of flicker noise. Also, the limiting IF avoids the need of automatic gain control (AGC) and offer fast response to rapidly change signal levels due to link fading conditions. Also, the discriminator and slicing circuits are straightforward to design (NOTOR, CAVIGLIA e LEVY, 2003).

The primary disadvantage of the Low IF architecture is a loss of about 3 dB in sensitivity in comparison to Zero IF receivers. Additionally, a channel filter is required to extract the desired carrier, reject nearby interfering signals, and set the receiver pre-detection noise bandwidth. Finally, an image reject mixer (IRM) is required to reject signals at or near the receiver image frequency.

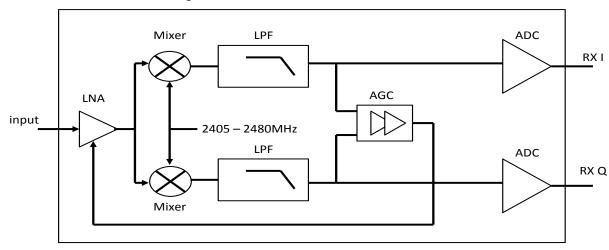

On the other hand, Zero IF architecture has four advantages compared to Low IF. The first it does not require the transceiver local oscillator (LO) to change frequency when transitioning between transmit and receive modes. Second, it does not require image reject mixer since there is no image frequency. Third, Zero-IF architecture utilizes a pair low pass filters, that are simpler to implement, to reject the high frequency noise and increase the SNR of output signals *I* and *Q*. Finally, the Zero IF architecture supports optimum demodulation with matched filter and synchronous detection techniques.

Unfortunately, Zero IF presents many imperfections like DC-offset, even-order distortion, flicker noise, I/Q mismatch and LO pulling/pushing (RAZAVI, 1997). To compensate them, the architecture include automatic gain control (AGC), post-mixer DC offset cancelation, and additional circuitry to implement synchronous demodulation and optimum baseband filtering. In addition, some care has to be taken to preserve amplitude balance and quadrature phase shift for the channels I and Q – also known as Error Vector Magnitude (EVM). This leads to a higher receiver currents and greater power dissipation in return to superior performance.

Figure 2.11 and Figure 2.12 illustrates Low IF and Zero IF architectures respectively.

Figure 2.11 - Low IF frontend architecture

Source: Notor, Caviglia and Levy (2003)

Figure 2.12 - Zero IF frontend architecture

Source: Notor, Caviglia and Levy (2003)

Moreover, Notor, Caviglia and Levy (2003) presents a comparison of Low-IF vs. Zero-IF (DCR) for receiver in terms of silicon area and silicon cost for 0.18 um process, presented in Table 2.2. It was used \$ 0.10/mm<sup>2</sup> for production quantities cost estimation.

Cost Parameters

Low IF RX

Zero IF RX

RF Front-End Area

0.9 mm²

1.75 mm²

IF Chain Area

1.6 mm²

2.5 mm²

RX Chip Area

2.5 mm²

4.25 mm²

RX Die Cost

\$ 0.25

\$ 0.425

Table 2.2 - Rx architecture cost

Source: Notor, Caviglia and Levy (2003)

Therefore, although Zero IF presents a better performance, current chip sets are giving more importance to power consumption and die cost, consequently given preference for Low IF receiver architectures.

Kwon, Park, et al. (2012) present a more detailed analysis about transceiver RF Frontend. They compare the advantages and disadvantages of different approaches of low-power and low-cost systems seeking reduce the power consumption in the sleep and the active mode. The "References" column list several published works in which the respective approach was used. For instance, in the second line they referenced five works that used Scaling Down CMOS approach that enhance the respective advantages and disadvantages columns. Regulator for sleep block, RC oscillator, current bleeding mixer, stacked VCO, passive wake-up block, quick start oscillator, and LNA with negative "gm" blocks were implemented with focus on low power. As result an ultra low power transceiver was achieved.

The main considerations and techniques taken into account are summarized in Table 2.3.

Table 2.3 - Advantages and disadvantages for low-power and low-cost systems

|                       | References                                                                                                              | Advantages                                 | Disadvantages                                                                                                            | (KWON, PARK, et al., 2012) |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------|

| CMOS<br>approaches    | Scaling Down:<br>(BAKER, 2005)<br>(LEE, 1998)<br>(MARK, 2010)<br>(PHAN, KIM, et al., 2005)<br>(LEE, JANG, et al., 2007) | • ft increases • VDD decreases • Low Power | Hard to meet the standard specification using the low VDD                                                                | 0.18 um                    |

|                       | Thick Metal Layer:<br>(ABIDI, POTTIE and KAISER, 2000)                                                                  | Sheet resistance<br>decreases -> high<br>Q | Cost increases                                                                                                           | In use at inductor         |

| Circuit<br>approaches | Weak inversion: (SHAMELI and HEYDARI, 2006) (LIN, SANCHEZ, et al., 1998) (ELMOURABIT, LU and PITTET, 2005)              | Low power                                  | Poor frequency response                                                                                                  | In use at LNA and RC-OSC   |

|                       | MTCMOS:                                                                                                                 | Low power                                  | Cost increases                                                                                                           | Not in use                 |

|                       | (JIAO and KURSUN, 2010)  Negative Gm: (ALLAM, MANKU and MARSY, 1996)                                                    | High Q at inductor -> low power            | Complicated tuning                                                                                                       | In use in LNA              |

|                       | Current reuse:<br>(ZHENG, YAO, et al., 2009)<br>(KARANICOLAS, 1996)                                                     | Low power                                  | High noise     Headroom     decreases                                                                                    | In use at VCO and DIV2     |

| System approaches     | Digitized receiver using SD-ADC:<br>(KWON, PARK, et al., 2008)<br>(PHILIPS and PETER, 2004)                             | Multi-standard     Low power               | Not good to protect from interferes                                                                                      | Low IF                     |

|                       | Subsampling:<br>(JAKONIS, KALLE, <i>et al.</i> , 2005)<br>(DEVRIES and MASON, 2008)                                     | • Multi-standard • Low power               | High noise     High upconversion of phase noise                                                                          | Low IF                     |

|                       | Polar transmitter:<br>(ZHUANG, WAHEED and<br>STASZEWSKI, 2010)                                                          | Multi-standard     Low power               | Complicated control                                                                                                      | Zero IF                    |

|                       | Wake-up: (HAKKINEN and VANHALA, 2008) (DRAGO, SEBASTIANO, et al., 2009) (HUANG, RAMPU, et al., 2010)                    | Low power                                  | Wake up by the interferers                                                                                               | In use                     |

|                       | (PLETCHER, RABAY and GAMBINI, 2009)                                                                                     |                                            |                                                                                                                          |                            |

| Operating approaches  | Sleep mode:<br>(JURDAK, RUZZELI and<br>O'HARE, 2010)                                                                    | Low power                                  | <ul> <li>Impossible to quick<br/>response</li> <li>Required additional<br/>circuits (RC, OSC,<br/>regulators)</li> </ul> | In use                     |

Source: Kwon, Park, et al.(2012)

To finish, Kwon, Park, *et al.* (2012) compare their performance with others CMOS transceivers and the results are shown in Table 2.4.

Table 2.4 - Performance comparison of CMOS transceivers

|                                                      | Arch.                             | Power                                                                           | Sensitivity | RX                                                                         |                                                   | TX/DA                                                               | Die                         |

|------------------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------------------------------|-----------------------------|

|                                                      | (RX/TX)                           | Consumption (RX/TX/sleep)                                                       |             | LNA                                                                        | Mixer                                             |                                                                     | size<br>(mm2)               |

| (KWON,<br>BYUN, et al.,<br>2009)                     | Low IF /<br>Direct<br>modulation  | 25.74mW<br>30.06mW<br>1.44uW                                                    | -95dBm      | Cascode with negative gm                                                   |                                                   | Differential<br>common source<br>topology with off<br>chip inductor | 7.84 <sup>[3]</sup>         |

| (NAM, CHOI, et al., 2007)                            | Low IF /<br>Direct<br>modulation  | 22.3 mW <sup>[1]</sup><br>18 mW <sup>[1]</sup>                                  | -94dBm      | Gm boosted<br>LNA                                                          | Gilbert cell<br>current<br>reuse LNA<br>and mixer | -                                                                   | 5.125                       |

| (RAJA, CHEN, et al., 2010)                           | Low IF /<br>Zero IF               | 10.8mW <sup>[2]</sup><br>16.2mW <sup>[2]</sup>                                  |             | Common source with resistive load                                          | Gilbert Cell                                      | External inductor load                                              | 3.61                        |

| (EO, YU, et al., 2007)                               | Low IF /<br>Zero IF               | 32.4mW <sup>[1]</sup><br>30.6mW <sup>[1]</sup>                                  |             | Single ended<br>sascode LNA<br>with<br>inductive<br>source<br>degeneration |                                                   | Class AB power<br>amp. external<br>inductor                         | 6.5                         |

| (BALANKUT<br>TY, YU, et al.,<br>2010) <sup>[4]</sup> |                                   | 32.5mW                                                                          |             | Single ended cascade LNA                                                   | Gilbert Cell                                      |                                                                     | 2.9                         |

| (KLUGE,<br>POEGEL, et<br>al., 2006)                  | Low IF /<br>Direct<br>modulation  | 26.46mW<br>28.26mW<br>3dBm output                                               | -101dBm     | Stacked LNA                                                                | Passive<br>switching<br>pairs                     | Class AB power<br>amp. With on-<br>chip LC                          | 5.77                        |

| (RETZ,<br>SHANAN, et<br>al., 2009)                   | Zero IF /<br>Direct<br>Modulation | 30.24mW<br>32.4mW                                                               | -96dBm      | Common gate<br>LNA                                                         | Passive<br>current<br>mode<br>quadrature<br>mixer | -                                                                   | 5.9                         |

| (NGUYEN,<br>KIM, et al.,<br>2007) <sup>[5]</sup>     | Zero IF / -                       | 20.7mW <sup>[1]</sup><br>40.5mW <sup>[1]</sup>                                  |             | Single ended cascade                                                       | Balanced passive mixer                            | -                                                                   | 10                          |

| (SEO, MOON, et al., 2007) <sup>[5]</sup>             | Zero IF / -                       | 25.2mW <sup>[1]</sup><br>28.8mW <sup>[1]</sup>                                  | -98dBm      | Current reuse<br>complementa<br>ry technique<br>without<br>inductor        |                                                   | Differential<br>common source<br>topology with off<br>chip inductor | 3.96                        |

| (KWON,<br>PARK, et al.,<br>2012)                     | Low IF /<br>Zero IF               | 18.36mW <sup>[1]</sup> 23.58mW <sup>[1]</sup> 1.08uW <sup>[1]</sup> 0dBm output | -101dBm     | Cascode with negative gm                                                   | Current<br>reuse mixer                            | Differential<br>common source<br>topology with off<br>chip inductor | 7.84 <sup>[3]</sup><br>3.96 |

| [I] Mat in a                                         | lude modem                        |                                                                                 |             | [4] 00                                                                     | nm process                                        | 0 6 V                                                               |                             |

<sup>[1]</sup> Not include modem

Source: Kwon, Park, et al. (2012)

<sup>[4] 90</sup> nm process, 0.6 V

$<sup>^{\</sup>text{\tiny{[2]}}}$  Not include modem and PLL

<sup>&</sup>lt;sup>[5]</sup> 915 MHz

<sup>[3]</sup> Including MCU and flash memory

#### 2.3.2 Converters

In complex systems and in portable applications the main architectural decisions of converters are often determined based on bandwidth, resolution and power available.

For DAC, Resistors Chain is the commonly chosen architecture for short bandwidth and low-resolution transceivers due to its stability and power consumption. Current Steering is another option when high speed and high resolution is required. Although it has the same advantages of the previous, Capacitor's Switches introduce switching noises to the signal. For this reason it is avoided in RF applications (SHE and ISMAIL, 2002).

Nevertheless, all DAC architectures for transceivers are quite simple and, compared to the RF Frontend, they do not influence in the transmitter power dissipation (most of them consumes in order of "uW").

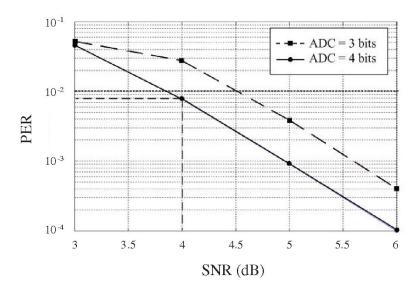

ADCs, on the opposite, have complex architectures. The power consumption varies sharply according to topology, resolution and bandwidth. Figure 2.13, presented by Pelgrom (2010), illustrates this dependency through the projected power dissipation according to resolution and bandwidth of ADCs.

Figure 2.13 - Projected power dissipation (1pJ/bit)

Source: Pelgrom (2010, p. 427)

Therefore, choosing the correct ADC architecture that meets to the application requirements is mandatory. For IEEE 802.15.4 the main requirements are BW = 2 MHz, low power, and the minimum resolution required by digital baseband for carrier synchronization.

From Table 2.5, extracted from Pelgrom (2010) which summarizes the main ADC topologies and specifications, it is clear that Successive approximations and Sigma-delta are the two topologies that most fit to the standard. It can not be neglected, however, that in the near future multi-standard transceivers will be a reality. This means that a single ADC will operate with different bandwidth and resolutions. Therefore, choose the most versatile ADC topology that still accomplishes the low-power requirements of the standard, results not in a technical but market advantage. For this reason, the Sigma-Delta ADC was chosen instead of SAR.

Type of analog-to-digital **Clock cycles Specification** converter for N bit conversion Full-flash converter 1 Very fast BW = 1GHz, N < 6-8, power hungry N < 8.91 Folding converter N < 12-14, fast BW = 10 - 200 MHz, efficient, Pipeline N latency of > N clock cycles Successive N Compact, BW = 2 - 5 MHz, N < 12, low power approximations 20 - 50N up to 24, BW = 100 Hz - 5 MHzSigma-delta  $2^{N}$ N = 14 - 20, BW = 10 kHz**Dual-slope**

Table 2.5 - ADC topologies and specifications

Source: Pelgrom (2010, p. 423)

Scolari and Enz (2004) compare three different architectures of sigma-delta ADC for IEEE 802.15.4 standard in order determine which better fits for the application: Direct conversion, Low IF, and Low IF with quadrature band-pass.

Direct conversion is the simplest because of the absence of IF and, therefore, any image frequency. This results in reduced power consumption and high integration. The disadvantages are a strong DC component caused by self-coupling of the LO signal occurring at the mixer input and flicker noise.

Low IF with Low-Pass sigma delta presents no flicker noise and the intermediate corner frequency (frequency at which the flicker noise is equal to the white noise – fc) of IF can reduce the noise power. The count is that the "fc" can not be chosen too high because the quantization noise of the Sigma-Delta starts to degrade the SNR.

The last one is the Low IF with quadrature band-pass Sigma-Delta. It avoids the quantization noise and flicker noise but it is more sensitive to the mismatch of I and Q signals.

Therefore, any of the last two could be used if countermeasures for their imperfections

are predicted.

Until now the bandwidth and the best ADC topology for low power is defined. The last parameter is the resolution.

The resolution of an ADC implies in the quantization noise added to the signal that propagates to baseband. Determine the minimum resolution depends on the minimum SNR the baseband supports to succeed in the signal recovery. The SNR consist not only from the noise of an ADC but also from channel and the RF frontend according to the Equation 2.2

$$SNR = \frac{P_{signal}}{W_{channel+radio} + W_{adc}}$$

(2.2)

Where:

- $P_{signal} = Signal power$

- W<sub>channel</sub> = Noise power introduced by channel

- W<sub>adc</sub> = Noise power introduced by ADC

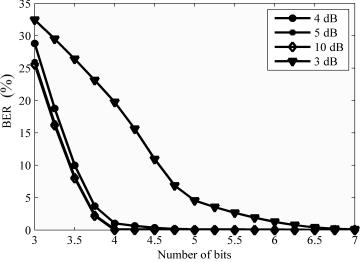

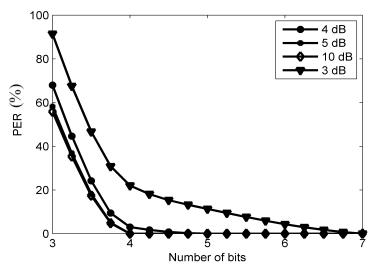

To define the ADC output bit number (N), Wang, Huang, *et al.* (2006) simulate their proposed transceiver architecture varying the N of the ADC and plotting the SNR vs. Packet Error Rate (PER) curves for each N, shown in Figure 2.14. Therefore, for a PER of 1% their digital baseband requires at least 4 bits for a SNR of 4 dB. Since digital baseband SNR robustness is singular to the architecture, a similar simulation is recommended to determine the minimum ADC resolution.

Figure 2.14 - Resolution requirement of the ADC for Digital Baseband

Source: Wang, Huang, et al (2006)

#### 2.3.3 Baseband

The baseband is the responsible for the carrier recovery, despreading and transmit the packet information (MPDU) to MAC layer. For IEEE 802.15.4 standard the most complex function is the correct synchronization. Since the frequency error caused by clock variations between transmitter and receiver might vary 10% of the bandwidth,  $\pm 200$  kHz, and the low power application requires low complexity, a robust and simple algorithm becomes mandatory.

Synchronizers comprise estimation and recovery processes. The first is commonly executed in digital domain. Recovery, on the other hand, can be done on analog, through feedback the estimation to compensate in the VCO, as implemented by Wang, Huang, *et al.* (2006), or in digital, through inner product of income signal and the signal generated with the frequency error.

Although digital correction might lead to a bigger area, it is a trend nowadays to push signal processing to digital. The main reason is to avoid parameters variations in analog circuit components caused by corners, temperature and supply voltage, and process variation in fabrication.

Mengali and D'Andrea (1997) present a collection of estimation algorithms for linear modulator and continuous phase modulation for the three synchronizers: frequency, phase and timing. Table 2.6 presents some algorithms applicable to IEEE 802.15.4 standard and their main advantages and disadvantages.

Table 2.6 - Synchronization algorithms performance

|                         | Algorithm              | Advantages                                                         | Disadvantages                                                                       |  |

|-------------------------|------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|

| Frequency<br>Estimation | Data-Aided             | High precision                                                     | Low operation range or high SNF required                                            |  |

|                         | Decision-<br>Directed  | Simple implementation                                              | Low precision and high SNR required                                                 |  |

|                         | Delay-and-<br>multiply | Robust to low SNR and high operation range                         | Low Precision                                                                       |  |

| Phase<br>Estimation     | Data-Aided             | High precision, robust to low/intermediate SNR, and low complexity | As SNR increases, precision is degraded which might require long observation length |  |

|                         | Decision-<br>Directed  | High precision                                                     | Intermediate to high SNR required                                                   |  |

|                         | Ad Hoc<br>Feedforward  | Robust to low SNR                                                  | Medium precision                                                                    |  |

| Timing<br>Estimation | Decision-<br>Directed | Low SNR, good tracking and high precision                | Long pulses required, have false locks and it is complex implementation |

|----------------------|-----------------------|----------------------------------------------------------|-------------------------------------------------------------------------|

|                      | Feedforward           | Short pulses, low SNR and low complexity                 | Poor tracking and medium precision                                      |

|                      | Feedback              | Short pulses, no false locks, low SNR and low complexity |                                                                         |

Source: Mengali and D'Andrea (1997)

From the Table 2.6, it is clear that there will always be trade-off between any of those algorithms. Moreover, the choice of any of those algorithms, as they are, will not lead to the best solution. As it is described in next paragraphs, the combination of some of those in a practical hardware produces a higher performance.

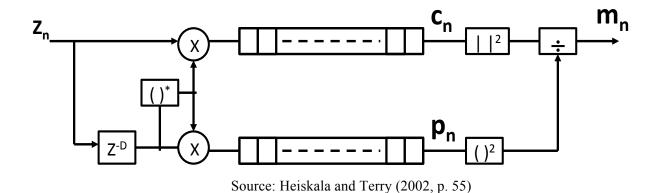

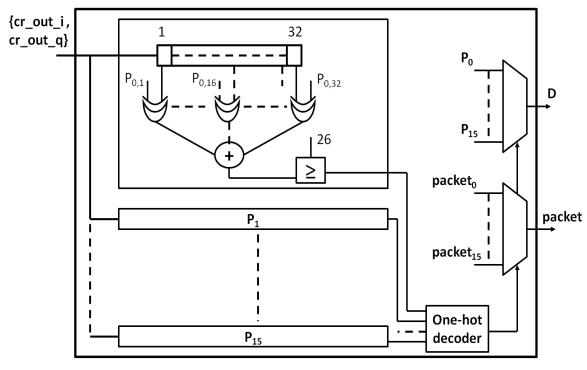

Targeting OFDM LANs, 802.11 more specifically, Heiskala and Terry (2002) present a simple method for packet detection called "delay and correlate" developed by Schmidl and Cox (1996), which imply the Delay-and-Multiply with extra features. The method is based in two sliding windows C and P, as shown in Figure 2.15. C window is the cross-correlation between received signal and a delayed version of the received signal. The delay  $z^{-D}$  is equal to the period of the preamble. The P window calculates the received signal energy during cross-correlation window and it is used to normalize the decision statistic.

Figure 2.15 - Delay and correlate architecture

From Figure 2.15, the Equation 2.3 and Equation 2.4 are extracted to calculate the value of  $c_n$  and  $p_n$  respectively. Note that the "\*" means complex conjugate and  $Z^D$  means the delay in digital signal processing. In the equations, L means the window length.

$$c_n = \sum_{k=0}^{L-1} z_{n+k} z_{n+k+D}^*$$

(2.3)

$$p_n = \sum_{k=0}^{L-1} z_{n+k+D} z_{n+k+D}^* = \sum_{k=0}^{L-1} |z_{n+k+D}|^2$$

(2.4)

The decision statistic  $m_n$  is calculated from Equation 2.5.

$$m_n = \frac{|c_n|^2}{(p_n)^2} \tag{2.5}$$

When the received signal consists of only noise, the output of  $c_n$  of the delayed cross-correlation is zero-mean random variable. Once the start of the packet is received,  $m_n$  jumps quickly to its maximum value.

In addition, using same structure and adding the expected preamble,  $t_k$ , the algorithm becomes a symbol timing estimation, as shown in Equation 2.6.

$$t_{s} = arg \left\{ \max_{n} \left| \sum_{k=0}^{L-1} z_{n+k} t_{k}^{*} \right|^{2} \right\}$$

$$(2.6)$$

The value of n, which corresponds to maximum absolute value of the cross-correlation, is the symbol-timing estimate.

Also, the length of L of the cross-correlation determines the performance of the algorithm. Larger values improve performance, but also increase the amount of computation required.

Based in TDMA applications, Classen, Meyr and Sehier (1993) merged the Delay-and-Multiply with Data-Aided algorithms and proposed a method in which timing estimation from Equation 2.6 and frequency estimation can be performed simultaneously if the preamble exhibits some kind of periodicity. Equation 2.7 and Equation 2.8, resulted from this method, calculates the start of frame and frequency error estimation respectively.

$$\dot{n} = \max_{n} \left\{ \left| \sum_{k=1}^{L-1} [z_{n-k} z_{n-k-D}^*] d_n \right| \right\}$$

(2.7)

$$\emptyset = \frac{1}{D} \arg \left\{ \left| \sum_{k=1}^{L-1} [z_{n-k} z_{n-k-D}^*] d_n \right| \right\} | n = \dot{n}$$

(2.8)

Where:

- Ø is the frequency error

- D is the delay window

- $d_n$  is the inner product of preamble with the preamble delayed (windowed)

- $\vec{n}$  is the timing estimation

- L is the number of frames in the preamble

Moreover, the probability of an incorrect frame synchronization is less than 10<sup>-5</sup> for AWGN SNR >= 3 dB and the structure provides a robust synchronization over a Rician fading channel (multipath channel model) if the estimation length is small with respect to the inverse coherence bandwidth of the fading process (CLASSEN, MEYR e SEHIER, 1993).

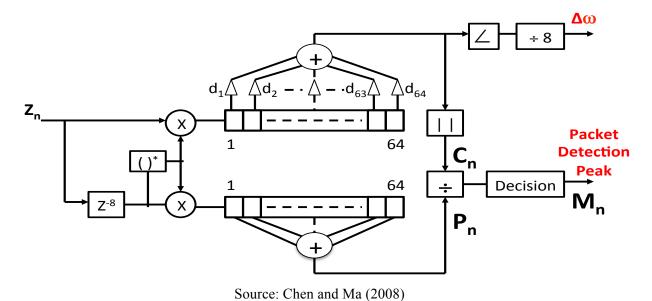

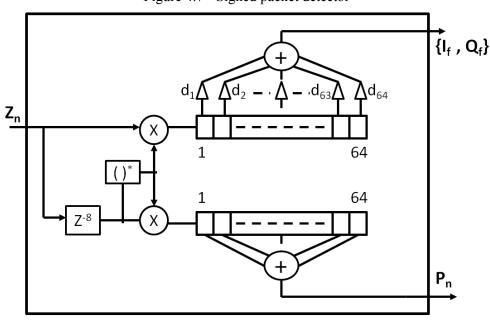

To conclude this subsection, from structure presented by Heiskala and Terry (2002) and the method proposed by Classen, Meyr and Sehier (1993), Chen and Ma (2008) developed a 1.8 mW baseband processor for IEEE 802.15.4. The biggest advantage of such architecture is to merge packet detection, symbol timing, and frequency estimation in a single block. Equations 2.9-2.12 and Figure 2.16 detail the method. Also, the fix-point implementation by Chen and Ma (2008) is robust to SNR down to 4.5 dB.

$$C_n = \sum_{i=0}^{L-1} |z_{n-i} z_{n-i-D}^*| d_i$$

(2.9)

$$P_n = \sum_{i=0}^{L-1} |z_{n-i-D}|^2$$

(2.10)

$$M_n = \left(\frac{|\mathcal{C}_n|}{P_n}\right)^2 \tag{2.11}$$

$$d_i = p_i p_{i+D}^* (2.12)$$

Figure 2.16 - Packet detector, timing and frequency estimation

### 2.3.4 Adaptive Architectures

From previous subsections it is clear that much effort was spent in the RF Frontend, Converters and Baseband leaving few margin for improvement. Moreover, all transceivers architectures seen until now were designed to the worst condition and become overdesigned for a less constrained environment. Therefore, adaptive system becomes an important player for those who seeks bigger transceiver power reduction. The goal of next paragraphs is to explore a few of adaptive architecture proposed in several baseband fields.

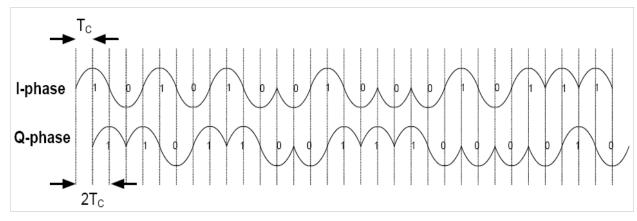

In RF Frontend and ADC field, Oguz, Morch and Dehollain (2011) analyze the reconfiguration strategy and average power dissipation reduction in a direct-conversion IEEE 802.15.4 receiver. High-level power models are built for the Low Pass Filter and a SAR ADC. The trial-and-error solver in Oguz, Morecho, *et al.* (2010) finds the filter Signal Noise and Distortion Radio (SNDR), the filter order, and the ADC SNDR combination that minimizes the total power dissipation for a given operating condition. The optimum is reached with a first-order-filter together with a reconfigurable ADC with SNR between 21 dB and 69.8 dB (ENOB of 3.2 and 11.3 bits).

The necessity for adaptive ADCs for multiple applications, especially in Software Radio, emerges recently. Veldhoven and Roermund (2011) discuss flexible Sigma-Delta ADCs for multiband devices using multiple oversampling rate (OSR). It presents a scalable

modulator and the relationship with the RF Frontend for Wireless and Cellular applications to achieve a scalable bandwidth. To configure the bandwidth it uses defined integrators capacitors for each OSR frequency the converter will operate. This keeps the signal gain without interfering in the converter stability.

Although it was published 10 years earlier, Gulati and Lee (2002) goes further and target in a reconfigurable ADC converter in which topology, resolution, and current bias are the variables. The topology is configured between Pipeline and Sigma-Delta allowing the achievement of a wide operation range. Capacitors size, pipeline length, and OSR are others configurable parameters. Also, bias current of the operational amplifier is adjusted according to the sampling frequency. Such architecture is capable to operate from 0 to 10 MHz of bandwidth and has a resolution range from 6 to 16 bits. For full resolution, a Sigma-Delta topology is used in a 10 MHz frequency, 9.4 kHz of bandwidth, and OSR of 512. The power consumption in this mode is 17.6 mW. In pipeline mode, 24.6 mW is achieved for 2.62 MHz and 11 resolution bits. The core area is 5.5 mm² for 0.6 um CMOS process. Figure 2.17 illustrates the power vs. SNR and the SNR vs. Bandwidth according to OSR.

**Constant Bandwidth Locus Constant Power Locus** Bandwidth=9.4KHz Power=17.7mW (Varying clock frequency) (fixed clock frequency, variable Bandwidth) 100 20 (512)95 (512)18 (256)90 16 (128)Power (mW) 85 SNR (dB) 80 (64)10 75 (256)8 70 6 65 (51)60 (128)(41)(32)55 50 75 85 95 55 65 10 1000 100 1 SNR (dB) Input Bandwidth (KHz)

Figure 2.17 - OSR and SNR effects in ADC power consumption

Source: Gulati and Lee (2002)

In the digital baseband, Dwivedi, Amrutur and Bhat (2011) designed power scalable digital baseband for a Low-IF receiver for IEEE 802.15.4 standard. The bit width is used to reduce the power under favorable signal and interference scenarios, thus recovering the design margins introduced to handle the worst-case conditions. The architecture, illustrated in Figure 2.18, uses a SNR estimator and interference detector (IDSE), variable tap and variable

coefficient FIR filter, an adaptive control unit, and an adaptation procedure to achieve up to 85% of power reduction.

Adaptivity control unit VGA control LUT Interference Detector and SNR  $SNR_{FE}$  | SFD Controller check  $(f_s, Q_{dig})$ VGA ADC down-converter Q FIR Clock Reference generato Various ROM Decimator Tracking Digital Demodulator CORDIC Acquisitio Interference est SFD check

Figure 2.18 - Adaptive receiver based in signal SNR

Source: Dwivedi, Amrutur and Bhat (2011)

The cost of adaptive architecture is 16% of the design area. It consumes 10 mW in synchronization and 2.49 down to 0.49 mW in the average for 256-packet size, according to the environment condition. Also, the process used was 0.13um, which gives scaling advantage in dynamic consumption compared to other references. The counter side of this architecture is the lower probability of synchronization acquisition at poor SNR caused by absent of buffered data on synchronization unit.

In summary, this chapter described the specifications of IEEE 802.15.4 standard, the transceiver main parts and architectures proposed by academy to reduce power consumption. In the high-end research are the adaptive architectures based in the LPF, ADC operation range and resolution, digital baseband data width, and income packet's SNR. None of them, however, combines the adaptive ADC resolution with a SNR robust digital baseband to decrease the converter power in a lower constraint environment. This blank research space leads to the current work proposal discussed in chapter 3.

### 3 ADAPTIVE RECEIVER ARCHITECTURE

Chapter 2 described the specifications of IEEE 802.15.4 standard and the three parts of transceiver exploring topologies and architectures proposed in published articles and books. As it was mentioned, the most used transmitter architecture is direct-conversion. Also, its main power dissipation is driven by the Driver Amplifier to increase the signal power to antenna. Therefore, most of proposals to reduce transmission power are targeted to receiver.

In addition, RF Frontend, ADC, and digital baseband architectures for WPAN applications were deeply investigated in the past 10 years, requiring huge effort nowadays to achieve significant improvements. As alternative, adaptive architectures according to system characteristics and environment become the preferred research spot.

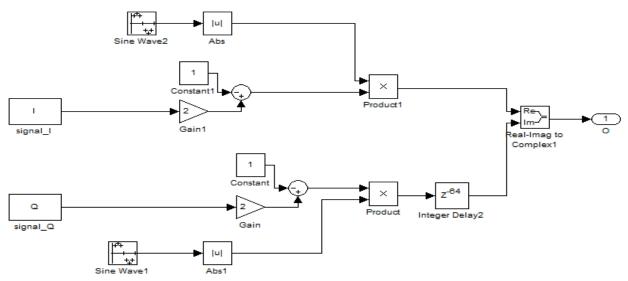

The current work joined the relationship of SNR and power of ADC explored in Dwivedi, Amrutur and Bhat (2011) with the baseband introduced in Chen and Ma (2008) to present a simple, power efficient low SNR robust system adaptive receiver architecture. ADC converters, O-QPSK baseband architecture, adaptive ADC power control block and a reference feedback signal compose it. Figure 3.1 illustrates the top-level block diagram. As can be observed, the architecture does not cover the RF Frontend part, being restricted to converters and baseband.

$Z_{(t)} \qquad \qquad Z_n \qquad \text{Digital} \qquad P_n$  Adaptive ADC power control Signal reference

Figure 3.1 - Adaptive ADC resolution architecture

Source: The author

In the figure,  $Z_{(t)}$  is the continuous time output of Frontend RF signal that is converted

to digital domain,  $Z_n$ . Digital Baseband calculates the LQI, recover the carrier and despread the signal to send the PSDU,  $P_n$ , to MAC layer. The Adaptive ADC power control sets the ADC resolution according to SNR value of *signal reference*.

In receiver wake-up, the ADC starts operation with full resolution and digital baseband search for a valid packet. If the preamble is detected, digital baseband estimates the input signal SNR, during LQI calculation, and feedback the value to Adaptive ADC power control. According to a pre-defined LUT that relates the quantization noise added to signal by ADC resolution, and the SNR of  $Z_n$ , the control block acts in the ADC to adjust the output resolution to achieve the minimum signal SNR supported by digital baseband.

Next sections detail the three blocks covering topology: architecture, system modeling and simulation in Matlab tool (MATHWORKS, 2011).

### 3.1 Analog-to-Digital Converter

Subsection 2.3.2 exposed some ADC topologies and their specifications. Two of them fit better to the IEEE 802.15.4 standard requirements: Sigma-Delta and SAR.

Although SAR could lead to less ADC power consumption, its operation range in terms of bandwidth and resolution would limit the proposed solution application for other standards. Sigma-Delta ADC, on the other hand, is more versatile due to a wider bandwidth and resolution, mandatory characteristics to be used in multi-standards transceivers. Next paragraphs present an architecture overview of the last including the ADC parameters used.

### 3.1.1 Sigma-Delta ADC Architecture Overview

Sigma-Delta contains a comparator, voltage reference, a switch, one or more integrators and summing circuits, and a digital low pass filter.

A perfect classical N-bit sampling ADC has an *rms* quantization noise of  $q/\sqrt{12}$  uniformly distributed within the Nyquist band of dc to  $f_s/2$ , where q is the value of LSB and  $f_s$  is the sampling rate (BAJDECHI e HUIJSING, 2003).

Therefore, its SNR with full-scale sine wave input will be (6.02N + 1.76dB). Also, the ADC imperfections make its noise greater than theoretical minimum quantization noise, resulting in effective resolution lower than N-bits. Equation 3.1 defines the Effective Number of Bits (ENOB):

$$ENOB = \frac{SNR - 1.76dB}{6.02dB} \tag{3.1}$$

For a much higher sampling rate,  $Kf_s$ , the rms quantization noise remains  $q/\sqrt{12}$ , but the noise is distributed over a wider bandwidth dc to  $Kf_s/2$ . If a digital low pass filter is applied to the output, much of quantization noise is removed without affecting the desired signal, improving the ENOB. The factor K is referred as Oversampling Ratio (OSR). Another advantage of oversampling is the requirements relax of analog antialiasing filter.

Since the digital output filter reduces the bandwidth, the output data rate may be lower than the original sampling rate and still satisfy the Nyquist criterion. This may be achieved by passing every  $M^{th}$  result to the output and discarding the remainder. The process is known as "decimation" by a factor M. M can have any integer value, provided that the output data rate is more then twice the signal bandwidth.

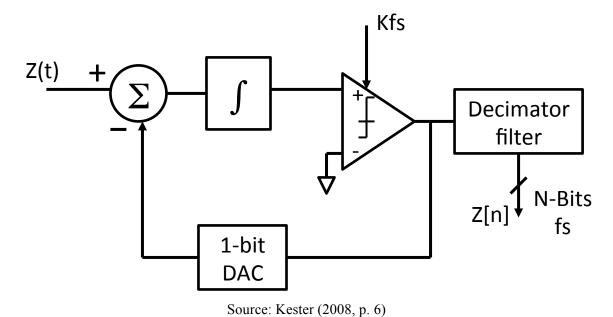

Figure 3.2 - First order Sigma-Delta ADC modulator

To enlighten the Sigma-Delta operation, assume a dc input  $Z_{(t)}$ , illustrated in Figure 3.2. The integrator is constantly ramping up or down the input of comparator. The output of the comparator is fed back through a 1-bit DAC to the summing input. The negative feedback loop from the comparator output through the 1-bit DAC back to the summing point will force the average dc voltage in the DAC output to be equal to  $Z_{(t)}$ . The average DAC output voltage

is controlled by the *ones-density* in the 1-bit data stream from the comparator output. As the input signal increases towards the supply voltage, the number of "ones" in the serial bit stream increases, and the number of "zeros" decreases. The behavior is similar but opposite if the signal goes negative. Therefore, the average value of the input voltage is contained in the serial bit stream out of the comparator. This circuit is called "first-order modulator" because only one integrator composes it. The Decimation Filter processes the serial bit-stream and produces the final output data.

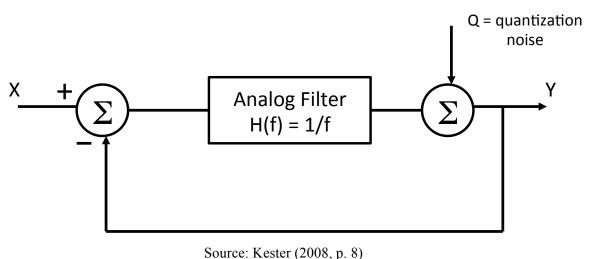

The concept of noise shaping is best explained in the frequency domain by considering the simple Sigma-Delta modulator model of Figure 3.3.

Figure 3.3 - First order modulator model in frequency domain

The integrator in the modulator is represented as an analog low-pass filter with transfer function of H(f) = 1/f. This transfer function has an amplitude response that is inversely proportional to the input frequency. The 1-bit quantizer generates quantization noise, Q, which is injected into the output-summing block. Equation 3.2 expresses the output model:

$$Y = \frac{X}{f+1} + \frac{Qf}{f+1}$$

(3.2)

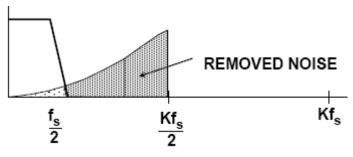

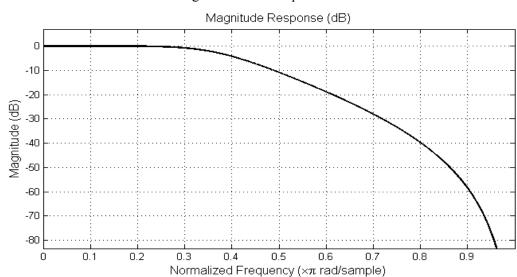

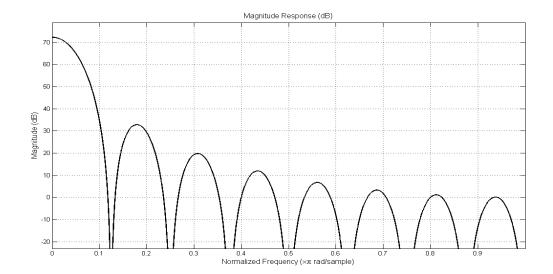

Note that as the frequency f approaches zero, the output voltage Y approaches X with no noise component. At higher frequencies, the amplitude of the signal component approaches zero, and the noise components approaches Q. Figure 3.4 shows noise shaping effect and also includes the decimation filter cutting off the higher noise-frequencies.

Figure 3.4 - Noise shaping and low pass decimator filter

Source: Kester (2008, p. 5)

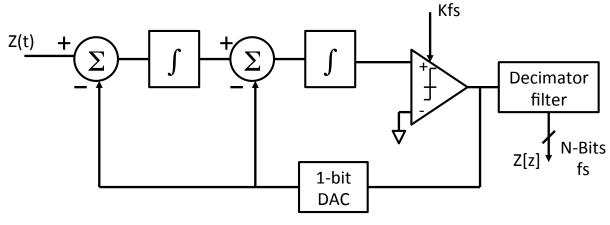

By using more than one integration and summing stage in the modulator, higher orders of quantization noise shaping can be achieved and even better ENOB for a given oversampling ratio. Figure 3.5 illustrates a second order modulator.

Figure 3.5 - Second order Sigma-Delta architecture

Source: Kester (2008, p. 9)

In addition, Figure 3.6 shows the relationship between the order of the modulator and the amount of oversampling necessary to achieve a particular SNR. For instance, if the OSR is 64, an ideal second-order system is capable of providing an SNR of about 80dB. This implies, according to Equation 3.1, approximately 13 ENOB.

Therefore, in sigma-delta analog to digital converters, the order of the modulator, the oversampling ratio, and the window of signal averaged in decimation filters deeply impact the converter SNR. This gives two alternatives to adjust the resolution according to SNR: dynamically increase and decrease the modulator order; change the OSR.

The dynamically adjustment of modulator order requires to set many parameters to avoid the block instability, which might be complex to implement. Changing the OSR, as

suggested by Veldhoven and Roermund (2011), is easier to implement and requires only adjust the capacitors values (the switch frequency in case of switched capacitors) in the modulator integrators to adjust the output gain.

120 THIRD-ORDER LOOP\* 21dB / OCTAVE 100 SECOND-ORDER LOOP 80 15dB / OCTAVE SNR (dB) 60 FIRST-ORDER LOOP 9dB / OCTAVE 40 \* > 2nd ORDER LOOPS DO NOT 20 OBEY LINEAR MODEL 0 8 16 32 64 128 256 OVERSAMPLING RATIO, K

Figure 3.6 - SNR, OSR, and modulator order relationship

Source: Kester (2008, p. 10)

Finally, the specification of ADC used is presented in Table 3.1.

Table 3.1 - Sigma-Delta ADC specification

| Modulator order                        | Second order     |

|----------------------------------------|------------------|

| Maximum OSR                            | 128              |

| <b>Decimation Filter topology</b>      | Third order sinc |

| <b>Maximum Decimation Filter Ratio</b> | 16               |

| Input bandwidth                        | 1 MHz            |

| Output sampling/rate                   | 8 M samples      |

| Maximum Output Resolution              | 7 bits           |

| <b>Modulator Power Consumption</b>     | 1.8 mW           |

| <b>Decimator Power Consumption</b>     | 1.55 mW          |

Source: The author

### 3.2 Digital Baseband

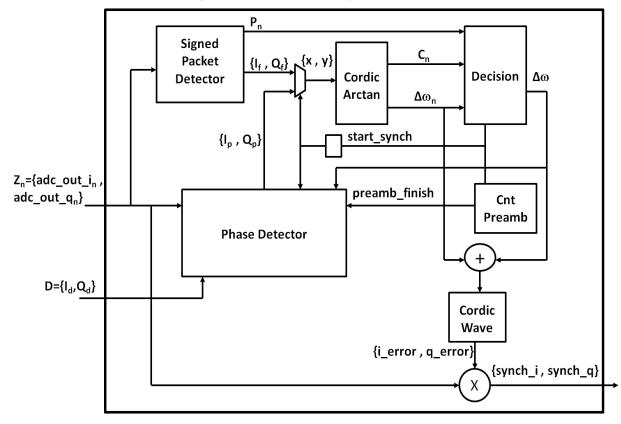

The digital baseband architecture, as already mentioned in the beginning of the chapter, is based in Chen and Ma (2008) proposal. Its advantages compared to others are the SNR robustness down to 3 dB, frequency operation of 4 MHz, and consumption of 1.8 mW, consequence of its simple and optimized algorithms. In subsection 2.3.3, only one part of the architecture was explained. In this section a top-level representation, illustrated in Figure 3.7, and remaining blocks functionality and architecture are detailed.

$Z_{n}$  Packet Detection  $A\omega$  Phase Estimation Despreading  $P_{n}$  NCO  $P_{n}$  Estimation  $P_{n}$

Figure 3.7 - Digital baseband processor architecture

Source: Chen and Ma (2008)

After the receiver wake-up, only the Packet Detection block is active. Its function is to detect the preamble, to estimate the carrier frequency offset ( $\Delta\omega$ ), and to determine the exact sample in which the symbol started – timing estimation. The start of preamble sample is found through a peak caused by a cross-correlation of input signal and preamble. Since there are 8 equals and successive symbols, the block produces up to 8 valid peaks, depending on the packet frame position in the instant the receiver wakes-up. The block considers a valid packet after three consecutive peaks, when it enables the remaining blocks and disables itself. For more detail of the algorithm and architecture of this block, please refer to subsection 2.3.3.

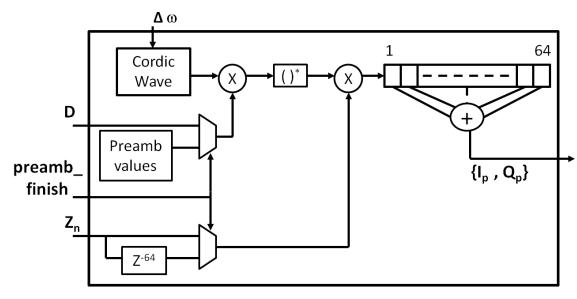

Phase Estimation block, illustrated in Figure 3.8, uses a preamble look-up table ( $P_{n+k}$ ), a wave signal generator, multipliers, conjugate block, an average of 64 samples, and arctan function to track the phase of the input signal.