## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

#### DALTON MARTINI COLOMBO

## Design of analog integrated circuits aiming characterization of radiation and noise

Thesis proposal presented in partial fulfillment of the requirements for the degree of doctorate in Microelectronics

Advisor: Prof. Dr. Gilson Wirth Co-Advisor: Prof. Dr. Sergio Bampi

## CIP - CATALOGAÇÃO NA PUBLICAÇÃO

#### Colombo, Dalton Martini

Design of analog integrated circuits aiming characterization of noise and radiation / Dalton Martini Colombo – Porto Alegre: Programa de Pós-Graduação em Microeletrônica, 2015.

92 f.:il.

Thesis (Doctorate) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica. Porto Alegre, BR – RS, 2015. Advisor: Gilson Wirth; Co-Advisor: Sergio Bampi.

1. Ruído Flicker. 2. Radiação 3. Referências de tensão. I. Wirth, Gilson, II. Bampi, Sergio.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Vladimir Pinheiro do Nascimento

Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb

Coordenador do PGMICRO: Prof. Fernanda Gusmão de Lima Kastensmidt

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

To Maria Aparecida Martini Colombo, Decio Colombo e Allan Martini Colombo

#### **ACKNOWLEDGEMENTS**

Aos meus pais, Maria Aparecida Martini Colombo, Decio Colombo, e meu irmão, Allan Martini Colombo por todo amor e apoio que sempre me deram.

Meu orientador Prof. Gilson Wirth, pelas várias oportunidades que me foram concedidas, apoio e pela confiança em mim depositada. Meu co-orientador, Prof. Sergio Bampi por todo apoio, motivação e suporte durante essa jornada.

À Maíra Malinoski, por todo amor, companheirismo e motivação na reta final do trabalho.

Ao André Luís Rodeguiero Rosa e Felipe Werle pela amizade, companheirismo e por todo apoio no término do projeto do chip fabricado em 130 nm.

Ao Alan Rossetto, pelo bom trabalho de organização e preparação do experimento de radiação realizado em IEAv (Instituto de Estudos Avançados) - Departamento de Ciência e Tecnologia Aeroespacial (DCTA), em São José dos Campos, Brasil.

Fernando Paixão Cortes, Antonio David Souza, Prof. Luiz Fernando Ferreira, Juan Pablo Brito, Arthur Liraneto, Luciano de Paula, Eduardo Conrad e Henrique Pimentel, pela amizade e apoio durante o doutorado, e pelas horas dividindo o mesmo laboratório (#110).

Ao Francisco Osman pela amizade e nossas idas ao forró. Ao amigo Alexandre Simionovski pelo suporte no projeto da PCB.

Fabrício Lara e Gabriela Furtado que fizeram bom trabalho de medição do circuitos.

À Estefânia Aquila, minha professora, que sempre me ensinou muito.

Rafael Cantalice, Gabriela Girardi, Rafael Laufer, Renata Sanfins de Carvalho, Antonio Carlos Beck, Renato Campana, Tatiana Bernardi, Carlo Bernardi, Angélica Anjos, Fabricío Mattos, Fernanda Borba, Vanderlei Borba e Marta Borba, Frederico Möller, Rafael Soares, Ismael Fraga, Dean Karolak, Jorge dos Santos, Sandro Binsfeld, Giovano Camaratta, Moacir Monteiro, André Constantino e Valeska, Mauricio Bartok, Germán Fierro, Prof. Ricardo Reis, Prof. Eric Fabris, Prof. Henri Boudinov, NSCAD, biblioteca e funcionários do Instituto Informática.

Ao Prof. Hamilton Klimach, Laurent Corcelle, Prof. Luiz Fernando Ferreira e Prof. Tiago Balen, por todas contribuições e revisão desse trabalho.

As agências de fomento, CNPq e CAPES, pois sem o auxílio financeiro este trabalho não seria possível.

#### In English... I'm very grateful to:

Prof. Christian Fayomi from Université du Québec à Montréal (UQAM), Canada. Working as a visitor researcher in his laboratory was really important to my personal and professional development.

Purushothaman Srinivasan, for our research project at Texas Instruments, USA, and all his support during my stay in Dallas.

Django Trombley, Andrew Marshall, Richard Taylor and Xin Zhang for all important support during my work at Texas Instruments.

Michelle Adame, Neil Dalal, Lihn Pham, Andrew Whitcomb, Mylinh Luong, Geneviève Leblanc, Hugues Lemarseillais, Jayanta Baral, special people who made my life happier while far away from Brazil.

#### **ABSTRACT**

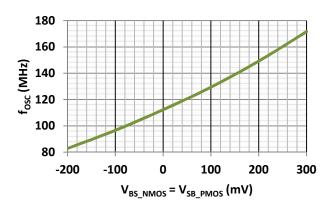

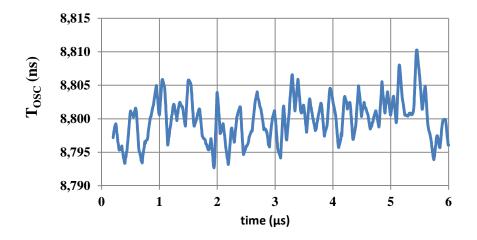

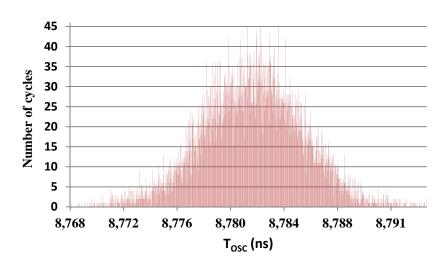

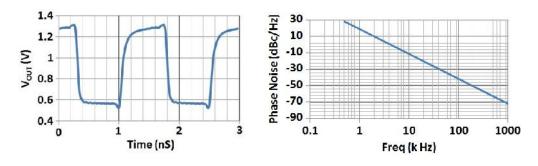

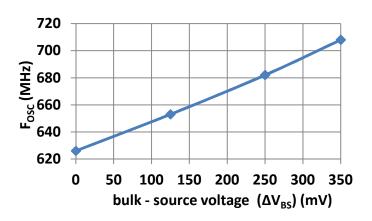

This thesis is focused on two challenges faced by analog integrated circuit designers when predicting the reliability of transistors implemented in modern CMOS processes: radiation and noise. Regarding radiation, the concern of this work is the Total Ionizing Dose (TID): accumulation of ionizing dose deposited (electrons and protons) over a long time in insulators leading to degradation of electrical parameters of transistors (e.g. threshold voltage and leakage). This work presents a case-study composed by bandgap-based and threshold voltagebased voltage reference circuits implemented in a commercial 130 nm CMOS process. A chip containing the designed circuits was irradiated through -ray Cobalt source (60 Co) and the impact of TID effects up to 490 krad on the output voltages is presented. It was found that the impact of radiation on the output voltage accuracy was similar or more severe than the variation caused by the process variability for most of the case-study circuits. For the bandgap-based reference implemented using thin-oxide and thick-oxide transistors, TID effects result in a variation of the output voltage of 5.5 % and 12%, respectively. For the threshold voltage references, the output variation was between 2% and 15% depending on the circuit topology. Regarding noise, the concern of this work is the transistor flicker noise under cyclostationary operation, that is, when the voltage at transistor gate terminal is constantly varying over time. Under these conditions, the flicker noise becomes a function of V<sub>GS</sub>; and its is not accurately predicted by traditional transistor flicker noise models. This thesis presents a case-study composed by voltage oscillators (inverter-based ring and LC-tank topologies) implemented in 45 and 130 nm CMOS processes. The oscillation frequency and its dependency on the bulk bias were investigated. Considering the ring-oscillator, the average oscillation frequency variation caused by supply voltage and bulk bias variation are 495 kHz/mV and 81 kHz/mV, respectively. The average oscillation frequency is 103.4 MHz for a supply voltage of 700 mV, and the measured averaged period jitter for 4 measured samples is 7.6 ps. For the LC-tank, the measured oscillation frequency was 2.419 GHz and the total frequency variation considering 1 V of bulk bias voltage was only  $\sim 0.4$  %.

**Keywords:** Flicker noise. RTS noise. Radiation. Total dose effects. Voltage reference. oscillators. LC-tank. Bandgap. Threshold voltage.

# PROJETO DE CIRCUITS INTEGRADOS ANALÓGICOS VISANDO CARACTERIZAÇÃO DE RUÍDO E RADIAÇÃO

Esta tese de doutorado trata de dois desafios que projetistas de circuitos integrados analógicos enfrentam quando estimando a confiabilidade de transistores fabricados em modernos processos CMOS: radiação e ruído flicker. Em relação a radiação, o foco desde trabalho é a Dose Total Ionizante (TID): acumulação de dose ionizante (elétrons e prótons) durante um longo período de tempo nas camadas isolantes dos dispositivos, então resultando na degradação dos parâmetros elétricos (por exemplo, a tensão de limiar e as correntes de fuga). Este trabalho apresenta um caso de estudo composto por circuitos referência tensões de baseados na tensão de bandgap e na tensão de limiar dos transistores. Esses circuitos foram fabricados em uma tecnologia comercial CMOS de 130 nm. Um chip contendo os circuitos foi irradiado usando raio gama de uma fonte de cobalto (60 Co), e o impacto dos efeitos da radiação até uma dose de 490 krad nas tensões de saída é apresentado. Foi verificado que o impacto da radiação foi similar ou até mesmo mais severo que os efeitos causados pelo processo de fabricação para a maior parte dos circuitos projetados. Para as referências baseadas na tensão de bandgap implementadas com transistores de óxido fino e grosso, a variação na tensão de saída causada pela radiação foi de 5.5% e 15%, respectivamente. Para as referências baseadas na tensão de limiar, a variação da tensão de saída foi de 2% a 15% dependendo da topologia do circuito. Em relação ao ruído, o foco desta tese é no ruído flicker do transitor MOS quando este está em operação ciclo-estacionária. Nesta condição, a tensão no terminal da porta está constantemente variando durante a operação e o ruído flicker se torna uma função da tensão porta-fonte e não é precisamente estimado pelos tradicionais modelos de ruído flicker dos transistores MOS. Esta tese apresenta um caso de estudo composto por osciladores de tensão (topologia baseada em anel e no tanque LC) projetados em processos 45 e 130 nm. A frequência de oscilação e sua dependência em relação à polarização do substrato dos transistores foi investigada. Considerando o oscilador em anel, a média da variação da frequência de oscilação causada pela variação da tensão de alimentação e da polarização do substrato foi 495 kHz/mV e 81 kHz/mV, respectivamente. A média da frequência de oscilação é de 103,4 MHz e a média do jitter medido para 4 amostras é de 7.6 ps. Para o tanque LC, a frequência de oscilação medida é de 2,419 GHz e sua variação considerando 1 V de variação na tensão de substrato foi de aproximadamente 0,4 %.

Palavras Chave: Ruído *flicker*. Radiação. Dose Total Ionizante. Referências de tensão.

## LIST OF FIGURES

| Figure 1.1- NMOS with radiation-induced positive charges and interface traps                                                                               |                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Figure 1.3 - Defects (dangling bonds) at Si-SiO <sub>2</sub>                                                                                               |                  |

| Figure 1.4 - Flicker noise spectrum                                                                                                                        | 27               |

| Figure 1.5 - RTN noise on the design margin of CMOS SRAM                                                                                                   | 28               |

| Figure 2.2 - ΔV <sub>TH_TID</sub> as a function of time after irradiation pulse                                                                            | 35               |

| Figure 2.3 - Defects at Si/SiO <sub>2</sub> interface structure                                                                                            | 36               |

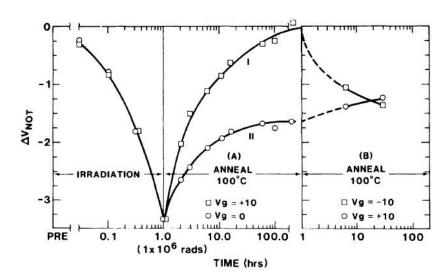

| Figure 2.4 - Shift on $V_{TH}$ due to oxide trapped charge ( $\Delta V_{NOT}$ )                                                                            | 38               |

| Figure 2.6 - Dangling bond and Si-H at Si-SiO <sub>2</sub> interface                                                                                       | 39               |

| Figure 2.8 - $V_{TH}$ , $\Delta V_{NOT}$ (trapped oxides) and $\Delta V_{NIT}$ (Interface state charge)                                                    | 41               |

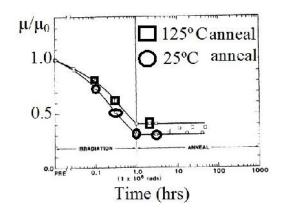

| Figure 2.10 - Mobility ratio before and after irradiation ( $\mu/\mu_0$ )                                                                                  |                  |

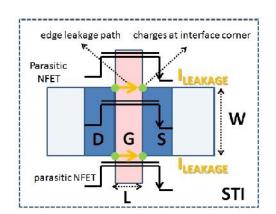

| Figure 2.11 - Top view of NMOS with STI and the edge leakage path                                                                                          | 45               |

| Figure 2.12 - $I_{OFF}$ at $V_{GS} = 0$ of NMOS irradiated under three bias conditions                                                                     | 46               |

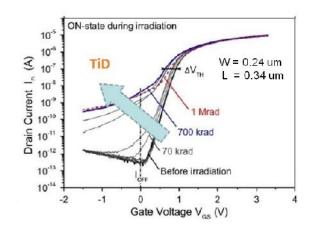

| Figure 2.13 - $I_{DS}$ versus $V_{GS}$ of NMOS (W/L = 0.24 $\mu$ m/0.34 $\mu$ m) at several total dose step                                                | ps46             |

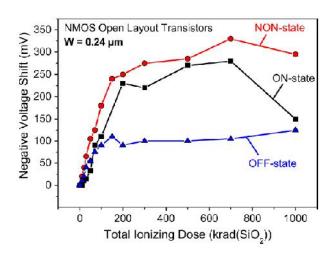

| Figure 2.14 - Negative shift on V <sub>TH</sub> of NMOS for 3 bias conditions                                                                              | 47               |

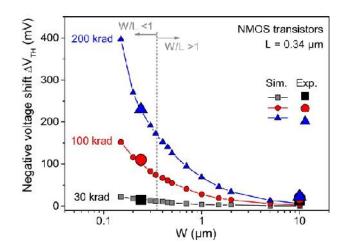

| Figure 2.15- Negative shift on V <sub>TH</sub> of NMOS as a function of W                                                                                  | 47               |

| Figure 2.16 - Top view of enclosed layout transistor                                                                                                       | 52               |

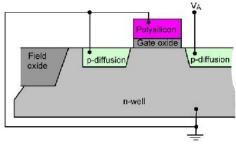

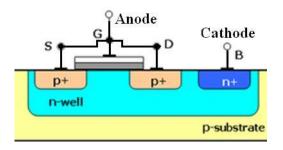

| Figure 2.17 - Cross section of dynamic-threshold MOS diode                                                                                                 | 53               |

| Figure 3.1 - Trap instantaneous occupancy after turn-on of V <sub>GS</sub>                                                                                 | 56               |

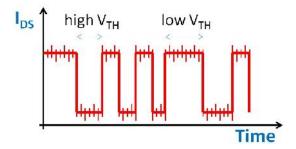

| Figure 3.2 - Impact of single trap on I <sub>DS</sub> for a MOSFET (RTS noise)                                                                             | 57               |

| Figure 3.3 - Power spectral density for a single trap                                                                                                      | 57               |

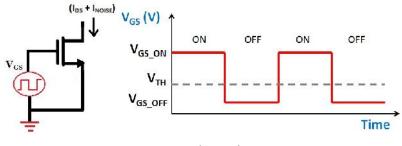

| Figure 3.4 - Switching bias applied in the transistor gate                                                                                                 | 58               |

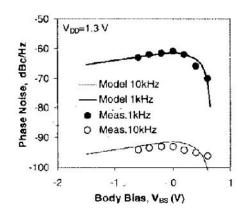

| Figure 3.5 - Phase noise of ring-oscillator as a function of V <sub>BS</sub>                                                                               | 61               |

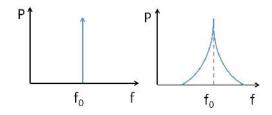

| Figure 3.6- Power spectrum for ideal oscillator (left) and with phase noise (right)                                                                        | 66               |

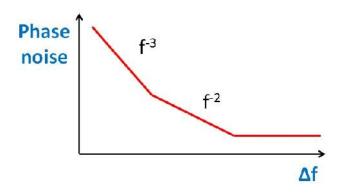

| Figure 3.7- Typical phase noise of a LC oscillator versus offset from carrier                                                                              | 69               |

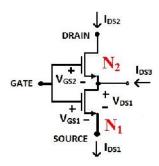

| Figure 4.1- Self cascode transistor                                                                                                                        |                  |

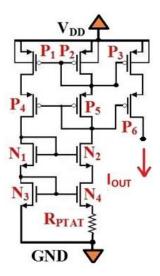

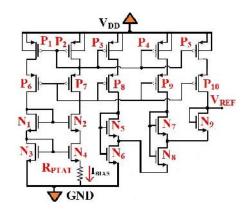

| Figure 4.2 - Current reference with PTAT TC                                                                                                                | 74               |

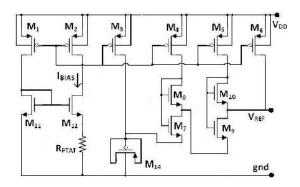

| Figure 4.3 - Low voltage Bandgap reference                                                                                                                 | 75               |

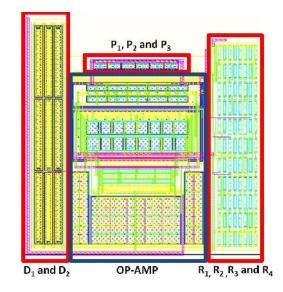

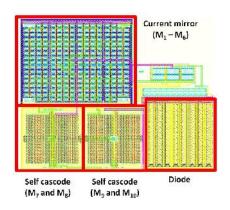

| Figure 4.4 - Layout of V <sub>REF_1</sub>                                                                                                                  |                  |

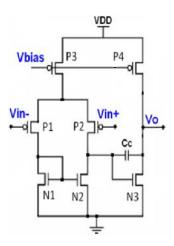

| Figure 4.5 - Two stages PMOS input amplifier                                                                                                               | 77               |

| Figure 4.6 - PMOS acting as a diode                                                                                                                        | 79               |

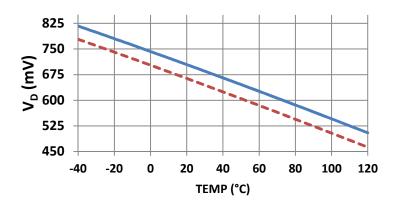

| Figure 4.7- Diode voltage vs temp for vertical PNP (line) and PMOS_diode (dotted)                                                                          | 79               |

| Figure 4.8- Simple V <sub>TH0</sub> -based voltage reference                                                                                               | 81               |

| Figure 4.9 - V <sub>TH</sub> as a function of L - reverse short channel effect                                                                             | 82               |

| Figure 4.10 - V <sub>TH0</sub> -based voltage reference (V <sub>REF_4</sub> )                                                                              | 84               |

| Figure 4.11- Layout of V <sub>REF_4</sub>                                                                                                                  |                  |

| Figure 4.12 - V <sub>TH0</sub> -based voltage reference (V <sub>REF_5</sub> )                                                                              | 86               |

| Figure 4.13 - Layout of V <sub>REF_5</sub>                                                                                                                 |                  |

| Figure 4.14 - V <sub>TH0</sub> -based voltage reference (V <sub>REF_6</sub> )                                                                              |                  |

| Figure 4.15 - Bandgap ( $V_{G0}$ ) - based voltage reference ( $V_{REF\_7}$ )                                                                              | 89               |

| Figure 4.16 - Layout of V <sub>REF_8</sub>                                                                                                                 | 90               |

| Figure 4.17- Voltage regulator using V <sub>REF_1</sub>                                                                                                    | 91               |

| Figure 4.18 - I <sub>REF</sub> vs. temperature                                                                                                             | 92               |

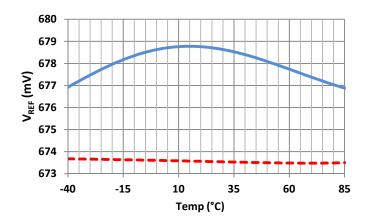

| Figure 4.19 - V <sub>REF</sub> Vs Temp: V <sub>REF</sub> 1 (dotted) and V <sub>REF</sub> 5 (line)                                                          |                  |

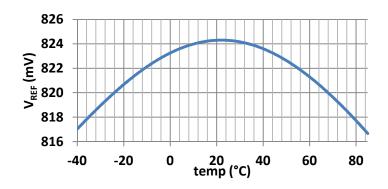

| Figure 4.20 - V <sub>REF_6</sub> vs. temperature                                                                                                           | 93               |

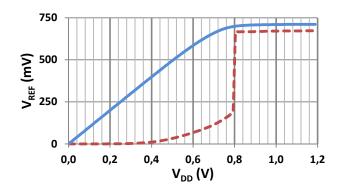

| Figure 4.21 - V <sub>REF</sub> Vs VDD: V <sub>REF_1</sub> (dotted) and V <sub>REF_5</sub> (line)                                                           | 93               |

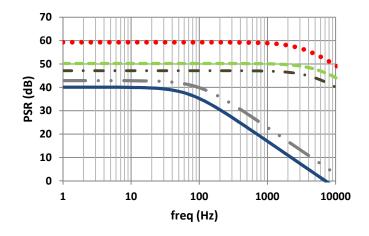

| Figure 4.22 - PSR: Highest to the lowest values: V <sub>REF_5</sub> , V <sub>REF_3</sub> , V <sub>REF_4</sub> , V <sub>REF_1A</sub> and V <sub>REF_5</sub> | <sub>_1</sub> 95 |

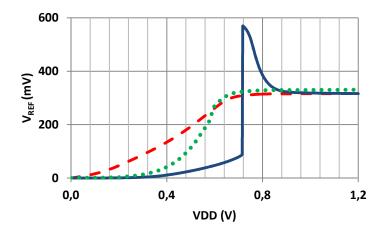

| Figure 4.23 - V <sub>REF</sub> vs. VDD: V <sub>REF_1A</sub> (line), V <sub>REF_3</sub> (broken line) and V <sub>REF_4</sub> (dotted)                       |                  |

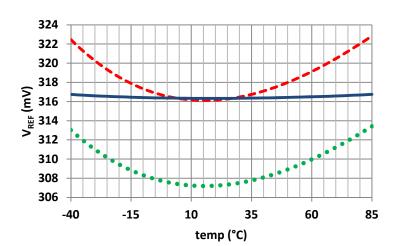

| Figure 4.24 - V <sub>REF</sub> vs. temp: V <sub>REF_1A</sub> (line), V <sub>REF_3</sub> (broken line) and V <sub>REF_4</sub> (dotted) | 96  |

|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.25 - V <sub>REF</sub> vs. tem: V <sub>REF_7</sub> (line) and V <sub>REF_8</sub> (broken line)                                | 96  |

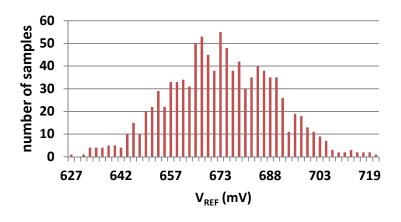

| Figure 4.26 - Histogram of V <sub>REF_1</sub> at 22 °C                                                                                | 99  |

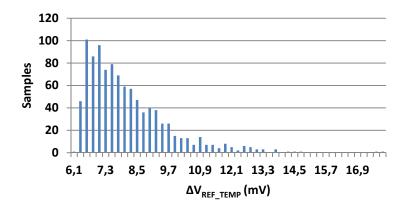

| Figure 4.27 - Histogram of $\Delta V_{REF\_TEMP}$ for $V_{REF\_3}$                                                                    | 101 |

| Figure 4.28 - Simulated V <sub>REF_4</sub> before and after TID                                                                       |     |

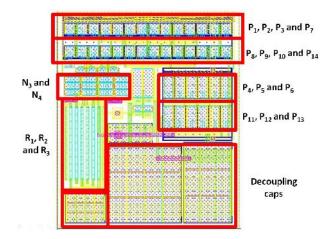

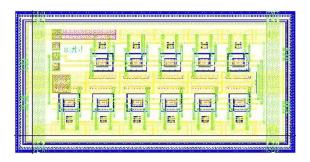

| Figure 4.29 - Layout of the integrated circuit designed in 130 nm CMOS                                                                | 103 |

| Figure 5.1: Linear model for an oscillator                                                                                            | 105 |

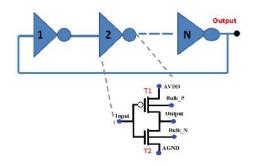

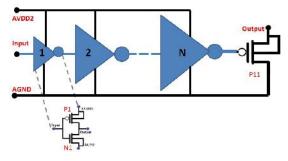

| Figure 5.2 - Ring oscillator composed by CMOS inverters                                                                               | 107 |

| Figure 5.3 - Triple well NMOS transistor                                                                                              |     |

| Figure 5.4: Output buffer composed by CMOS inverters designed in 130 nm                                                               | 109 |

| Figure 5.5: Oscillator and output buffer design in 130 nm                                                                             |     |

| Figure 5.7: Layout of the output buffer designed in 130nm process                                                                     | 109 |

| Figure 5.8 - Output buffer designed in 45 nm process                                                                                  | 110 |

| Figure 5.9 - Layout of ring oscillator designed in 45 nm process                                                                      | 110 |

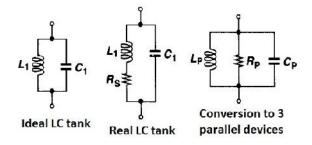

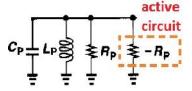

| Figure 5.9 - Ideal, realistic LC-tank and its conversion                                                                              | 111 |

| Figure 5.10 - One port oscillator                                                                                                     |     |

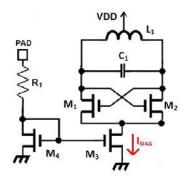

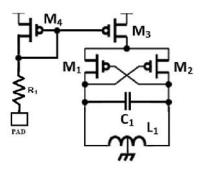

| Figure 5.11- NMOS cross couple LC-tank oscillator                                                                                     | 113 |

| Figure 5.12- PMOS cross couple LC-tank oscillator                                                                                     |     |

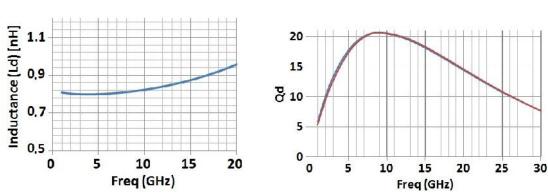

| Figure 5.14 - Simulated inductance (Ld) and quality factor (Qd)                                                                       |     |

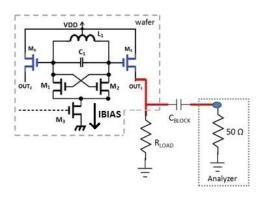

| Figure 5.15. NMOS cross-coupled LC tank oscillator with source follower                                                               |     |

| Figure 5.16 - Layout of OSCN3 (left) and OSCP1 (right)                                                                                | 121 |

| Figure 5.17 - Layout of the gm-pair of OSCP1                                                                                          |     |

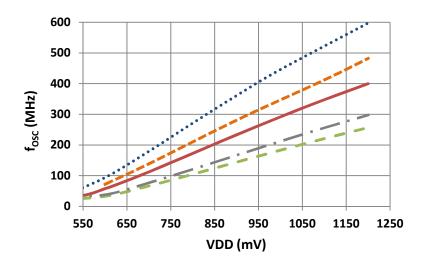

| Figure 5.18 - f <sub>OSC</sub> vs. VDD using corner models: FF (dots), FS (broken line), TT (line)                                    |     |

| (line and dots), SS (broken line)                                                                                                     |     |

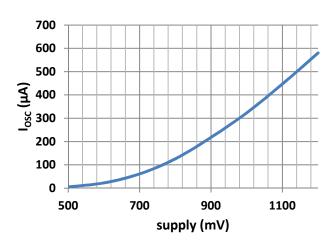

| Figure 5.19 - I <sub>OSC</sub> (μA) vs. supply (mV)                                                                                   |     |

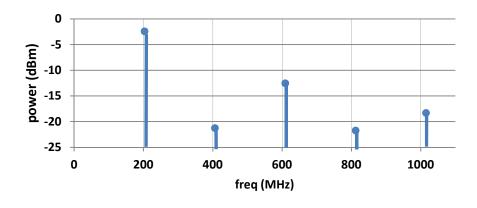

| Figure 5.20 - Simulated power spectrum (dBm) for the ring-oscillator                                                                  |     |

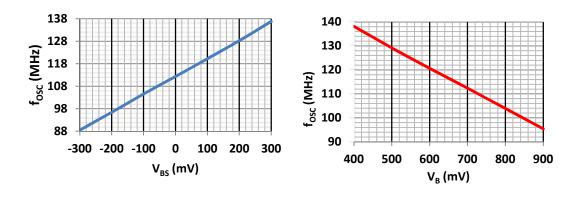

| Figure 5.21 - Simulated effect of bulk bias on f <sub>OSC</sub> : NMOS (left) and PMOS (right)                                        |     |

| Figure 5.22 - Simulated effect of bulk bias on $f_{OSC}$ for both devices simultaneously                                              |     |

| Figure 5.23 - Simulated Phase noise vs. offset frequency for 130-nm ring oscillator                                                   |     |

| Figure 5.24 - T <sub>OSC</sub> (ns) vs. time (μs) using transient noise analysis                                                      |     |

| Figure 5.25 - T <sub>OSC</sub> (ns) vs. number of cycles                                                                              |     |

| Figure 5.26 - Test bench for the ring-oscillator simulation                                                                           |     |

| Figure 5.27 - Transient simulation (left) and phase noise analysis (right)                                                            |     |

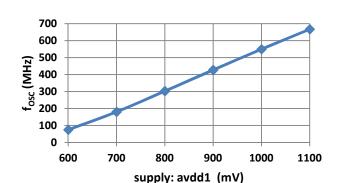

| Figure 5.28 - f <sub>OSC</sub> as a function of VDD for 45-nm ring oscillator                                                         |     |

| Figure 5.29 - Test bench for transient and phase noise simulation                                                                     |     |

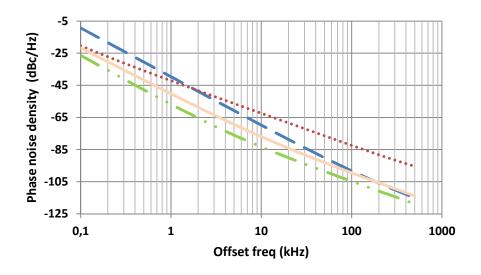

| Figure 5.30- Phase noise of OSC <sub>N1</sub> (line), OSC <sub>N2</sub> (dots), OSC <sub>N3</sub> (broken line) and OSC               |     |

| (line plus two points)                                                                                                                |     |

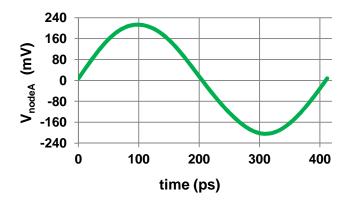

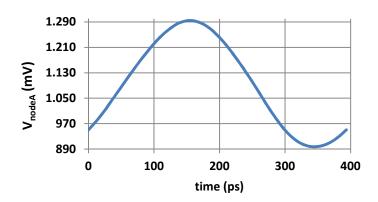

| Figure 5.31 - Voltage at the input of source follower OSC <sub>P1</sub> (transient analysis)                                          |     |

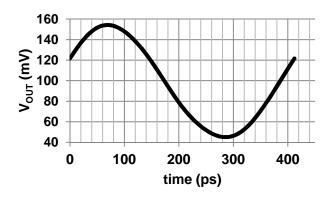

| Figure 5.32 - Output voltage of OSC <sub>P1</sub> (transient analysis)                                                                |     |

| Figure 5.33 - Voltage at the input of source follower for OSC <sub>N3</sub> (transient analysis)                                      |     |

| Figure 5.34 - Output voltage of OSC <sub>N3</sub> (transient analysis)                                                                |     |

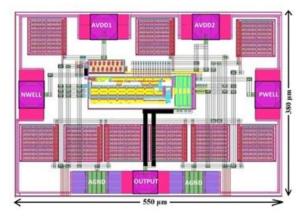

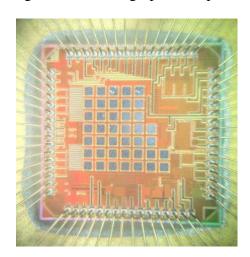

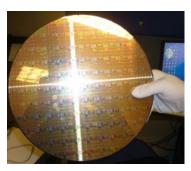

| Figure 6.1 - Micrograph of chip                                                                                                       |     |

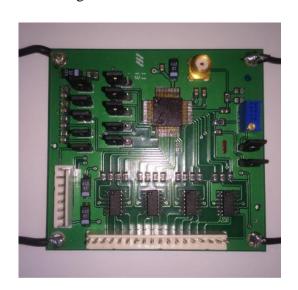

| Figure 6.2 - Test board                                                                                                               |     |

| Figure 6.3 - I <sub>REF</sub> at 20 °C for 10 samples                                                                                 |     |

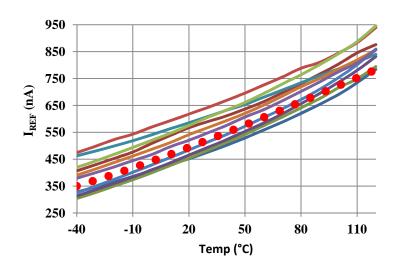

| Figure 6.4 - I <sub>REF</sub> vs temp for 10 samples (lines) and simulation (dotted)                                                  |     |

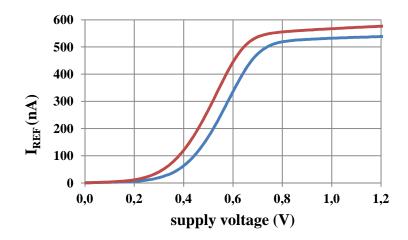

| Figure 6.5 - I <sub>REF</sub> vs supply voltage for 2 measured samples                                                                |     |

| Figure 6.6 - V <sub>REF_1</sub> at 20°C for ten samples                                                                               |     |

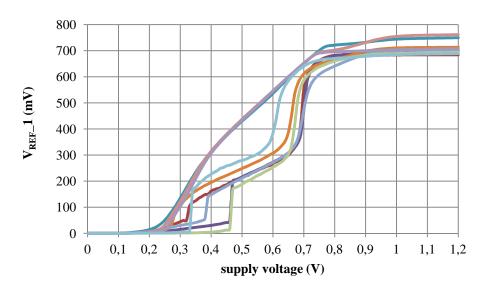

| Figure 6.7 - Measured V <sub>REF_1</sub> vs supply voltage                                                                            |     |

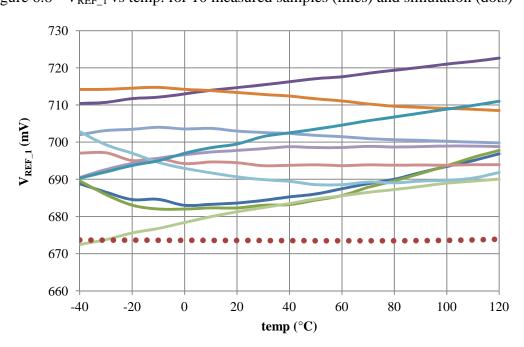

| Figure 6.8 - V <sub>REF_1</sub> vs temp. for 10 measured samples (lines) and simulation (dots)                                        |     |

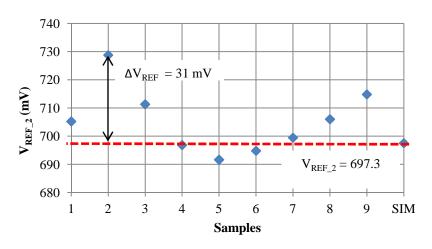

| Figure 6.9 - Measured V <sub>REF_2</sub> at 20°C for 9 samples                                                                        | 145 |

|                                                                                                                                       |     |

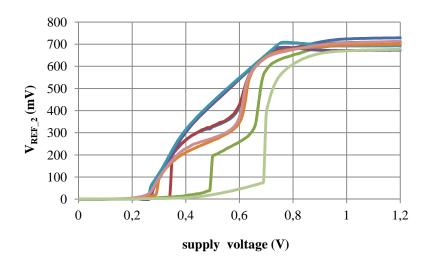

| Figure 6.10 - Measured V <sub>REF_2</sub> vs supply voltage                                     | 145 |

|-------------------------------------------------------------------------------------------------|-----|

| Figure 6.11 - V <sub>REF_2</sub> vs temp. for 9 measured samples (lines) and simulation (dots)  | 146 |

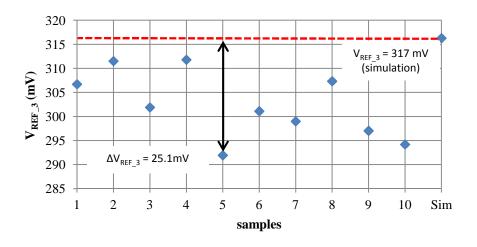

| Figure 6.12 - V <sub>REF_3</sub> at 20°C for 10 samples                                         |     |

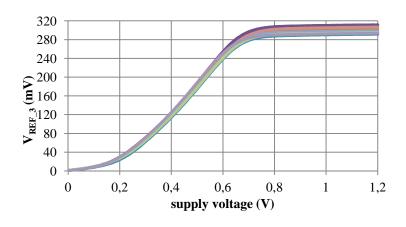

| Figure 6.13 - Measured V <sub>REF_3</sub> vs supply voltage for 10 samples                      | 148 |

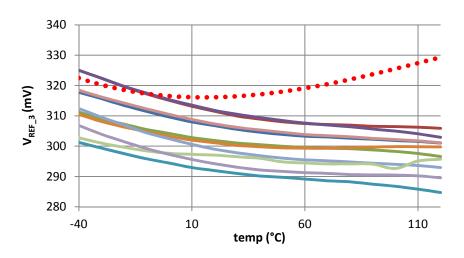

| Figure 6.14 - V <sub>REF_3</sub> vs temp. for 10 measured samples (lines) and simulation (dots) | 148 |

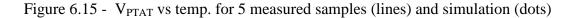

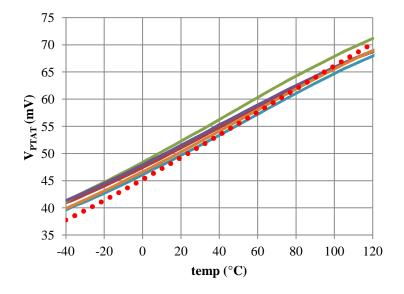

| Figure 6.15 - V <sub>PTAT</sub> vs temp. for 5 measured samples (lines) and simulation (dots)   | 150 |

| Figure 6.16 - V <sub>CTAT</sub> vs temp. for 5 measured samples (lines) and simulation (dots)   | 151 |

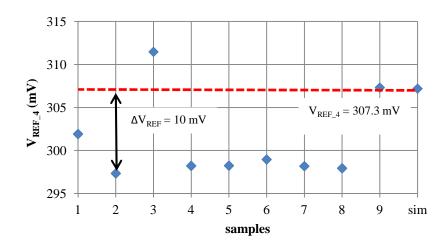

| Figure 6.17- Measured V <sub>REF_4</sub> at 20°C for 9 samples                                  | 151 |

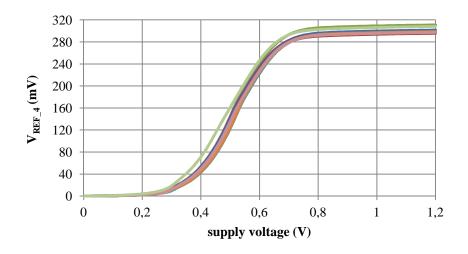

| Figure 6.18 - Measured V <sub>REF_4</sub> vs supply voltage for 9 samples                       | 152 |

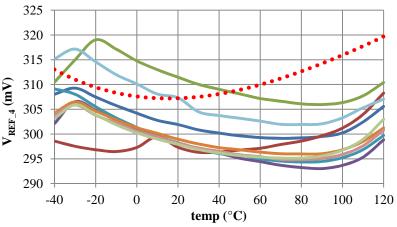

| Figure 6.19 - V <sub>REF_4</sub> vs temp. for 9 measured samples (lines) and simulation (dots)  | 153 |

| Figure 6.20 - V <sub>REF_5</sub> at 20°C for 10 samples                                         | 155 |

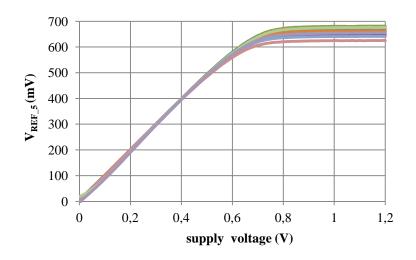

| Figure 6.21- Measured V <sub>REF_5</sub> vs supply voltage for 10 samples                       | 155 |

| Figure 6.22 - V <sub>REF_5</sub> vs temp. for 10 measured samples (lines) and simulation (dots) | 156 |

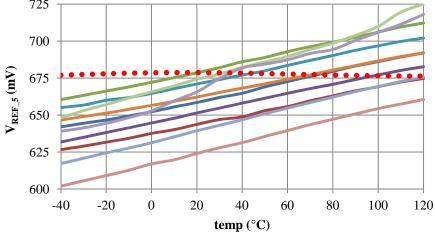

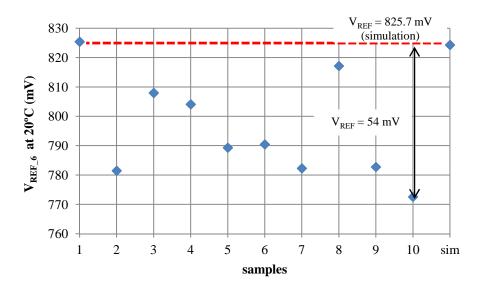

| Figure 6.23 - V <sub>REF_6</sub> at 20°C for 10 samples                                         | 157 |

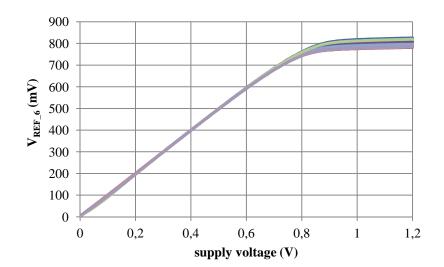

| Figure 6.24 - Measured V <sub>REF_6</sub> vs supply voltage for 10 samples                      | 158 |

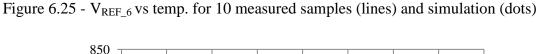

| Figure 6.25 - V <sub>REF_6</sub> vs temp. for 10 measured samples (lines) and simulation (dots) | 158 |

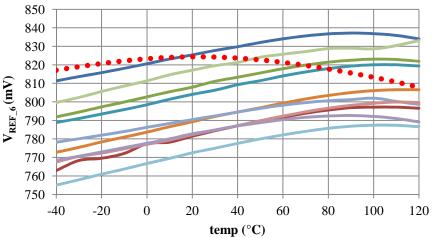

| Figure 6.28 - V <sub>DIODE</sub> as a function of temp. for 5 samples and simulation (dotted)   | 160 |

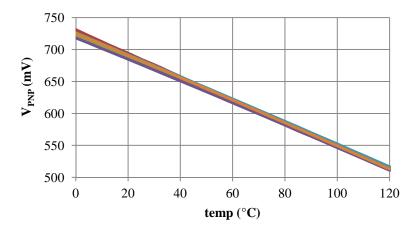

| Figure 6.27 - V <sub>PMOS</sub> as a function of temp. for 5 samples and simulation (dotted)    |     |

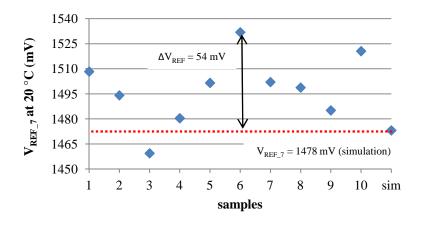

| Figure 6.28 - V <sub>REF_7</sub> at 20°C for 10 samples                                         | 161 |

| Figure 6.29 - V <sub>REF_8</sub> at 20°C for 10 samples                                         | 162 |

| Figure 6.30 - Measured $V_{REF\_7}$ vs supply voltage for 10 samples                            | 163 |

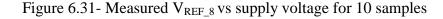

| Figure 6.31- Measured V <sub>REF_8</sub> vs supply voltage for 10 samples                       | 163 |

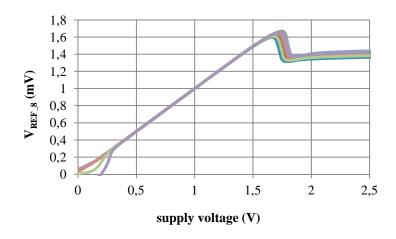

| Figure 6.32 - $V_{REF_{-}7}$ vs temp. for 10 measured samples (lines) and simulation (dots)     | 164 |

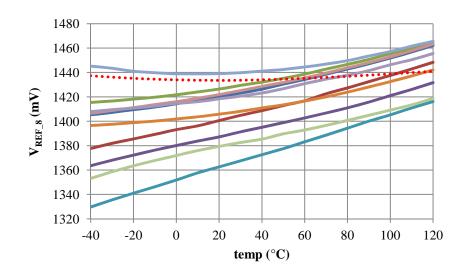

| Figure 6.33 - $V_{REF\_8}$ vs temp. for 10 measured samples (lines) and simulation (dots)       | 166 |

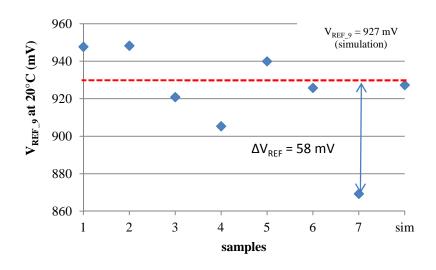

| Figure 6.34 - V <sub>REF_9</sub> at 20°C for 7 samples                                          | 167 |

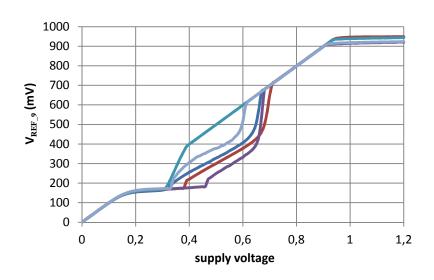

| Figure 6.35 - V <sub>REF_9</sub> vs supply voltage for 5 samples                                | 167 |

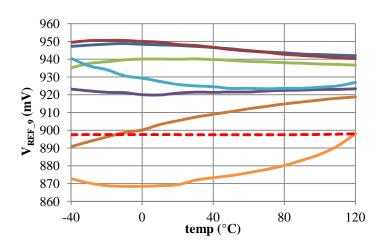

| Figure 6.36 - V <sub>REF_9</sub> vs temp. for 7 measured and simulation (dotted)                |     |

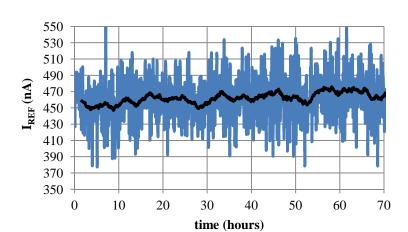

| Figure 6.38 - I <sub>REF</sub> vs time (hours): moving average (black) and raw data (blue)      | 169 |

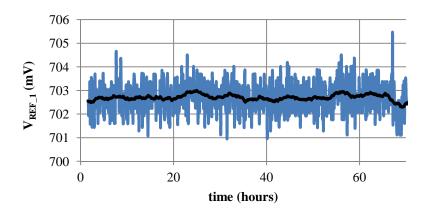

| Figure 6.39 - $V_{REF_1}$ vs time (hours): moving average (black) and raw data (blue)           |     |

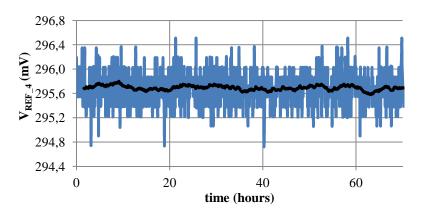

| Figure 6.40 - $V_{REF\_4}$ vs time (hours): moving average (black) and raw data (blue)          | 170 |

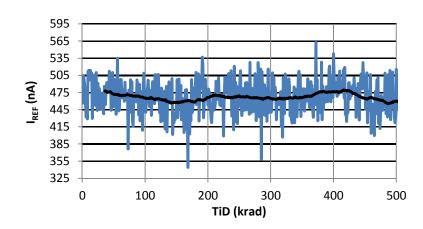

| Figure 6.41 - I <sub>REF</sub> vs TID (krad)                                                    | 171 |

| Figure 6.42 - V <sub>REF_1</sub> vs TID (krad)                                                  |     |

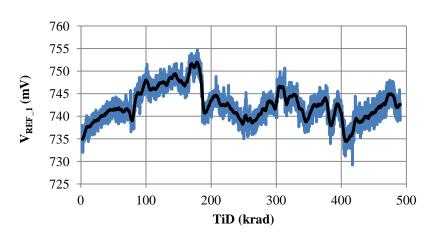

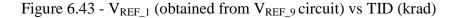

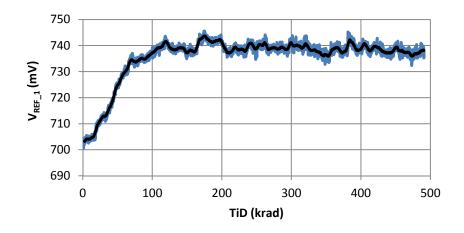

| Figure 6.43 - V <sub>REF_1</sub> (obtained from V <sub>REF_9</sub> circuit) vs TID (krad)       | 172 |

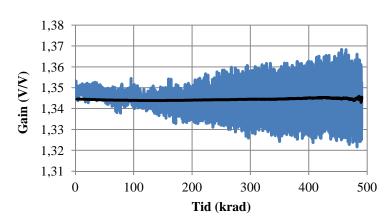

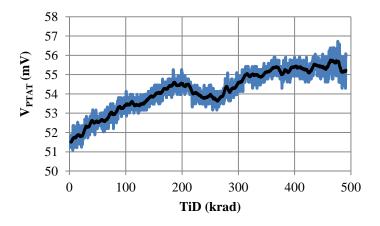

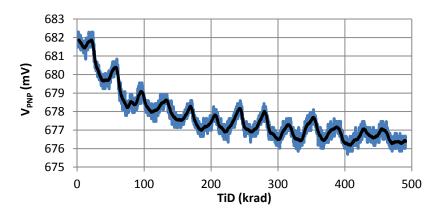

| Figure 6.46 - V <sub>PTAT</sub> vs TID (krad)                                                   |     |

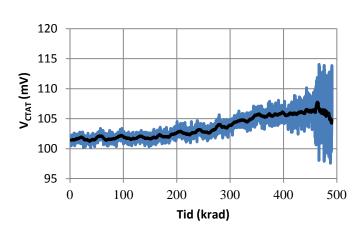

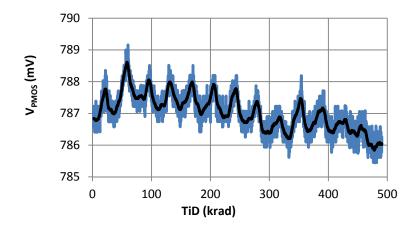

| Figure 6.47 - V <sub>CTAT</sub> vs TID (krad)                                                   |     |

| Figure 6.48 -V <sub>REF_4</sub> vs TID (krad)                                                   |     |

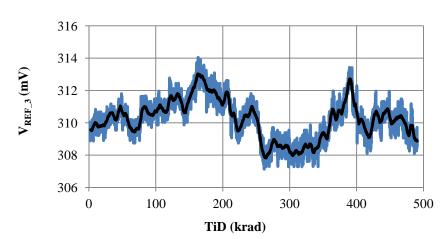

| Figure 6.49 - V <sub>REF_3</sub> vs TID (krad)                                                  |     |

| Figure 6.50 - V <sub>CTAT</sub> (V <sub>PNP</sub> ) vs TID (krad)                               |     |

| Figure 6.51 - V <sub>CTAT</sub> (V <sub>PMOS</sub> ) vs TID (krad)                              |     |

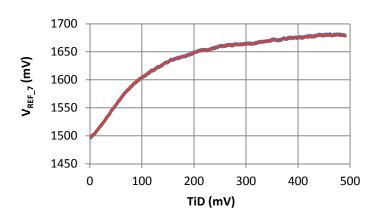

| Figure 6.52 - V <sub>REF_7</sub> vs TID (krad)                                                  |     |

| Figure 6.53 - V <sub>REF_8</sub> vs TID (krad)                                                  |     |

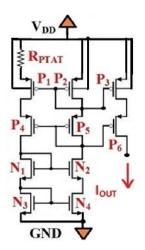

| Figure 6.54 - Modification of the PTAT current source                                           |     |

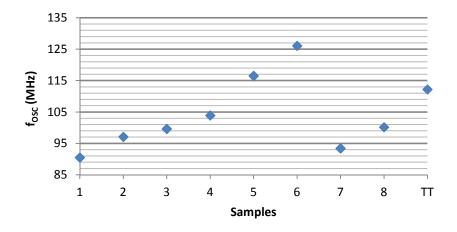

| Figure 7.1 - Measured $f_{OSC}$ (MHz) for 8 samples with $VDD_{RING} = 700 \ mV$                |     |

| Figure 7.2- Measured $f_{OSC}$ (MHz) for 8 samples with $VDD_{RING} = 800 \text{ mV}$           |     |

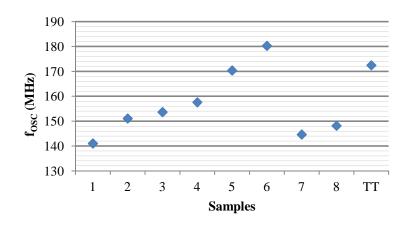

| Figure 7.3 - Measured $f_{OSC}$ vs $VDD_{RING}$ for 8 oscillator samples and simulation (dots)  |     |

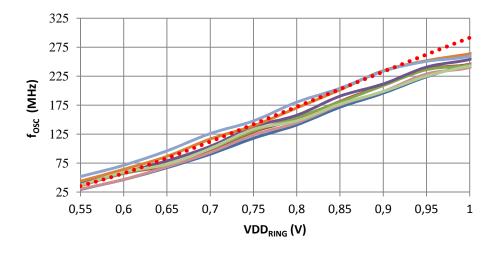

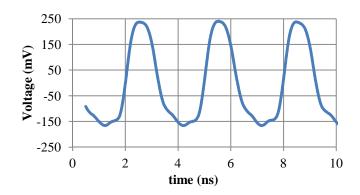

| Figure 7.4 - Measured output voltage vs time for $VDD_{RING} = 1.2 \text{ V}$ (sample # 1)      |     |

| Figure 7.5 - Measured output voltage vs time for $VDD_{RING} = 0.8 \text{ V}$ (sample # 1)      |     |

| Figure 7.6 - Power spectrum for $VDD_{RING} = 1.2 \text{ V (sample # 1)}$                       |     |

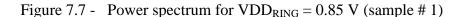

| Figure 7.7 - Power spectrum for $VDD_{RING} = 0.85 \text{ V}$ (sample # 1)                      |     |

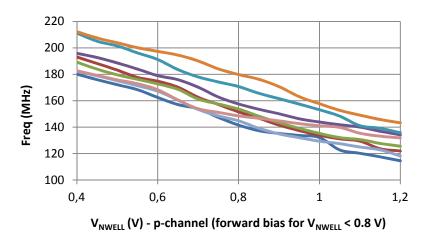

| Figure 7.8 - Measured $f_{OSC}$ vs $V_{BS}$ (n-channel) for 8 samples. $VDD_{RING} = 0.8 \ V$   | 191 |

| Figure 7.9 - Measured $f_{OSC}$ vs $V_{NWELL}$ (p-channel) for 8 samples (VDD <sub>RING</sub> = 0.8 V)   | 191 |

|----------------------------------------------------------------------------------------------------------|-----|

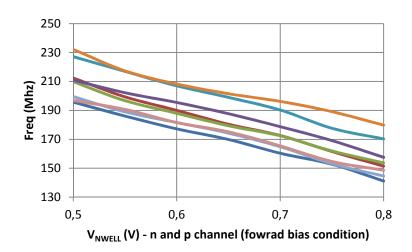

| Figure 7.10 - Measured $f_{OSC}$ vs $V_{NWELL}$ (both bias) for 8 samples (VDD <sub>RING</sub> = 0.8 V)  | 192 |

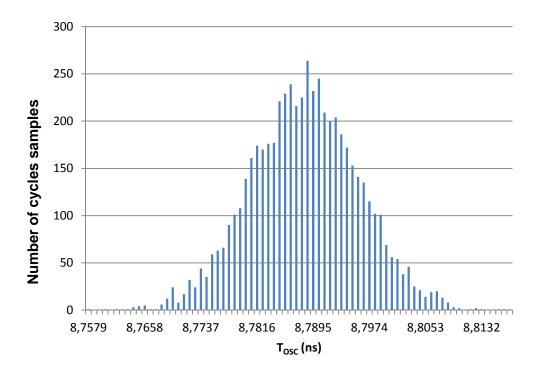

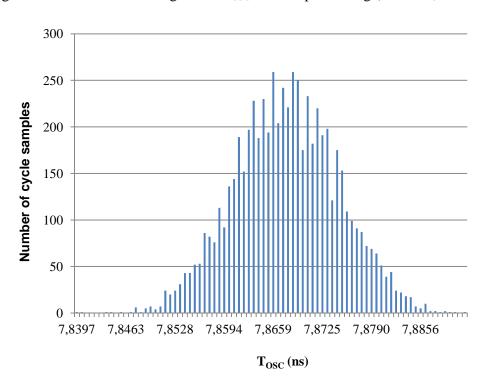

| Figure 7.11 - Measured histogram of $T_{OSC}$ for sample #5 ring (VDD <sub>RING</sub> = 0.7 V)           | 193 |

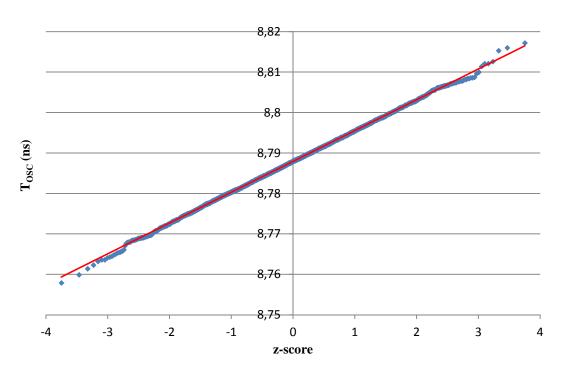

| Figure 7.12 - Normal Probability Plot ( $T_{OSC}$ ) for sample #5 ring ( $VDD_{RING} = 0.7 \text{ V}$ )  | 194 |

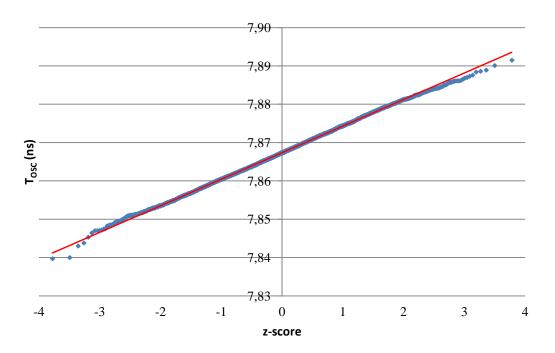

| Figure 7.13 - Measured histogram of $T_{OSC}$ for sample #6 ring (VDD <sub>RING</sub> = 0.7 V)           | 195 |

| Figure 7.14 - Normal Probability Plot ( $T_{OSC}$ ) for sample # 6 ring ( $VDD_{RING} = 0.7 \text{ V}$ ) | 196 |

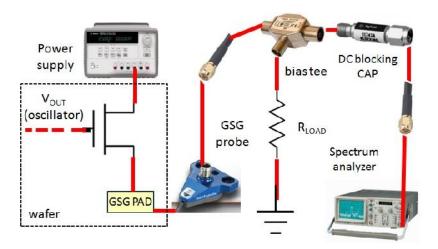

| Figure 7.20 - Block diagram of the measurement setup                                                     | 202 |

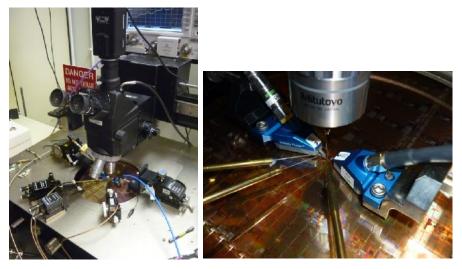

| Figure 7.21- Measurement setup: probe station, DC and GSG probes                                         | 203 |

| Figure 7.22 - Complete setup with power supply and spectrum analyzer                                     | 203 |

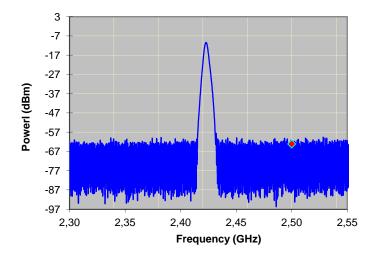

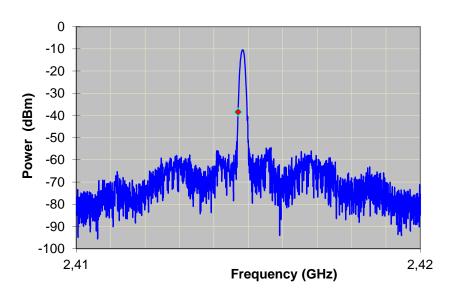

| Figure 7.23 - Power Spectrum of OSC <sub>N3</sub> (span = 250 MHz)                                       | 204 |

| Figure 7.24 - Power Spectrum of OSC <sub>N3</sub> (span = 10 MHz)                                        | 204 |

| Figure 7.26 - Measured oscillation frequency for OSC <sub>N1</sub>                                       | 205 |

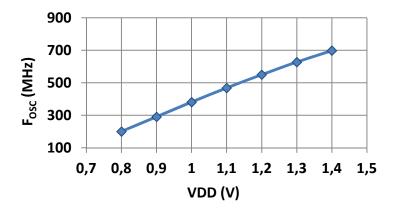

| Figure 7.27 - Measured f <sub>OSC</sub> as a function of supply for the ring-oscillator                  | 207 |

| Figure 7.29 - Measured f <sub>OSC</sub> as a function of V <sub>BS</sub> for the ring oscillator         | 207 |

| Figure A.1 - V <sub>DSAT</sub> and V <sub>EFF</sub> as a function of IC                                  | 231 |

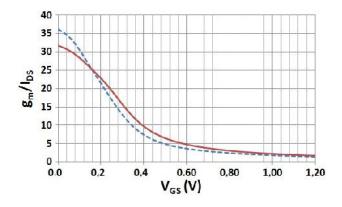

| Figure A.2 - Simulated g <sub>m</sub> /I <sub>DS</sub> for NMOS (dotted line) and PMOS (line)            | 231 |

|                                                                                                          |     |

## LIST OF TABLES

| Table 2.1: TID on $V_{TH\_TID}(mV)$ , $I_{DS\_TID}(\%)$ and $I_{LEAKAGE}$                                     | 50  |

|---------------------------------------------------------------------------------------------------------------|-----|

| Table 2.2: Impact of TID on $V_{REF}$ ( $V_{TH\_TID}$ ) of voltage references                                 | 54  |

| Table 4.1: Devices size of I <sub>REF</sub>                                                                   |     |

| Table 4.2: Devices size of V <sub>REF_1</sub>                                                                 | 77  |

| Table 4.3: Devices size of operational amplifier                                                              |     |

| Table 4.4: Devices size of V <sub>REF 2</sub>                                                                 |     |

| Table 4.5: Devices size of V <sub>REF_3</sub>                                                                 |     |

| Table 4.6: Devices size of V <sub>REF_4</sub>                                                                 |     |

| Table 4.7: Devices size of V <sub>REF 5</sub>                                                                 |     |

| Table 4.8: Devices size of V <sub>REF_6</sub>                                                                 |     |

| Table 4.9: Devices size of V <sub>REF 7</sub> and V <sub>REF 8</sub>                                          |     |

| Table 4.10: Simulated Performance parameters using TT models                                                  |     |

| Table 4.11: Simulated V <sub>REF</sub> and I <sub>REF</sub> using corner models                               |     |

| Table 4.12: V <sub>REF_MAX</sub> and V <sub>REF_MIN</sub> using corner models                                 |     |

| Table 4.13: Monte Carlo analysis of V <sub>REF</sub> and I <sub>REF</sub> @ 22.5 °C                           | 99  |

| Table 4.14: Monte Carlo analysis of $V_{REF\_TEMP}$ and $I_{REF\_TEMP}$                                       |     |

| Table 5.1: Devices Dimensions                                                                                 |     |

| Table 5.2: f <sub>OSC</sub> vs. supply for ring-oscillator designed in 130 nm process                         |     |

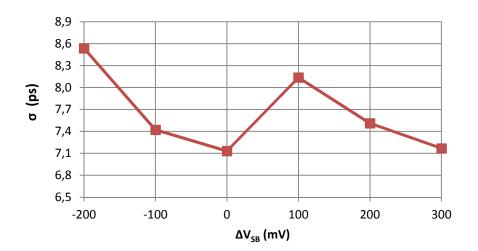

| Table 5.3: $T_{OSC}$ (ns) and sigma (ps) as a function of bulk bias ( $V_{BULK}$ )                            |     |

| Table 5.4: Post-extracted performance for 45 nm ring at VDD = 1.1 V                                           |     |

| Table 5.5: Post-extracted performance parameters as a function of $V_{BS}$ (mV)                               |     |

| Table 5.6: Post-extracted parameters for $OSC_{N1}$ , $OSC_{N2}$ , $OSC_{N3}$ and $OSC_{P1}$                  |     |

| Table 5.7: Parameters as a function of $V_{BULK}$ for $OSC_{N1}$ , $OSC_{N3}$ and $OSC_{P1}$                  |     |

| Table 5.8: Phase noise as function of $V_{BULK}$ for $OSC_{N1}$ , $OSC_{N3}$ and $OSC_{P1}$                   |     |

| Table 6.1: $I_{REF}$ (nA) at 20°C and $I_{REF}$ TEMP (nA) for 10 measured samples                             |     |

| Table 6.2: Summary of measured performance for 10 samples of I <sub>REF</sub>                                 |     |

| Table 6.3: $V_{REF_{-1}}$ (mV) at 20°C and $V_{REF_{-TEMP}}$ (mV) for 10 measured samples                     |     |

| Table 6.4: Summary of measured performance for 10 samples of $V_{REF_{-1}}$                                   |     |

| Table 6.5: $V_{REF_2}$ (mV) at 20°C and $V_{REF_{TEMP}}$ (mV) for 9 measured samples                          |     |

| Table 6.6: Summary of measured performance for 9 samples of $V_{REF_2}$                                       |     |

| Table 6.7: $V_{REF_3}$ (mV) at 20°C and $V_{REF_{1}TEMP}$ (mV) for 10 measured samples                        |     |

| Table 6.8: Summary of measured performance for 10 samples of $V_{REF_3}$                                      |     |

| • • • • • • • • • • • • • • • • • • • •                                                                       |     |

| Table 6.9: Measured V <sub>PTAT</sub> , V <sub>CTAT</sub> (mV) at 20 °C, and V <sub>TEMP</sub> (-40 to 80 °C) |     |

| Table 6.10: V <sub>REF_4</sub> (mV) at 20°C and V <sub>REF_TEMP</sub> (mV) for 9 measured samples             |     |

| Table 6.11: Summary of measured performance for 9 samples of $V_{REF\_4}$                                     |     |

| Table 6.12: $V_{REF\_5}$ (mV) at 20°C and $V_{REF\_TEMP}$ (mV) for 10 measured samples                        |     |

| Table 6.13: Summary of measured performance for 10 samples of V <sub>REF_5</sub>                              |     |

| Table 6.14: V <sub>REF_6</sub> (mV) at 20°C and V <sub>REF_TEMP</sub> (mV) for 10 measured samples            |     |

| Table 6.15: Summary of measured performance for 10 samples of V <sub>REF_6</sub>                              |     |

| Table 6.16: Measured V <sub>PNP</sub> , V <sub>PMOS</sub> (mV) at 20 °C and V <sub>TEMP</sub> (0 to 120 °C)   |     |

| Table 6.17: $V_{REF\_7}$ and $V_{REF\_8}$ at 20°C and $V_{REF\_TEMP}$ for 10 measured samples                 |     |

| Table 6.18: Measured performance for 10 samples of $V_{REF\_7}$ and $V_{REF\_8}$                              |     |

| Table 6.19: $V_{REF\_9}$ (mV) at 20°C and $V_{REF\_TEMP}$ (mV) for 7 measured samples                         |     |

| Table 6.20: TID and measured performance of $V_{REF}$ and $I_{REF}$                                           |     |

| Table 7.1: Measured Period jitter ( ) for 4 samples                                                           |     |

| Table 7.2: Measured Period jitter ( ) for sample #5 as a function of bulk bias                                |     |

| Table A.1: Process parameters for the used 130 nm CMOS process                                                |     |

| Table A.2: Sensibility analysis for V <sub>REF_4</sub> at 22.5 °C                                             | 236 |

#### LIST OF ABREVIATIONS AND ACRONYMS

BGR Bandgap voltage reference

BiCMOS Bipolar Junction Transistor and CMOS technology

TC Temperature coefficient

DTMOST Dynamic-threshold voltage MOS transistor

PTAT Proportional to absolute Temperature

PTAT<sup>2</sup> Square PTAT

CTAT Complementary to Absolute Temperature

OA Operational amplifier

VLSI Very Large Scale Integration

CMOS Complementary Metal Oxide Semiconductor

BJT Bipolar junction transistor

IC Integrated Circuit

PSR Power Supply Rejection

PSRR Power Supply Rejection Ratio

BW Bandwidth

DRAM Dynamic Random Access Memory

PLL Phase Locked Loop

TSMC Taiwan Semiconductor Manufacturing Company

DAC Digital to Analog Converter

ADC Analog to Digital Converter

VLSB Least Significant Bit

VR Voltage Reference

PLL Phase Look Loop

TC Temperature Coefficient

SNR Signal-to-noise-ratio

RMS Root-mean-square

TEMP Temperature

SoC System-on-Chip

SiP System-in-Package

VCO Voltage controlled oscillator

DCO Digital controlled oscillator

RTN Random Telegraph Noise

RTS Random Telegraph Signal

EDA Electronic Design Assistant

TID Total Ionising Dose

SEE Single Event Effects

SED Single Event Disturb

SEU Single Event Upset

SET Single Event Transient

SEL Single Event Latchup

SESB Single Event Snapback

SEGR Single Event Gate Rupture

DD Displacement Damage effects

STI Shallow Trench Isolation

TIE Time Interval Error

RBW Resolution Bandwidth

VBW Video Bandwidth

GSG Ground Signal Ground

#### LIST OF SYMBOLS

f<sub>OSC</sub> Frequency of oscillation

T<sub>OSC</sub> Period of oscillation

f<sub>C</sub> Flicker corner frequency for MOSFETs

Trap (flicker noise defect) time constant

the duration of the trapped state or the mean time before

emission occurs,

the duration of the empty state of the trap

V<sub>REF</sub> Voltage Reference

V<sub>G0</sub> Bandgap energy of silicon extrapolated for zero Kelvin

V<sub>TH0</sub> Threshold voltage of transistor extrapolated to zero Kelvin

V<sub>BE</sub> Base-emitter voltage

$\Delta V_{BE}$  The difference between the emitter-base voltages of two BJT's

$\Delta V_{REF\ TEMP}$  Variation of the  $V_{REF}$  over the operation temperature range

V<sub>LSB</sub> Voltage that corresponds to 1 bit variation in a Data Converter

U<sub>T</sub> Thermal voltage

J<sub>C</sub> Collector current density

A Geometric and fabrication process parameter

γ Temperature coefficient

α Temperature coefficient of the current source supplying the

diodes

k Boltzmann's constant

q Charge of electron

T Absolute temperature

T<sub>0</sub> Room Temperature

$\beta_F$  Common-emitter current gain

I<sub>C</sub> Collector Current

I<sub>B</sub> Base Current

I<sub>S</sub> Saturation Current

n Ratio of emitter areas

C Temperature-independent constant

D Temperature-independent constant

N Temperature-independent constant

x Arbitrary number defined by the temperature dependence of the

current forced through the collector

V<sub>GS</sub> Gate-source voltage

I<sub>D0</sub> Process constant

n' Subthreshold slope factor

W Channel Width

L Channel Length

V<sub>OV</sub> Overdrive Voltage

V<sub>OS</sub> Offset Voltage

V<sub>TH</sub> Threshold Voltage

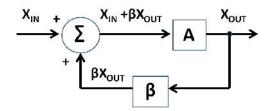

$\beta_N$  Negative feedback factor

β<sub>P</sub> Positive feedback factor

V<sub>PTAT</sub><sup>2</sup> Square proportional to the temperature voltage

I<sub>Supply</sub> Supply Current

VDD<sub>MIN</sub> Minimum supply voltage for one traditional BGR

$\Delta V_{REF}$  Variation in  $V_{REF}$

$\Delta V_{REF\_TOTAL}$  Total Variation in  $V_{REF}$

$\Delta V_{REF_i}$  Variation in  $V_{REF}$  due to each error source

V<sub>REF MONTE CARLO</sub> Output voltage from Monte Carlo Analysis

$\Delta V_{REF\_TEMP\_MONTE\_CARLO}$  Variation in  $V_{REF}$  over TEMP range from Monte Carlo Analysis

V<sub>OS\_MONTE\_CARLO</sub> Offset voltage from Monte Carlo Analysis

$V_{REF\ UPPER}$  3 $\sigma$  behavior for the damaged output voltage

$V_{REF\_DOWN}$  3 $\sigma$  behavior for the damaged output voltage

$\Delta V_{REF\_NOISE}$  Variation of output voltage due the noise

V<sub>PEAK-TO-PEAK</sub> 3 value of noise behavior

V<sub>RMS</sub> RMS noise

gm Transconductance

V<sub>FS</sub> Initial full-scale tolerance expected

V<sub>LSB</sub> Value of the least significant bit

K<sub>F</sub> Device-specific noise model constant

$\Delta V_{TH\_TID}$  Variation in the transistor threshold voltage due to TID

VDD<sub>RING</sub> Supply Voltage of the ring oscillator

## TABLE OF CONTENTS

| 1 INTRODUCTION                                                                                      | 20 |

|-----------------------------------------------------------------------------------------------------|----|

| 1.1 Motivation and Scope                                                                            | 22 |

| 1.1.1 Radiation Effects and Total Ionizing Dose                                                     |    |

| 1.1.2 Transistor flicker and random telegraph noise                                                 | 25 |

| 1.2 Objectives of this thesis                                                                       |    |

| 1.2.1 Voltage references                                                                            | 30 |

| 1.2.2 Oscillators                                                                                   | 32 |

| 1.3 Thesis Organization                                                                             | 33 |

| 2 TOTAL IONIZATION DOSE (TID)                                                                       | 34 |

| 2.1 Trapped holes, bond reformation and rebound                                                     | 34 |

| 2.2 Interface state charges                                                                         | 38 |

| 2.3 Mobility degradation                                                                            |    |

| 2.4 Impact of transistor scaling on the radiation effects                                           |    |

| 2.5 Shallow Trench Isolation, subthreshold slope and leakage                                        |    |

| 2.6 Integrated resistors and 130 nm CMOS technology                                                 |    |

| 2.6.1 Thin-oxide transistors (1.2 V) - (BOCHENEK, 2012)                                             |    |

| 2.6.2 Thick-oxide transistors (2.5 V) - (BOCHENEK, 2012)                                            |    |

| 2.7 Irradiated PMOS                                                                                 |    |

| 2.8 Irradiated BJTs                                                                                 |    |

| 2.9 Radiation hardening techniques                                                                  |    |

| 2.10 TID on the performance of voltage references                                                   | 52 |

| 3 FLICKER AND RTS NOISE                                                                             | 55 |

| 3.1 Random Telegraph Signal (RTS)                                                                   | 57 |

| 3.2 Flicker noise under switched bias (cyclostationary operation)                                   | 58 |

| 3.3 Cyclostationary operation with forward bulk bias during the off-state                           | 60 |

| 3.4 Cyclostationary operation and traditional flicker noise models                                  |    |

| 3.5 Cyclostationary noise simulation using Spectre RF                                               | 63 |

| 3.6 Transistor flicker noise model proposed by Wirth and Silva                                      |    |

| 3.7 Jitter definition                                                                               |    |

| 3.8 Phase noise definition                                                                          |    |

| 3.8.1 Phase noise measurement                                                                       |    |

| 3.8.2 Phase noise analytical models for oscillators                                                 | 68 |

| 4 VOLTAGE REFERENCES - CASE STUDY I                                                                 | 70 |

| 4.1 Concepts                                                                                        | 70 |

| 4.1.1 First-order temperature compensation                                                          | 72 |

| 4.2 I <sub>REF</sub> : PTAT Current Reference                                                       |    |

| 4.3 V <sub>REF</sub> _1: Bandgap-based reference                                                    |    |

| 4.3.1 Impact of the operational amplifier on the performance of voltage reference                   |    |

| 4.4 V <sub>REF_2</sub> : Bandgap-based reference using PMOS diode                                   |    |

| 4.5 V <sub>REF_3</sub> : Simple V <sub>TH0</sub> -based Reference                                   |    |

| 4.6 V <sub>REF</sub> _4: Alternative V <sub>TH0</sub> -based reference                              |    |

| 4.7 V <sub>REF</sub> _5: V <sub>TH0</sub> -based reference using composite transistors              |    |

| 4.8 V <sub>REF_6</sub> : Resistorless V <sub>TH0</sub> -based reference using composite transistors |    |

| 4.9 V <sub>REF</sub> 7 and V <sub>REF</sub> 8: Bandgap reference using 2.5-V transistors            |    |

| 4.10 V <sub>REF_9</sub> : Low dropout (LDO) regulator                                               | 91 |

| 4.11 Post extraction simulation results                                                      | 91  |

|----------------------------------------------------------------------------------------------|-----|

| 4.11.1 Impact of fabrication process effects                                                 | 96  |

| 4.11.2 Impact of radiation effects (TID)                                                     |     |

| 4.12 Integrated circuit with the designed circuits                                           | 103 |

| 5 OSCILLATORS - CASE STUDY II                                                                | 105 |

| 5.1 Basic concepts                                                                           | 105 |

| 5.2 Ring oscillator implemented in 130 nm CMOS process                                       |     |

| 5.3 Ring oscillator implemented in 45 nm CMOS process                                        |     |

| 5.4 Cross-coupled LC tank oscillators                                                        |     |

| 5.4.1 NMOS cross couple LC-tank                                                              | 113 |

| 5.4.2 PMOS cross couple LC-tank                                                              | 115 |

| 5.4.3 Integrated Inductor                                                                    | 116 |

| 5.4.4 Designed oscillators                                                                   | 119 |

| 5.5 Post-extraction simulation results                                                       |     |

| 5.5.1 Inverter-based ring oscillator (11 stages) using 130 nm CMOS process                   |     |

| 5.5.2 Inverter-based ring oscillator using 45 nm CMOS process                                |     |

| 5.5.3 Cross-couple LC tank oscillator using 45 nm CMOS process                               | 130 |

| 6 SILICON MEASUREMENT - VOLTAGE REFERENCES                                                   | 137 |

| 6.1 Measurement setup for temp. and VDD dependency characterization                          | 137 |

| 6.2 I <sub>REF</sub> : PTAT Current Reference                                                |     |

| 6.3 V <sub>REF 1</sub> : Bandgap-based reference                                             |     |

| 6.4 V <sub>REF 2</sub> : Bandgap-based reference using PMOS diode                            |     |

| 6.5 V <sub>REF</sub> 3: Simple V <sub>TH0</sub> -based reference                             |     |

| 6.6 V <sub>REF_4</sub> : Alternative V <sub>TH0</sub> -based reference                       | 149 |

| 6.7 V <sub>REF_5</sub> : V <sub>TH0</sub> -based reference using composite transistors       |     |

| 6.8 $V_{REF\_6}$ : Resistorless $V_{TH0}$ -based reference using composite transistors       |     |

| 6.9 $V_{REF\_7}$ and $V_{REF\_8}$ : Bandgap reference using 2.5-V transistors                |     |

| 6.10 $V_{REF\_9}$ : Low dropout (LDO) regulator                                              |     |

| 6.11 TID effects                                                                             |     |

| 6.11.1 TID Measurement setup test                                                            |     |

| (101)                                                                                        | 171 |

| 6.11.3 V <sub>REF_1</sub> : Bandgap-based reference                                          |     |

| 6.11.4 V <sub>REF_9</sub> : Low dropout regulator                                            |     |

| 6.11.5 V <sub>REF_4</sub> : Alternative V <sub>TH0</sub> -based reference                    |     |

| 6.11.5.1 V <sub>PTAT</sub> voltage                                                           |     |

| 6.11.5.3 V <sub>REF 4</sub> voltage                                                          |     |

| 6.11.6 V <sub>REF_3</sub> : Simple V <sub>TH0</sub> -based reference                         |     |

| 6.11.7 V <sub>REF 7</sub> and V <sub>REF 8</sub> : Bandgap reference using 2.5-V transistors |     |

| 6.11.7.1 V <sub>CTAT</sub> voltage implemented by means of PNP device                        |     |

| 6.11.7.2 V <sub>CTAT</sub> voltage implemented by means of p-channel transistor              |     |

| 6.11.7.3 V <sub>REF_7</sub> and V <sub>REF_8</sub> voltages                                  | 180 |

| 6.11.8 Radiation Hardening By Design (RHBD)                                                  | 182 |

| 6.12 Final conclusions                                                                       | 184 |

| 6.12.1.1 TID and fabrication process effects                                                 |     |

| 6.12.1.2 Temperature performance and impact of fabrication process                           |     |

| 7 SILICON MEASUREMENT - OSCILLATORS                                                          |     |

| 7.1 Oscillators implemented in 130 nm CMOS process                                           | 187 |

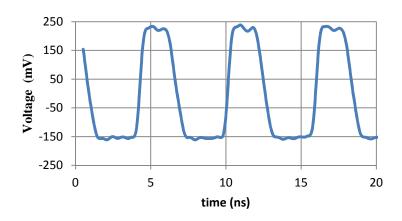

| 7.1.1 | Oscillation frequency (f <sub>OSC</sub> )                   | 187 |

|-------|-------------------------------------------------------------|-----|

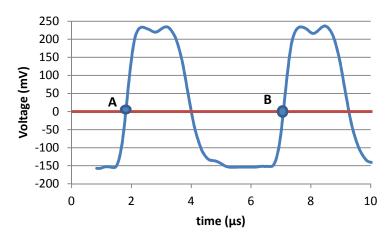

|       | Output voltage waveform                                     |     |

|       | Power spectrum                                              |     |

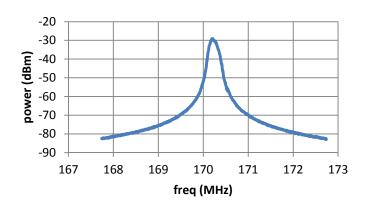

| 7.1.4 | f <sub>OSC</sub> as a function of bulk bias                 | 190 |

| 7.1.5 | Period Jitter                                               | 192 |

| 7.1.6 | Ring-Oscillator Period Jitter as a function of bulk bias    | 197 |

| 7.1.7 | Measured Period Jitter for battery supplied ring oscillator | 199 |

| 7.1.8 | Comments on the Period Jitter calculation                   | 200 |

| 7.2   | Oscillators implemented in 45 nm CMOS process               | 201 |

| 7.2.1 | Measurement Setup                                           | 201 |

| 7.2.2 | LC-tank oscillators                                         | 203 |

| 7.2.3 | Ring-Oscillator                                             | 206 |

| 7.3   | Conclusions                                                 | 208 |

| 8 C   | ONCLUSIONS                                                  | 211 |

| REFE  | RENCES                                                      | 214 |

| PUBL  | LICATIONS BY THE AUTHOR OF THIS DOCTORAL THESIS             | 227 |

| ANE   | ( A: DESIGN METHODOLOGY USING INVERSION COEFFICIENT         | 228 |

#### 1 INTRODUCTION

All the progress done in the semiconductor industry since early 70's is well known and it undoubtedly affects our life. It is one of the reasons why we are currently living in the era of "ubiquitous computing", where the human-computer interaction is each time closer and present in our daily life. The well known historical observation about the trends on the advances of semiconductor technologies done by Gordon Moore in 1965 (MOORE, 1997) was true for more than 30 years. The number of functionality per chip (bits and transistors) and the processor performance (clock frequency x instructions per clock) has doubled each 1.5 to 2 year during many years. However, in the last years, the number of transistors and clock frequency has not increased in this same slope as before (IWAI, 2009).

As a result of the evolution of the fabrication process of integrated circuits, huge improvements were done in the speed, power consumption, compactness, functionality and integration level of integrated circuits. Due to these improvements, the historical reduction in the cost per function implemented inside IC's were around 25-29% per year, while the semiconductor market growth were historically ~17% per year, but maturing to slower growth in more recent history (ITRS, 2012).

All this progress of MOS circuits has been accomplished by the downscaling of their components since early of 1970. For instance, in 1971 using a 10 µm CMOS process, Intel introduced the 4004 processor with 2,300 transistors and a clock speed of 108 kHz (INTEL, 2013). Nowadays, commercial processors fabricated in 22-nm process (*e.g.* Processor Intel Itanium 9500) have 8 cores, 3.1 billions of transistors and clock speed of more than 2.5 GHz (INTEL, 2013). Technologies such as strained silicon, high-k/metal gate and multi-gate transistors (*e.g.* tri-gate) are employed to increase performance of the new generation of processors (INTEL-b, 2013). In 2015, Intel announces the fabrication of a new processor called Skylake implemented using a 3D tri-gate (FinFET) transistors of 14 nm process (BOHR, 2015).

Nowadays, the miniaturization of digital functions sustained by the incorporation into devices of new materials and transistor concepts will still continue, although in slower ratio, what is called "More Moore" by some organizations (ITRS, 2012). One example of a new technique that will allow the increase of the number of components per mm<sup>2</sup> is the stack of

layers of transistors on the top of each other composing a monolithic 3D integrated circuit (XIE, 2008).

In addition, there is also a lot of work been done to enhance the compatibility of CMOS and non-digital technologies, which enable the migration of non-digital components from the PCB into the package containing the integrated circuits (System-in-Package, SiP), or even into the chip itself (System-on-Chip, SoC). For example, it would be possible to have an integration of digital circuits with: passive components, high-voltage devices, microelectromechanical systems (MEMS) or nanoeletromechanical systems (NEMS), sensors, actuators and micro-fluidic devices. This concept of functional diversification is called "More than Moore" (ITRS, 2010).

A significant part of the developments of CMOS fabrication process mentioned above was driven by the market of high-performance digital circuits, such as microprocessor (WHITE, 2013). Therefore, although there was a huge reduction on size, cost and power consumption of digital circuits, it is currently much more difficult to implement analog circuits using these modern IC technologies.

Examples of difficulties when designing IC with modern technologies that become even more challenging are the noise and the process variability (e.g. fluctuations of the threshold voltage). Because transistor mismatch and flicker noise are inversely proportional to the transistor area (PELGROM, 1989), (RAZAVI, 2001), their impact on the performance of integrated circuits tends to be worse with the transistor size downscaling. Moreover, due to the reduction of the supply voltage, the analog voltage range that can be handled in RF and mixed-signal circuits has decreased significantly. In addition, short channel effects, such as hot carrier effects (PAGEY, 2002), also imposes a challenge for the long-term circuit reliability of integrated circuits.

Other example of current concern on the design of integrated circuits is the radiation (BALEN, 2010) and (SIMIONOVSKI, 2012). The incidence of ionizing particles was previously considered an issue only for CMOS circuits used for aerospace industry and for high-energy physics applications. Moreover, due to the reduction of transistor dimensions, the supply voltage and the capacitance required to store data, integrated circuits are at the present time, more susceptible to the influence of ionizing radiation even when such circuits are operating at ground level (O'GORMAN, 1994).

Although the challenges to design RF and analog circuits has increased, its applications and fraction on semiconductor market has increased (ITRS, 2011). This happen, for instance, due to the fourth generation of cellular phones that requires analog and RF circuits to implement functions that are not properly and efficiently implemented by digital circuits. As analog circuits are bridges between the digital world and the analog real word, these circuits will be always a fundamental part on the design of new products. As a consequence, there is a crucial demand for research that face the challenges of designing high performance analog and RF circuits using new CMOS processes. This thesis focus on two of these challenges, transistor noise and radiation effects.

## 1.1 Motivation and Scope

#### 1.1.1 Radiation Effects and Total Ionizing Dose

Circuits operating in space environment experience constant bombardment by a wide spectrum of energetic photons and particles coming from the sun and galaxies. The presence of these high-energy particles, ionizing particles (*e.g.* protons, neutrons, electrons, alpha particles or heavy ions) and electromagnetic radiation (*e.g.* gamma-ray) can cause temporary or permanent faults on the operation of the electronic circuits (BOUDENOT, 2007). As for instance, satellites and space telescopes can have its lifetime shorted due to the impact of these high-energy particles that come from cosmic rays, solar flares/winds, and radiation belts (XAPSOS, 2014).

The electronic used in nuclear power plants and physics research laboratories also suffer with high incidence of these participles. But besides of these specific applications, circuits operating at the ground level are also susceptible to the impact of the ionizing radiation, although in lower intensity (O'GORMAN, 1994). In (JUST, 2013), it was demonstrated that SRAM memories could suffer soft errors (*i.e.* the corruption of the information stored in the memory) due to natural radiation (*e.g.* atmospheric neutrons) at ground level.

When these high-energy ions, subatomic particles or atoms moving at relativistic speeds interacts with semiconductor, effects such as Single Event Effects (SEE) and Total Ionising Dose (TID) can happen (BOUDENOT, 2007).

Single Event Effects (SEE) are defined by a sudden high ionising dose deposition of particles (e.g. protons and heavy ions) in a sensitive region (e.g. transistor reverse-biased

junctions) resulting in functional anomalies of the integrated circuit. This instantaneous perturbation can be or not destructive.

The permanent or momentary corruption of the information stored in a memory element (named as SED and SEU, respectively) or an impulse response of certain amplitude and duration (named as SET) are examples of nondestructive single event effects. A permanent corruption of the information does not mean that the electronic circuit is physically damaged or destroyed, and thus, it can be eventually reprogrammed. SED, SEU and SET are acronyms that means Single Event Disturb, Single Event Upset and Single Event Transient, respectively.

Examples of destructive effects on transistors are Single Event Latchup (SEL), Single Event Snapback (SESB) and Single Event Gate Rupture (SEGR) (DUZELLIER, 2004). In these cases, transistors and the electronic circuit is physically damaged and may not work.

All the above mentioned effects can cause several errors in integrated circuits, as for instance, error conversion in data converters, data corruption in memories (KAY, 2012), calculation errors in microprocessors and power drops in voltage regulators. It is important to see that with the advances of the CMOS technology and the increased speed of operation, effects like SET tend to become even more critical (DUZELLIER, 2004). Moreover, the modeling and simulation of such effects on the performance of complex circuits with reduced dimensions becomes also more difficult. Note that the size of sensitive areas of integrated circuits are in the same order of the size of ionizing particles.

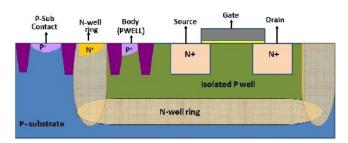

Other effect, not instantaneous as SEE, but that happens over a long time is the Total Ionising Dose. It is the accumulation of ionising dose deposition (electrons and protons) over a long time in insulators (e.g. transistor gate oxide layers or field oxides) leading to degradation of electrical performance of the device (BOUDENOT, 2007). For instance, radiation can induce trapped charges in the gate oxide which causes a shift ( $\Delta V_{TH\_TID}$ ) in the transistor threshold voltage ( $V_{TH}$ ) (SCHRIMPF, 2007). If the shift is large enough, for instance, the NMOS Enhancement transistor cannot be turned off even with zero volts applied at its gate terminal (OLDHAN, 2003). Figure 1.1 shows the cross section of NMOS transistor with radiation-induced positive charges trapped in the gate oxide.

Radiation induced positive charges Radiation induced Interface traps

Figure 1.1- NMOS with radiation-induced positive charges and interface traps

Source: the author

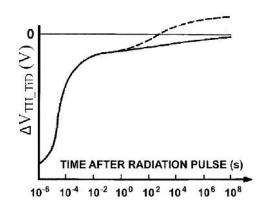

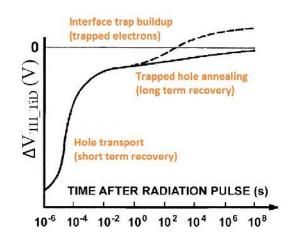

Figure 1.2 shows the variation in the threshold voltage caused by the irradiation  $\Delta V_{TH\_TID}$  (OLDHAN, 2003). Initially, due to the radiation energy that reaches the gate oxide, several electron/holes pairs are created. Some of these charge carriers quickly recombine. Due to the higher mobility, electrons that do not recombine are swept out of the oxide while holes stays trapped in the  $SiO_2$  interface. These positive charges leads to an initial negative shift of  $V_{TH}$ . Subsequent carrier recombination tends to decrease the shift of the threshold voltage.

Moreover, the shift on  $V_{TH}$  can also becomes positive due to the radiation-induced buildup of interface traps at the Si/SiO<sub>2</sub> interface. These interface traps are shown in figure 1.1 and are similar to those ones induced by the fabrication process. These radiation induced defects can trap electrons and produce a positive shift of  $V_{TH}$ , that is represented by the dotted line in figure 1.2. In summary,  $\Delta V_{TH\_TID}$  is roughly a result of two main processes with opposite effects: trapped holes and created interface traps (OLDHAN, 2003). Moreover, charges can be trapped in thick oxide isolation, resulting in an increase in drain-source leakage currents, both intra- as well as inter-devices, and thus, contributing to  $\Delta V_{TH\_TID}$ . More details of these processes will be explained in chapter 2.

Other issue caused by TID on CMOS process is the increase of gate leakage current. This problem is especially important in low power circuits implemented in recent CMOS technologies due to the very thin oxide thickness. Due to irradiation, many defects are created in the SiO<sub>2</sub> which can lead to trap-assisted tunneling current of electrons from the substrate to the gate contact, therefore increasing power consumption and causing failures (OLDHAN, 2003).

Figure 1.2 - Shift in the threshold voltage of NMOS due to TID

Source: the author, modified from (OLDHAN, 1981).

Besides TID and SEE discussed above, a third effect also can happen in semiconductors is the accumulation of crystal lattice defects caused by high energy radiation. Energetic particles (protons and ions) can displace atoms from their sites in the silicon lattice structure leading to displacement damage effects (DD) and electrically active defects that reduce the carrier lifetime (*i.e.* average time required by minority carrier to recombine) and carrier mobility (SCHRIMPF, 2007). This effect is also referred as "accumulation of non-ionising dose deposition" (DUZELLIER, 2004). Differently from ionising dose, this type of radiation has not enough energy to remove tightly bound electrons from atoms and thus creating ions.

This work is focused on the effects of TID on the performance of analog integrated circuits. As  $\Delta V_{TH}$ \_TID and the increased current leakage tend to damage the performance or even to cause permanent failures, they should be well understood with intention of properly designing analog circuits.

#### 1.1.2 Transistor flicker and random telegraph noise

Regarding the noise generated by MOSFETs, one can mention the thermal noise and the flicker noise as the main important noise types. The most significant source of thermal noise is the transistor channel, while the ohmic sections of the transistor (*e.g.* gate, source, drain) can also have lower contribution. The thermal or white noise is caused by the random motion of electrons in electronics and its power spectrum is flat up to 100 THz (RAZAVI, 2001).

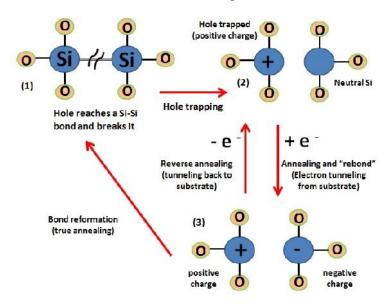

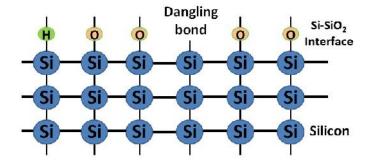

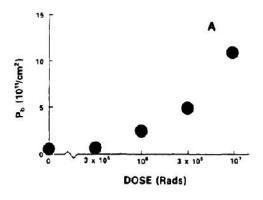

This work focus on the flicker noise. Flicker noise is mainly related to the trapping/de-trapping process of minority carriers into/from traps located at the silicon-oxide (Si-SiO<sub>2</sub>)

interface or inside the gate oxide. Therefore, this type of noise is proportional to the number of available traps, that are physically, dangling bonds. Dangling bonds can be created by the IC fabrication process or lately formed by the rupture (*e.g.* due to hot carrier injection or radiation) (PAGEY, 2002) of weak Si-Si bonds caused by oxygen vacancies (DRUIJF, 1995). Carrier capture and emission back to the channel leads to current fluctuations (ΔI<sub>DS</sub>).

Figure 1.3 illustrates the defects in the Si-SiO<sub>2</sub> interface and the trapping and de-trapping mechanism. Note that traps are represented by white points and they are located inside the oxide gate. One could argue that a more precise illustration would be if the traps were located exactly at the Si-SiO<sub>2</sub> interface, since these traps are the main source of 1/f noise - as will be discussed in chapter 3. Each defect is characterized by its own time constant , which is function of its distance from the channel (z) according to the equation 1.1, where  $_0$  is  $\sim 10^{-10}$  s and  $_F$  is  $\sim 2 \times 10^8$  cm<sup>-1</sup> is the tunneling parameter (BALANDIN, 2013).

$$\tau = \tau_0 \cdot e^{(\lambda_F \cdot z)} \tag{1.1}$$

Recent work, however, has shown that modern oxides are simply too thin to support the elastic tunneling model described by equation (1.1) (and still implemented in BSIM model) (CAMPBELL, 2009). Moreover, no correlation between trap distance from the interface (variable "z" in equation 1.1), and capture and emission time constants was observed by (NAGUMO, 2010). There is still a lot of work to be developed in the above subject.

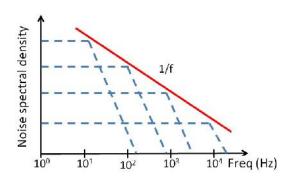

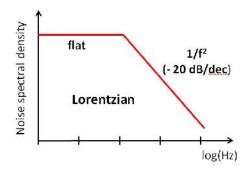

The contribution of all traps with different results in a set of trapping and de-trapping electrons, resulting in a noise spectrum density inversely proportional to the frequency range as it is shown in figure 1.4. Each dotted line in figure 1.4 represents one trap (BALANDIN, 2013).

Gate oxide Source Substrate Drain  $r_3$

Figure 1.3 - Defects (dangling bonds) at Si-SiO<sub>2</sub>

Source: (BALANDIN, 2013)

Figure 1.4 - Flicker noise spectrum

Source: the author, modified from (BALANDIN, 2013)

Flicker noise is a problem because it affects the performance of digital, analog and RF circuits. Few examples of the impact of 1/f noise on the performance of electronic circuits are listed below:

- degrades the phase noise and jitter of integrated oscillators (GIERKINK, 1999)

- causes erratic behavior in static random-access memory (AADITHYA, 2013)

- limits the number of effective bits achieved by data converters (NEU, 2010)

- limits the accuracy of voltage references circuits (HOLMAN, 1994)

The impact of 1/f noise is even more critical for small-area low power CMOS circuits implemented in recent nanometer CMOS technologies. The low supply voltage (*e.g.* lower than one volt) means lower signal to noise ratio. Small area transistors (*e.g.* transistor length < 100 nm) presents higher flicker noise since its 1/f noise is inversely proportional to transistor area. Moreover, the use of halo doping to reduce the short channel effects results in higher flicker noise performance (SRINIVASAN, 2012).

When the transistor length becomes very small (e.g. L < 130 nm), the number of traps in the Si-SiO<sub>2</sub> interface becomes also small, and in these cases, the discrete noise generated by these traps are not referred as 1/f noise, but as random telegraph noise (RTN) or random telegraph signal (RTS) (DIERICKX, 1992). As for instance, if the transitor has only one trap, the current (or resistance) fluctuations happens between only two discrete values, analogous to the telegraph signal.

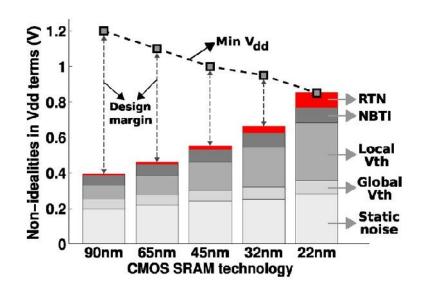

Figure 1.5 shows the impact of RTS on the design margin of CMOS SRAM circuits has increased as transistor dimensions has decreased. Lower the technological node and the supply voltage, smaller the design margin and worse the RTS noise.

Figure 1.5 - RTN noise on the design margin of CMOS SRAM

Source: (AADITHYA, 2013)

This thesis is focused in a particular condition of the flicker or RTS noise, that is called cyclostationary (PHILLIPS, 2000). Circuits with time-varying operating points modulates the noise generated by bias-dependent noise sources, and therefore, modulates the transfer function from the noise source to the output and then, a non-stationary noise is generated. This periodic variation of the output noise, called cyclostationary noise, is especially important in oscillators, mixers and data converters since the bias voltage (gate-voltage) of some transistors are constantly varying with time. Traditional simulation tools (*e.g.* SPICE) do not properly estimate cyclostationary noise (PHILLIPS, 2000) (AADITHYA, 2013), what makes the subject of this thesis very important for circuit and electronic design assistant tool (EDA) designers.

#### 1.2 Objectives of this thesis

This work deals with two challenges in the design of analog integrated circuits: the impact of TID and flicker noise (under cyclostationary conditions) in the performance of analog integrated circuits.

In order to verify the effects of TID in analog circuits implemented in advanced CMOS process, voltage reference circuits were chosen as case-study. Several architectures of voltage reference are available in literature and the most part of them are based on Bandgap voltage

$(V_{BG})$  and transistor threshold voltage  $(V_{TH})$ . Those ones based on  $V_{TH}$  are specially important when low-voltage and low-power operation is required, and therefore, were implemented in this work.

The most part of the designed circuits were designed to operate at 1 V due to the current low power and low voltage requirements of many applications. The CMOS process used to implement the voltage references is a standard and commercial 130 nm CMOS process. The most circuit implementation were done using core transistors (*i.e.* thin oxide and VDD = 1.2 V). However, since the impact of irradiation also depends on  $t_{ox}$ , a voltage reference using 2.5 V devices (thicker oxide) were also designed. Moreover, a traditional PTAT current reference and a simple voltage regulator were also implemented.

The temperature and supply voltage dependency, process variability and TID effects on the performance of the designed circuits were characterized. The TID effects were characterized after irradiation using -ray of a Cobalt source ( $^{60}$ Co).

The content developed in this thesis can be used for (i) better design of voltage references when radiation is the concern, (ii) a modeling of radiation effects and also for (iii) the development of simulation tools (EDA) for TID irradiation (Colombo, 2013)

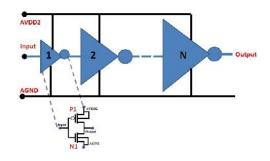

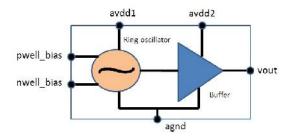

Regarding the impact of flicker noise on analog circuits, voltage oscillators were chosen as case-study in our work. The implemented voltage oscillators have key transistors that operate in cyclostationary regime, whose gate voltage is constantly varying with time. As a consequence, the output noise of these circuits, normally called jitter or phase noise, can be used as case-study for the investigation of cyclostationary noise.

Our research group at UFRGS has been working in the developing of improved transistor flicker noise models for several years (DA SILVA, 2008). One of the fundamental steps of this work is the analysis of jitter and phase noise of fabricated circuits, and its comparison with simulation results. Therefore, the second part of this thesis works as a brick in the development of improved flicker noise models.

Two topologies of voltage oscillators were implemented: (a) ring-oscillator and (b) LC-tank oscillator. Ring-oscillator is a proper case-study because its jitter or phase noise is a direct function of flicker noise of transistors working in cyclostationary operation. It is a simple circuit that is composed only by transistors that are constantly switching in time and then, it is an useful case-study.