## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

#### FILIPE DE AGUIAR GEISSLER

# METODOLOGIA DE INJEÇÃO DE FALHAS BASEADA EM EMULAÇÃO DE PROCESSADORES

Dissertação apresentada como requisito parcial para a obtenção do grau de Mestre em Microeletrônica.

Prof. Dra. Fernanda Lima Kastensmidt Orientadora

### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA INSTITUTO DE INFORMÁTICA

#### FILIPE DE AGUIAR GEISSLER

# Metodologia de injeção de falhas baseada em emulação de processadores

Dissertação apresentada como requisito parcial para a obtenção do grau de Mestre em Microeletrônica.

Prof. Dra. Fernanda Lima Kastensmidt Orientadora

### CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Geissler, Filipe de Aguiar

Metodologia de Injeção de Falhas Baseada em Emulação de Processadores / Filipe de Aguiar Geissler. — Porto Alegre: Programa de Pós-Graduação em Microeletrônica, 2014.

85 f.:il.

Dissertação (mestrado) — Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica. Porto Alegre, BR — RS, 2014. Orientador: Fernanda Gusmão de Lima Kastensmidt.

1. Efeitos da Radiação em Processadores. 2. Metodologias e ferramentas de injeção de falhas. 3. Emulação de processadores. I. Kastensmidt, Fernanda Gusmão de Lima. II. Metodologia de injeção de falhas baseada em emulação de processadores.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Aldo Bolten Lucion Diretor do Instituto de Informática: Prof. Flávio Rech Wagner

Coordenador do PGMICRO: Prof. Ricardo Reis

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

# Dedicatória

Dedico este trabalho com muito amor à minha mãe Suzana Pas de Aguiar, à minha tia Sandra Pas de Aguiar, em memória à minha madrinha Honorina Pas de Aguiar, e especialmente em memória à minha avó Maria Pas de Aguiar.

### Agradecimentos

Quero agradecer a força do amor da minha vida, minha noiva, Ariane Moraes, por ter estado ao meu lado me incentivando, alegrando e sendo compreensiva em todos os momentos e por me ajudar a revisar a dissertação. A minha mãe Suzana, tia Sandra e avó Maria pelo amor e dedicação. A minha tia Lourdes que mesmo estando longe nunca deixa de estar presente. Ao meu primo Daniel por inúmeras horas de descontração em sua companhia e amizade. A toda a minha família e amigos pela união nas horas de dificuldade.

Um agradecimento a empresa PARKS S. A., pelo incentivo e flexibilidade para a formação de profissionais cada vez mais capacitados. Aos colegas e amigos do setor de pesquisa e desenvolvimento, com os quais convivo e aprendo diariamente. Um agradecimento ao meu coordenador Leandro Mondin, pelo apoio para que este mestrado fosse concluído e ao colega Alexandre Martins pelas sugestões durante o desenvolvimento deste trabalho. E finalmente, gostaria de agradecer em especial à minha orientadora Fernanda Kastensmidt, pela riqueza de ideias, paciência, flexibilidade e compreensão durante a execução deste trabalho.

### **Fault Injection Methodology Based on Processor Emulation**

#### **ABSTRACT**

This dissertation aims to present a fault injection methodology based on microprocessor emulation. The effects caused by radiation in microprocessors, operating in space or at high altitudes, have been studied in the literature for the development of fault tolerance mechanisms. With the growing popularity of COTS (Commercial Off-The-Shelf) processors usage, in critical applications, a number of concerns have arisen due to the lack of reliability, presented in these systems. Due to the lack of fault tolerance mechanisms, these COTS devices are more susceptible to radiation effects. In this context, software-based fault tolerance techniques have been studied in the literature in order to increase the reliability of this approach. To validate such fault tolerance mechanisms, the use of fault injection techniques is applicable. These fault injection techniques have several limitations which can preclude their applicability, depending on of its design approach. Factor such as cost, unavailability of hardware description - used by fault injection techniques based on simulation or emulation with FPGA (Field Programmable Gate Array), and the long time demanded to execute experiments, are some examples of limitations in the available techniques. Based on this, the alternative fault injection methodology presented in this work aims to reduce these limitations. Based on the dynamic translation of instructions usage to accelerate the execution of application on emulators, the methodology presents a fault model for transient and permanent faults applicable in this scenario. As a classification method of the observed effects in this process, a model in the literature has been used. To validate this methodology, a fault injector based on the QEMU emulator was implemented. Later, a case study with the fault injector was performed for three software structures running at a time on a MIPS 24kc processor, representing three different levels of complexity: Linux operating system, RTEMS (Real-Time Operating System), and a dedicated application. Each system was submitted to a fault injection campaign emulating Single Event Upsets (SEUs). As fault targets it was selected the processor registers and the data memory. Finally, the analysis obtained with the experiments showed the different effects observed for the three levels of complexity. Besides that, the fault injector performance could be evaluated providing in the end a tool to help in the development of software-based fault injection techniques.

**Keywords:** Radiation effects in microprocessors, Fault Injection Methodology, Processor Emulation, Software-based fault tolerance techniques.

### Metodologia de Injeção de falhas baseada em Emulação de Processadores

#### **RESUMO**

Esta dissertação tem por finalidade apresentar uma metodologia de injeção de falhas baseada em emulação de processadores. Os efeitos causados pela radiação em processadores, operando no espaço ou em altitudes elevadas, têm sido estudados na literatura para o desenvolvimento de mecanismos de tolerância a falhas. Com a crescente popularidade do uso de processadores comerciais, (COTS - do inglês, Commercial Off-The-Shelf), em aplicações críticas, uma série de preocupações tem surgido devido a falta de confiabilidade apresentada por estes sistemas. Sendo desprovidos de mecanismos de tolerância para melhor robustez em ambientes espaciais, estes dispositivos comerciais são mais suscetíveis aos efeitos da radiação. Neste contexto, técnicas de tolerância a falhas baseadas em software vêm sendo estudadas a fim de aumentar a confiabilidade desta abordagem. Para a devida validação de tais mecanismos de tolerância, o uso de técnicas de injeção de falhas é aplicável. Estas técnicas de injeção de falhas possuem uma série de limitações que podem inviabilizar a sua aplicabilidade, dependendo da abordagem utilizada. Fatores como custo, indisponibilidade da descrição de hardware – utilizada em técnicas de injeção de falhas por simulação ou emulação em FPGA (Field Programmable Gate Array), e o longo tempo necessário para execução dos experimentos, são alguns exemplos de limitações das técnicas disponíveis. Com base nisso, a metodologia de injeção de falhas alternativa apresentada neste trabalho, visa reduzir as limitações presentes nas mais diversas técnicas. Baseada na utilização de tradução dinâmica de instruções, para acelerar o processo de execução de aplicações em emuladores, a metodologia apresenta um modelo de falhas para efeitos transientes e permanentes, aplicáveis neste cenário. Como método de classificação dos efeitos observados neste processo, um modelo presente na literatura foi utilizado. Para validação desta metodologia, um injetor de falhas baseado no emulador QEMU foi desenvolvido. Posteriormente, um estudo de caso com o injetor de falhas foi realizado para três estruturas de software distintas executando individualmente no processador MIPS 24kc, representando três níveis de complexidade distintos: sistema operacional Linux, sistema de tempo real, (RTEMS – do inglês, Real-Time Operating System), e uma aplicação dedicada. Cada sistema foi submetido a uma campanha de injeção de falhas transientes para emulação de efeitos singulares (SEU do inglês, Single Event Upset). Como alvo de falhas, foram selecionados os registradores do processador e a memória de dados. Por fim, as análises obtidas através dos experimentos mostraram os diferentes efeitos observados para os três níveis de complexidade dos softwares executados. Além disso, se pôde avaliar o desempenho do injetor de falhas, disponibilizando ao final do trabalho uma ferramenta para o auxílio no desenvolvimento de técnicas de tolerância a falhas por software.

**Palavras-Chave:** Efeitos da radiação em processadores, Metodologia de injeção de falhas, Emulação de processadores, Tolerância a falhas em software.

### LISTA DE ABREVIATURAS E SIGLAS

AMUSE Autonomous MultiLevel Emulation System of Soft Error Evaluation

ASIC Application-specific Integrated Circuit

BDM Background Debug Mode

CEU Code Emulating Upset

CEU Code Emulating Upset

COTS Commercial Off-The-Shelf

CPU Central Processing Unit

CTR Compile-Time Reconfiguration

DFI Direct Fault Injection

EDM Error Detection Mechanism

EMM Experimental Module Manager

EXFI Exception-based Fault Injector

FERRARI Flexible Software-based Fault and Error Injection System

FI Fault Injector

FIHU Fault Injection Hardware Unit FPGA Field Programmable Gate Array

GAS GNU AS

GIT Gerenciamento de Injeção de Falhas

GL Gate Level

GNU General Public License

HDL Hardware Description Level

I2C Inter-integrated Circuit

IP Intellectual Property

JTAG3 Joing Tag Access Group 3

LET Linear Energy Transfer

LLVM Low Level Virtual Machine

MBU Single-Event Multiple-Bit Upset

MEFISTO Multi-level Error/Fault Injection Simulation Tool

MEFISTO-L Multi-level Error/Fault Injection Simulation Tool

MMU Memory Unit Management

OCD Common on-Chip Debugging

OCD-FI Common on-Chip Debugging Fault Injector

PC Personal Computer

QEMU Quick Emulator

RAM Random Access Memory

RCT Run Control & Trace

RI Representação Intermediária

RT Real-Time

RTEMS Real-Time Operating System

RTL Register-Transfer Level

RTR Real-Time Configuration

SDF Standard Delay Format

SEE Single-Event Effects

SET Single-Event Transient

SEU Single-Event Upset

SPI Serial Peripheral Interface

SRAM Static Random Access Memory

SWIFI Software-implemented Fault Injection

TB Bloco de Tradução

VHDL VHSIC Hardware Description Language

# LISTA DE FIGURAS

| Figura 1.1: Categorização dos métodos de injeção de falhas em função do modelo de processador e     | 27        |

|-----------------------------------------------------------------------------------------------------|-----------|

| posicionamento de alguns autores nestas categorias.                                                 | 27        |

| Figura 2.1: Aspectos relativos ao desempenho de execução de aplicações em função da técnica de      |           |

| injeção de falhas com diferentes abordagens                                                         |           |

| Figura 2.2: Estrutura de simulação de injeção de falhas da ferramenta FERRARI                       | 35        |

| Figura 2.3: Modelo de falhas para execução de instrução errada                                      | 37        |

| Figura 2.4: Arquitetura do ambiente de injeção de falhas Xception                                   | 38        |

| Figura 2.5: Ambiente de injeção de falhas EXFI                                                      | 39        |

| Figura 2.6: Metodologia de injeção de falhas por CEU                                                | 41        |

| Figura 2.7: Arquitetura organizacional do sistema Linux                                             |           |

| Figura 2.8: Utilização de interface de depuração de processadores                                   |           |

| Figura 2.9: Estrutura OCD-FI para injeção de falhas.                                                |           |

| Figura 2.10: Técnicas de injeção de falhas baseadas em simulação                                    |           |

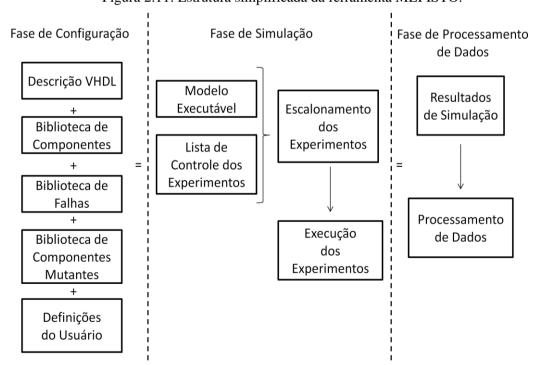

| Figura 2.11: Estrutura simplificada da ferramenta MEFISTO                                           | 47        |

| Figura 2.12: Estrutura do modelo de sabotadores: (a) USS, (b) BSS, (c) nUSS e (d) nBSS              | , ,<br>49 |

| Figura 2.13: Alteração da definição de componente e arquitetura em linguagem VHDL para construç     |           |

| de um mutante.                                                                                      |           |

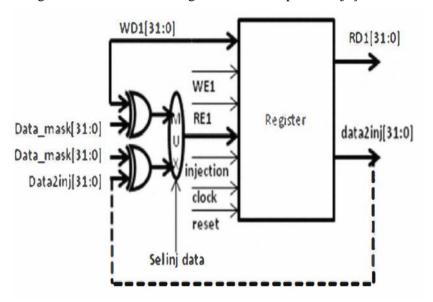

| Figura 2.14: Estrutura do registrador com suporte a injeção de falhas.                              |           |

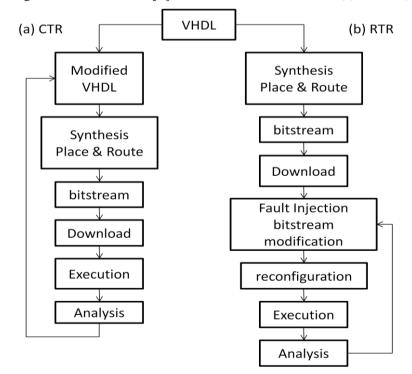

| Figura 2.15: Fluxo de emulação de hardware em FPGA.                                                 |           |

| Figura 2.16: Fluxo de injeção de falhas em FPGA CTR (a) e RTR (b)                                   |           |

| Figura 2.17: Ambiente de injeção de falhas com emulação de hardware por FPGA                        | 52<br>51  |

| Figura 2.17. Amoiente de injeção de jainas com emutação de naraware por FFGA                        | 54        |

| Figura 2.18: Circuito de instrumentação para injeção de falhas                                      |           |

| Figura 2.19: Arquitetura do ambiente de injeção de falhas                                           |           |

| Figura 2.20: Sistema de injeção de falhas autônomo.                                                 |           |

| Figura 3.1: Estrutura de um emulador de processador                                                 |           |

| Figura 3.2: Processo de tradução dinâmica de instruções                                             |           |

| Figura 3.3: Processo de tradução dinâmica de instruções                                             |           |

| Figura 3.4: Processo de tradução dinâmica de instruções                                             |           |

| Figura 3.5: Aplicação QEMU como processo em um sistema operacional                                  |           |

| Figura 3.6: Fluxo de execução do emulador QEMU                                                      |           |

| Figura 3.7: Representação intermediária da instrução addi                                           |           |

| Figura 3.8: Descrição da operação movl_T0_r1 em linguagem C                                         |           |

| Figura 4.1: Protótipos de rotinas para injeção de falhas no ambiente de emulação de arquiteturas    | 74        |

| Figura 4.2: Estrutura básica de um bloco traduzido.                                                 | 75        |

| Figura 4.3: Fluxo de injeção de falhas no emulador de arquiteturas.                                 | 76        |

| Figura 4.4: Ambiente de experimentação com injetor de falhas baseado no emulador QEMU               | 78        |

| Figura 5.1: Estrutura dos sistemas alvo de injeção de falhas (a) RTEMS, (b) LINUX e (c) sistema     |           |

| simples.                                                                                            | 82        |

| Figura 5.2: Distribuição de falhas no tempo                                                         | 84        |

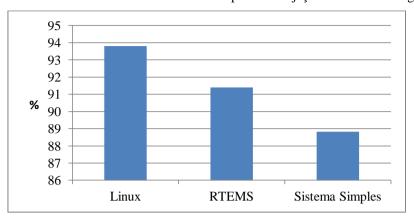

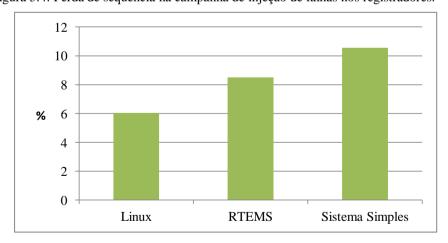

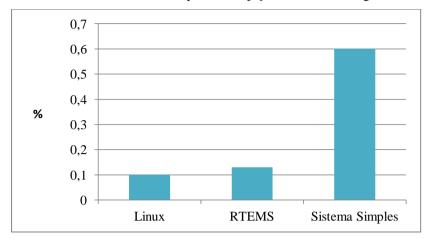

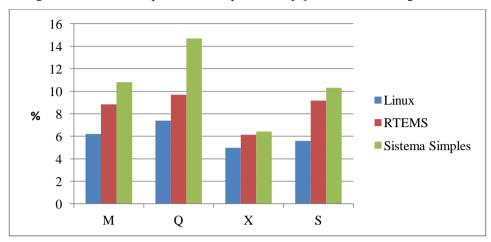

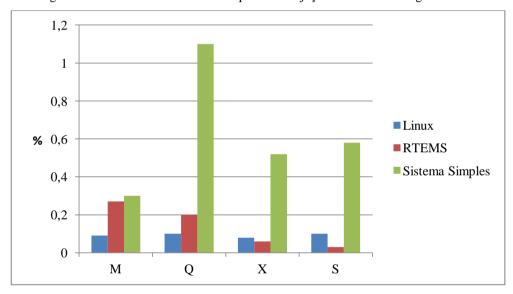

| Figura 5.3: Falhas mascaradas e/ou toleradas campanha de injeção de falhas nos registradores        |           |

| Figura 5.4: Perda de sequência na campanha de injeção de falhas nos registradores                   |           |

| Figura 5.5: Erros de resultados na campanha de injeção de falhas nos registradores                  |           |

| Figura 5.6: Falhas mascaradas e/ou toleradas na campanha de injeção de falhas nos registradores     |           |

| Figura 5.7: Perda de sequência na campanha de injeção de falhas nos registradores                   |           |

| Figura 5.8: Erros de resultado na campanha de injeção de falhas nos registradores                   |           |

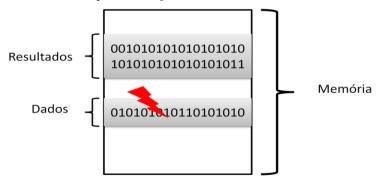

| Figura 5.9: Definição da área de dados alvo de falhas nos experimentos e área de resultados, gerada |           |

| após a execução de um benchmark                                                                     |           |

|                                                                                                     |           |

| Figura 5.10: Perda de sequência na campanha de injeção de falhas nos registradores                 | .89 |

|----------------------------------------------------------------------------------------------------|-----|

| Figura 5.11: Erros de resultado na campanha de injeção de falhas na memória                        | .89 |

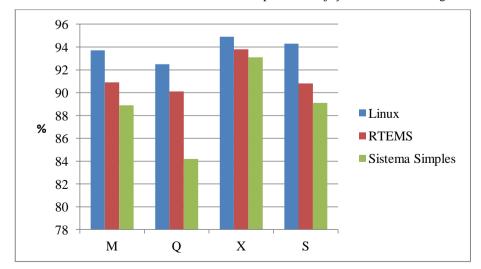

| Figura 5.12: Erros de resultado observados durante a injeção de falhas nos benchmarks para os três |     |

| sistemas com vetores de 1000, 3000 e 5000 falhas                                                   | .91 |

| Figura 5.13: Total de falhas injetadas com os sistemas AMUSE, ASTERICS e injetor desenvolvido no   |     |

| trabalhotrabalho                                                                                   | .93 |

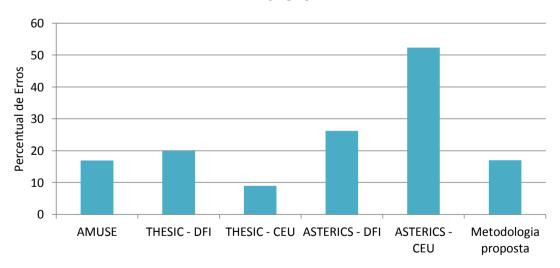

| Figura 5.14: Percentual de erros de resultado dos 3 trabalhos selecionados em comparação a         |     |

| metodologia proposta                                                                               | .93 |

|                                                                                                    |     |

# LISTA DE TABELAS

| Tabela 2.1: Parâmetros de simulação para injeção de falhas                                     | 37       |

|------------------------------------------------------------------------------------------------|----------|

| Tabela 2.2: Emulação de arquiteturas comparada a outras técnicas de injeção de falhas          | 58       |

| Tabela 4.1: Atributos para definição de uma falha.                                             | 70       |

| Tabela 4.2: Modelo de falhas para memória                                                      | 71       |

| Tabela 4.3: Modelo de falhas para memória                                                      |          |

| Tabela 4.4: Componentes do ambiente de experimentação.                                         |          |

| Tabela 4.5: Conjunto de benchmarks disponíveis para o processo de emulação                     |          |

| Tabela 5.1: Número de ciclos de relógio emulados e correspondente tempo visto pelo sistema ho. | spedeiro |

| no processo de emulação do processador MIPS 24Kc.                                              | 82       |

| Tabela 5.2: Registradores da arquitetura MIPS, alvos de falhas durante os experimentos         |          |

| Tabela 5.3: Tempo de execução dos experimentos para cada benchmark, em cada sistema            |          |

# **SUMÁRIO**

| ΑB  | STRACT                                                | 16 |

|-----|-------------------------------------------------------|----|

| RE  | SUMO                                                  | 17 |

| LIS | STA DE ABREVIATURAS E SIGLAS                          | 18 |

| LIS | STA DE FIGURAS                                        | 20 |

| LIS | STA DE TABELAS                                        | 22 |

| 1   | INTRODUCÃO                                            | 26 |

| 2   | INJEÇÃO DE FALHAS EM PROCESSADORES                    | 29 |

| 2.1 |                                                       | 29 |

| _   | 2.1.1 Injeção de Falhas                               | 30 |

| 2.2 | Abordagens para injeção de falhas em processadores    | 30 |

| 2.3 | Metodologias de Injeção de Falhas                     | 31 |

| 2.4 | Injeção de Falhas em Processadores por Hardware       | 32 |

| 2.5 | Injeção de Falhas por Software                        | 33 |

|     | 2.5.1 Metodologias e Ferramentas de Injeção de Falhas |    |

|     | 2.5.1.1 Ferramenta de injeção de falhas FERRARI       |    |

|     | 2.5.1.2 Ambiente de injeção de falhas Xception        |    |

|     | 2.5.1.3 Sistema de Injeção de Falhas EXFI             | 39 |

|     | 2.5.1.4 Rotinas de Software para Injeção de Falhas    | 41 |

| 2.6 | Injeção de Falhas <i>Built-in</i>                     | 43 |

| 2   | 2.6.1 Módulos de software para injeção de falhas      |    |

|     | 2.6.1.1 Sistema Linux e suporte a tempo real          | 43 |

|     | 2.6.1.2 Módulo de Kernel                              |    |

| 2   | 2.6.2 Injeção de falhas com uso de OCD                | 44 |

| 2.7 |                                                       |    |

|     | 2.7.1 Metodologia de injeção de falhas por simulação  | 47 |

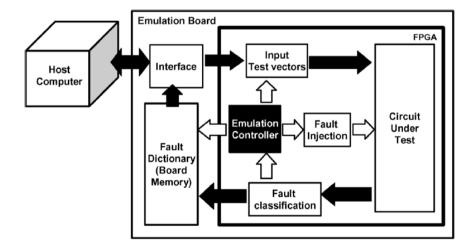

| 2   | 2.7.2 Metodologia de injeção de falhas por emulação   | 51 |

| 3 PLA          | TAFORMAS DE EMULAÇÃO DE PROCESSADORE             | ES 60 |

|----------------|--------------------------------------------------|-------|

| 3.1 Tr         | abalhos Relacionados                             | 61    |

| 3.1.1          | Injetor de Falhas baseado no emulador FauMachine |       |

| 3.1.2          | Sistema integrado de injeção de Falhas           | 61    |

| 3.1.3          | Injeção de falhas para auto teste                | 61    |

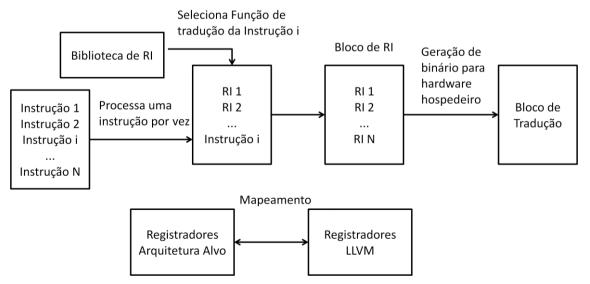

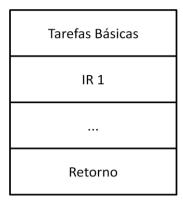

|                | adução Dinâmica                                  |       |

| 3.2.1          | Processo de tradução de instruções               |       |

| 3.2.2<br>3.2.3 | Representação Intermediária                      |       |

| 3.2.3          | Dinamica de Execução de Codigo Binario           | 04    |

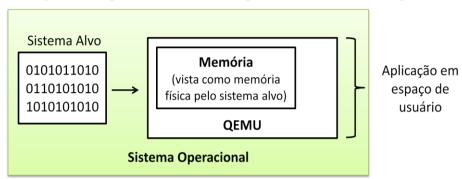

|                | ataforma de Emulação de Processadores QEMU       |       |

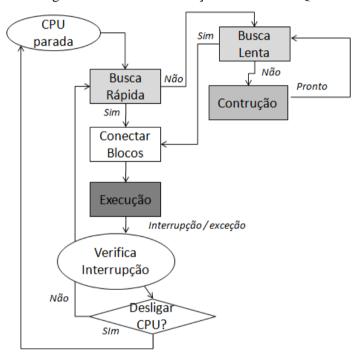

| 3.3.1<br>3.3.2 | Estrutura de execução da máquina QEMU            |       |

| 3.3.3          | Tradutor dinâmico TCG                            |       |

|                | POSTA DE METODOLOGIA DE INJEÇÃO DE FAL           |       |

| 4.1 Re         | dução de Limitações                              | 68    |

| 4.2 Me         | odelo de Falhas                                  |       |

| 4.2.1          | Elementos de Memória                             |       |

| 4.2.2          | Alvos e parametrização                           |       |

|                | 2.1 Referência de tempo                          |       |

|                | 2.2 Memória                                      |       |

|                | 2.4 Dispositivos de entrada e saída              |       |

|                | 2.5 Rotinas de Injeção de Falhas                 |       |

| 4.2.3          | Modificações no processo de tradução dinâmica    |       |

| 4.2.4          | Classificação de Falhas                          |       |

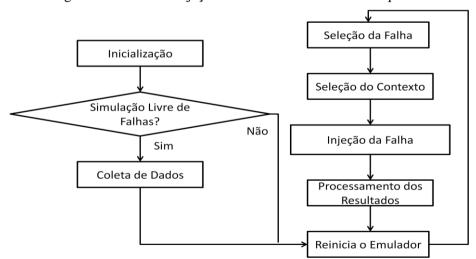

| 4.3 Flu        | ıxo de Injeção de <i>Soft Errors</i>             | 76    |

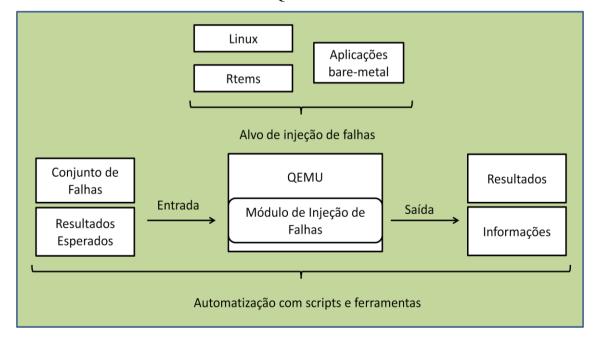

| 4.4 En         | nulação de Sistemas Complexos                    | 77    |

| 4.5 Inj        | jetor de Falhas baseado no Emulador QEMU         |       |

| 4.5.1          | Instrumentação e ferramentas                     |       |

| 4.5.2          | Ciclo de trabalho do ambiente de experimentação  | 80    |

|                | SULTADOS DA INJEÇÃO DE FALHAS DA METODO<br>A     |       |

| 5.1 Co         | onfiguração do ambiente de experimentação        |       |

|                |                                                  |       |

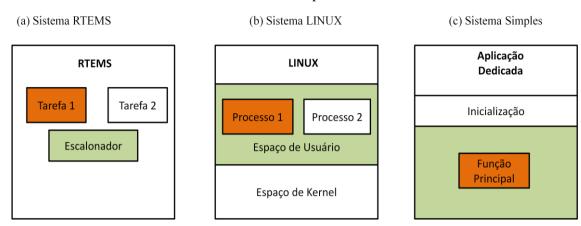

| 5.2 Est        | trutura dos sistemas alvo de falhas              | 81    |

|                | jeção de Falhas em Registradores                 |       |

| 5.3.1          | Distribuição de Falhas                           |       |

| 5.3.2          | Comparação de handhade de sistemas               |       |

| 5.3.3          | Comparação de benchmarks                         | 86    |

|                | jeção de Falhas na Memória                       |       |

| 5.4.1          | Abordagem para injeção de falhas na memória      | 88    |

| 5.4 | 4.2 Classificação das falhas para o caso da memória | 88  |

|-----|-----------------------------------------------------|-----|

| 5.5 | Considerações sobre testes exaustivos               | 89  |

| 5.6 | Tempo de Execução dos Experimentos                  | 91  |

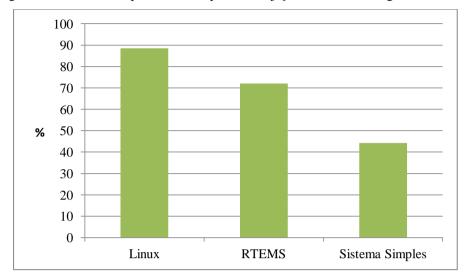

| 5.7 | Análise comparativa de desempenho                   | 93  |

| CON | NCLUSÃO                                             | 95  |

| REF | FERÊNCIAS                                           | 97  |

| APÊ | ENDICE A – ARTIGO LATW (2014)                       | 103 |

# 1 INTRODUÇÃO

O uso de processadores comerciais em aplicações críticas tem sido realidade no desenvolvimento de soluções tecnológicas. Denominados de Commercial Off-The-Shelf (COTS), esses processadores comerciais representam o estado da arte da indústria de semicondutores. Com alto nível de integração em virtude da baixa dimensão dos transistores, é possível alcançar altas taxas de frequência de operação com baixo consumo de potência. No entanto, tais tecnologias estão mais vulneráveis a falhas transientes, ou soft errors, causados pelos efeitos da radiação e interferências eletromagnéticas. Desprovidos de mecanismos de tolerância a falhas muito presentes em processadores para aplicações espaciais e militares, os dispositivos COTS ficam mais suscetíveis aos efeitos conhecidos como singulares, (SEEs - do inglês, Single Event Effects). Estes efeitos singulares são caracterizados pela interação de partículas energizadas com dispositivos semicondutores, produzindo comportamentos indesejados no sistema. Devido ao impacto de uma partícula em uma junção PN, localizada em um nó sensível de um circuito, através da transferência de energia da partícula para o nó, pares elétrons-lacuna podem ser gerados e uma corrente produzida. A interpretação desta corrente no circuito pode acarretar alterações no comportamento deste, e consequente efeito no software em execução (DODD, 2003).

Para viabilizar o uso de dispositivos COTS em aplicações críticas, o desenvolvimento de mecanismos de tolerância a falhas em software surge como uma abordagem eficiente e largamente empregada. Com foco em confiabilidade, estas aplicações integram na sua estrutura mecanismos de recuperação diante dos erros detectados, com o mínimo de impacto no desempenho e alteração do comportamento original da aplicação (RHOD, 2008). Contudo, para o processo de validação destes mecanismos de tolerância a falhas, é necessário submeter a aplicação em condições semelhantes a que ela será exposta em uma situação real. Neste cenário, o uso de técnicas de injeção de falhas é altamente empregado para validar a eficiência destas técnicas, permitindo assim uma melhor avaliação da solução proposta.

Injeção de falhas é uma técnica efetiva de análise para permitir um melhor entendimento do comportamento de um sistema quando falhas são introduzidas sob o sistema alvo (IYER, 1995). Dependendo da técnica de injeção de falhas utilizada para avaliação do sistema, é necessário construir uma infraestrutura para este fim, contemplando laboratórios com equipamentos dedicados, tais como aceleradores de partículas, lasers, etc. Outra abordagem muito comum é ter o modelo de comportamento de hardware do processador descrito em alto nível, normalmente nas linguagens VHDL (VHSIC Hardware Description Language) ou Verilog, para realização da injeção de falhas. Nesta situação, as falhas são injetadas por simulação, ou por emulação, sendo esta última com uso de prototipação em FGPA (Field Programmable Gate Array).

Para o caso de dispositivos COTS, o modelo de comportamento de hardware de um processador raramente é disponibilizado por parte de fabricantes, inviabilizando o uso de descrição de hardware no processo de injeção de falhas. Em virtude disso, se faz necessário o uso do hardware final do processador ou, para o caso de um hardware mais dedicado a uma aplicação, um ASIC (*Application Specific Integrated Circuit*), em conjunto com a utilização de técnicas de injeção de falhas que se utilizem de radiação. Em tal situação, o aumento de demanda em termos de custo e tempo de desenvolvimento tem grande impacto em projetos.

Uma alternativa a descrição de hardware é o uso do modelo de hardware descrito em software, utilizado em emuladores de arquiteturas, ou máquinas virtuais. Tais modelos são disponibilizados por parte de fabricantes de processadores para viabilizar aplicações com suporte a virtualização e também para permitir o desenvolvimento de software em fases iniciais de projeto, sem a presença do hardware final, ainda em processo de elaboração (CHANG, 2013; MARGINEAN, 2014). Com base nisso, em posse do código fonte destes modelos para emuladores, falhas podem ser injetadas durante a emulação.

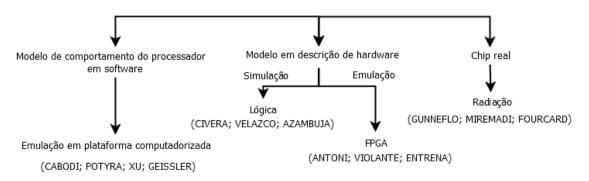

Diante da variedade de técnicas de injeção de falhas disponíveis é possível classificar os métodos posicionando alguns autores que representam grupos de trabalho os quais utilizam determinado método. Na figura 1.1 são definidas basicamente as categorias com base no tipo de modelo do processador alvo de falhas. A primeira categoria representa emulação de modelos de hardware descritos em software, utilizados em emuladores. Cabe salientar que o termo emulação utilizado nesta dissertação, quando se referindo ao modelo de processador descrito em software, referese em recriar as funções originais de processador em outro, visando desempenho de execução. Neste caso, não há compromisso em reproduzir os estados internos do hardware real. Em contrapartida, o termo simulação envolve modelar fielmente ou tão próximo quanto possível os estados internos de um processador e arquitetura organizacional, permitindo neste caso a execução de um pipeline, por exemplo. No entanto, pode se encontrar na literatura o emprego do termo de forma errada, causando em muitos casos confusão. A segunda categoria contempla o uso de modelos de hardware para simulação lógica e emulação em FPGA. E finalmente o último grupo, aplicado quando se tem por finalidade uma análise mais realística, faz uso da injeção de falhas por hardware, com uso de radiação.

Figura 1.1: Categorização dos métodos de injeção de falhas em função do modelo de processador e posicionamento de alguns autores nestas categorias.

Este trabalho tem por finalidade apresentar uma metodologia de injeção de falhas baseada em emulação de processadores. O trabalho é direcionado a redução das limitações apresentadas por outras técnicas, visando o aumento do desempenho de execução de experimentos, bem como a estruturação de um método flexível e aplicável a qualquer arquitetura de processadores, incluindo processadores COTS. Além disso, o trabalho proposto contribui com melhorias em relação a publicações recentes na literatura, que fazem uso de emulação de processadores para injeção de falhas (XU, 2012; YI, 2013). Outra proposta feita no trabalho é sua aplicabilidade no desenvolvimento e análise de técnicas de tolerância para sistemas operacionais. Tal motivação tem origem com base em limitações apresentadas por certas técnicas de injeção de falhas, como é o caso da simulação de descrição de hardware, por exemplo. Devido ao alto tempo necessário para simulação de hardware e software complexos, seu uso se torna restrito. Neste contexto, a emulação de processadores pode ser uma alternativa para acelerar os experimentos de forma considerável.

Este trabalho esta organizado da seguinte maneira: o capítulo 2 apresenta uma breve introdução a falhas transientes oriundas da radiação, abordando também técnicas e metodologias de injeção de falhas em processadores e injetores de falhas aplicáveis neste contexto; o capítulo 3 apresenta plataformas de emulação de processadores e também conceitos utilizados na parte experimental do trabalho; o capítulo 4 apresenta uma proposta de metodologia de injeção de falhas com uso de emulação de processadores, juntamente com um ambiente de injeção de falhas desenvolvido com base na metodologia proposta, fazendo uso do emulador de processadores QEMU (BELLARD, 2005); o capítulo 5 apresenta os experimentos e resultados obtidos com o uso do ambiente de injeção de falhas, para um estudo de caso com a arquitetura MIPS; e para finalizar, o capítulo 6 apresenta as conclusões desta dissertação, publicações decorrentes deste trabalho e as possibilidades de trabalhos futuros.

# 2 INJEÇÃO DE FALHAS EM PROCESSADORES

Os efeitos observados em processadores devido à interação com radiação têm sido preocupantes tanto para o desenvolvimento de software para aplicações espaciais quanto para aplicações em nível terrestre. Os *soft errors* surgem como um resultado destas interações, ocasionando alterações nos elementos de memória utilizados por estas aplicações executadas nestes processadores. Tendo em vista que processadores COTS não possuem foco em tolerância para aplicabilidade em ambientes críticos, o desenvolvimento de software tolerante é uma abordagem para uso neste contexto. Com base nisso, uma variedade de técnicas e ferramentas para injeção de falhas têm sido desenvolvida na literatura para validação destes mecanismos de tolerância.

# 2.1 Falhas transientes causadas pela radiação em dispositivos semicondutores

Efeitos causados pela radiação em processadores podem ser classificados como transientes ou permanentes. Os efeitos transientes não causam quaisquer danos ao circuito em teste, produzindo somente alterações no comportamento e nos valores de elementos de memória utilizados por aplicações. Por outro lado, os efeitos permanentes comprometem o processador em parte ou todo ele, impossibilitando em muitos casos a sua utilização.

#### 2.1.1 Injeção de Falhas

As técnicas de injeção de falhas buscam modelar os efeitos singulares para reproduzi-los durante o processo de execução de uma aplicação em um processador. Tais efeitos podem ser classificados em duas categorias, conforme Dodd (DODD, 2003): (a) single-event upsets (SEUs) e (b) single-event transients (SETs). Os SEUs são inversões de valores lógicos (bit-flips) em elementos de memória comumente utilizados por processadores, tais como registradores ou células de memória. Nesta situação, um dos bits de um byte pode ser invertido logicamente devido ao efeito causado por partículas em circuitos integrados, ocasionado assim comportamentos inesperados em uma aplicação em execução no processador, dependendo da situação. Para o caso em que múltiplos bits são alterados, a denominação para este tipo de efeito é single-event multiple-bit upsets (MBUs), podendo ser observado em elementos de memória do circuito tão bem como no mesmo byte. Outro efeito bastante preocupante em dispositivos semicondutores está relacionado a pulsos transientes propagados na lógica combinacional de um circuito, os SETs, pois estes podem ser interpretados pelo circuito gerando alterações em um ou mais elementos de memória (BALEN, 2010).

#### 2.1.2 Propriedades das técnicas de injeção de falhas

Para definição de um método comparativo entre diferentes abordagens e técnicas de injeção de falhas, Arlat (ARLAT, 2003) apresenta uma série de propriedades as quais definem o nível de efetividade das técnicas e possíveis limitações, são elas:

- Alcançabilidade: define a propriedade de gerar falhas em locais específicos ou muitas vezes inacessíveis para certos tipos técnicas. Um exemplo seria possibilidade de acesso a partes que compõem o circuito integrado;

- Controlabilidade: define a propriedade relacionada a espaço e tempo. O espaço simboliza uma determinada localização para injeção de uma ou mais falhas, e o tempo, simboliza o número de ciclos de relógio que devem ser contados até o momento da aplicação de uma falha;

- Repetibilidade: define a propriedade que trata da repetição exata dos experimentos ou com alto grau de exatidão. Dessa forma, tal propriedade depende da controlabilidade sobre espaço e tempo;

- Reprodutibilidade: define a propriedade de reproduzir os resultados obtidos em experimentos anteriores;

- Não intrusividade: define a propriedade de minimização de qualquer impacto no comportamento do sistema;

- Medição de tempo: define a propriedade relacionada à aquisição de informações de tempo, como contagem de ciclos de relógio, com associação aos eventos observados no experimento. Em alguns casos, um processador de referência é utilizado para geração de resultados;

- Eficácia: define a propriedade de redução do número de experimentos não significantes, que não produzem efeito no sistema alvo, produzindo erros de medida. Normalmente a abordagem para redução desta ineficácia é o aumento da amplitude, tempo ou duração dos estímulos, ou interferência física aplicada ao hardware em teste.

#### 2.2 Abordagens para injeção de falhas em processadores

O uso de descrição de hardware para o processo de injeção de falhas em processadores é uma técnica muito comum na análise de mecanismos de tolerância. Com base na simulação lógica, utilizando-se de ferramentas como ModelSIM® (MENTOR GRAPHICS, 2014), é possível injetar falhas alterando-se elementos que definem o comportamento do hardware, por meio de recursos do simulador ou instrumentação do código VHDL ou *Verilog*. Outra abordagem aplicável ao uso da descrição de hardware é a injeção de falhas durante a emulação em FPGA, por meio de prototipação. Neste cenário, alterações no código que programa a FPGA, ou módulos de hardware para injeção de falhas agindo como sabotadores, são algumas das abordagens normalmente empregadas.

Diante da falta da descrição de hardware, outra abordagem aplicável é a utilização de emulação por software. Neste tipo de técnica é necessário ter o modelo do processador descrito em software. Com a utilização de uma máquina virtual, falhas podem ser injetadas por meio de alterações no código fonte do emulador e modelo, sendo estas aplicadas durante o processo de emulação. Além desta, outra técnica muito comum e mais realística é a injeção de falhas por radiação, submetendo o processador a um feixe de partículas, de forma que estas produzam alterações nos elementos de

memória do hardware real. Neste último, aceleradores de partículas podem ser utilizados para este fim.

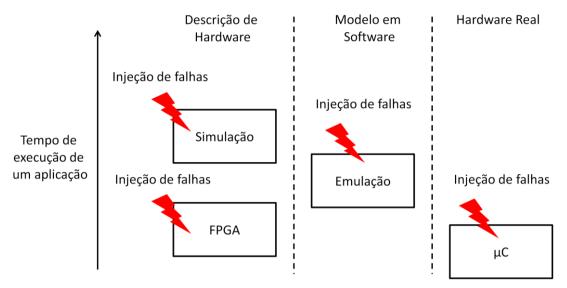

Figura 2.1: Aspectos relativos ao desempenho de execução de aplicações em função da técnica de injeção de falhas com diferentes abordagens.

Tendo em vista a variedade de técnicas de injeção de falhas aplicáveis para realização de testes, normalmente o desempenho de execução associado a cada técnica pode ser um fator determinante para escolha da mais apropriada. Na figura 2.1 são apresentadas as abordagens que fazem uso de descrição de hardware, modelo em software e hardware real do processador. É possível notar que quanto mais próximo do hardware, para os casos da injeção de falhas em emulação com FPGA e por radiação, mais rápido é o desempenho de execução de uma aplicação, visando à aproximação da frequência alvo do processador. Sendo assim, quando se quer desempenho, a tendência é optar por técnicas que se aproximam do hardware, tanto quanto possível. Para o caso de técnicas de injeção de falhas com utilização de modelo do processador em software, é possível verificar um aumento em desempenho de execução das aplicações alvo de falhas em comparação a simulação lógica. É importante destacar, que com tal abordagem também é possível injetar falhas em aplicações mais complexas, tais como sistemas operacionais, normalmente não utilizadas com técnicas de simulação. Além disso, fatores relacionados ao desempenho de emulação por software estão diretamente associados ao hardware hospedeiro e qualidade do emulador, podendo este, se aproximar do desempenho do hardware real, dependendo da situação.

### 2.3 Metodologias de Injeção de Falhas

Os estudos na literatura relacionados ao desenvolvimento de metodologias e ferramentas para injeção de falhas, aplicáveis na realidade de processadores, normalmente fazem uso de uma das seguintes abordagens:

- Injeção de falhas por hardware;

- Injeção de falhas por software;

- Injeção de falhas built-in;

- Injeção de falhas por simulação.

A injeção de falhas por hardware é uma técnica que depende de equipamentos adicionais ao dispositivo o qual se está analisando. Sendo considerada uma técnica mais realística utiliza-se de equipamentos que possibilitam emular condições ou gerar erros em circuitos integrados. A principal finalidade desta é viabilizar a observação do comportamento do sistema diante de um modelo de falhas em que se tem interesse. Aceleradores de partículas são utilizados para injetar falhas dentro de circuitos integrados. O uso de feixe de íons é comumente aplicado em tal situação para avaliar soft errors no sistema observado (GUNNEFLO, 1989; MIREMADI, 1995). Outro método aplicado nesta abordagem é a utilização de lasers (laser facilities), que apresenta uma técnica não invasiva, não destrutiva e controlada, para geração de erros (SAMSON, 1997). A injeção de falhas por software permite através do uso de módulos de software, a modificação do conteúdo de elementos de memória utilizados pelas aplicações em execução. Tais elementos são afetados e erros são emulados sem a necessidade de hardware adicional. Outro aspecto fundamental de tal abordagem é a não necessidade do protótipo ou versão final de hardware em fases iniciais de projeto (KANAWATI, 1995; CARREIRA, 1995). No entanto, tal técnica, conhecida como injeção de falhas baseada em software, ou software-implemented fault injection (SWIFI), necessita de alta intrusão, sendo muitas vezes necessária a modificação do código fonte da aplicação, comprometendo o desempenho de execução da mesma. Uma alternativa em relação a abordagem SWIFI tradicional, é apresentada pelo uso de emulação de processadores (POTYRA, 2007; CABODI, 2010). Nesta abordagem, o método de injeção de falhas está associado à utilização de um emulador de processadores para injeção de falhas, ou utilização deste para validação de técnicas baseadas em SWIFI. A injeção de falhas do tipo built-in é baseada no princípio do uso de módulos de software, suportados por sistemas operacionais ou uso de interfaces de depuração. A primeira baseia-se no uso de módulos do Kernel do sistema operacional Linux (LINUX KERNEL ORGANIZATION, 2014), ou mecanismos semelhantes de outros sistemas operacionais. Já a segunda faz uso de interfaces de depuração do hardware alvo de falhas. Tais interfaces estão presentes na maioria dos processadores mais recentes, permitindo o acesso a registradores e/ou posições de memória para devida emulação de falhas (FIDALGO, 2006). Por fim, a injeção por falhas está relacionada a injeção de falhas no modelo de descrição de hardware, ou HDL (Hardware Description Level (JENN, 1994; BOUÉ, 1998; FOLKESSON, 1998) que normalmente é aplicada para esse fim. Outra variante desta técnica é o uso de prototipação em FPGA (Field Programmable Gate Array) (ANTONI, 2001; CIVERA, 2001) do processador alvo, proporcionando um maior número de possíveis simulações em um tempo consideravelmente inferior a outras técnicas.

### 2.4 Injeção de Falhas em Processadores por Hardware

Técnicas de injeção de falhas baseadas em hardware podem ser classificadas em duas categorias (HSUEH, 1997): (a) injeção de falhas com contato, no qual o injetor requer contato físico com o hardware em teste, explorando modificações nas condições de corrente e voltagem do sistema alvo e (b) injeção de falhas sem contato, em que o uso de equipamentos externos utilizados não exige contato com o circuito ou sistema alvo em teste. Esta última utiliza-se de fenômenos físicos para geração de erros no

sistema alvo como, por exemplo, aceleradores de partículas com utilização de íons pesados. Tais técnicas permitem o acesso a partes do sistema que outros métodos de injeção de falhas não conseguem acessar, impossibilitando a análise completa da solução de tolerância.

A modelagem de falhas deve descrever o mais próximo possível a realidade a qual o equipamento será submetido, neste caso a radiação. Falhas transientes produzidas por íons pesados, gerando SEUs em circuitos integrados, exemplificam uma boa abordagem para análise de mecanismos de tolerância a falhas (GUNNEFLO, 1989; MIREMADI, 1995). Este tipo de abordagem, a qual se utiliza de bombardeamento de circuitos por meio de um feixe de partículas, é definida como teste de radiação em nível terrestre. Bastante difundida, se baseada na utilização de feixes originados por aceleradores de partículas. Nesta técnica, a fidelidade à geração de condições espaciais é função direta da energia do feixe de partículas para um dado valor de transferência linear de energia, (LET - do inglês, *Linear Energy Transfer*). Feixes com alta energia reproduzem com maior aproximação o ambiente espacial. No entanto, há alto custo e alta complexidade para utilização de tal técnica.

Além de injeção de falhas utilizando feixe de íons pesados, é possível utilizar feixe de prótons, permitindo alta transferência de energia, chegando a valores de pico de 230 MeV em comparação a valores típicos gerados por feixes de íons pesados, que atingem em torno de 100 MeV. Dentre as maiores limitações apresentadas por aceleradores de partículas, podem ser destacadas: (i) disponibilidade, (ii) alto custo e (iii) informações sobre espaço e tempo (REED, 2003).

Diante das limitações apresentadas por técnicas comumente utilizadas, uma série de alternativas a injeção de falhas por meio de feixe de partículas tem sido explorada como, por exemplo, laser por pulso e micro feixes. O laser por pulso tem por princípio aumentar a controlabilidade e reprodutibilidade de geração de SEEs. Basicamente, são gerados pulsos de luz de aproximadamente 1 pico segundo com energia suficiente para a geração de pares elétron-lacuna no semicondutor em questão. Para o caso do micro feixe, o princípio baseia-se no uso de campo magnético e campo elétrico. O conjunto de íons, gerado pelo acelerador de partículas, passa por um conjunto de ímãs para produção de diâmetro menor que 1 micro metro e é acelerado pelo campo elétrico. Para valores de diâmetro em torno de 10 micro metros, a energia cai de 50 MeV para 15 MeV (REED, 2003).

Embora a técnica de injeção de falhas baseada em hardware se aproxime de situações reais, a mesma necessita de equipamentos dedicados para execução de experimentos e, em consequência disso, o custo do projeto tende a aumentar. Em adição, aspectos como controlabilidade e reprodutibilidade representam problemas evidentes nos experimentos. O uso de tal técnica é recomendado para fases finais do processo de desenvolvimento, sendo utilizadas outras técnicas nas demais etapas do projeto.

### 2.5 Injeção de Falhas por Software

Na busca por redução de custo no desenvolvimento de projetos, técnicas de injeção de falhas baseadas em software surgem como uma solução atrativa em virtude da não necessidade de um hardware customizado. Técnicas de SWIFI permitem que em alto

nível se possa acessar hardware e software de forma a reproduzir falhas enfrentadas em situações reais em ambientes com radiação (CARREIRA, 1998).

O desenvolvimento de ferramentas bem como o aprimoramento de técnicas já existentes são objetos de estudo constantes para emulação de ambientes de radiação. Outro fator importante a ser considerado é a flexibilidade quanto ao tipo de aplicação que se deseja executar no sistema alvo. Sistemas operacionais ou aplicações mais complexas podem ser executados em oposição a limitações apresentadas por outras técnicas.

O efeito da radiação em recursos de hardware, como registradores, é normalmente analisados com o uso de emulação de SEUs. Para tal se faz necessária a definição de um modelo de falhas para aplicação da mesma. Entretanto, injeção de falhas por software pode enfrentar uma série de limitações, conforme Hsueh e Carreira (HSUEH, 1997; CARREIRA, 1998):

- Inacessibilidade do software a certos recursos os quais se tem interesse em injetar falhas;

- Limitação de mecanismos para disparar o processo de injeção de falhas;

- Comprometimento da execução da aplicação ou sistema operacional em diversos aspectos devido à instrumentação no software em execução;

- Monitoramento do sistema para coleta de dados para análise do impacto causado por uma falha, ocasionando em muitos casos problemas no desempenho;

- Reprodução de eventos reais emulados em software;

- Baixa resposta em resolução de tempo para verificação de propagação de erros em recursos de hardware utilizados;

- Dificuldade de portabilidade para outros processadores devido a metodologias amarradas a certos recursos da plataforma de hardware em uso.

Tais fatores são diretamente relacionados ao nível de intrusividade da técnica utilizada.

Injeção de falhas pode ser realizada por qualquer tipo de instrução disponível em processadores que tenham acesso a memória e/ou registradores (BENSO, 1999). Tal procedimento pode ser realizado normalmente por dois métodos distintos, conforme Hsueh (HSUEH, 1997), como segue:

- Injeção de falhas em tempo de compilação;

- Injeção de falhas em tempo de execução.

O método de injeção em tempo de compilação realiza a injeção de falhas por meio de modificação do código fonte ou *assembly* em tempo de compilação. Dessa forma, o procedimento pode alterar tanto um recurso, como um registrador, quanto a própria elaboração do software, emulando uma situação de erro gerada pelo hardware. Sendo uma técnica estática, é normalmente utilizada para simulação de falhas permanentes. Além do processo de injeção, se faz necessária a alteração do software para verificação do efeito causado pela falha, não necessitando de outro programa para análise. Nesta técnica é possível notar o alto nível de intrusividade e limitação quanto a possibilidade de dinâmica no processo de injeção. Para solucionar tal requisito, o método de injeção de falhas em tempo de execução tem por finalidade injetar falhas enquanto a aplicação está sendo executada no processador, podendo assim emular uma situação de falha transiente. Sendo um processo dinâmico, deve existir um meio de parametrizar os

experimentos como, por exemplo, especificar o instante de tempo para injeção de uma falha. Recursos como interrupção, presentes em processadores, podem ser utilizados de forma que sub-rotinas sejam acionadas para injeção das falhas. Outros recursos como traps ou exceptions podem ser acionados com o uso de instruções especiais inseridas no código fonte, como breakpoints. Este tipo de procedimento permite a injeção de uma falha em elementos de memória antes, após ou durante seu uso em um processador.

#### 2.5.1 Metodologias e Ferramentas de Injeção de Falhas

#### 2.5.1.1 Ferramenta de injeção de falhas FERRARI

O desenvolvimento de ferramentas de injeção de falhas tem sido proposto na literatura como um meio de validação de técnicas e metodologias de injeção de falhas (KANAWATI, 1995; CARREIRA, 1998). Devido ao alto grau de acessibilidade a recursos de hardware atualmente disponibilizados por processadores, a injeção de falhas emulada por software pode ser uma abordagem de baixo custo e sem riscos de danificação ao processador em avaliação. Em contraste, as técnicas de injeção de falhas com alteração de código fonte ou *assembly*, bem como modificação em tempo real do programa em execução, Kanawati (KANAWATI, 1995) propôs uma metodologia menos intrusiva, sem necessidade de alteração do programa executado no sistema alvo. Para validação da técnica proposta foi desenvolvida uma ferramenta chamada FERRARI (*Flexible Software-based Fault and Error Injection System*). Esta ferramenta baseia-se na utilização de um processo ou programa adicional ao conjunto de programas já existentes em execução no sistema alvo, que é responsável por corromper elementos de memória em uso pelo processo ou programa alvo em execução.

Sistema Operacional 1 5 6 9 8 7 4 3 2

Processo Injetor de Falhas Processo alvo

Figura 2.2: Estrutura de simulação de injeção de falhas da ferramenta FERRARI.

Fonte: Figura adaptada de (KANAWATI, 1995).

A figura 2.2 ilustra a metodologia de injeção de falhas, que é composta pelo processo injetor de falhas e processo alvo.

Toda sistemática de alteração de valores de elementos de memória utilizados pelo processo alvo é realizada com o uso de chamadas de sistemas presentes no ambiente UNIX. Dessa forma, toda e qualquer alteração no processo alvo passa pelo Kernel do sistema operacional em execução. A ferramenta FERRARI, a qual incorpora a metodologia, divide a simulação em 9 passos, conforme segue abaixo:

- 1. Requisição para criação do programa alvo, utilizando a chamada de sistema fork1:

- 2. Kernel do sistema cria o processo alvo;

- 3. Configuração do processo alvo de forma que o mesmo possa ser monitorado por outro processo, através do uso da chamada de sistema *ptrace* (LINUX PTRACE MAN PAGE);

- 4. Requisição para execução do processo alvo por parte do Kernel;

- 5. Recepção de notificação de estado de início de execução do processo alvo por parte do Kernel;

- 6. Requisição para alteração de elementos de memória com possível uso por parte do processo alvo, realizada através da chamada *ptrace*;

- 7. Alteração do programa conforme requisição, através do uso da chamada *ptrace*;

- 8. Finalização do programa alvo;

- 9. Notificação de terminação do processo alvo.

A estrutura de implementação do sistema FERRARI é composta por um conjunto de módulos: (i) módulo de inicialização e ativação, (ii) módulo de parametrização, (iii) módulo de injeção de falhas e (iv) módulo de coleta e análise de dados. O módulo de inicialização tem por função mapear recursos utilizados pelo programa alvo e realizar uma execução livre de falhas, na qual ocorre o armazenamento do resultado da execução do programa para futuras comparações. O módulo de parametrização interpreta entradas do usuário para o processo de simulação, tais como tempo de simulação, tipo de falhas e modelos de falhas. A tabela 2.1 apresenta um resumo dos parâmetros disponibilizados pela ferramenta para injeção de falhas na aplicação alvo. É importante destacar o parâmetro de modelo de falhas, o qual mapeia falhas de baixo nível, observadas em hardware, para falhas em alto nível, emuladas por software.

Tabela 2.1: Parâmetros de simulação para injeção de falhas.

| Parâmetro        | Descrição                                                                                                                                                                                                                                                                                                                                                                  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tipo de medida   | Seleciona o tipo de medida relacionada ao experimento, são elas: <b>cobertura</b> , que computa a efetividade de detecção por parte dos mecanismos de recuperação de falhas e <b>latência</b> , que mede o tempo de detecção de uma falha de forma que um mecanismo de recuperação possa entrar em ação.                                                                   |

| Localização      | Especifica uma localização na qual se quer injetar uma falha como posição de memória, registrador e etc.                                                                                                                                                                                                                                                                   |

| Tempo            | Especifica o tempo e duração no qual uma falha deve ser injetada, medido em ciclos de instrução. Tal parâmetro pode ser aleatório.                                                                                                                                                                                                                                         |

| Duração          | Seleção entre falhas permanentes e transientes.                                                                                                                                                                                                                                                                                                                            |

| Tipo de Falha    | Alteração de um bit através de uma operação XOR com uma máscara de bits ou alteração de um byte.                                                                                                                                                                                                                                                                           |

| Modelo de falhas | <ul> <li>Seleciona um modelo de falhas para injeção, são eles:</li> <li>Erro de decodificação de instrução: alteração do contador de programa em processo de decodificação de instruções para execução de outra instrução;</li> <li>Erro de operadores: modificação de endereço de memória utilizado em uma instrução que faz operações em posições de memória.</li> </ul> |

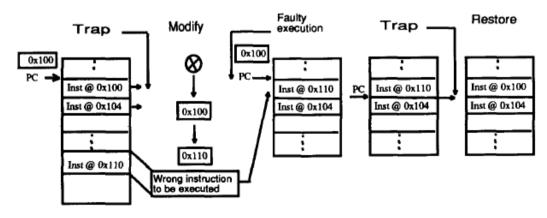

Figura 2.3: Modelo de falhas para execução de instrução errada.

Fonte: KANAWATI (1995).

O processo de injeção de falhas é realizado pelo módulo de injeção. O módulo verifica se a posição de memória definida ou registrador para injeção de uma falha foi

acessado, por meio uma *trap* do processador. Caso seja acessada tal posição, uma ação é executada. A figura 2.3 ilustra o modelo de falhas de erro de decodificação de instrução. Para injeção de uma falha uma máscara de bits é aplicada no contador de programa alterando o seu valor de 0x100 para 0x110. Tal procedimento ocasiona a execução de outra instrução. Após a execução desta outra instrução, é gerado um evento de *trap* e o valor anterior do contador de programa é restabelecido, e então o programa executa a partir da instrução seguinte.

Por fim, após o processo de injeção de uma falha, o módulo de análise e coleta de dados entra em ação. Tal módulo analisa a execução do programa alvo, armazena resultados da execução e guarda valores de latência de detecção de uma falha por parte de mecanismos de recuperação do sistema. O processo de análise de resultados é realizado a partir de arquivos de registros gerados durante as simulações. Tais arquivos permitem ao analisador verificar se o programa terminou normalmente, foi interrompido por um mecanismo de verificação de erro ou uma condição de tempo máximo de execução, pré-definida, foi excedida.

#### 2.5.1.2 Ambiente de injeção de falhas Xception

Como evolução das limitações apresentadas por técnicas que tem alta intrusividade no sistema alvo, Carreira (CARREIRA, 1998) propõe uma metodologia baseada na utilização de recursos de monitoramento e depuração presentes em processadores. O software *Xception* introduz um ambiente de injeção de falhas com mínima interferência na aplicação alvo. Sendo uma técnica de baixa intrusividade, a mesma não prevê alterações na aplicação alvo em execução no sistema operacional. Além de processos em espaço de usuário, tal técnica permite injetar falhas em espaço de Kernel.

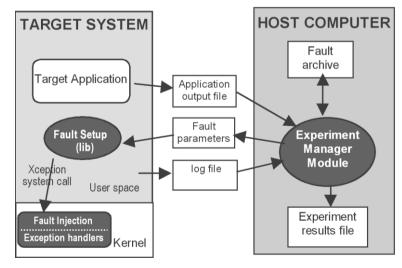

Figura 2.4: Arquitetura do ambiente de injeção de falhas Xception.

Fonte: CARREIRA (1998).

A figura 2.4 apresenta a estrutura do ambiente de simulação *Xception*. O ambiente é composto por um sistema alvo e um computador de controle. A estrutura de software é definida por três módulos, são eles:

- Módulo de Kernel, que suporta rotinas de injeção de falhas e tratamento de exceções do processador;

- Módulo de configuração de falhas, que é uma biblioteca responsável por receber parametrizações provenientes do computador de controle para devida configuração do Kernel;

Módulo de gerenciamento de experimentos ou EMM (Experimental Module Manager), que é um software que executa no computador de controle disponibilizando uma interface de configuração do ambiente, injeção de falhas e coleta e análise dos resultados.

A grande vantagem em relação a outros tipos de técnicas mais intrusivas é a utilização de exceções de hardware programadas via recursos de monitoramento e depuração do processador. Tal abordagem extingue o uso de instruções para geração de traps adicionadas no programa alvo. Outro importante aspecto a salientar é a condição para disparar o processo de injeção de uma falha. O conjunto de critérios ou atributos que podem ser observados é mais amplo, proporcionando mais situações para elaboração de modelos de falhas. No entanto, mesmo sendo uma técnica que tem pequeno impacto na execução da aplicação alvo, ela ainda adiciona intrusividade à medida que necessita alterar o Kernel do usuário por um que contenha a implementação das rotinas de injeção de falhas e configuração dos recursos de hardware utilizados pela metodologia.

#### 2.5.1.3 Sistema de Injeção de Falhas EXFI

O trabalho proposto por (BENSO, 1999) apresenta uma metodologia de injeção de falhas transientes que faz uso de um modo de configuração de processadores conhecido como *Trace Exception Mode*. Desta forma, ao posicionar uma rotina de software na memória para tratar eventos reportados pelo processador, neste modo especial de execução, a mesma se encarrega de computar o tempo para injeção de uma falha, entre outras funções.

Figura 2.5: Ambiente de injeção de falhas EXFI.

Fonte: Figura adaptada de (BENSO, 1999).

O procedimento proposto pelo autor resume-se em injetar a falha e verificar se o processo alvo de injeção de falhas não ultrapassa o limite máximo de tempo de

execução, já pré-definido para os experimentos. Ao contrário das ferramentas FERRARI e Xception, o ambiente de software EXFI (Exception-based Fault Injector) não necessita de qualquer modificação no código da aplicação ou sistema operacional alvo.

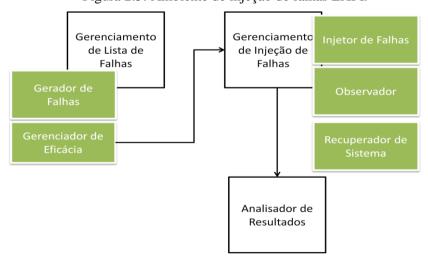

O sistema EXFI é composto basicamente por três módulos responsáveis pelo processo de experimentação. O ambiente de injeção de falhas é apresentado na figura 2.5. O módulo de gerenciamento de lista de falhas é o primeiro bloco acionado pelo processo. O mesmo tem por finalidade gerar uma lista de falhas conforme parametrização do usuário do sistema. O bloco responsável por esta tarefa é denominado gerador de lista de falhas. A especificação do número de falhas, região de memória de interesse e registradores são exemplos de parâmetros comuns os quais o gerador de falhas leva em conta para elaboração desta lista. Após a geração desta, entra em ação o bloco classificado como gerenciador de eficácia. Neste bloco a lista de falhas é otimizada removendo-se falhas as quais já se sabe previamente o efeito que causará no sistema. Outro papel importante é o armazenamento de informações da execução da aplicação ou sistema em condições livres de falhas, chamada simulação livre de falhas. Tais informações serão utilizadas posteriormente pelo módulo de gerenciamento de injeção de falhas (GIF).

O bloco GIF é o bloco mais complexo do ambiente de experimentação. Além da tarefa de injeção de falhas, efetuada com o controle do bloco injetor de falhas, o módulo GIF possui um bloco denominado observador, responsável pela observação dos efeitos causados pela falha. Por fim há o bloco responsável pela recuperação do sistema, denominado recuperador de sistema. Este bloco é aplicável para falhas que ocasionem eventos de hardware, tais como exceções. Nesta situação o bloco necessita de total controle do sistema de forma que uma nova execução da aplicação seja possível mantendo as mesmas condições sem a presença de uma falha. Cabe destacar outras tarefas fundamentais que desempenhadas pelo sistema GIF, são elas:

- Inicialização do sistema, que tem por finalidade carregar a aplicação em uma região de memória para execução;

- Inicialização dos parâmetros de injeção de falhas conforme a falha selecionada a partir da lista;

- Habilitação do monitoramento de execução de código (code tracing) e início de execução;

- Injeção de falhas conforme o número de instruções executadas;

- Verificação do número de instruções máximo pré-definido no experimento;

- Classificação de falhas.

O processo de injeção de falhas é efetuado por uma rotina que se utiliza do modo de monitoramento de execução do processador. Ao ser acionada, a mesma computa o número de instruções. Quando o número de instruções requerido para injeção de uma falha é atingido, a mesma é aplicada. Após a injeção, inicia-se a observação do comportamento da aplicação diante da falha, classificando-se os efeitos observados. São eles:

- Falha silenciosa, representada por uma falha que não produz alteração no comportamento do sistema;

- Mecanismo de detecção de erro (EDM), representado pela detecção presente no próprio software ou sistema;

- Violação por falha silenciosa, representada por uma alteração do comportamento do sistema não detectada por EDM, ocasionando erro nos resultados esperados;

- Limite de tempo de execução, representado pela alteração não detectada do comportamento do sistema que ultrapassa um limite de tempo pré-definido.

Por fim, temos o módulo chamado analisador de resultado, que é responsável por gerar um relatório de todo o processo de experimentação diante da lista de falhas.

#### 2.5.1.4 Rotinas de Software para Injeção de Falhas

Na busca por alternativas de análise dos efeitos da radiação em equipamentos eletrônicos, (VELAZCO, 2000) apresenta uma nova estratégia para geração de *upsets* via injeção de falhas de forma aleatória em localização e tempo. O método *Code Emulating Upset* (CEU), que emula *upsets* por meio de rotinas de software, introduz uma abordagem baseada no uso de recursos assíncronos, tais como interrupções presentes em processadores. Este tipo de abordagem permite a injeção de falhas em meio a execução de aplicações. Tal metodologia leva em conta a limitação de acesso a elementos internos que compõem um processador.

O processo de injeção de falhas é efetuado por uma rotina de software a qual é executada por meio de uma interrupção do processador. A rotina de falha emula um *bit-flip* ou alteração de valor lógico em um elemento de memória como registrador ou posição de memória. A alteração do bit do elemento de memória é realizada por meio da seguinte sequência:

- 1. Leitura do conteúdo do elemento de memória para variável temporária;

- 2. Aplicação de uma máscara de bits com uso de uma operação lógica XOR nesta variável temporária;

- 3. Escrita do valor da variável temporária no elemento de memória alvo da injeção de falha.

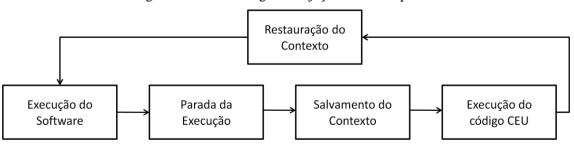

O fluxo de injeção de falhas é ilustrado na figura 2.6. A partir de uma interrupção detectada pelo processador, a execução do software é parada, e então uma rotina programada no vetor de interrupção do mesmo é executada. Tal rotina salva o contexto de execução da aplicação na pilha e salta para posição de memória onde se encontra a rotina de CEU. Após a execução da rotina de CEU, a qual injeta a falha, o contexto de execução da aplicação é retomado e a aplicação segue a execução do ponto onde parou.

Figura 2.6: Metodologia de injeção de falhas por CEU.

Fonte: Figura adaptada de (VELAZCO, 2000).

É importante destacar a flexibilidade de tal técnica, visto que através da manipulação da pilha é possível injetar falhas no contador de programa e outros registradores não acessíveis diretamente por meio do conjunto de instruções. Após o processo de injeção de falhas, começa a etapa de observação dos efeitos no sistema quanto ao resultado esperado após a execução da aplicação. A classificação dos erros é realizada através da comparação do conteúdo de uma região de memória, na qual o programa posiciona estes resultados com os obtidos através de uma execução livre de falhas e a comparação do tempo total de execução com o tempo esperado. São definidos três grupos para classificação de erros. O primeiro grupo, erros tolerados ou mascarados, trata dos erros mascarados durante a execução. Neste grupo são consideradas falhas injetadas em elementos de memória não utilizados pelo programa, assim como falhas injetadas em elementos de memória poucos antes de serem inicializados pela aplicação. O segundo grupo, erros de resultado, trata de erros nos resultados esperados após a execução da aplicação. E por fim, erro de sequência, que engloba uma condição de ultrapassagem de tempo de execução, normalmente ocasionada pela falta de resposta por parte do processador. Tipicamente esse tipo de erro resulta na necessidade de um processo de reinicialização por hardware do processador a fim de iniciar novamente uma nova simulação.

O uso da técnica de injeção de falhas CEUs foi comparado com técnicas de injeção de falhas por radiação demonstrando grande concordância de resultados. Ao contrário de técnicas abordadas por FERRARI, Xception e EXFI, a abordagem sugerida por (VELAZCO, 2000) define uma técnica mais portável para outros processadores, não dependendo de recursos específicos de cada um. Outra abordagem para validação de técnicas de detecção de falhas em nível de software foi utilizada por (NICOLESCU, 2001). A técnica consiste na utilização de um processo adicional, executando simultaneamente a aplicação alvo, denominado injetor de falhas. Tal aplicação aguarda um período de tempo aleatório e quando o mesmo é esgotado seleciona um elemento de memória e bit aleatórios para injeção de uma falha. Após a injeção da falha, o injetor observa o comportamento e transmite os resultados para um computador pessoal que controla os experimentos. Contrastando a técnica de CEU, a técnica citada acima é mais intrusiva, visto que executa uma aplicação com a função de sabotar no mesmo processador em que executa a aplicação alvo de falhas. Para casos em que se necessita de tempo de resposta de uma aplicação, como as de tempo real, o uso de um processo concorrente para injeção de uma falha acarreta no comprometimento da simulação de um ambiente mais realístico.

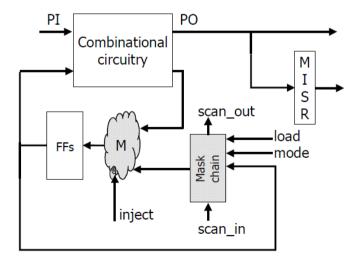

Uma abordagem semelhante ao método CEU foi utilizada por (ACLE, 2011). Visando analisar técnicas de tolerância por meio de redundância de tarefas em sistemas baseados em FPGA, com uso de memória SRAM executando IP core do processador NIOS-II, o autor propôs uma técnica de validação através do uso de uma rotina de injeção de falhas por software, executada em contexto de interrupção. O método se baseia na injeção de SEUs em partes acessíveis por software. A rotina de injeção de falhas é ativada durante a execução de uma aplicação. O acionamento é realizado em tempo aleatório, medido em ciclos de relógio. A seleção do elemento de memória alvo da injeção da falha e máscara de bits a ser aplicada para geração de SEU, via operação lógica XOR, são especificadas em uma região de memória acessada externamente por meio de uma interface de depuração (debug interface) do processador, por meio de computador de controle dos experimentos. Ao final da injeção de uma falha inicia-se a etapa de análise e classificação dos erros observados no sistema. Tendo em vista a

atratividade do uso FPGAs em aplicações críticas, tal metodologia possibilita avaliar e auxiliar no desenvolvimento de técnicas para melhorar a confiabilidade de sistemas baseados em IP cores.

Em uma análise comparativa de três técnicas de injeção de falhas por hardware e uma técnica SWIFI, (ARLAT, 2003) utiliza-se de uma abordagem alternativa de injeção de falhas por software. A mesma baseia-se na injeção de falhas antes da execução do código de máquina. O método altera o código de máquina antes de carregar a aplicação no processador. Sendo a falha injetada somente na aplicação alvo, o nível de intrusividade é baixo. Além disso, tal técnica permite uma acessibilidade não permitida por alteração de código fonte. No entanto, tal técnica é menos realística para falhas transientes, visto que simula somente falhas permanentes.

#### 2.6 Injeção de Falhas Built-in

A técnica de injeção de falhas do tipo *built-in* representa o grupo de técnicas que são desenvolvidas dentro do sistema em teste, podendo ser acionado em tempo real para realização de injeção de falhas. Porém, cabe separar esta abordagem em dois tipos: (i) desenvolvida exclusivamente por software, utilizando para isso módulos de software para injeção de falhas ou (ii) desenvolvida com o uso de uma interface de depuração suportada pelo próprio equipamento em teste, alvo da injeção de falhas. Esta interface é conhecida como recurso de depuração comum dentro do próprio circuito integrado ou OCD (*Common On-Chip Debugging*).

#### 2.6.1 Módulos de software para injeção de falhas

Com a tendência de utilização de COTS adotada no desenvolvimento de aplicações críticas, surgiu a necessidade de validação de recursos de tolerância implementados em software. O sistema embarcado que viabiliza a função do produto requer alto grau de recuperação diante de eventos externos caracterizando a confiabilidade do sistema. Tendo em vista tal necessidade, Cabodi (CABODI, 2010) propõe um sistema integrado de injeção de falhas para utilização tanto em plataformas reais de hardware quanto em ambientes de simulação. Neste último o objetivo é antecipar, em fases iniciais de projeto, problemas que podem ocorrer na plataforma real de hardware.

A proposta de um framework independente de arquitetura é sugerida pelo autor com base no uso de módulos de Kernel do sistema operacional Linux para emulação de SEUs. Um aspecto destacado é a possibilidade de injeção de falhas em sistemas de tempo real (RT – do inglês, *Real-Time*). A abordagem destaca a não utilização de recursos de depuração normalmente presentes em dispositivos COTS que, quando utilizados, acabam degradando ou comprometendo o desempenho em termos de requisito de tempo de execução, muito importante para aplicações de tempo real. Outro aspecto a salientar é a baixa intrusividade do suporte em software para injeção de falhas, que não necessita parar a execução do Kernel para injetar uma falha.

#### 2.6.1.1 Sistema Linux e suporte a tempo real

A utilização do sistema operacional Linux, objeto de estudo para validação da metodologia empregada nos experimentos de Cabodi (CABODI, 2010), é justificada

devido a premissa de sistemas atuais necessitarem de maior complexidade no software para gerenciamento do hardware. Desta forma, aplicações para determinado fim acabam por executar em um sistema mais complexo. O Linux não é um sistema de tempo real em sua natureza. Sendo assim, uma série de modificações se faz necessária em sua estrutura para suportar aplicações em tempo real. Alguns projetos como XENOMAI (XENOMAI PROJECT, 2014), entre outros, tentam dar suporte a um escalonamento de tarefas mais apropriado para tempo real.

#### 2.6.1.2 Módulo de Kernel

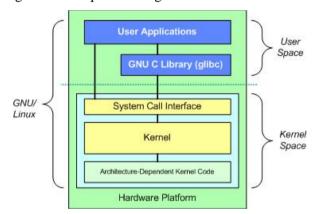

A estrutura básica de um sistema operacional Linux pode ser visualizada na figura 2.7. Nesta estrutura temos como primeira camada o espaço de usuário, onde as aplicações executam. A segunda camada é denominada de espaço de Kernel, onde módulos são responsáveis por gerenciar recursos de hardware entre outras funções. A comunicação entre espaço de Kernel e espaço de usuário é realizada através de chamadas de sistema, disponibilizadas por uma biblioteca escrita em linguagem C. Sendo considerado um sistema modular, o Linux permite que módulos de Kernel sejam carregados em tempo real ou integrados ao próprio Kernel em tempo de compilação.

Figura 2.7: Arquitetura organizacional do sistema Linux.

O framework proposto por Cabodi (CABODI, 2010) tem, como um dos elementos que compõem o sistema, um módulo não integrado ao Kernel do sistema operacional Linux. Tal módulo é o elemento central do framework. Através dele é possível coletar estatísticas, verificar informações da memória virtual e acessar elementos de memória os quais a aplicação alvo de injeção de falhas irá utilizar na sua execução. Através deste módulo é então possível injetar falhas de uma forma mais rápida, eficiente e transparente para aplicação, visto que tais ações são executadas em espaço de Kernel.

#### 2.6.2 Injeção de falhas com uso de OCD

Na busca por uma solução de baixo custo, mais integrada e efetiva para injeção de falhas, outra técnica, também classificada como *built-in*, é a injeção de falhas por emulação utilizando-se de interfaces de depuração ou *debug* presentes em processadores (FOLKESSON, 1997). Estas interfaces possibilitam o acesso direto a registradores,

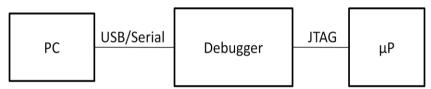

posições de memória, entre outros recursos. Disponível na maioria dos processadores, a interface de OCD (*On-chip Common Debugging*) tem como maior desvantagem a falta de padronização na sua elaboração. Devido a esta questão fabricantes de processadores disponibilizam sua própria interface e meios de acesso aos recursos de hardware. Um exemplo é o equipamento BDM (*Background Debug Mode*) disponibilizado para família PowerPC de processadores da empresa Freescale® (FREESCALE SEMICONDUCTOR). Tal equipamento possibilita o controle e monitoramento de um processador através de uma conexão a um PC. O dispositivo BDM acessa os recursos do processador através de sua própria interface JTAG3.

A atratividade da técnica resume-se a acessibilidade dos recursos de hardware em tempo real a execução de uma aplicação. Acesso à memória, registradores, suporte a breakpoints, entre outros, são alguns dos itens disponibilizados por este tipo de tecnologia. Desta forma, é então possível emular uma falha e observar o seu efeito na aplicação em execução. Tal abordagem é transparente para a aplicação não necessitando qualquer modificação no software. No entanto, dependendo do recurso que se deseja emular uma falha, pode ser necessário colocar o processador em um estado especial de depuração, comprometendo o desempenho de execução.

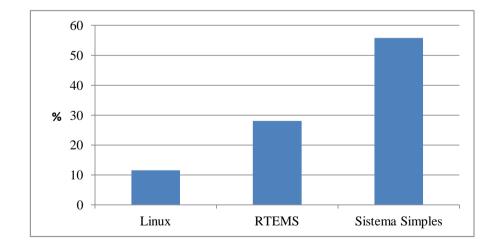

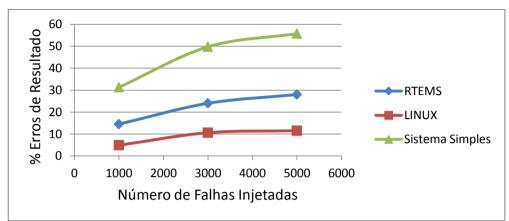

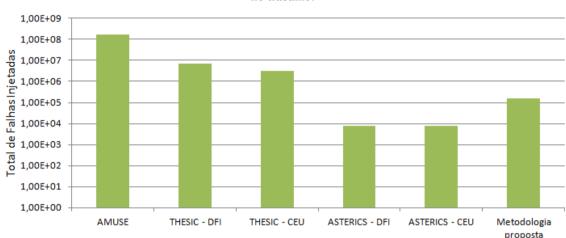

Figura 2.8: Utilização de interface de depuração de processadores.